Изобретение относится к вычислительной технике и предназначено для оценки предпочтительного уровня унификации технических средств (ТС) с целью минимизации затрат на проектирование и изготовление ТС при достаточном уровне их эффективности. Эту оценку можно осуществить с помощью обобщенного критерия, учитывающего эффективность ТС и объем финансирования их проектирования и изготовления.

Наиболее близким по технической сущности является устройство [1], содержащее группу из m первых регистров 1i (i=1…m), группу из m вторых регистров 2i, группу из m третьих регистров 3i, группу из m четвертых регистров 4i, пятый регистр 5, группу из m первых блоков умножения 6i, группу из m вторых блоков умножения 8i, группу из m первых сумматоров 9i, группу из n шестых регистров 10j, группу из n седьмых регистров 11j, группу из n третьих блоков умножения 12j (j=1…n), группу из m первых блоков деления 13i, второй сумматор 14, информационные входы которого подсоединены к выходам одноименных третьих блоков умножения 12j (j=1…n), первые входы которых подсоединены к выходам одноименных шестых регистров 10j, а вторые входы - к выходам одноименных седьмых регистров 11j, прямые выходы первых регистров 1i (i=1…m) подсоединены к первым входам одноименных первых блоков умножения 6i (i=1…m), вторые входы которых подсоединены к выходам одноименных вторых регистров 2i, выходы третьих регистров 3i (i=1…m) подсоединены к первым входам одноименных вторых блоков умножения 8i (i=1…m), выход каждого из которых подсоединен к первым входам первых сумматоров 9i, выходы которых подсоединены к первым входам первых блоков деления 13i, вторые входы которых подсоединены к выходам одноименных четвертых регистров 4i.

Задача изобретения - создать устройство, обеспечивающее повышение надежности и быстродействия за счет существенного сокращения аппаратных затрат. Это решение достигается тем, что в устройство для оценки предпочтительного уровня унификации ТС, содержащее группу из m первых регистров 1i (i=1…m), группу из m вторых регистров 2i, группу из m третьих регистров 3i, группу из m четвертых регистров 4i, пятый регистр 5, группу из m первых блоков умножения 6i, группу из m вторых блоков умножения 8i, группу из m первых сумматоров 9i, группу из n шестых регистров 10j, группу из n седьмых регистров 11j, группу из n третьих блоков умножения 12j (j=1…n), группу из m первых блоков деления 13i, второй сумматор 14, введены m вторых блоков деления 7i, триггер 15, первый элемент И 16, второй элемент И 17, элемент ИЛИ 18, первый элемент задержки 19, второй элемент задержки 20, третий элемент задержки 21, четвертый элемент задержки 22 и пятый элемент задержки 23, блок выбора максимального кода 24 вместе со связями.

Новизна предлагаемого устройства заключается в том, что новое техническое устройство отличается от прототипа тем, что дополнительно в него введены m вторых блоков деления 7i, триггер 15, первый элемент И 16, второй элемент И 17, элемент ИЛИ 18, первый элемент задержки 19, второй элемент задержки 20, третий элемент задержки 21, четвертый элемент задержки 22 и пятый элемент задержки 23, блок выбора максимального кода 24, первый выход триггера 15 подсоединен к первому входу первого элемента И 16, второй вход которого подсоединен к выходу пятого регистра 5, а выход - к первому входу элемента ИЛИ 18, второй выход триггера 15 подсоединен к первому входу второго элемента И 17, второй вход которого подсоединен к выходу второго сумматора 14, а выход - к второму входу элемента ИЛИ 18, выход которого подсоединен к первым входам вторых блоков деления 7i, вторые входы которых подсоединены к выходам одноименных первых блоков умножения 6i, а выходы - к вторым входам первых сумматоров 9i, обратные выходы первых регистров 1i (i=1…m) подсоединены к вторым входам одноименных вторых блоков умножения 8i (i=1…m), выходы первых блоков деления 13i подсоединены к одноименным входам блока выбора максимального кода 24, выходы 28 и 29 которых являются первым и вторым выходами устройства, первый вход 27 устройства подсоединен к управляющему входу сумматора 14 и к входу первого элемента задержки 19, выход которого подсоединен к управляющим входам вторых блоков деления 7i, к управляющим входам вторых блоков умножения 8i (i=1…m) и к входу второго элемента задержки 20, выход которого подсоединен к управляющим входам первых сумматоров 9i и к входу третьего элемента задержки 21, выход которого подсоединен к управляющим входам первых блоков деления 13i и к входу четвертого элемента задержки 22, выход которого подсоединен к управляющему входу блока выбора максимального кода 24 и к входу пятого элемента задержки 23, выход которого является третьим выходом 30 устройства.

Оценку предпочтительного уровня унификации ТС можно осуществить с помощью обобщенного критерия Pi, величина которого для i-го уровня унификации ТС определяется по формуле [1]:

где m - число анализируемых уровней унификации ТС;

Wi - эффективность ТС при i-м уровне ее унификации (например, вероятность выполнения задачи);

Si - объем финансирования проектирования и изготовления ТС при i-м уровне унификации (например, тыс. руб.).

Величину Si можно вычислить следующим образом [1]:

где Kпрi - коэффициент применяемости, характеризующий i-й уровень унификации ТС (0<Kпрi<1);

Sиi - стоимость составных частей элементов ТС, бывших в использовании при i-м уровне ее унификации (например, тыс. руб.);

Sнi - стоимость новых составных частей элементов ТС при i-м уровне ее унификации;

G - коэффициент, учитывающий степень проработки элементов ТС, бывших в использовании (он зависит от количества лет использования).

Коэффициент применяемости Kпрi, характеризующий уровень унификации ТС, представляет собой отношение количества использованных ранее элементов к общему числу элементов, содержащихся в ТС.

Опыт показывает, что коэффициент G можно оценить по следующей формуле [1]:

где Tmax - максимальное возможное время использования (проработки) унифицируемых элементов (подсистем) ТС, год;

T - фактическое время использования (проработки) этих элементов, год.

Принимая во внимание, что для современных ТС Tmax=10 годам, выражение (3) можно записать в виде

Поскольку упомянутую эффективность целесообразно увеличивать, а объем финансирования - уменьшать, то необходимо искать значение Kпрi, обеспечивающее наибольшую величину критерия Pi, т.е. Pimax. Далее это будет РЕЖИМ 1 работы устройства.

Недостатком этого подхода является низкая точность упомянутой оценки из-за следующего допущения: фактическое время использования (проработки) всех элементов (подсистем) ТС считаются одинаковыми.

Повышение точности оценки предпочтительного уровня унификации ТС за счет учета разницы времени использования различных ее элементов (подсистем) можно осуществить следующим образом [1]. Характеристики, учитывающие отличие во времени использования элементов ТС, назовем средневзвешенными. Тогда формулу (2) можно переписать в следующем виде:

где Sicb - средневзвешенный объем финансирования и изготовления ТС при i-м уровне ее унификации ТС;

Gcb - средневзвешенный коэффициент, учитывающий степень проработки элементов ТС, бывших в использовании (он зависит от средневзвешенного количества лет использования). По аналогии с формулой (4) величина Gcb вычисляется по следующей формуле:

где Tcb - средневзвешенное фактическое время использования элементов ТС, год.

Значение Tcb определяется по следующей зависимости:

где bj - весовой коэффициент, учитывающий важность j-го элемента в составе ТС, причем

n - общее количество элементов в составе ТС.

Проведя вычисления по формулам (7), (6), (5) и (1) можно определить тот вариант уровня унификации Kпрi, который обеспечивает максимальное значение критерия Pi.

Следует отметить, что в формуле (1) вместо величины Si подставляется значение Sicb.

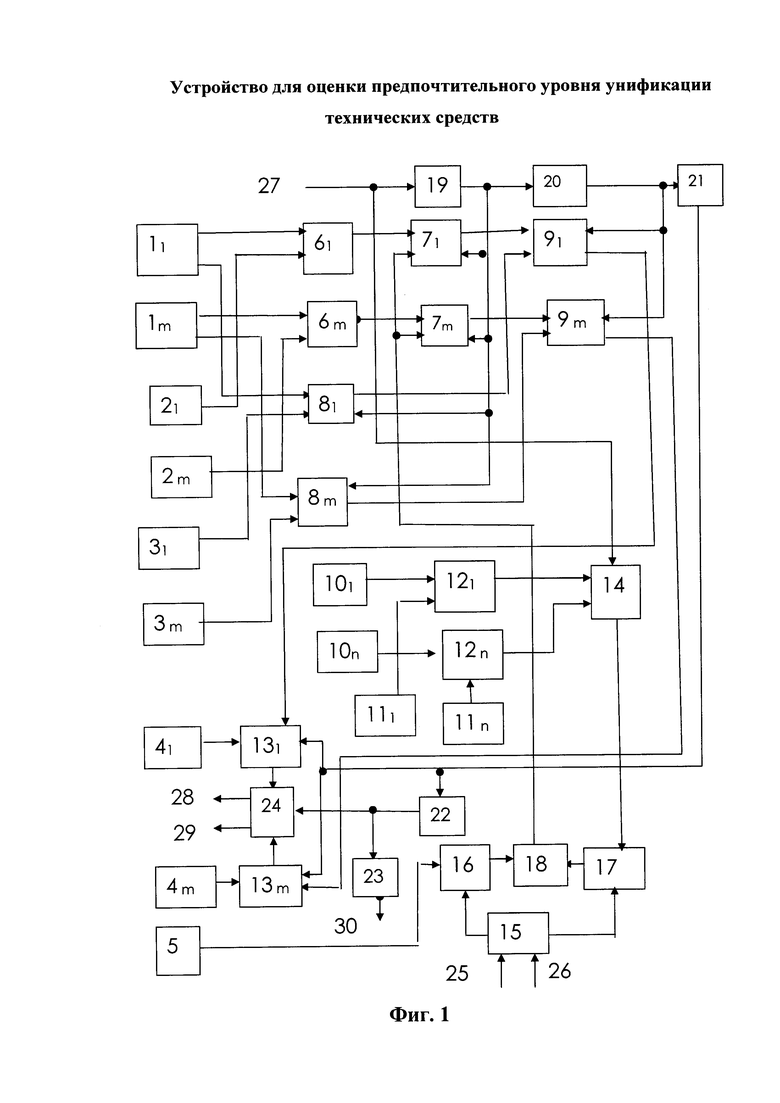

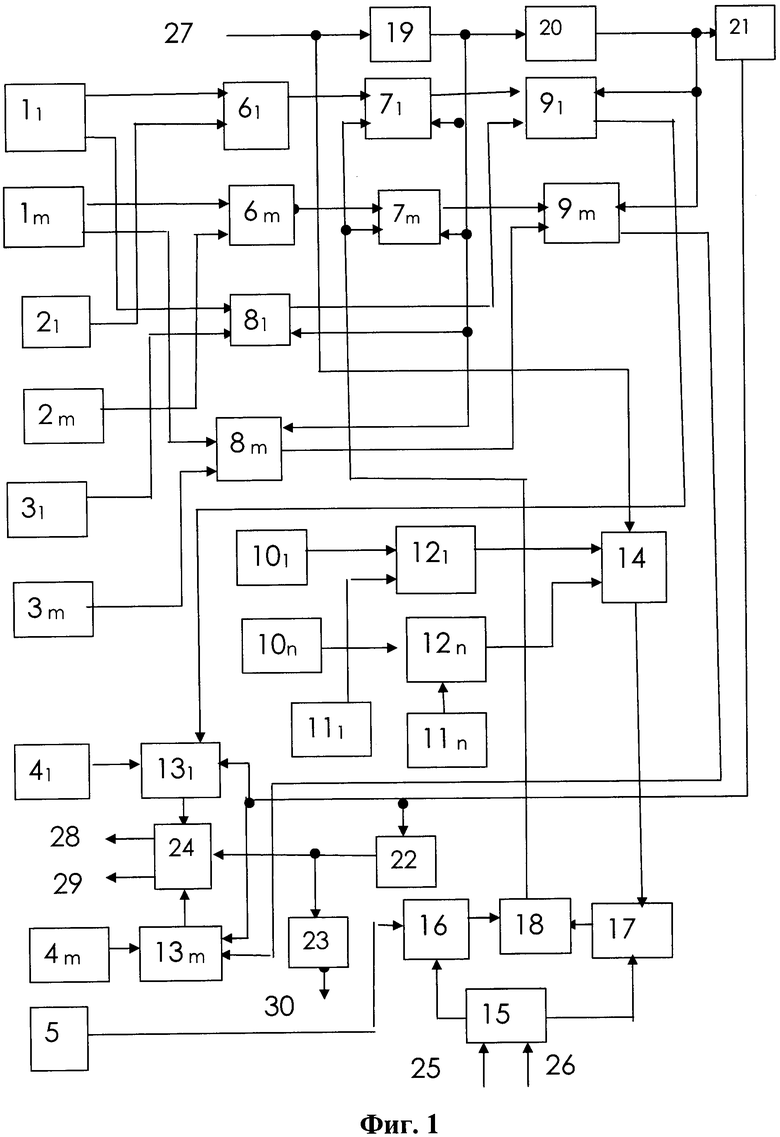

Сущность изобретения поясняется чертежом. На чертеже (фиг. 1) представлена структурная схема предлагаемого устройства, содержащая группы из m регистров 1i, 2i, 3i, 4i (i=1…m), регистр 5, m блоков умножения 6i, m блоков деления 7i, m блоков умножения 8i, m сумматоров 9i, n регистров 10j, 11j и блоков умножения 12j (j=1…n), m блоков 13i деления, сумматор 14, триггер 15, группы элементов И 16 и И 17, группа элементов ИЛИ 18, элементы задержки 19, 20, 21, 22 и 23, блок выбора максимального кода 24, входы устройства 25, 26 и 27, выходы устройства 28, 29 и 30.

В исходном состоянии на регистрах 1i (i=1…m) хранятся величины коэффициентов применяемости Kпрi, характеризующие i-й уровень унификации ТС. На регистрах 2i хранятся значения стоимости Sиi составных частей (элементов) ТС, бывших в использовании при i-м уровне ее унификации. На регистрах 3i хранятся величины стоимости Sнi новых составных частей (элементов) ТС при i-м уровне ее унификации. На регистрах 4i хранятся значения эффективности Wi ТС при i-м уровне ее унификации. На регистре 5 хранится величина фактического времени T использования (проработки) унифицируемых элементов ТС. На регистрах 10j (j=1…n) хранятся величины фактического времени использования (проработки) Tj унифицируемых элементов ТС, если величины фактического времени различны. На регистрах 11j (j=1…n) хранятся величины bj весовых коэффициентов, учитывающие важность j-го элемента в составе ТС.

После занесения всей исходной информации коды с выходов групп регистров 10j и 11j (j=1…n) значения Tj и bj засылаются соответственно на первый и второй входы каждого соответствующего блока умножения 12j. А коды с выходов первой 1i и второй 2i (i=1…m) групп регистров (значения Kпрi и Sиi) засылаются соответственно на первый и второй входы каждого соответствующего блока умножения 6i.

По сигналу пуска по входу 27 на сумматоре 14 происходит сложение значений Tj∗bj с выходов блоков умножения 12j (j=1…n). Результат с выхода сумматора 14 поступает на первый вход элемента И 17, с выхода которого значение суммы через элемент ИЛИ 18 поступает в качестве делителя на входы блоков деления 7i - это для режима работы устройства, при котором значения Tj различны, что обеспечивается установкой триггера 15 по входу 26 в соответствующее состояние.

Кроме того, сигнал пуска по входу 27 поступает на вход элемента задержки 19, который задерживает сигнал на суммарное время надежного срабатывания сумматора 14, элементов И 17 и ИЛИ 18. Сигнал с выхода элемента задержки 19 поступает на вход элемента задержки 20 и на управляющие входы блоков умножения 8i и блоков деления 7i (i=1…m).

С выходов блоков умножения 6i (i=1…m) значения Sиi∗Kпрi подаются на вход делимого каждого соответствующего блока деления 7i (i=1…m). На другой вход блока деления 7i в качестве делителя поступает код с выхода элемента ИЛИ 18, а на вход управления поступает код с выхода элемента задержки 19. С выходов блока деления 7i величины Sиi∗Kпрi/Tcb направляются на первые входы сумматоров 9i.

На блоках умножения 8i по сигналу с выхода элемента задержки 19 происходит умножение значений кодов с выходов регистров 3i и кодов с обратных выходов регистров 1i. При этом код с обратного выхода регистра 1i является дополнением до единицы, то есть значение (1-Kпрi), так как 0<Kпрi<1.

Элемент задержки 20 задерживает сигнал на время надежного срабатывания блока деления 7i, так как время срабатывания блока умножения намного меньше времени срабатывания блока деления. С выхода элемента задержки 20 сигнал поступает на управляющие входы сумматоров 9i и на вход элемента задержки 21.

С выходов сумматоров 9i значения Si, вычисленные по формуле (2), засылаются на вход делителя каждого соответствующего блока деления 13i, на второй его вход в качестве делимого поступает значение эффективности Wi с выхода регистра 4i. Блоки деления 13i срабатывают по сигналу с выхода элемента задержки 21. Элемент задержки 21 задерживает сигнал на время надежного срабатывания сумматора 9i.

Сигнал с выхода элемента задержки 21 поступает также и на вход элемента задержки 22, который задерживает сигнал на время надежного срабатывания блока деления 13i.

С выходов блоков деления 13i результаты поступают на одноименные входы блока выбора максимального кода 24, который срабатывает по сигналу с выхода элемента задержки 22.

На выходе 28 блока выбора максимального кода 24 появляется значение максимального критерия Рi, то есть Pmax. Этой величине будет соответствовать значение Kпр, характеризующее предпочтительный уровень унификации ТС. А на выходе 29 блока выбора максимального кода 24 появляется позиционный номер максимального критерия Pi.

Сигнал с выхода элемента задержки 22 поступает также и на вход элемента задержки 23, который задерживает сигнал на время надежного срабатывания блока выбора максимального кода 24. Сигнал на выходе 30 элемента задержки 23 означает окончание работы устройства.

Блок выбора максимального кода 24 может быть выполнен в соответствии с известным устройством [2].

Устройство функционирует в двух режимах в зависимости от исходных значений фактического времени использования (проработки) Tj (j=1…n) унифицируемых элементов ТС.

Режим I. Случай, когда фактическое время T использования элементов ТС одинаково. Тогда триггер 15 по входу 25 устанавливается в состояние, при котором информация на входы блоков деления 7i будет поступать через открытый элемент И 16 и элемент ИЛИ 18 с выхода регистра 5.

Режим II. Вариант, когда фактическое время использования элементов ТС различно. Тогда триггер 15 по входу 26 устанавливается в состояние, при котором информация на входы блоков деления 7i будет поступать через открытый элемент И 17 и элемент ИЛИ 18 с выхода сумматора 14.

Таким образом, технический результат заявляемого изобретения достигается за счет технических средств (блоков и элементов), упомянутых в описании работы устройства. Описанное устройство позволяет повысить надежность и быстродействие устройства при проектировании и изготовлении ТС при достаточном уровне их эффективности.

Промышленная применяемость обосновывается тем, что оно может быть использовано в разных областях (отраслях) производства при выборе предпочтительного уровня унификации ТС.

Следует ожидать, что данное изобретение может иметь большое значение в сфере массового производства, например в машиностроении (автомобили, станкостроение и пр.), электронной и радиопромышленности.

Литература.

1. RU 2519049. 2014.

2. USSR 1128249. 1984.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ПРИНЯТИЯ РЕШЕНИЯ В УСЛОВИЯХ НЕОПРЕДЕЛЕННОСТИ | 2012 |

|

RU2517243C1 |

| Устройство для моделирования процесса выбора товара | 2017 |

|

RU2666617C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ О РЮКЗАКЕ | 2010 |

|

RU2443013C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ О РЮКЗАКЕ | 2014 |

|

RU2542661C1 |

| Устройство для решения задачи о рюкзаке | 2015 |

|

RU2613854C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ВЫБОРА ТОВАРА | 2012 |

|

RU2491620C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ВЫБОРА ТОВАРА | 2016 |

|

RU2617564C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ ЗАЩИТЫ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 2007 |

|

RU2335016C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ О РЮКЗАКЕ | 2009 |

|

RU2413287C2 |

| Устройство для решения задачи выбора технических средств сложной системы | 2018 |

|

RU2713868C1 |

Изобретение относится к вычислительной технике и предназначено для оценки предпочтительного уровня унификации технических средств (ТС) и определения его оптимального уровня. Технический результат - повышение надежности и быстродействия устройства. Устройство для оценки уровня унификации ТС содержит группу из m первых регистров 1i (i=1…m), группу из m вторых регистров 2i, группу из m третьих регистров 3i, группу из m четвертых регистров 4i, пятый регистр 5, группу из m первых блоков умножения 6i, группу из m вторых блоков умножения 8i, группу из m первых сумматоров 9i, группу из n шестых регистров 10j, группу из n седьмых регистров 11j, группу из n третьих блоков умножения 12j (j=1…n), группу из m первых блоков деления 13i, второй сумматор 14, m вторых блоков деления 7i, триггер 15, первый элемент И 16, второй элемент И 17, элемент ИЛИ 18, первый элемент задержки 19, второй элемент задержки 20, третий элемент задержки 21, четвертый элемент задержки 22 и пятый элемент задержки 23, выход которого является третьим выходом 30 устройства, блок выбора максимального кода 24, выходы 28 и 29 которого являются первым и вторым выходами устройства, первый вход 27 устройства подсоединен к управляющему входу сумматора 14 и к входу первого элемента задержки 19. 1 ил.

Устройство для оценки предпочтительного уровня унификации технических средств, содержащее группу из m первых регистров 1i (i=1…m), группу из m вторых регистров 2i, группу из m третьих регистров 3i, группу из m четвертых регистров 4i, пятый регистр 5, группу из m первых блоков умножения 6i, группу из m вторых блоков умножения 8i, группу из m первых сумматоров 9i, группу из n шестых регистров 10j, группу из n седьмых регистров 11j, группу из n третьих блоков умножения 12j (j=1…n), группу из m первых блоков деления 13i, второй сумматор 14, информационные входы которого подсоединены к выходам одноименных третьих блоков умножения 12j (j=1…n), первые входы которых подсоединены к выходам одноименных шестых регистров 10j, а вторые входы - к выходам одноименных седьмых регистров 11j, прямые выходы первых регистров 1i (i=1…m) подсоединены к первым входам одноименных первых блоков умножения 6i (i=1…m), вторые входы которых подсоединены к выходам одноименных вторых регистров 2i, выходы третьих регистров 3i (i=1…m) подсоединены к первым входам одноименных вторых блоков умножения 8i (i=1…m), выход каждого из которых подсоединен к первым входам первых сумматоров 9i, выходы которых подсоединены к первым входам первых блоков деления 13i, вторые входы которых подсоединены к выходам одноименных четвертых регистров 4i, отличающееся тем, что в него дополнительно включены m вторых блоков деления 7i, триггер 15, первый элемент И 16, второй элемент И 17, элемент ИЛИ 18, первый элемент задержки 19, второй элемент задержки 20, третий элемент задержки 21, четвертый элемент задержки 22 и пятый элемент задержки 23, блок выбора максимального кода 24, первый выход триггера 15 подсоединен к первому входу первого элемента И 16, второй вход которого подсоединен к выходу пятого регистра 5, а выход - к первому входу элемента ИЛИ 18, второй выход триггера 15 подсоединен к первому входу второго элемента И 17, второй вход которого подсоединен к выходу второго сумматора 14, а выход - ко второму входу элемента ИЛИ 18, выход которого подсоединен к первым входам вторых блоков деления 7i, вторые входы которых подсоединены к одноименным выходам первых блоков умножения 6i, а выходы - к вторым входам первых сумматоров 9i, обратные выходы первых регистров 1i (i=1…m) подсоединены к вторым входам одноименных вторых блоков умножения 8i (i=1…m), выходы первых блоков деления 13i подсоединены к одноименным входам блока выбора максимального кода 24, выходы 28 и 29 которого являются первым и вторым выходами устройства, первый вход 27 устройства подсоединен к управляющему входу сумматора 14 и к входу первого элемента задержки 19, выход которого подсоединен к управляющим входам вторых блоков деления 7i, к управляющим входам вторых блоков умножения 8i (i=1…m) и к входу второго элемента задержки 20, выход которого подсоединен к управляющим входам первых сумматоров 9i и к входу третьего элемента задержки 21, выход которого подсоединен к управляющим входам первых блоков деления 13i и к входу четвертого элемента задержки 22, выход которого подсоединен к управляющему входу блока выбора максимального кода 24 и к входу пятого элемента задержки 23, выход которого является третьим выходом 30 устройства.

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ПРЕДПОЧТИТЕЛЬНОГО УРОВНЯ УНИФИКАЦИИ ТЕХНИЧЕСКИХ СИСТЕМ | 2013 |

|

RU2519049C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ПРИНЯТИЯ РЕШЕНИЯ В УСЛОВИЯХ НЕОПРЕДЕЛЕННОСТИ | 2013 |

|

RU2534924C2 |

| US2008244533 A1, 02.10.2008. | |||

Авторы

Даты

2016-06-10—Публикация

2014-12-25—Подача