Изобретение относится к области вычислительной техники и может быть использовано для получения точного решения задачи выбора товара. Цель изобретения - расширение функциональных возможностей устройства за счет более полного учета характеристик товара. Устройство в своем составе содержит: матрицу m*n первых регистров 1ij (i=1…m, j=1…n), по числу строк матрицы вторые регистры 6i (i=1…m), по числу строк матрицы сумматоры 8i (i=1…m), по числу строк матрицы блоки элементов И 7i (i=1…m), по числу столбцов матрицы третьи регистры 4j (j=1…n), четвертые регистры 5j (j=1…n), матрицу m*n первых блоков деления 2i,j (i=1…m, j=1…n), матрицу блоков умножения 3i,j (i=1…m, j=1…n), блок элементов ИЛИ 9, блок выбора максимального кода 10, дешифратор 11, первый элемент задержки 12, второй элемент задержки 13, третий элемент задержки 14, четвертый элемент задержки 15, триггер 16, пятые регистры 19i (i=1…m), вторые блоки деления 18i (i=1…m), пятый элемент задержки 17, вместе со связями.

Работа устройства основана на преобразовании исходных данных о наборе товаров и выборе из них предпочтительного.

Сущность рассматриваемой задачи заключается в следующем. Имеется m однотипных товаров с известными n характеристиками qj (j=1…n) и их эталонные значения q0j. Известны также весовые коэффициенты αj (j=1, …, n) важности для конкретного потребителя j-й характеристики товара. Тогда показатель конкурентоспособности каждого товара по отношению к выбранному эталону по j-му качеству определяется как Qj=qj/q0j, а для всех товаров эти показатели будут описываться матрицей Qm*n.

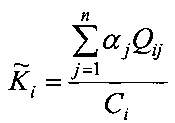

Интегральный показатель конкурентоспособности i-го товара (i=1…m) должен учитывать цену товара Ci (i=1…m). В этом случае он будет иметь вид:

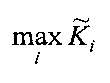

Выбор потребителя в этом случае сводится к максимизации интегрального показателя конкурентоспособности, т.е. потребитель предпочтет товар, имеющий

Известны устройства для подобного моделирования [1] которые позволяют определить наилучший вариант по иным критериям.

Наиболее близким по технической сущности к заявляемому устройству является устройство для моделирования [1], содержащее матрицу m*n первых регистров 1i,j (i=1…m, j=1…n), по числу строк матрицы вторые регистры 6i (i=1…m), по числу строк матрицы сумматоры 8i (i=1…m), по числу строк матрицы блоки элементов И 7i (i=1…m), по числу столбцов матрицы третьи регистры 4j (j=1…n), четвертые регистры 5j (j=1…n), матрицу m*n первых блоков деления 2i,j (i=1…m, j=1…n), матрицу блоков умножения 3i,j (i=1…m, j=1…n), блок элементов ИЛИ 9, блок выбора максимального кода 10, дешифратор 11, первый элемент задержки 12, второй элемент задержки 13, третий элемент задержки 14, четвертый элемент задержки 15, триггер 16.

Недостатком данного устройства является невозможность моделирования выбора наилучшего варианта товара по заданным потребителем критериям с учетом стоимостных характеристик.

Задача изобретения - создать устройство, обеспечивающее моделирование выбора наилучшего варианта товара по заданным потребителем критериям.

Сущность изобретения состоит в том, что в устройство для моделирования процесса выбора товара, содержащее матрицу m*n первых регистров 1i,j, (i=1…m, j=1…n), по числу строк матрицы вторые регистры 6i, (i=1…m), по числу строк матрицы сумматоры 8i, (i=1…m), по числу строк матрицы блоки элементов И 7i (i=1…m), по числу столбцов матрицы третьи регистры 4j, (j=1…n), четвертые регистры 5j, (j=1…n), матрицу m*n первых блоков деления 2i,j (i=1…m, j=1…n), матрицу блоков умножения 3i,j, (i=1…m, j=1…n), блок элементов ИЛИ 9, блок выбора максимального кода 10, дешифратор 11, первый элемент задержки 12, второй элемент задержки 13, третий элемент задержки 14, четвертый элемент задержки 15, триггер 16, выход которого является выходом 21, а вход подсоединен к выходу четвертого элемента задержки 15, пусковой вход 20 подсоединен к входу первого элемента задержки 12 и к управляющим входам блоков деления 2i,j (i=1…m, j=1…n), второй вход каждого из которых подсоединен к выходу одноименного первого регистра 1i,j (i=1…m, j=1…n), а третий вход - к выходу одноименного четвертого регистра 5j, (j=1…n), выход первого элемента задержки 12 подсоединен к входу второго элемента задержки 13 и к управляющим входам блоков умножения 3i,j (i=1…m, j=1…n), второй вход каждого из которых подсоединен к выходу одноименного блока деления 2i,j (i=1…m, j=1…n), а третий вход - к выходу одноименного третьего регистра 4j, (j=1…n), выход второго элемента задержки 13 подсоединен к входу третьего элемента задержки 14 и к управляющим входам сумматоров 8i (i=1…m), вторые входы которого подсоединены к выходам одноименных блоков умножения 3i,j (i=1…m, j=1…n), первый выход блока выбора максимального кода 10 является выходом 23 устройства, а второй выход подсоединен к входу дешифратора 11, выходы которого подсоединены к одноименным управляющим входам блоков элементов И 7i (i=1…m), вторые входы которых подсоединены к выходам вторых регистров 6i (i=1…m), а выходы подсоединены к одноименным входам блока элементов ИЛИ 9, выход которого является выходом 22 устройства,  пятые регистры 19i (i=1…m), вторые блоки деления 18i (i=1…m), пятый элемент задержки 17, вход которого подсоединен к выходу третьего элемента задержки 14, а выход подсоединен к входу четвертого элемента задержки 15 и к управляющему входу блока выбора максимального кода 10, выход пятого регистра 19i (i=1…m) подсоединен к первому входу второго блока деления 18i (i=1…m), второй вход которого подсоединен к выходу сумматора 8i (i=1…m), а выход подсоединен к одноименному входу блока выбора максимального кода 10, выход третьего элемента задержки 14 подсоединен к управляющему входу второго блока деления 18i (i=1…m).

пятые регистры 19i (i=1…m), вторые блоки деления 18i (i=1…m), пятый элемент задержки 17, вход которого подсоединен к выходу третьего элемента задержки 14, а выход подсоединен к входу четвертого элемента задержки 15 и к управляющему входу блока выбора максимального кода 10, выход пятого регистра 19i (i=1…m) подсоединен к первому входу второго блока деления 18i (i=1…m), второй вход которого подсоединен к выходу сумматора 8i (i=1…m), а выход подсоединен к одноименному входу блока выбора максимального кода 10, выход третьего элемента задержки 14 подсоединен к управляющему входу второго блока деления 18i (i=1…m).

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

Новизна предлагаемого устройства заключается в том, что новое техническое устройство отличается от прототипа тем, что дополнительно в него введены пятые регистры 19i (i=1…m), вторые блоки деления 18i (i=1…m), пятый элемент задержки 17, вход которого подсоединен к выходу третьего элемента задержки 14, а выход подсоединен к входу четвертого элемента задержки 15 и к управляющему входу блока выбора максимального кода 10, выход пятого регистра 19i (i=1…m) подсоединен к первому входу второго блока деления 18i (i=1…m), второй вход которого подсоединен к выходу сумматора 8i (i=1…m), а выход подсоединен к одноименному входу блока выбора максимального кода 10, выход третьего элемента задержки 14 подсоединен к управляющему входу второго блока деления 18i (i=1…m).

Изобретательский уровень достигается тем, что ввод соответствующих элементов в известный прототип вместе со связями позволяет решить новую техническую задачу, решение которой в известных компьютерах и в литературе в настоящее время не отражено. Предлагаемое устройство позволяет расширить функциональные возможности устройства.

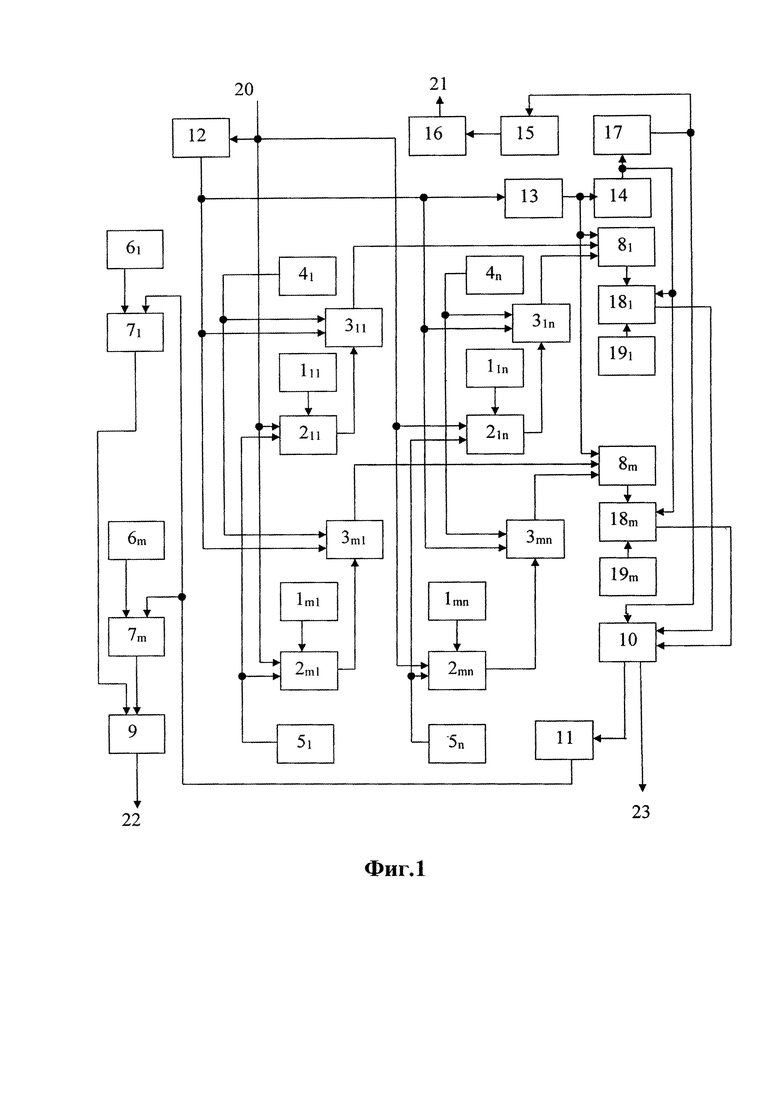

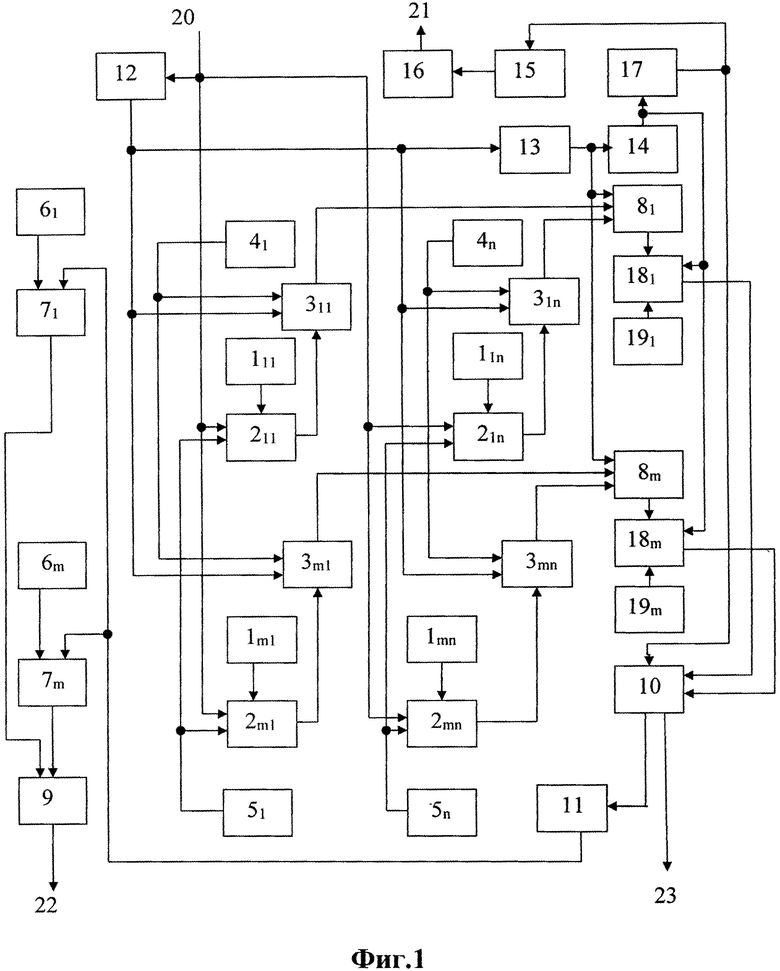

Сущность изобретения поясняется чертежом. На фиг.1 представлена структурная схема предлагаемого устройства, где на фиг. 1 представлены матрица регистров 1i,j (i=1…m, j=1…n), матрица блоков деления 2у, матрица блоков умножения 3i,j, по числу столбцов матрицы регистры 4j и регистры 5j (j=1…n), по числу строк матрицы регистры 6i (i=1…m), блоки элементов И 7i (i=1…m), сумматоры 8i (i=1…m), блок элементов ИЛИ 9, блок выбора максимального кода 10, дешифратор 11, элементы задержки 12, 13, 14, 15, триггер 16, пятые регистры 19i (i=1…m), вторые блоки деления 18i (i=1…m), пятый элемент задержки 17, вход 20, выходы 21, 22 и 23 вместе со связями.

Устройство работает следующим образом.

В исходном состоянии на регистрах 1i,j (i=1…m, j=1…n) хранятся j-е показатели качества i-го товара, на регистрах 4j хранятся весовые коэффициенты важности j-го показателя качества с точки зрения потребителя товара. На регистрах 5j (j=1…n) хранятся эталонные оценки j-х показателей качества товара. На регистрах 6i (i=1…m) хранятся коды анализируемых товаров. На регистрах 19i (i=1…m) хранятся стоимости анализируемых товаров. Триггер 16 находится в нулевом (сброшенном) состоянии, и на его выходе 21 находится нулевой сигнал.

Работа устройства начинается после подачи сигнала ПУСК на вход 20 устройства, после чего в блоках деления 2i,j (i=1…m, j=1…n) происходит деление содержимого регистра 1i,j (i=1…m, j=1…n) на содержимое регистра 5j (j=1…n). Одновременно пусковой входной сигнал 20 поступает на вход элемента задержки 12, который задерживает сигнал на время t12, равное времени надежного срабатывания блока деления 2i,j (i=1…m, j=1…n).

Сигнал с выхода элемента задержки 12 поступает на вход элемента задержки 13 и на управляющие входы блоков умножения 3i,j (i=1…m, j=1…n), где происходит умножение содержимого блока деления 2i,j (i=1…m, j=1…n) на значение содержимого регистра 4j (j=1…n).

Результат с выхода каждого блока умножения 3i,j (i=1…m, j=1…n) поступает на одноименный вход сумматора 8i (i=1…m), на управляющий вход которого поступает разрешающий сигнал с выхода элемента задержки 13, который задерживает сигнал на время t13, равное времени надежного срабатывания блока умножения 3i,j (i=1…m, j=1…n).

Коды с выхода сумматоров 8i (i=1…m) поступают на первые входы блоков деления 18i (i=1…m), на вторые входы которых в качестве делителя поступают коды с выходов регистров 19i (i=1…m).

Код с выхода элемента задержки 13 поступает также на вход элемента задержки 14, с выхода которого сигнал поступает на вход элемента задержки 17 и на управляющие входы блоков деления 18i (i=1…m). Элемент задержки 17 задерживает сигнал на время t17, равное времени надежного срабатывания блока деления 18i (i=1…m).

Коды с выходов блоков деления 18i (i=1…m) поступают на одноименные входы блока выбора максимального кода 10, который обеспечивает выбор максимального кода из группы поступивших и его порядковый номер. На управляющий вход блока 10 поступает сигнал с выхода элемента задержки 17.

Порядковый номер максимального кода с выхода блока 10 поступает на вход дешифратора 11, с выхода которого поступает на одноименные входы блоков элементов И 7i (i=1…m), с выходов которых коды поступают на одноименные входы блока элементов ИЛИ 9, на выходе 22 которого появляется код наилучшего товара.

Одновременно сигнал с выхода элемента задержки 15, который задерживает сигнал на время t15, равное времени надежного срабатывания блока 10, поступает на установочный в единичное состояние вход триггера 16, на выходе 21 которого появляется сигнал окончания работы устройства.

Предлагаемое устройство для моделирования процесса выбора товара в составе элементов 1-19 (см. фиг. 1) может быть построено на известных стандартных микросхемах, выпускаемых отечественной промышленностью, при этом блок 10 выбора максимального кода может быть реализован по известной схеме "Устройство для определения экстремального кода", представленной в [2].

1. АС №2491620, кл. G06F 12/14, 2013.

2. АС №997028, кл. G06F 7/04, 1983.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования процесса выбора изделия | 2021 |

|

RU2779255C1 |

| Устройство для моделирования процесса выбора товара | 2017 |

|

RU2666617C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ВЫБОРА ТОВАРА | 2012 |

|

RU2491620C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ПРЕДПОЧТИТЕЛЬНОГО УРОВНЯ УНИФИКАЦИИ ТЕХНИЧЕСКИХ СРЕДСТВ | 2014 |

|

RU2586573C1 |

| Устройство для моделирования графика работы сотрудников учреждения | 2022 |

|

RU2788323C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ О НАЗНАЧЕНИЯХ | 2010 |

|

RU2439687C1 |

| Устройство для решения задачи выбора технических средств сложной системы | 2018 |

|

RU2713868C1 |

| Устройство для решения задачи о назначениях исполнителей по работам | 2017 |

|

RU2665305C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ О РЮКЗАКЕ | 2010 |

|

RU2443013C1 |

| Устройство для решения задачи о назначениях | 2016 |

|

RU2613523C1 |

Изобретение относится к области вычислительной техники. Техническим результатом является расширение функциональных возможностей устройства за счет выбора наилучшего варианта товара по заданным потребителем критериям. Устройство содержит матрицу регистров 1i,j (i=1…m, j=1…n), матрицу блоков деления 2у, матрицу блоков умножения 3i,j, по числу столбцов матрицы регистры 4j и регистры 5j (j=1…n), по числу строк матрицы регистры 6i (i=1…m), блоки элементов И 7i (i=1…m), сумматоры 8i (i=1…m), блок элементов ИЛИ 9, блок выбора максимального кода 10, дешифратор 11, элементы задержки 12, 13, 14, 15, триггер 16, пятые регистры 19i (i=1…m), вторые блоки деления 18i (i=1…m), пятый элемент задержки 17, вход 20, выходы 21, 22 и 23 вместе со связями. 1 ил.

Устройство для моделирования процесса выбора товара, содержащее матрицу m*n первых регистров 1i,j (i=1…m, j=1…n), по числу строк матрицы вторые регистры 6i (i=1…m), по числу строк матрицы сумматоры 8i (i=1…m), по числу строк матрицы блоки элементов И 7i (i=1…m), по числу столбцов матрицы третьи регистры 4j (j=1…n), четвертые регистры 5j (j=1…n), матрицу m*n первых блоков деления 2i,j (i=1…m, j=1…n), матрицу блоков умножения 3i,j (i=1…m, j=1…n), блок элементов ИЛИ 9, блок выбора максимального кода 10, дешифратор 11, первый элемент задержки 12, второй элемент задержки 13, третий элемент задержки 14, четвертый элемент задержки 15, триггер 16, выход которого является выходом 21, а вход подсоединен к выходу четвертого элемента задержки 15, пусковой вход 20 подсоединен к входу первого элемента задержки 12 и к управляющим входам блоков деления 2i,j (i=1…m, j=1…n), второй вход каждого из которых подсоединен к выходу одноименного первого регистра 1i,j (i=1…m, j=1…n), а третий вход - к выходу одноименного четвертого регистра 5j (j=1…n), выход первого элемента задержки 12 подсоединен к входу второго элемента задержки 13 и к управляющим входам блоков умножения 3i,j (i=1…m, j=1…n), второй вход каждого из которых подсоединен к выходу одноименного блока деления 2i,j (i=1…m, j=1…n), а третий вход - к выходу одноименного третьего регистра 4j (j=1…n), выход второго элемента задержки 13 подсоединен к входу третьего элемента задержки 14 и к управляющим входам сумматоров 8i (i=1…m), вторые входы которого подсоединены к выходам одноименных блоков умножения 3i,j (i=1…m, j=1…n), первый выход блока выбора максимального кода 10 является выходом 23 устройства, а второй выход подсоединен к входу дешифратора 11, выходы которого подсоединены к одноименным управляющим входам блоков элементов И 7i (i=1…m), вторые входы которых подсоединены к выходам вторых регистров 6i (i=1…m), а выходы подсоединены к одноименным входам блока элементов ИЛИ 9, выход которого является выходом 22 устройства, отличающееся тем, что в него введены пятые регистры 19i (i=1…m), вторые блоки деления 18i (i=1…m), пятый элемент задержки 17, вход которого подсоединен к выходу третьего элемента задержки 14, а выход подсоединен к входу четвертого элемента задержки 15 и к управляющему входу блока выбора максимального кода 10, выход пятого регистра 19i (i=1…m) подсоединен к первому входу второго блока деления 18i (i=1…m), второй вход которого подсоединен к выходу сумматора 8i (i=1…m), а выход подсоединен к одноименному входу блока выбора максимального кода 10, выход третьего элемента задержки 14 подсоединен к управляющему входу второго блока деления 18i (i=1…m).

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ВЫБОРА ТОВАРА | 2012 |

|

RU2491620C1 |

| Устройство для определения экстремального кода | 1981 |

|

SU997028A1 |

| Измерительный прибор для зерновых материалов | 1933 |

|

SU34774A1 |

| US 20050021436 A1, 27.01.2005. | |||

Авторы

Даты

2017-04-25—Публикация

2016-03-29—Подача