Область техники, к которой относится изобретение

Настоящее изобретение относится к системе связи/широковещания.

Уровень техники

В системе связи/широковещания, производительность линии связи может значительно снижаться из-за различных шумов канала и явления замирания и межсимвольной помехи (ISI). Поэтому, для реализации высокоскоростных цифровых систем связи/широковещания, требующих обработки больших объемов данных и высокой надежности, например мобильной связи нового поколения, цифрового вещания и мобильного интернета, требуется развитие технологии для преодоления шума и замирании и ISI. В последнее время, в рамках исследований для преодоления шума и т.д., активно проводятся исследования в отношении кода коррекции ошибок в качестве способа повышения надежности связи и широковещания за счет эффективного восстановления искаженной информации.

Код контроля четности низкой плотности (LDPC), впервые введенный в 1960-х Gallager, был забыт по причине сложности, трудной для реализации на технологическом уровне того времени. Однако, поскольку турбокод, предложенный Berrou и Glavieux, Thitimajshima в 1993 г. продемонстрировал производительность, приближающуюся к канальной емкости по Шеннону, были проведены различные анализы в отношении производительности и характеристики турбокода, и осуществлялись различные исследования в отношении итерационного декодирования и канального кодирования на основании графика. Это стало побудительной причиной возвращения к исследованиям кода LDPC в конце 1990-х, в результате которых было установлено, что когда декодирование осуществляется с применением итерационного декодирования на основании алгоритма суммы произведений на графике Таннера, соответствующем коду LDPC, достигается производительность, приближающаяся к канальной емкости по Шеннону.

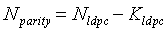

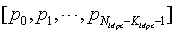

Код LDPC, в общем случае, задается как матрица контроля четности м может выражаться с использованием двустороннего графика, обычно именуемого графиком Таннера. LDPC-кодер принимает информационное слово LDPC, состоящее из

LDPC-кодирование включает в себя процесс для определения кодового слова, удовлетворяющего условию уравнения (1).

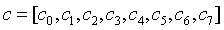

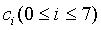

В уравнении (1), H это матрица проверки четности, c это кодовое слово, ci это i-й бит кодового слова, и Nldpc это длина кодового слова.

Матрица H проверки четности состоит из Nldpc столбцов, и i-й столбец означает, что он связан с i-м битом кодового слова ci.

В общем случае, согласно коду LDPC, кодирование осуществляется в случае, когда длина информационного слова и длина кодового слова заранее определены, как

В случае, когда участок бита сокращается или прореживается с учетом информационного слова и длины четности, производительность кодового слова может заметно изменяться на основании того, какой бит сокращается или прореживается. Таким образом, существует необходимость в способе выбора сокращенного бита и прореженных битов для поддержания оптимизированной производительности.

Сущность изобретения

Аспект настоящего изобретения призван решить, по меньшей мере, вышеупомянутые проблемы и/или недостатки и обеспечить, по меньшей мере, описанные ниже преимущества. Соответственно, аспект настоящего изобретения призван обеспечить устройство и способ выбора сокращенных и прореженных битов при поддержании оптимизированной производительности в системе связи/широковещания.

В соответствии с аспектом настоящего изобретения, предусмотрен способ действия передающей стороны в системе связи/широковещания. Способ включает в себя определение количества битов, подлежащих заполнению нулями, определение количества

В соответствии с другим аспектом настоящего изобретения, предусмотрен способ действия передающей стороны в системе связи/широковещания. Способ включает в себя LDPC-кодирование информационных битов контроля четности низкой плотности (LDPC) для генерации кодового слова, определение количества

В соответствии с еще одним аспектом настоящего изобретения, предусмотрен способ действия принимающей стороны в системе связи/широковещания. Способ включает в себя прием сокращенного кодового слова, определение количества битов заполнения нулями, определение количества

В соответствии с еще одним аспектом настоящего изобретения, предусмотрен способ действия принимающей стороны в системе связи/широковещания. Способ включает в себя: прием прореженного кодового слова, определение количества прореженных битов среди битов четности контроля четности низкой плотности (LDPC) прореженного кодового слова, определение количества

В соответствии с еще одним аспектом настоящего изобретения, предусмотрено устройство передающей стороны в системе связи/широковещания. Устройство может включать в себя блок заполнения для определения количества битов, подлежащих заполнению нулями, определения количества

В соответствии с еще одним аспектом настоящего изобретения, предусмотрено устройство передающей стороны в системе связи/широковещания. Устройство может включать в себя кодер для LDPC-кодирования информационных битов контроля четности низкой плотности (LDPC) для генерации кодового слова, и блок прореживания для определения количества

В соответствии с еще одним аспектом настоящего изобретения, предусмотрено устройство принимающей стороны в системе связи/широковещания. Устройство может включать в себя приемник для приема сокращенного кодового слова, блок восстановления сокращенных битов для определения количества битов заполнения нулями, определения количества

В соответствии с еще одним аспектом настоящего изобретения, предусмотрено устройство принимающей стороны в системе связи/широковещания. Устройство может включать в себя приемник для приема прореженного кодового слова, и блок восстановления битов прореживания для определения количества прореженных битов среди битов четности контроля четности низкой плотности (LDPC) прореженного кодового слова, определения количества

Система связи/широковещания может кодировать и декодировать информационные биты различных длин и одновременно поддерживать оптимизированную производительность путем группирования столбцов с учетом характеристики матрицы проверки четности, и осуществления сокращения и прореживания на основе групп битов, соответствующих каждой группе столбцов.

Другие аспекты, преимущества и отличительные признаки изобретения станут ясны специалистам в данной области техники из нижеследующего подробного описания, которое, совместно с прилагаемыми чертежами, раскрывает иллюстративные варианты осуществления изобретения.

Краткое описание чертежей

Вышеуказанные и другие аспекты, признаки и преимущества определенных примерных вариантов осуществления настоящего изобретения явствуют из нижеследующего описания, рассматриваемого совместно с прилагаемыми чертежами, в которых:

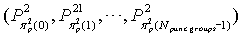

фиг. 1 - вид, демонстрирующий пример матрицы проверки четности, предусмотренной в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

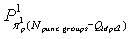

фиг. 2 - блок-схема, демонстрирующая передающую сторону в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

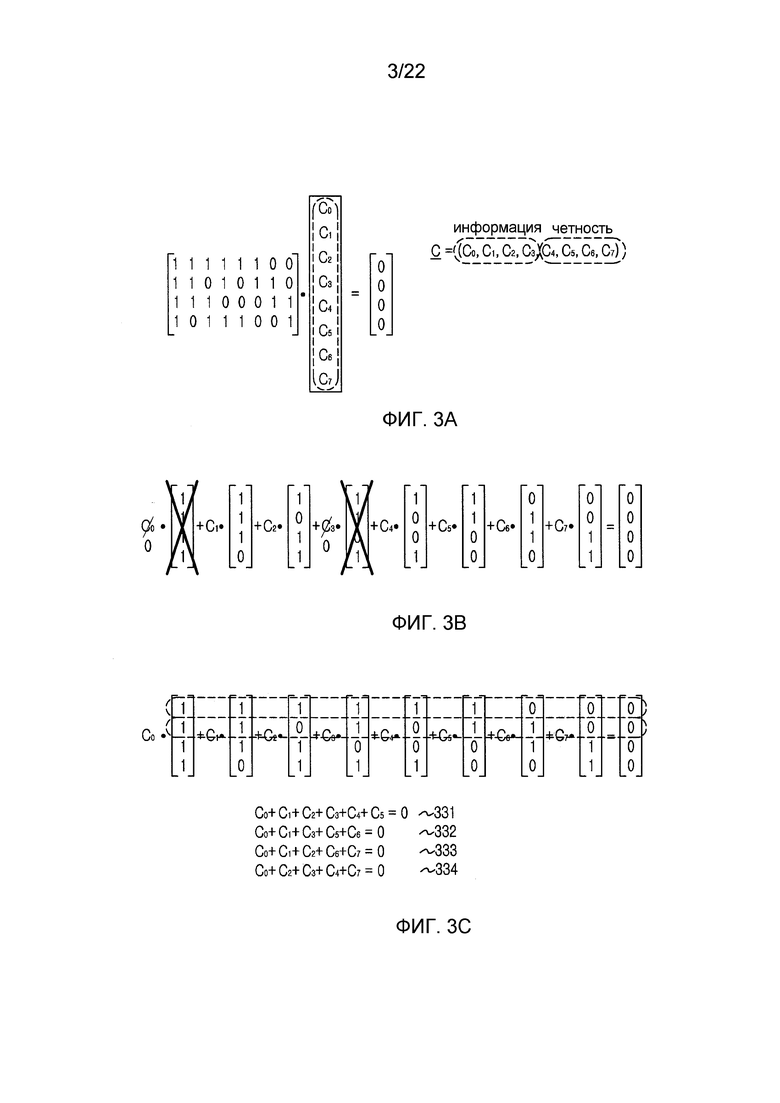

фиг. 3A-3C - виды, демонстрирующие уравнение, связывающее матрицу проверки четности и кодовое слово, в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

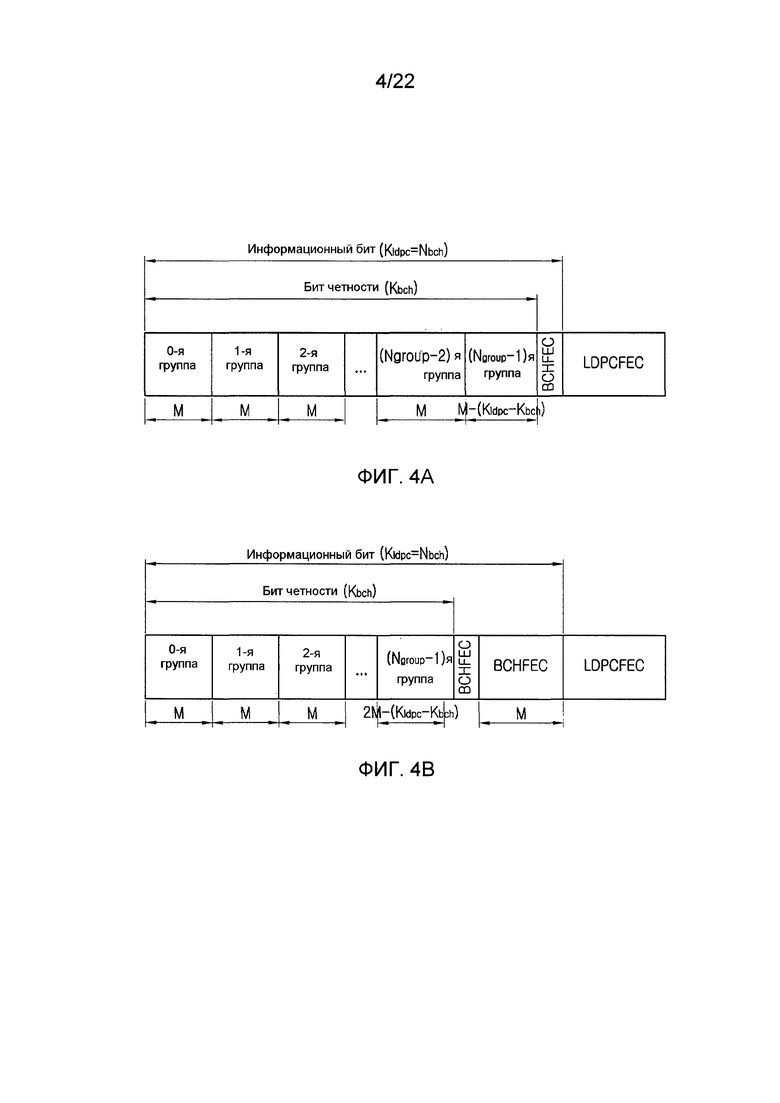

фиг. 4A и 4B - виды, демонстрирующие группирование информационных битов в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

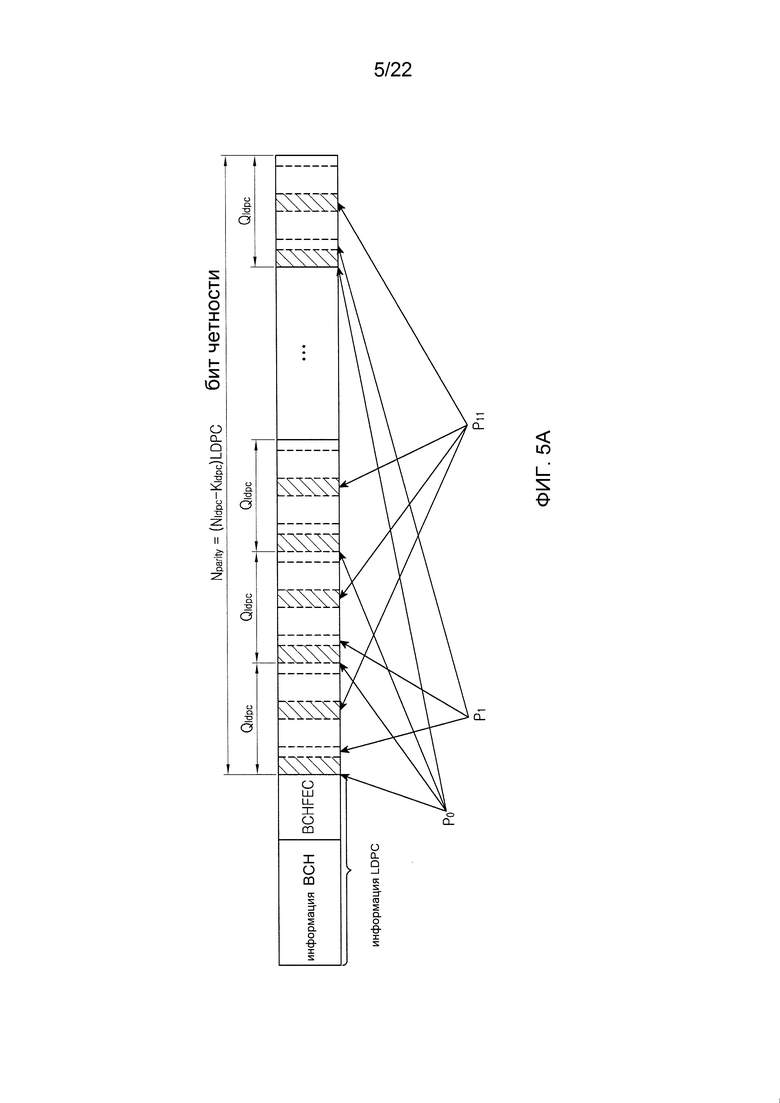

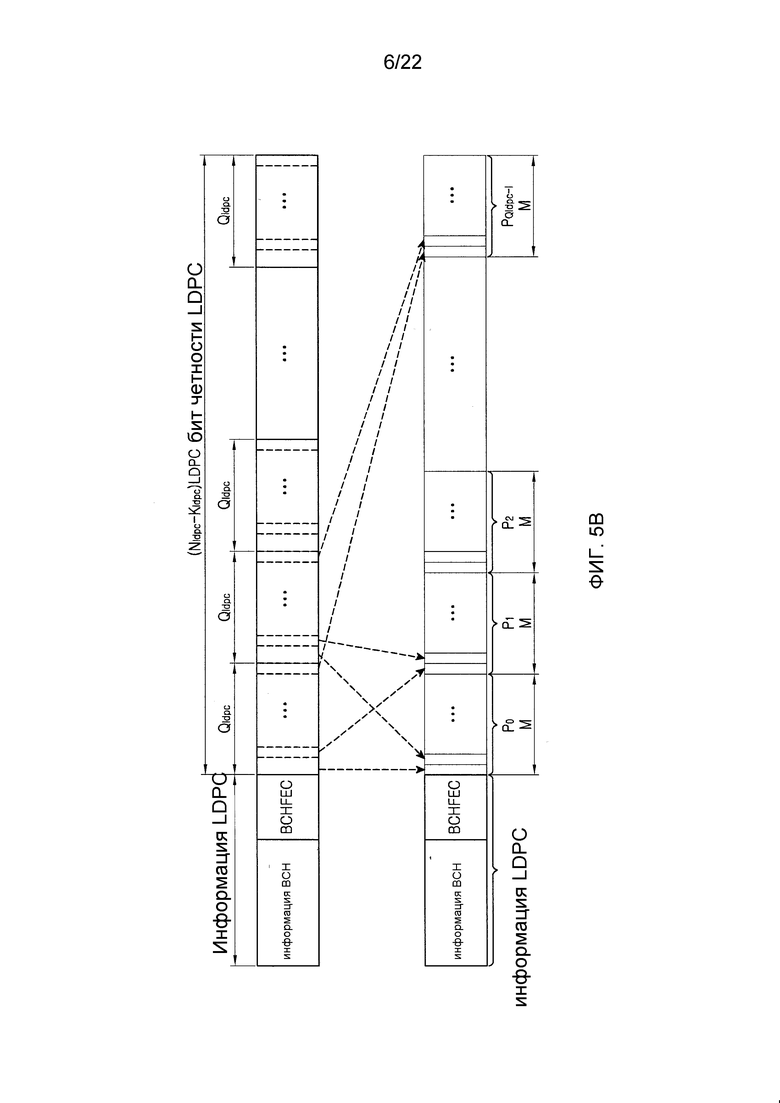

фиг. 5A и 5B - виды, демонстрирующие группирование битов четности в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

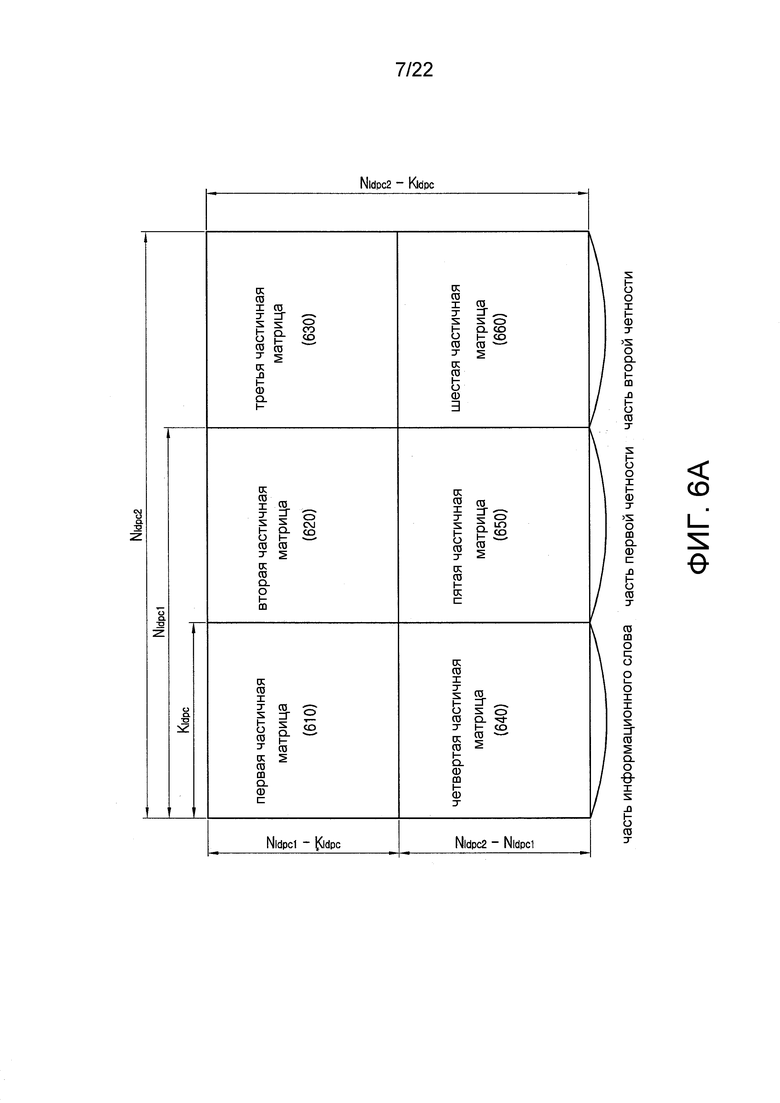

фиг. 6A и 6B - виды, демонстрирующие пример матрицы проверки четности, предусмотренной в системе связи/широковещания согласно другому варианту осуществления настоящего изобретения;

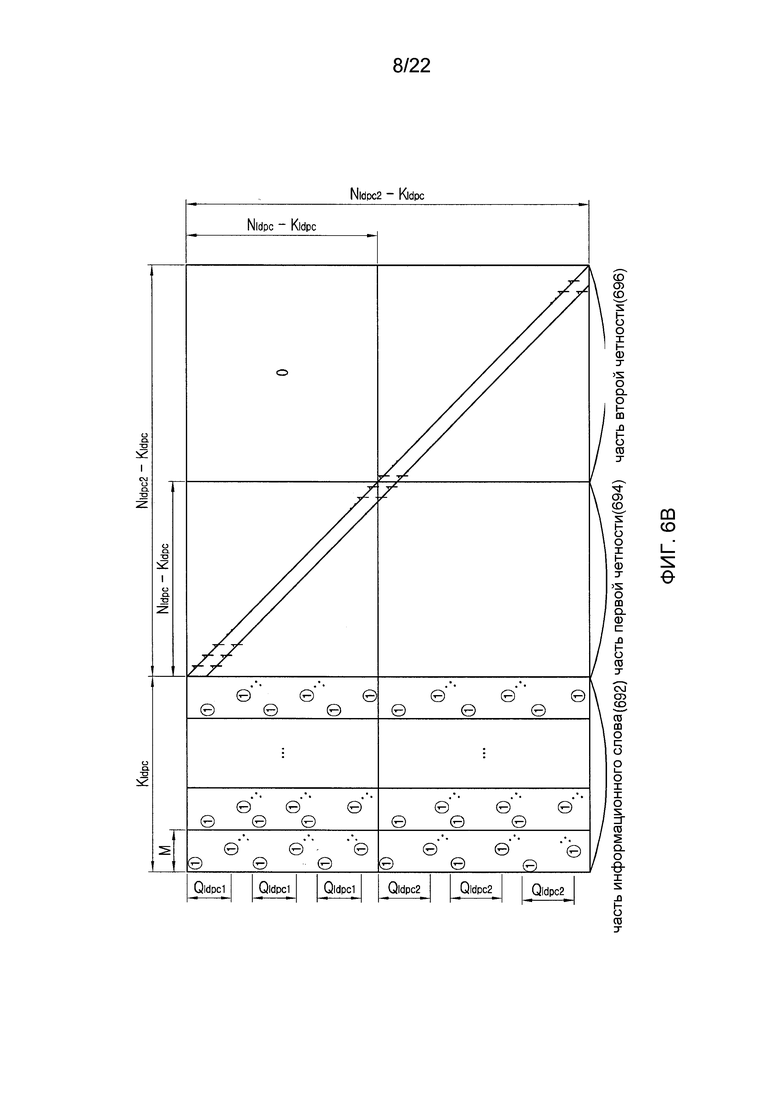

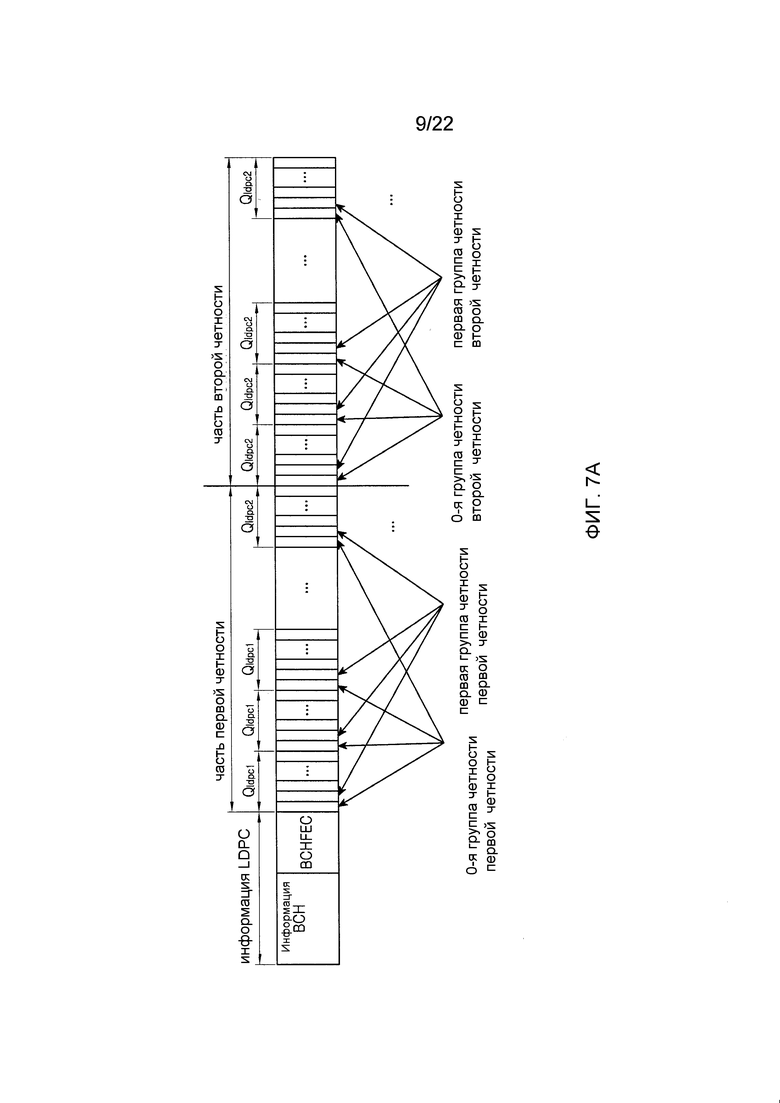

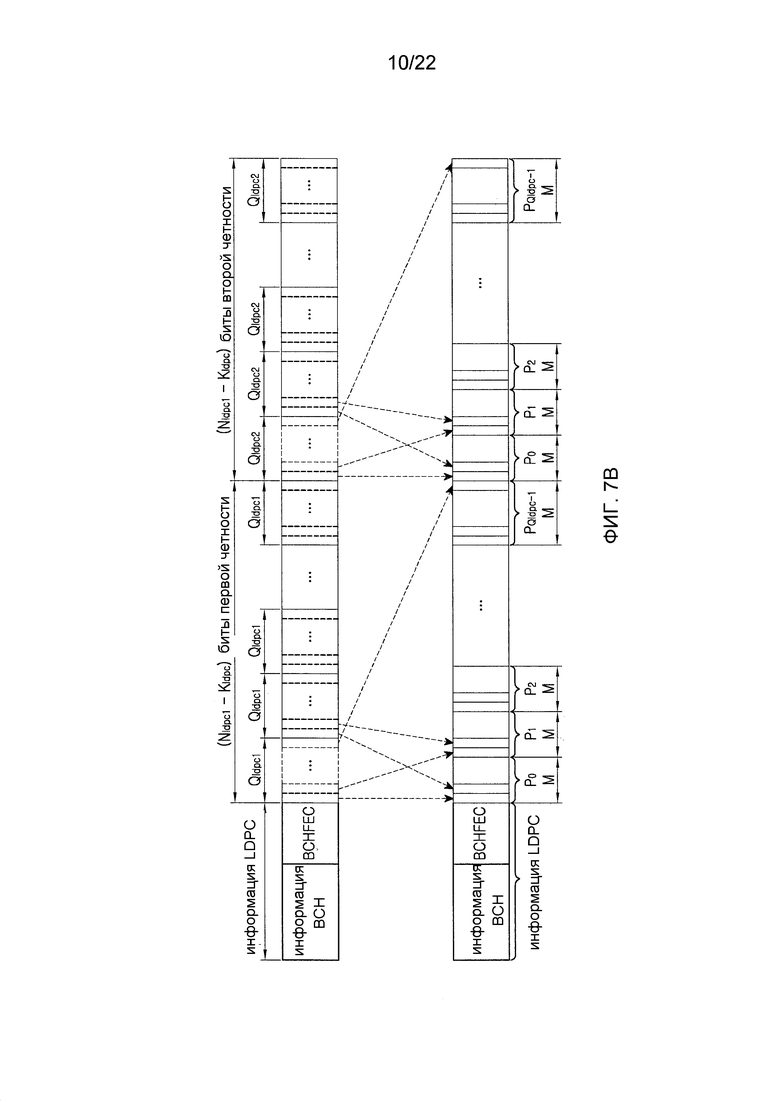

фиг. 7A и 7B - виды, демонстрирующие группирование битов четности в системе связи/широковещания согласно другому варианту осуществления настоящего изобретения;

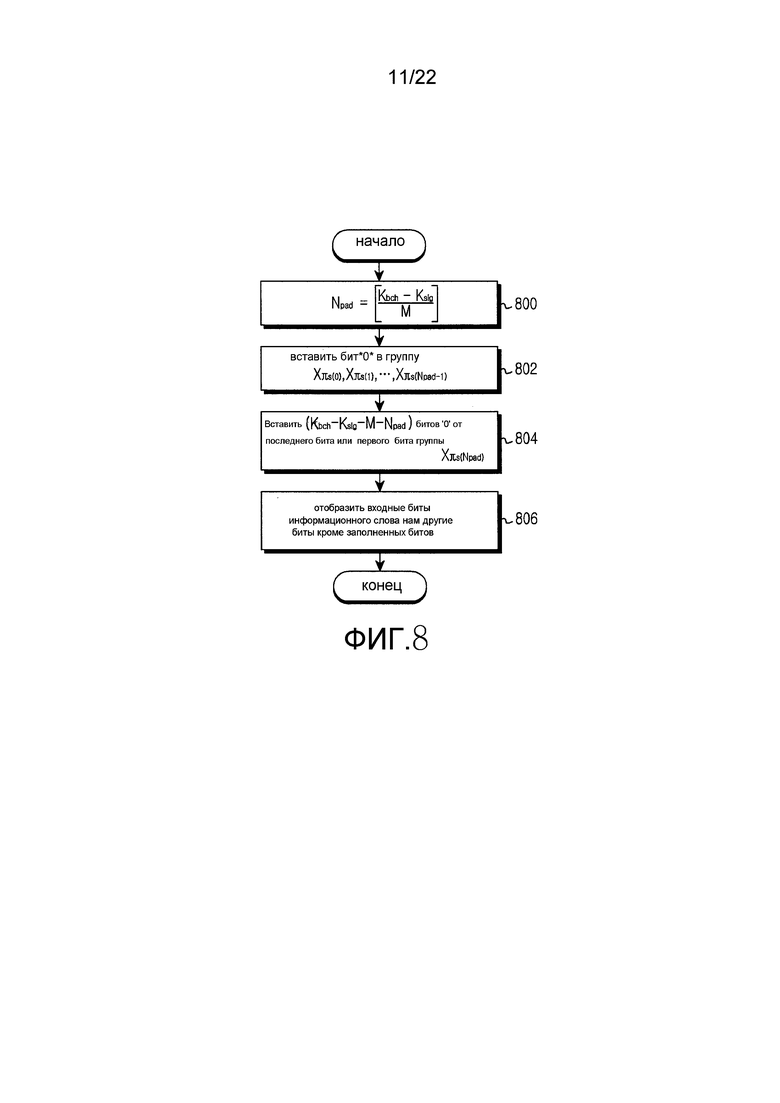

фиг. 8 - вид, демонстрирующий процедуру заполнения в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

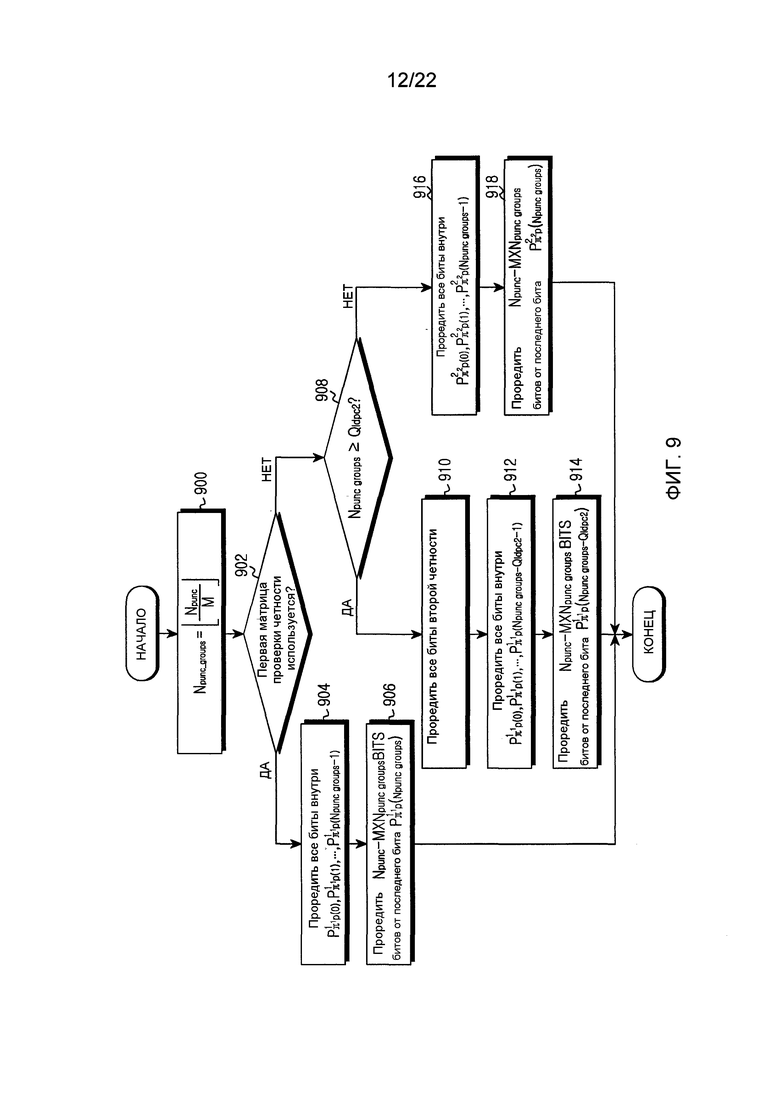

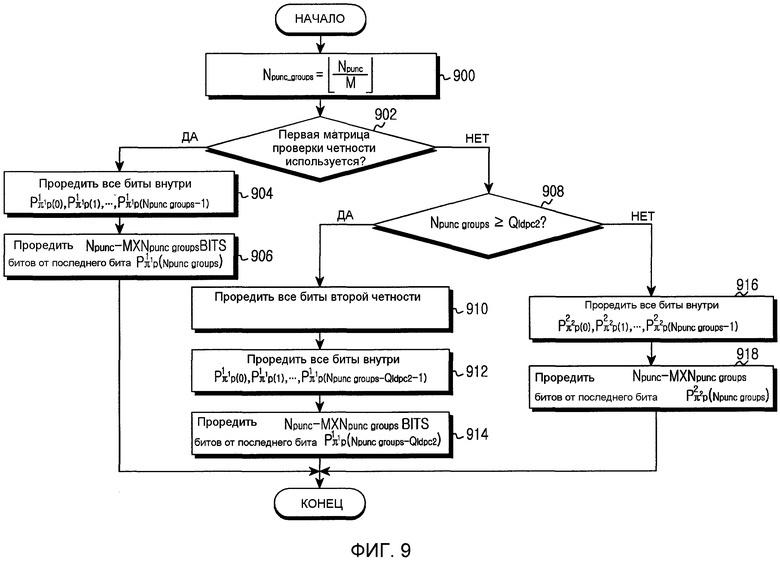

фиг. 9 - вид, демонстрирующий процедуру прореживания в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

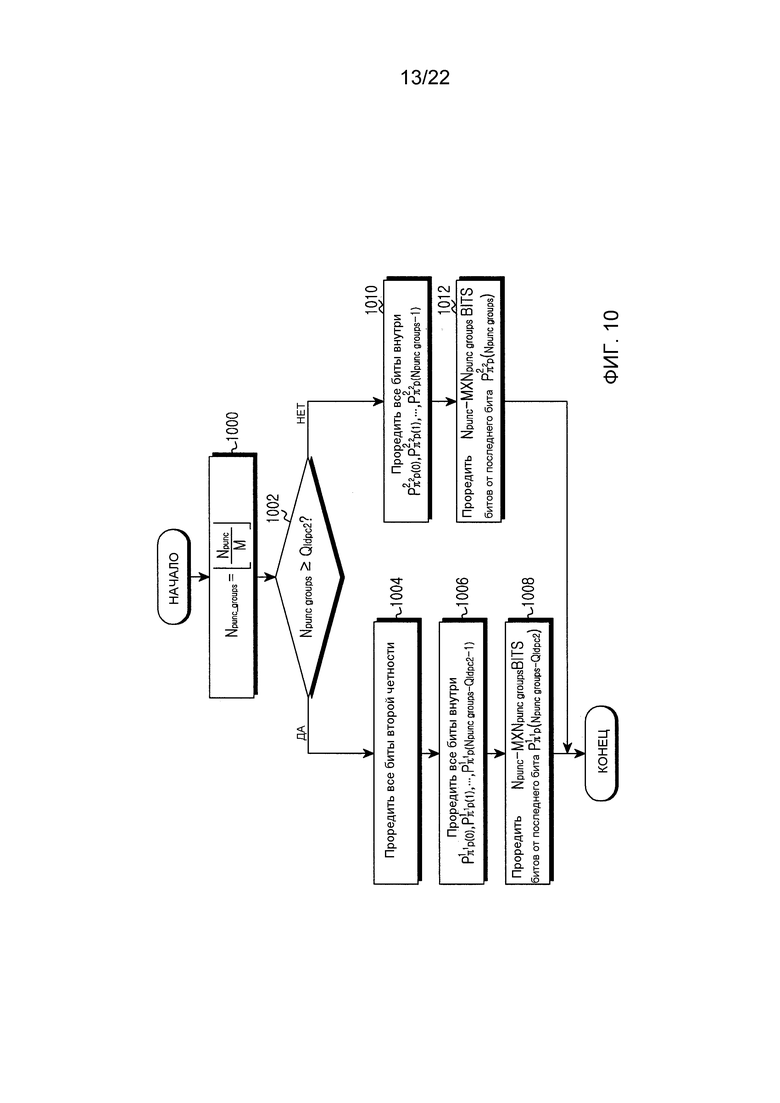

фиг. 10 - вид, демонстрирующий процедуру прореживания в системе связи/широковещания согласно другому варианту осуществления настоящего изобретения;

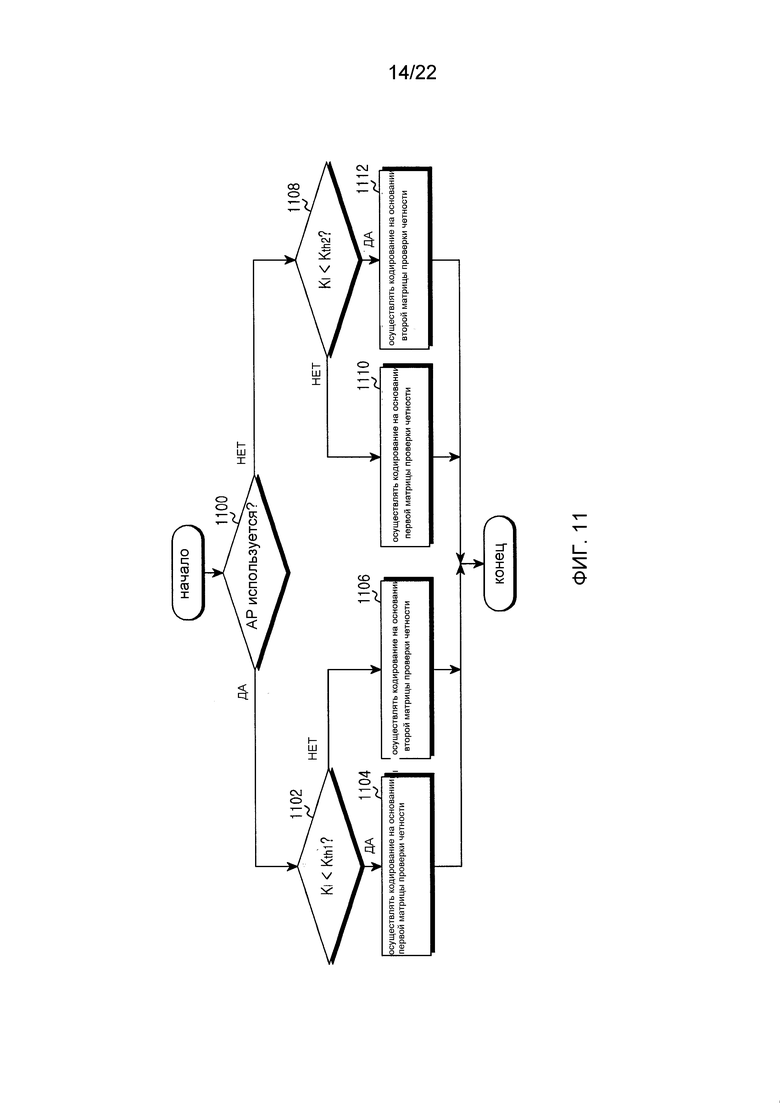

фиг. 11 - вид, демонстрирующий процедуру для определения формы матрицы проверки четности в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

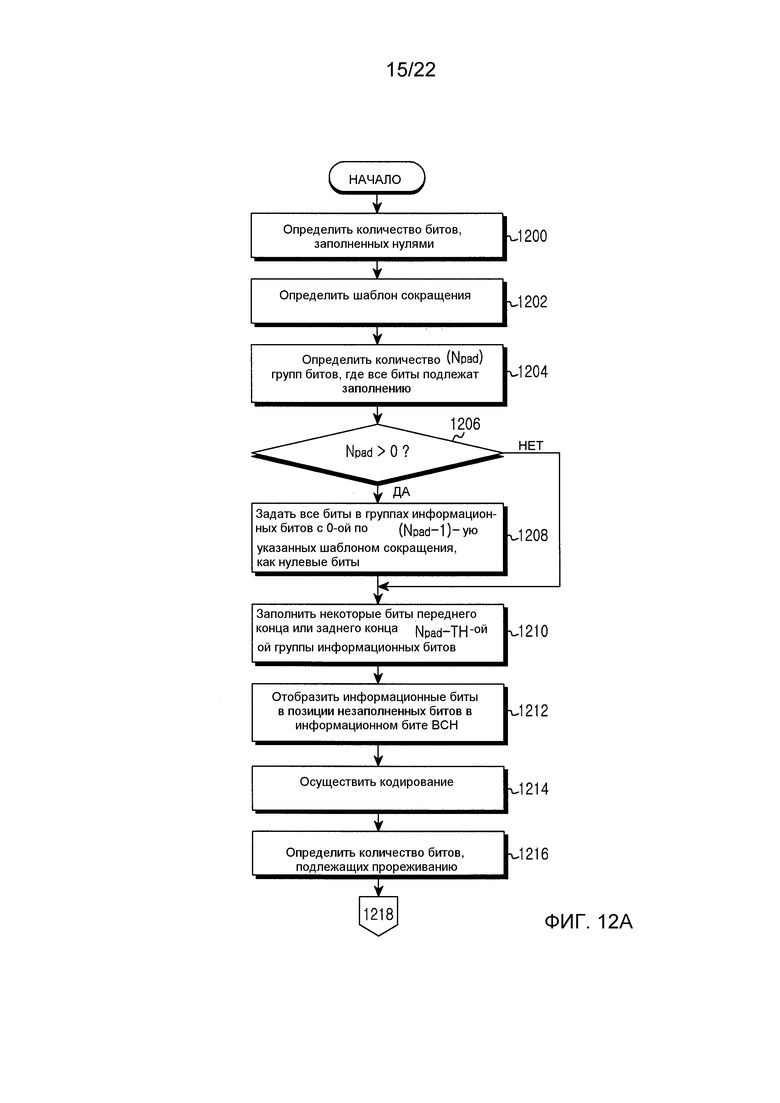

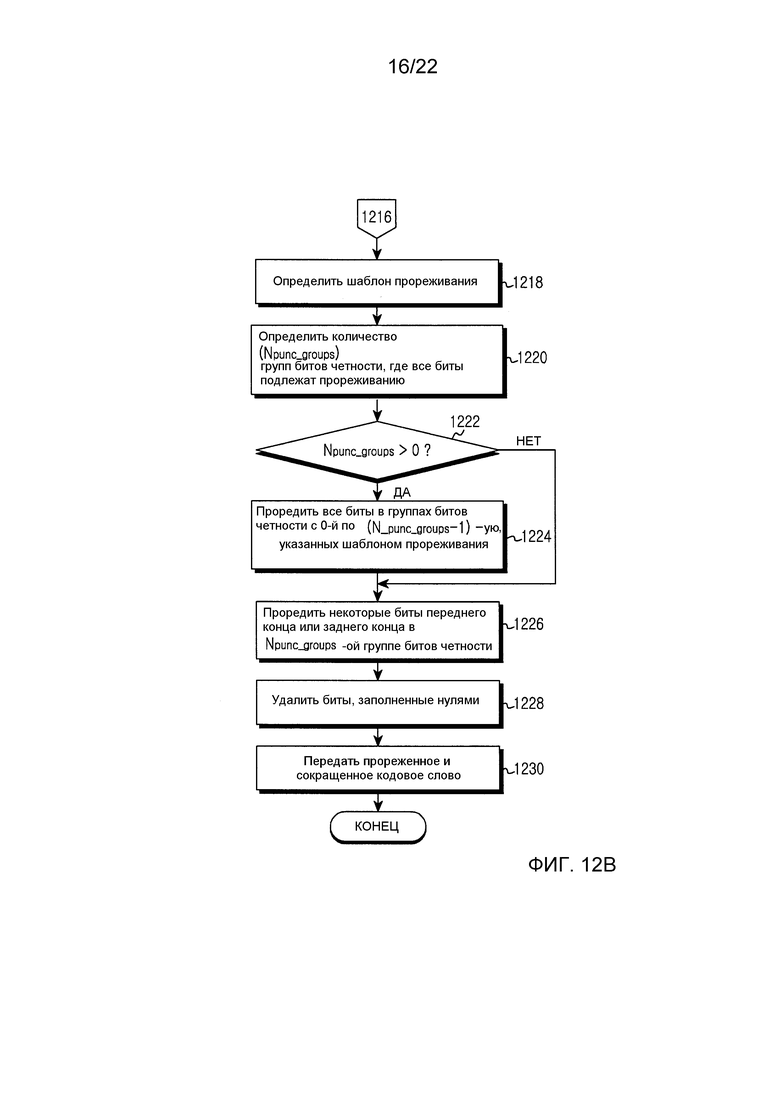

фиг. 12A и 12B - виды, демонстрирующие рабочую процедуру передающей стороны в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

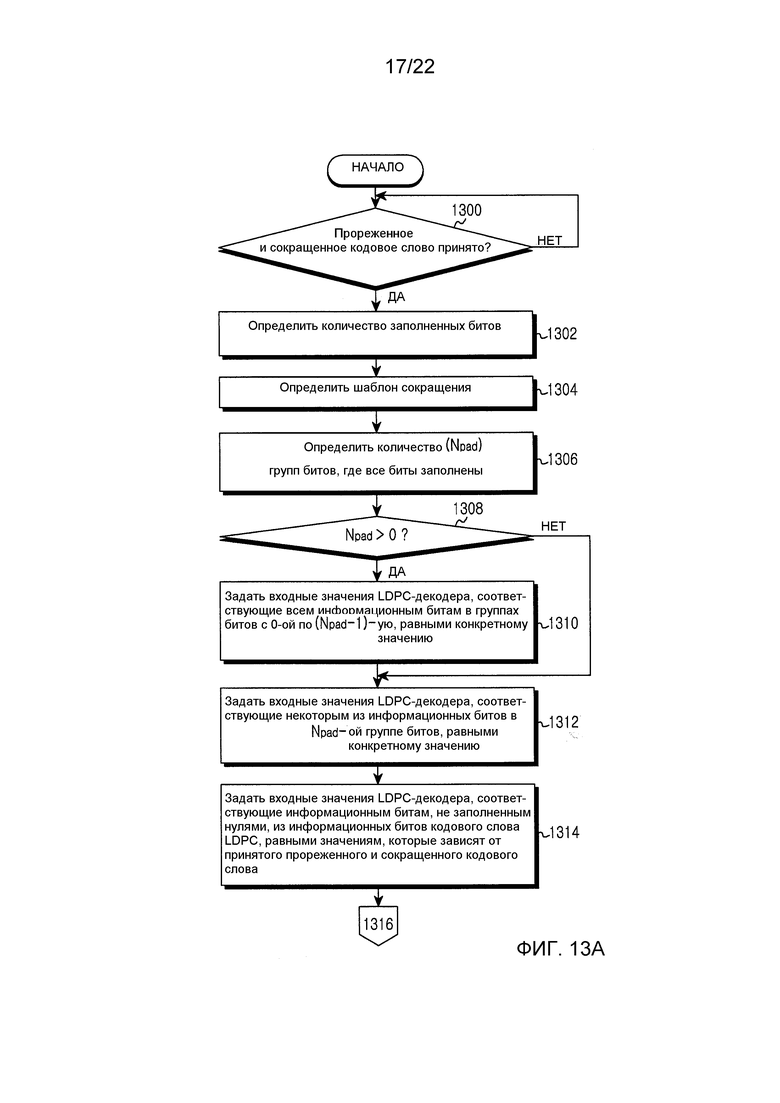

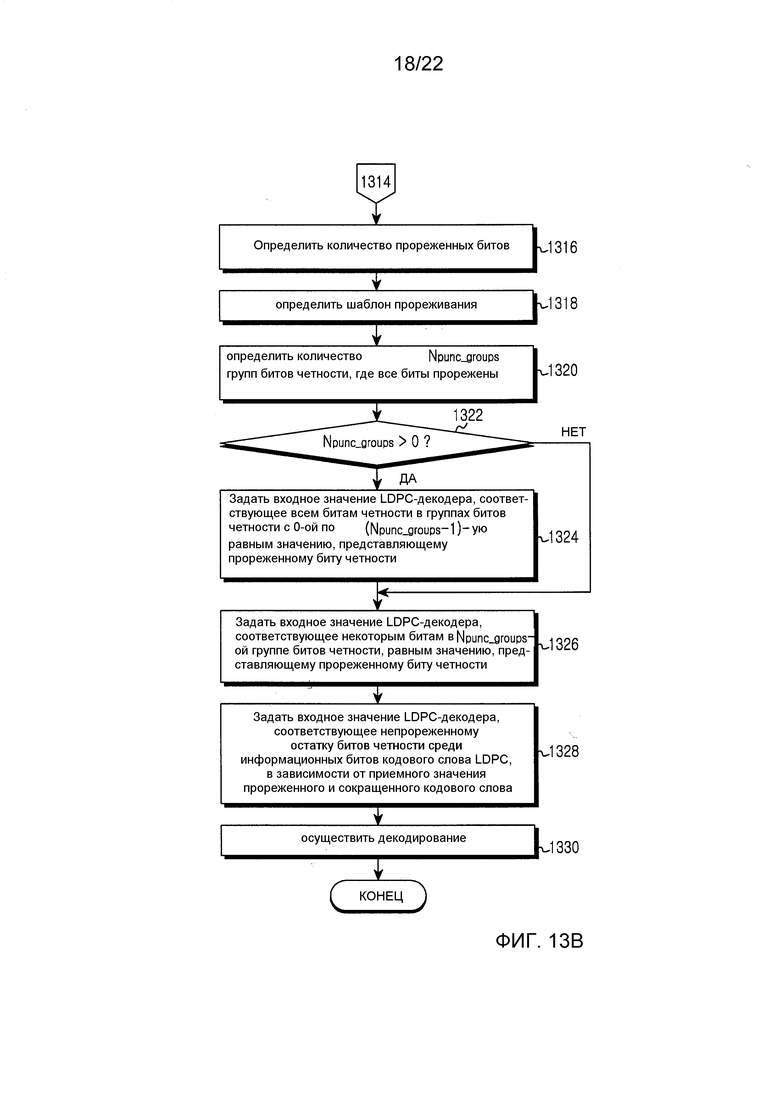

фиг. 13A и 13B - виды, демонстрирующие рабочую процедуру принимающей стороны в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

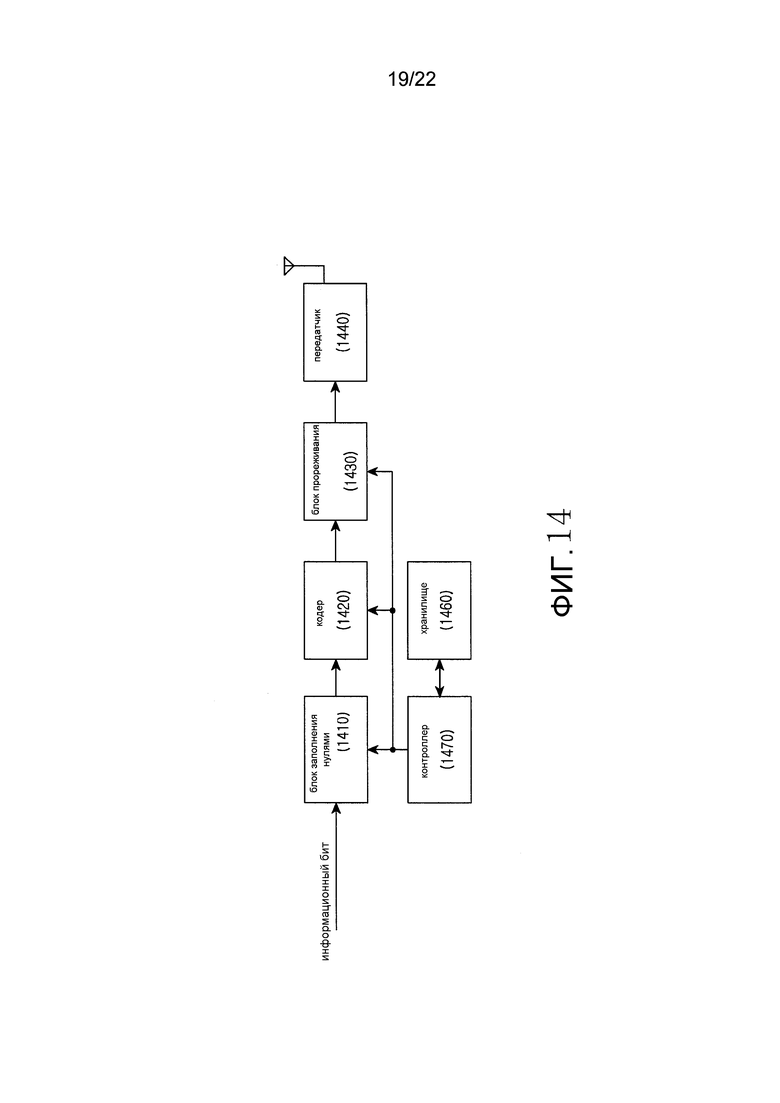

фиг. 14 - блок-схема, демонстрирующая передающую сторону в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

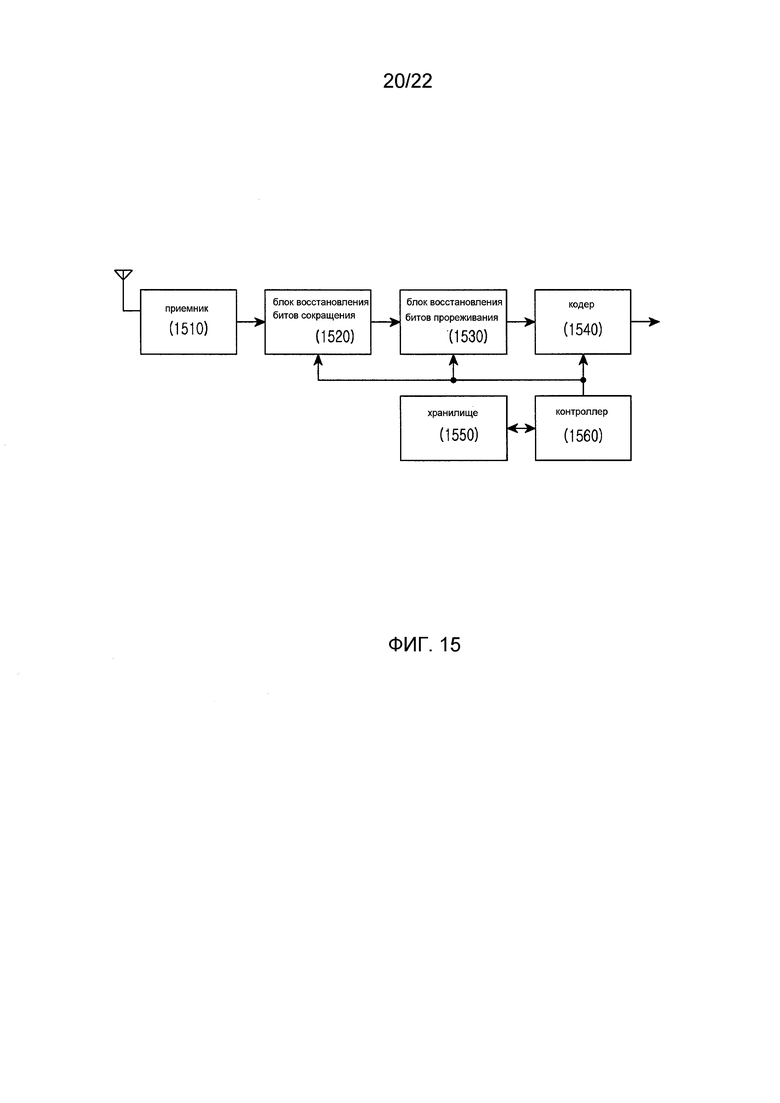

фиг. 15 - блок-схема, демонстрирующая принимающую сторону в системе связи/широковещания согласно варианту осуществления настоящего изобретения;

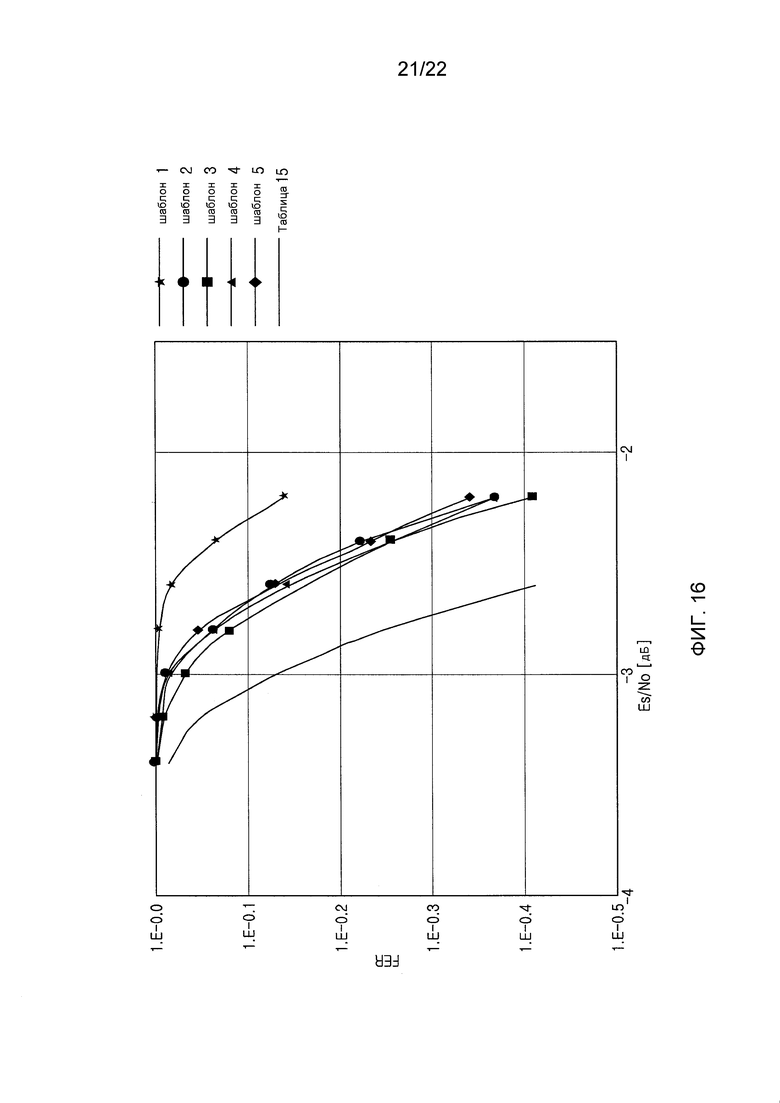

фиг. 16 - вид, демонстрирующий производительность системы связи/широковещания согласно варианту осуществления настоящего изобретения; и

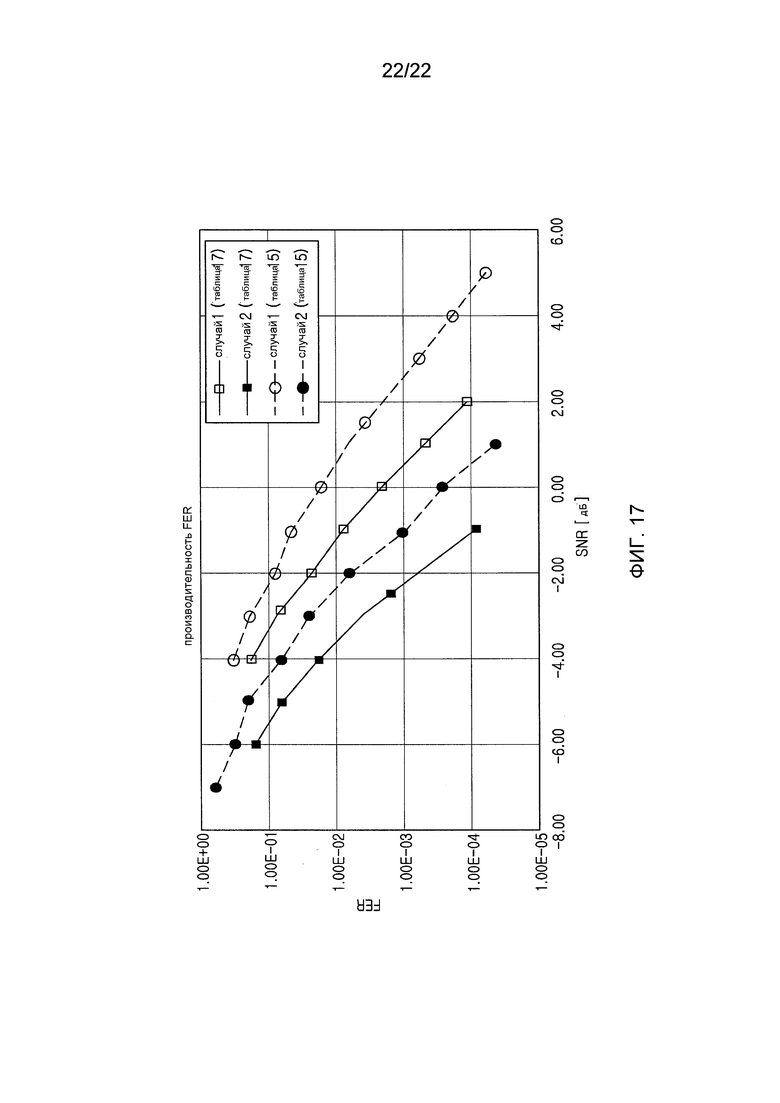

фиг. 17 - вид, демонстрирующий производительность системы связи/широковещания согласно варианту осуществления настоящего изобретения.

В чертежах, аналогичные ссылочные позиции обозначают аналогичные части, компоненты и структуры.

Подробное описание иллюстративных вариантов осуществления

Нижеследующее описание со ссылкой на прилагаемые чертежи призвано способствовать полному пониманию иллюстративных вариантов осуществления изобретения, заданных формулой изобретения и ее эквивалентами. Оно включает в себя различные конкретные детали, способствующие этому пониманию, но их следует рассматривать лишь как иллюстративные. Соответственно, специалисты в данной области техники могут предложить различные изменения и модификации описанных здесь вариантов осуществления, не выходя за рамки объема и сущности изобретения. Кроме того, описания общеизвестных функций и конструкций опущены для ясности и краткости.

Далее, в настоящем изобретении описана технология сокращения или прореживания некоторых битов кодового слова соответствующих коду LDPC, без снижения производительности в системе связи/широковещания.

В дальнейшем, в настоящем изобретении используются термины и названия, определенные согласно Digital Video Broadcasting the 2nd Generation Terrestrial (DVB-T2), который является одним из европейских стандартов цифрового вещания, и системе Digital Video Broadcasting Next Generation Handheld (DVB-NGH), которая в настоящее время проходит стандартизацию. Однако настоящее изобретение не ограничивается терминами и названиями и применимо к другим системам, осуществляющим кодирование и декодирование.

В настоящем изобретении рассматривается матрица проверки четности, структура которой представлена на фиг. 1. Матрица проверки четности, представленная на фиг. 1, имеет систематическую структуру, где кодовое слово включает в себя информационное слово как есть. В дальнейшем, хотя настоящее изобретение описано на основании матрицы проверки четности, показанной на фиг. 1, объем применения настоящего изобретения не ограничивается матрицей проверки четности, показанной на фиг. 1.

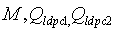

На фиг. 1,

Согласно фиг. 1, матрица проверки четности делится на частичную матрицу 110, соответствующую информационному слову, и частичную матрицу 120, соответствующую четности. Частичная матрица 110, соответствующая информационному слову, включает в себя

В частичной матрице 120, соответствующей четности, включающей в себя столбцы с

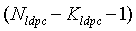

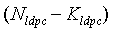

Согласно фиг. 1, матрица проверки четности, то есть структура частичной матрицы 110 информационного слова, включающая в себя столбцы с 0-го по (

где

Согласно уравнению (2), выясняется, что, когда известно только значение

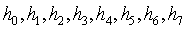

Согласно вышеозначенным правилам, степени всех столбцов, принадлежащих i-й группе столбцов, одинаковы и равны

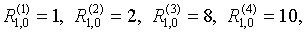

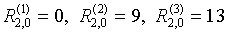

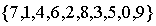

В порядке конкретного примера, в случае, когда

В уравнении (3),

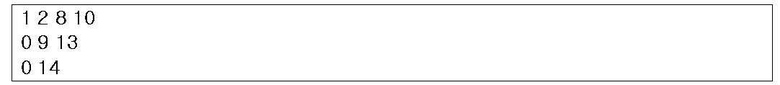

Последовательности позиций (вес-1) согласно уравнению (3), представляющие индекс строки, где 1 присутствует в 0-м столбце каждой группы столбцов, можно более кратко выразить в нижеприведенной таблице 1.

Таблица 1 представляет позицию (вес-1), другими словами, элемента имеющего значение 1. i-я последовательность позиций вес-1 выражается индексами строки, где вес-1 присутствует в 0-м столбце, принадлежащем i-й группе столбцов. Когда используется таблица 1, может генерироваться частичная матрица информационного слова размером 15×15 матрицы проверки четности размером 30x15. Кроме того, поскольку в отношении частичной матрицы четности размером 15×15 заранее определяется, что она имеет двухдиагональную структуру, матрица проверки четности размером 30×15 может генерироваться с использованием таблицы 1.

Помимо длины

Пример матрицы проверки четности, параметры которой указаны в таблице 2, приведен в таблице 3. Выражая матрицу проверки четности, индекс группы столбцов, указанный столбцом 'i' в нижеприведенной таблице 3, в общем случае, можно исключить.

Далее, в настоящем изобретении описан процесс кодирования кода LDPC с использованием матрицы проверки четности, имеющей структуру, показанную на фиг. 1. Для удобства описания, в настоящем изобретении, в порядке примера, описана матрица проверки четности, представленная в таблице 3. Как описано выше, процесс кодирования кода LDPC определяет кодовое слово C, удовлетворяющее уравнению связи, где произведение матрицы проверки четности и кодового слова равно 0. Существуют различные способы кодирования в отношении данной матрицы проверки четности, и описанный ниже процесс кодирования приведен исключительно в качестве примера.

Последовательность i-й строки таблицы 3 последовательно представляет информацию, касающуюся i-й группы столбцов. Таким образом, в порядке конкретного примера, настоящее изобретение поясняет процесс LDPC-кодирования с использованием матрицы проверки четности, имеющей структуру, показанную на фиг. 1 исходя из того, что

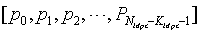

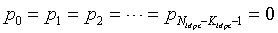

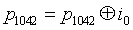

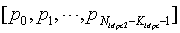

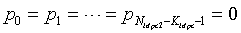

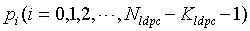

На этапе 1, кодер инициализирует биты четности. Таким образом,

На этапе 2, кодер накапливает 0-й информационный бит

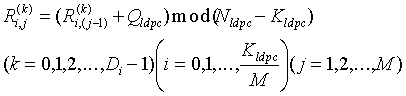

В уравнении (4),

На этапе 3, кодер накапливает 0-й информационный бит

где

В уравнении (5), значение адреса накопителя совпадает с индексом строки, где присутствует вес-1 m-го столбца матрицы проверки четности. Кроме того,

В уравнении (6),

На этапе 4, кодер накапливает 72-й информационный бит

где

На этапе 5, новая строка таблицы 3 используется для определения адреса бита четности в отношении каждой группы из 72 новых информационных битов. После осуществления вышеописанного процесса на всех информационных битах, последние биты четности определяются следующим образом.

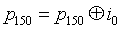

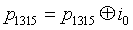

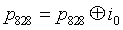

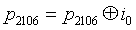

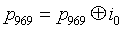

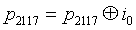

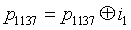

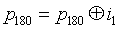

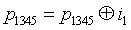

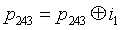

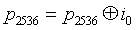

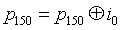

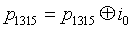

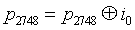

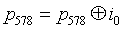

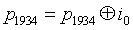

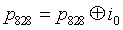

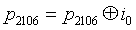

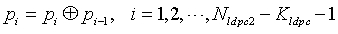

На этапе 6, осуществляется операция уравнения (8). При этом,

где

На этапе 7, кодер определяет окончательные значения

Как описано выше, столбец матрицы проверки четности, связанный с

На Фиг. 2 показана блок-схема, демонстрирующая передающую сторону в системе связи/широковещания согласно варианту осуществления настоящего изобретения.

Согласно фиг. 2, передающая сторона включает в себя контроллер 202, блок 204 заполнения нулями (0), кодер 206 Бозе-Чаудхури-Хоквенгема (BCH), LDPC-кодер 208 и блок 210 прореживания. Кодер может включать в себя BCH-кодер 206 и LDPC-кодер 208. Альтернативно, кодер может включать в себя блок 204 заполнения нулями, BCH-кодер 206, LDPC-кодер 208 и блок 210 прореживания.

Блок 204 заполнения нулями заполняет, по меньшей мере, один бит, имеющий значение 0, в информационных битах. Таким образом, блок 204 заполнения нулями согласуется по длине строки входных битов BCH-кодера 206 за счет заполнения бита, имеющего, по меньшей мере, одно нулевое значение, в входных информационных битах. Например, блок 204 заполнения нулями может определять позицию, по меньшей мере, одного нулевого бита и затем дополнительно осуществлять заполнение в информационных битах. В порядке другого примера, блок 204 заполнения нулями может заменять нулевые биты позиции ненулевого бита в строке нулевых битов длины строки входных битов BCH-кодера 206, полностью состоящей из нулевых битов, информационными битами. В частности, информационные биты

BCH-кодер 206 генерирует

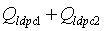

LDPC-кодер 208 генерирует кодовое слово LDPC

Блок 210 прореживания принимает кодовое слово LDPC

Контроллер 202 обеспечивает информацию для определения, по меньшей мере, одного из позиции и количества битов, подлежащих заполнению нулями, на блок 204 заполнения нулями, обеспечивает информацию, касающуюся, по меньшей мере, одного из количества и позиции битов четности BCH на BCH-кодер 206, обеспечивает скорость кодирования, длину кодового слова, матрицу проверки четности и т.д. на LDPC-кодер 208, и обеспечивает информацию для определения, по меньшей мере, одного из количества и позиции прореженных битов на блок 210 прореживания. В случае, когда блок 210 прореживания имеет функцию удаления нулей, контроллер 202 обеспечивает информацию для определения, по меньшей мере, одного из позиции и количества битов, подлежащих заполнению нулями, на блок 210 прореживания наподобие указания блоку 204 вставки нулей. Кроме того, в случае, когда работа блока 204 заполнения нулями, BCH-кодера 206 и блока 210 прореживания не требуется, контроллер 202 может предписывать блоку 204 заполнения нулями, BCH-кодеру 206 и блоку 210 прореживания не работать.

В вышеописанной конструкции, поскольку бит заполняется нулем блоком 204 заполнения нулями и затем бит, заполненный нулем, удаляется блоком 210 прореживания, биты, заполненные нулями, не передаются. Заполнение битов до кодирования и удаление заполненных битов после вышеописанного кодирования именуется сокращением. Таким образом, сокращение включает в себя заполнение битов нулями до кодирования и удаление битов, заполненных нулями.

В случае варианта осуществления, представленного на фиг. 2, выходной сигнал блока 204 заполнения нулями поступает на блок 206 BCH-кодирования. Однако, согласно другому варианту осуществления настоящего изобретения, BCH-кодер 206 может быть упразднен. Таким образом, система может не использовать код BCH. В этом случае, выходной сигнал блока 204 заполнения нулями может непосредственно вводиться в LDPC-кодер 208. Согласно еще одному варианту осуществления настоящего изобретения, позиции BCH-кодера 206 и блока 204 заполнения нулями могут меняться местами. Таким образом, первые информационные биты до заполнения могут вводиться в BCH-кодер 206, выходной сигнал BCH-кодера 206 может обеспечиваться на блок 204 заполнения нулями, и выходной сигнал блока 204 заполнения нулями может обеспечиваться на LDPC-кодер 208.

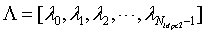

Передающая сторона согласно варианту осуществления настоящего изобретения заранее может сохранять информацию позиции битов, подлежащих сокращению или прореживанию, на основании заранее заданной последовательности индексов, или определять информацию позиции посредством операции согласно заранее заданному правилу, и затем выбирать позицию объектных битов сокращения или прореживания в информационных битах или кодовом слове LDPC на основании количества битов, подлежащих сокращению или прореживанию. В дальнейшем, для удобства описания, в настоящем изобретении последовательность сокращенных битов именуется 'шаблоном сокращения', а последовательность прореженных битов - 'шаблоном прореживания'. Шаблон сокращения и шаблон прореживания означают последовательность групп прореженных битов четности или последовательность групп сокращенных битов.

настоящее изобретение предусматривает определение шаблон сокращения и шаблон прореживания для применения сокращения и прореживания к строке входных битов переменной длины, и выбирает сокращенные/прореженные биты на основании количества сокращенных/прореженных битов и шаблона сокращения/прореживания.

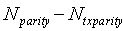

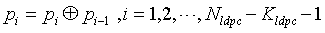

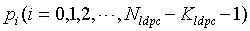

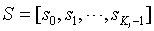

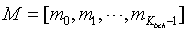

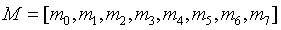

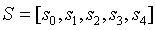

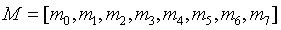

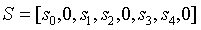

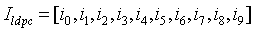

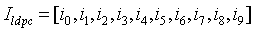

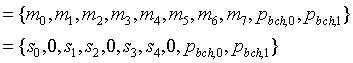

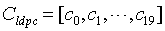

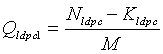

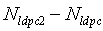

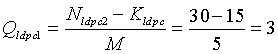

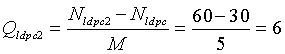

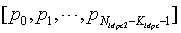

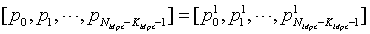

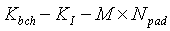

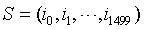

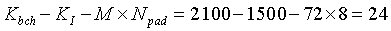

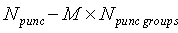

Конкретный пример сокращения и прореживания описан ниже. В случае, когда длина

Например, когда

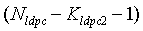

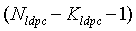

где

Строка

где

Строка

где

Как описано выше, в случае, когда сокращение и прореживание осуществляются на информационных битах

В частности, в случае осуществления LDPC-кодирования на основании матрицы проверки четности, имеющей структуру, показанную на фиг. 1, последовательность сокращенных и прореженных битов можно определить на групповой основе информационных битов и битов четности. Таким образом, настоящее изобретение предусматривает деление информационные биты и биты четности на множество групп битов, включающих в себя заранее определенное количество битов, определяет последовательность сокращенных и прореженных групп в отношении групп битов, и затем сокращает и прореживает биты на необходимое количество битов на основании шаблона сокращения и шаблона прореживания, определенных на основе групп битов.

В вышеописанном процессе сокращения и прореживания, заполнение осуществляется на входных битах BCH-кодера 206, и последовательность входных битов BCH-кодера 206 идентична последовательности входных битов LDPC-кодера 208. Кроме того, поскольку совместная производительность кода LDPC и кода BCH демонстрирует преобладание производительности кодового слова LDPC, последовательность сокращения можно определить на основании характеристики кодового слова LDPC. В частности, в случае, когда код LDPC основан на матрице проверки четности, имеющей структуру, показанную на фиг. 1 при определении последовательности сокращения, последовательность сокращения можно определить на основании группы информационных битов, соответствующей группе столбцов матрицы проверки четности.

Далее, в настоящем изобретении описано соотношение между матрицей проверки четности и сокращением/прореживанием, и подробно описан процесс для определения шаблона сокращения и шаблона прореживания для системы, осуществляющей LDPC-кодирование с использованием матрицы проверки четности, структура которой показана на фиг. 1.

Фиг. 3A-3C иллюстрируют уравнение, связывающее матрицу проверки четности и кодовое слово, в системе связи/широковещания согласно варианту осуществления настоящего изобретения.

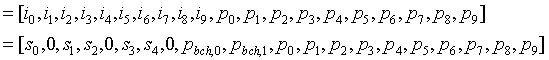

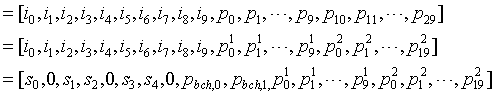

Фиг. 3A иллюстрирует соотношение между матрицей проверки четности и кодовым словом. Как описано выше, выполняется условие

В описанном ниже процессе сокращения, настоящее изобретение предусматривает задание последовательности позиций, где бит заполняется нулем, в качестве шаблона сокращения, заполнение бита нулем с последующим его кодированием, и удаление заполненных битов из кодового слова на основании шаблона сокращения. Однако, согласно другому варианту осуществления настоящего изобретения, шаблон сокращения можно использовать для определения последовательности позиций, где информационные биты, введенные в кодовое слово, вводятся, а не последовательности позиций, где бит заполняется нулем. Шаблон сокращения представляет последовательность позиций, где бит заполняется нулем. Таким образом, последовательность позиций, в которые отображаются информационные биты в кодовом слове, можно получить с использованием шаблона сокращения. Таким образом, при считывании шаблона сокращения в обратном порядке, получается последовательность позиций, куда отображаются информационные биты. Таким образом, процесс сокращения может осуществляться путем определения позиций, куда информационные биты, введенные в кодовое слово, отображаются в обратном порядке шаблона сокращения, отображения '0' в биты, в которые информационные биты не отображаются, и их кодирования, и затем удаления из кодового слова битов, в которые был отображен 0.

Кроме того, в описанном ниже процессе прореживания, настоящее изобретение предусматривает задание последовательности выбора прореженных битов в качестве шаблона прореживания и прореживание битов согласно шаблону прореживания. Однако, согласно другому варианту осуществления настоящего изобретения, шаблон прореживания можно использовать для определения последовательности битов, не подлежащих прореживанию, а не последовательности позиций битов, подлежащих прореживанию. Поскольку шаблон прореживания представляет последовательность прореженных битов, когда шаблон прореживания считывается в обратном порядке, получается последовательность непрореженных битов. Таким образом, процесс прореживания может осуществляться путем определения битов, не прореженных в обратном порядке шаблона прореживания, и прореживания остальных битов. В частности, в случае осуществления прореживания на фиксированной длине, а не на переменной длине, непрореженные биты можно определить на основании шаблона прореживания.

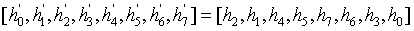

Кроме того, согласно фиг. 3C, произведение матрицы проверки четности

Тот факт, что позиция столбца матрицы проверки четности изменяется, просто эквивалентен тому факту, что позиция битов кодового слова изменяется. Поэтому, в случае, когда позиция столбца матрицы проверки четности изменяется, когда позиция сокращенных информационных битов и позиция прореженных битов четности изменяются по одному и тому же шаблону, можно гарантировать одинаковую производительность. В этом случае, набор кодовых слов не изменяется. Например, согласно фиг. 3B, предположим, что, когда столбцы матрицы проверки четности представляют собой

Как описано выше, в случае, когда длина

Далее, в настоящем изобретении описан процесс для определения последовательностей сокращения и прореживания на основе групп битов при допущении, что матрица проверки четности имеет структуру, показанную на фиг. 1, и подробно описаны последовательности сокращения и прореживания.

Прежде всего, последовательность сокращения для информационного бита определяется следующим образом.

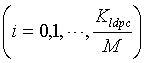

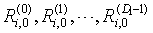

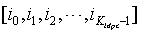

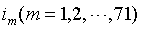

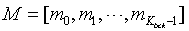

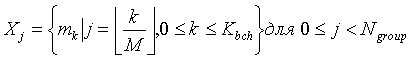

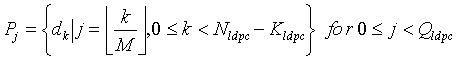

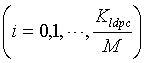

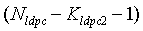

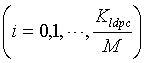

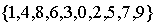

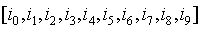

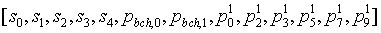

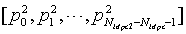

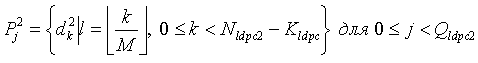

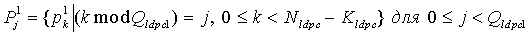

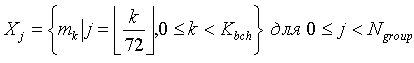

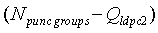

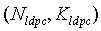

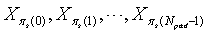

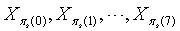

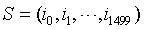

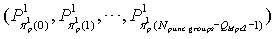

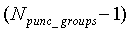

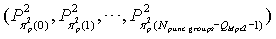

В отношении всех информационных битов BCH

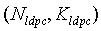

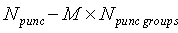

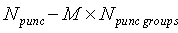

где

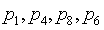

В случае конфигурирования групп битов согласно уравнению (12), группа битов задается согласно фиг. 4A и 4B. Согласно фиг. 4A и 4B, каждая группа битов включает в себя M битов, и последняя группа битов включает в себя

Настоящее изобретение предусматривает задание шаблона сокращения на основе групп битов. При этом, как описано выше, поскольку информационные биты BCH идентичны остальным битам, кроме бита четности кода BCH среди информационных битов LDPC, настоящее изобретение предусматривает определение последовательность сокращения с учетом информационных битов LDPC. При этом настоящее изобретение предусматривает определение последовательность сокращения на основании данной матрицы проверки четности. Процесс для определения последовательности сокращения на основании данной матрицы проверки четности описан ниже.

В матрице проверки четности структуры представленный на фиг. 1, частичная матрица 110 информационного слова может делиться на группы столбцов, состоящие из M последовательных столбцов. Поэтому информационные биты LDPC, соответствующие каждому столбцу в группе столбцов, состоящих из M битов, могут формироваться из группы информационных битов согласно уравнению (12).

Таким образом, 0-я группа битов, показанная на фиг. 4A, соответствует 0-й группе столбцов, показанной на фиг. 1. Кроме того, 0-я группа битов включает в себя, по меньшей мере, один бит, и каждый бит в 0-й группе битов, показанной на фиг. 4A, соответствует каждому столбцу в 0-й группе столбцов, показанной на фиг. 1. Кроме того, i-я группа битов, показанная на фиг. 4A, включает в себя биты, соответствующие столбцам в i-й группе столбцов, показанной на фиг. 1. Соответственно, шаблон сокращения можно определить путем определения последовательности группы столбцов для удаления на основе групп столбцов в матрице проверки четности. Другими словами, переключение с последовательности удаления группы столбцов на последовательность группы информационных битов, соответствующих каждой группе столбцов, может быть шаблоном сокращения.

Шаблон сокращения означает последовательность сокращенных битов или последовательность групп сокращенных битов. В случае, когда шаблон сокращения задается как последовательность групп битов, последовательность сокращенных битов в каждой группе сокращенных битов может задаваться по-разному. Поскольку биты, принадлежащие одной и той же группе, имеют одинаковую степень и одинаковую производительность цикла, можно получить одинаковую производительность в качестве способа определения последовательности сокращения на битовой основе.

Затем, последовательность прореживания в отношении бита четности определяется следующим образом.

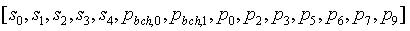

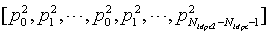

Фиг. 5A и 5B иллюстрируют группирование битов четности в системе связи/широковещания согласно варианту осуществления настоящего изобретения. Фиг. 5A и 5B предполагаются случай использования матрицы проверки четности структуры, представленной на фиг. 1.

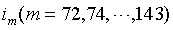

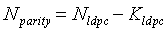

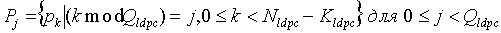

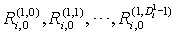

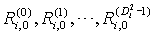

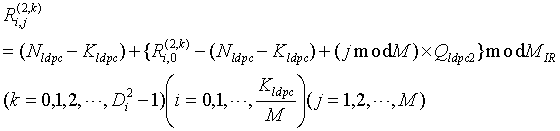

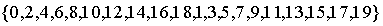

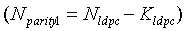

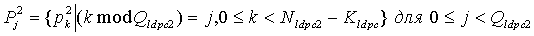

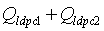

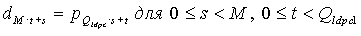

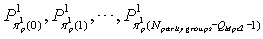

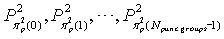

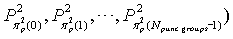

Согласно фиг. 5A, все биты четности LDPC

где

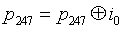

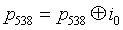

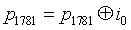

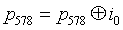

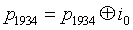

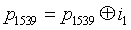

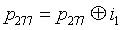

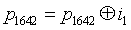

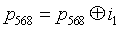

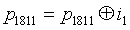

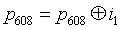

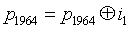

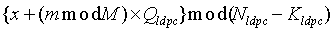

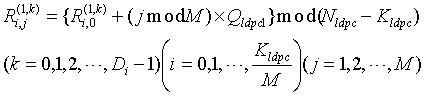

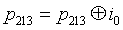

Согласно фиг. 5B, когда биты четности преобразуются согласно нижеследующему уравнению (14), группы битов четности, заданные уравнением (15), можно конфигурировать. Уравнение (14) вызывает эффект перемежения битов четности.

где

где

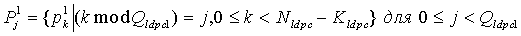

Биты четности, образующие j-ю группу битов четности

Поскольку биты в одной и той же группе битов четности имеют одинаковую степень и одинаковую характеристику цикла, когда шаблон прореживания определяется на групповой основе, гарантируется такая же производительность, как при нахождении оптимизированного шаблона прореживания на битовой основе. Таким образом, настоящее изобретение предусматривает определение шаблона прореживания на основе групп битов четности.

Фиг. 6A и 6B иллюстрируют пример матрицы проверки четности, предусмотренной в системе связи/широковещания согласно другому варианту осуществления настоящего изобретения.

Матрица проверки четности, показанная на фиг. 6A и 6B, является расширенной формой матрицы проверки четности, показанной на фиг. 1, которую можно использовать, когда настоящее изобретение призвано поддерживать кодовое слово, имеющее более низкую скорость кодирования, в то же время включающей в себя кодовое слово, кодированное на основании матрицы проверки четности, показанной на фиг. 1. Например, передающая сторона может осуществлять кодирование с использованием первой матрицы проверки четности, когда требуется высокая скорость кодирования, и может использовать расширенная вторая матрица проверки четности, когда требуется низкая скорость кодирования. В порядке другого примера, передающая сторона может осуществлять кодирование с использованием первой матрицы проверки четности при вводе информационных битов малой длины, и может осуществлять кодирование с использованием расширенной второй матрицы проверки четности, при вводе информационных битов большой длины.

Согласно фиг. 6A, матрица проверки четности включает в себя первую частичную матрицу 610, вторую частичную матрицу 620, третью частичную матрицу 630, четвертую частичную матрицу 640, пятую частичную матрицу 650 и шестую частичную матрицу 660. Первая частичная матрица 610 из шести частичных матриц идентична частичной матрице 110 информационного слова, показанной на фиг. 1, и вторая частичная матрица 620 идентична частичной матрице 120 четности, показанной на фиг. 1. Кроме того, матрица, состоящая из второй частичной матрицы 620, третьей частичной матрицы 630, пятой частичной матрицы 650 и шестой частичной матрицы 660 образует часть четности и имеет двухдиагональную структуру.

Для удобства описания, в настоящем изобретении матрица, сформированная из первой частичной матрицы 610 и второй частичной матрицы 620, называется 'первой матрицей проверки четности'. Структура 'первой матрицы проверки четности' идентична структуре матрицы проверки четности, представленной на фиг. 1. Кроме того, в настоящем изобретении матрица, сформированная из первой частичной матрицы 610, второй частичной матрицы 620, третьей частичной матрицы 630, четвертой частичной матрицы 640, пятой частичной матрицы 650 и шестой частичной матрицы 660, называется 'второй матрицей проверки четности'. Таким образом, из частичных матриц, представленных на фиг. 6A, первая частичная матрица 610 и вторая частичная матрица 620 включены в первую матрицу проверки четности и вторую матрицу проверки четности, но третья частичная матрица 630, четвертая частичная матрица 640, пятая частичная матрица 650 и шестая частичная матрица 660 включены исключительно во вторую матрицу проверки четности.

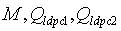

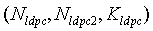

Матрица проверки четности, представленная на фиг. 6A конкретно описана ниже. На фиг. 6A,

Первая частичная матрица 610 и четвертая частичная матрица 640, соответствующие информационному слову, включают в себя

Фиг. 6B более подробно иллюстрирует структуру матрицы проверки четности. В матрице, сформированной из второй частичной матрицы 620, третьей частичной матрицы 630, пятой частичной матрицы 650 и шестой частичной матрицы 660, соответствующих 'второй части четности', включающей в себя столбцы с

Структура частичной матрицы, включающая в себя первую частичную матрицу 610, соответствующую информационному слову в матрице проверки четности, то есть частичную матрицу, включающую в себя столбцы с 0-го по

Кроме того, структура частичной матрицы, включающая в себя четвертую частичную матрицу 640, соответствующую информационному слову в матрице проверки четности, то есть частичную матрицу, включающую в себя столбцы с 0-го по

Таким образом, форма четвертой частичной матрицы 640 аналогична форме первой частичной матрицы 610, и значение

Хотя матрица проверки четности описана со ссылкой на фиг. 6A и 6B, матрица проверки четности, показанная на фиг. 6A и 6B, является примером матрицы проверки четности, к которой применимо настоящее изобретение, и объем настоящего изобретения не ограничивается этим.

Как описано выше, структура первой частичной матрицы 610, соответствующей информационному слову в матрице проверки четности, то есть частичной матрице, включающей в себя столбцы с 0-го по

где

Как описано выше, структура частичной матрицы, включающая в себя четвертую частичную матрицу 640, соответствующую информационному слову в матрице проверки четности, то есть частичную матрицу, включающую в себя столбцы с 0-го по

где

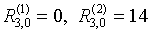

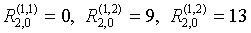

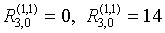

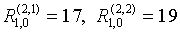

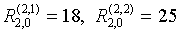

Согласно правилам, код LDPC, хранящий информацию, касающуюся матрицы проверки четности, можно кратко описать следующим образом. В порядке конкретного примера, в случае, когда

где

Информация позиции строки, где вес-1 располагается в 0-м столбце трех групп столбцов четвертой частичной матрицы 640, можно выразить в виде последовательностей, подчиняющихся уравнению (19). Последовательности, подчиняющиеся уравнению (19) можно именовать 'последовательностью позиций вес-1'.

где

Последовательности позиций вес-1 согласно уравнению (19), представляющие индекс строки, где 1 располагается в 0-м столбце каждой группы столбцов, можно выразить более кратко в нижеприведенной таблице 4.

В таблице 4 указана позиция элемента, имеющего вес-1, то есть значение 1 в матрице проверки четности. i-я последовательность позиций вес-1 выражается индексами строки, где вес-1 присутствует в 0-м столбце, принадлежащем i-й группе столбцов. Информацию, связанную с позицией 1, принадлежащей четвертой частичной матрице 740, можно выразить в виде независимой таблицы. Таким образом, как показано в таблице 5 и фиг. 5B, информационное слово в отношении вес-1, дополнительно необходимого во второй матрице проверки четности информационного слова для вес-1 в отношении первой матрицы проверки четности, можно выразить отдельно.

В отношении длины

Вариант осуществления, представляющий позицию вес-1 матрицы проверки четности можно выразить согласно нижеследующей таблице 8 с использованием матрицы проверки четности, имеющей параметры таблицы 7 и имеющей структуру, представленную на фиг. 6A и 6B, и выражающую индекс строки вес-1 в 0-м столбце каждой группы столбцов, как описано выше. В выражении матрицы проверки четности, индекс группы столбцов, обозначенный 'i' в таблице 8, в общем случае, можно исключить.

Числа, представленные в таблице 8, включают в себя числа, выражающие позицию вес-1 матрицы проверки четности структуры, представленной на фиг. 1, представленной в таблице 2. Как описано выше, таблица 8 также может отдельно выражать информацию вес-1 в отношении первой матрицы проверки четности и информацию вес-1 в отношении второй матрицы проверки четности.

Далее, в настоящем изобретении описан процесс кодирования на основании матрицы проверки четности, форма которой представлена на фиг. 6A и 6B. В дальнейшем, для удобства описания, в настоящем изобретении приведено описание исходя из предположения случая выражения информации, касающейся матрицы проверки четности, форма которой представлена на фиг. 6A и 6B, и индекса строки, где вес-1 присутствует в 0-м столбце каждой группы столбцов, согласно таблице 8. Таким образом, количество

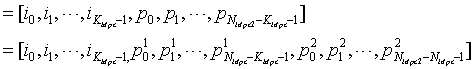

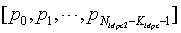

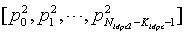

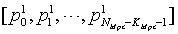

Кодовое слово можно выразить уравнением (20).

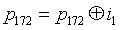

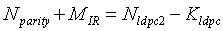

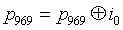

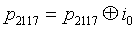

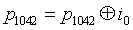

В уравнении (20) биты четности

Далее в настоящем изобретении описано процесс для приема информационных битов

На этапе 1, кодер инициализирует все биты четности равными 0 согласно нижеследующему уравнению (21).

где

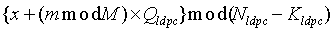

На этапе 2, кодер накапливает 0-й информационный бит

где

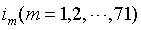

На этапе 3, в отношении остальных M-1(=7) информационных битов

где

где

В уравнении (23) и уравнении (24),

На этапе 4, в отношении каждой группы из 72 информационных битов, новая строка адресных таблиц используется для определения адреса бита четности.

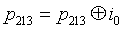

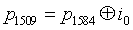

На этапе 5, после осуществления вышеупомянутого процесса на всех информационных битах, последние биты четности определяются следующим образом. Осуществляется операция согласно уравнению (25). При этом,

где

Кодер определяет окончательные значения

Как описано выше, столбец матрицы проверки четности, связанный с

Как описано выше, кодирование может осуществляться на основании матрицы проверки четности, форма которой представлена на фиг. 6A и 6B. Как описано выше, матрица проверки четности, представленная на фиг. 6A и 6B, делится на часть информационного слова и часть четности (включены первая часть четности и вторая часть четности), причем часть информационного слова может состоять из множества групп столбцов, и информация, где присутствует вес-1 части информационного слова матрицы проверки четности, можно выразить на основании значения индекса строки где присутствует вес-1 0-го столбца каждой группы столбцов. Кроме того, адрес бита четности выражается на основании значения индекса строки, где присутствует вес-1 0-го столбца каждой группы столбцов, и используется в ходе процесса кодирования. Кроме того, в случае, когда требуются только биты первой четности, кодирование может осуществляться на основании только первого участка матрицы проверки четности в матрице проверки четности, имеющей структуру, показанную на фиг. 1, или матрице проверки четности, показанной на фиг. 6A и 6B, и в случае, когда требуются и бит первой четности, и бит второй четности, кодирование может осуществляться на основании второй матрицы проверки четности, показанной на фиг. 6A и 6B. Процесс для осуществления кодирования на основании только первого участка матрицы проверки четности и процесс для осуществления кодирования на основании только второго участка матрицы проверки четности идентичны тем, которые не осуществляют кодирование по адресу бита четности, превышающему

Сокращение и прореживание, когда кодирование осуществляется на основании матрицы проверки четности, форма которой представлена на фиг. 6A и 6B, описаны ниже со ссылкой на фиг. 2.

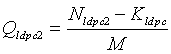

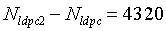

В случае, когда длина

Строка выходных битов BCH-кодера 206, показанного на фиг. 2, такая же, как описано выше. Строка

где

Столбец

где

В частности, в случае осуществления LDPC-кодирования на основании матрицы проверки четности структуры, представленной на фиг. 6A и 6B, последовательность сокращенных и прореженных битов можно определить на основе групп информационных битов. Таким образом, настоящее изобретение предусматривает деление информационных битов и битов четности, образующих кодовое слово, на множество групп информационных битов, включающих в себя заранее определенное количество битов, и определение последовательности сокращенных и прореженных групп в отношении групп информационных битов к группам битов четности, с последующим сокращением и прореживанием битов на необходимое количество на основании шаблона сокращения и шаблона прореживания, определенных на групповой основе. Кроме того, настоящее изобретение предусматривает различение между битами первой четности и битами второй четности для определения шаблона прореживания и прореживание битов второй четности с приоритетом при осуществлении прореживания.

Затем, последовательность прореживания для бита четности определяется следующим образом.

Фиг. 7A и 7B иллюстрируют группирование битов четности в системе связи/широковещания согласно другому варианту осуществления настоящего изобретения. В частности, фиг. 7A и 7B иллюстрируют случай использования матрицы проверки четности, имеющей структуру матрицы проверки четности, показанной на фиг. 6.

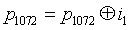

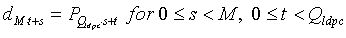

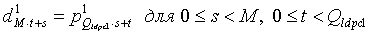

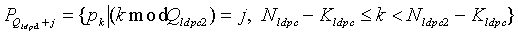

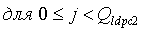

Согласно фиг. 7A, биты четности

где

'Биты второй четности'

где

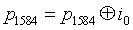

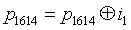

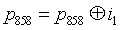

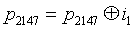

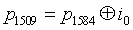

Согласно фиг. 7B, когда 'биты первой четности' преобразуются согласно нижеследующему уравнению (30), можно конфигурировать группы битов первой четности, заданные уравнением (31). Уравнение (30) вызывает эффект перемежения битов четности.

где

где

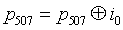

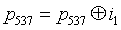

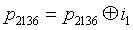

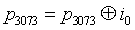

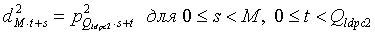

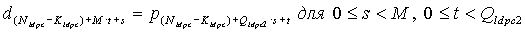

Согласно фиг. 7B, когда 'биты второй четности' преобразуются согласно нижеследующему уравнению (32), можно конфигурировать группы битов второй четности, заданные уравнением (33). Уравнение (32) вызывает эффект перемежения битов четности.

где

где

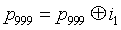

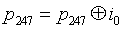

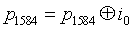

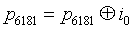

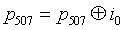

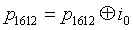

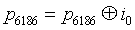

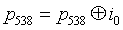

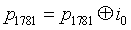

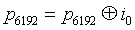

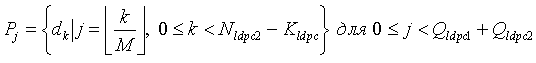

Согласно вышесказанному, биты четности

где

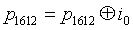

Согласно фиг. 7B, когда 'биты четности' преобразуются согласно уравнению (35), можно конфигурировать группы битов четности, заданные уравнением (36). Уравнение (35) вызывает эффект перемежения битов четности.

где

где

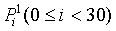

В уравнениях (28) и (31), биты четности, образующие j-ю группу битов первой четности

Поскольку биты в одной и той же группе битов первой четности до группы битов второй четности имеют одинаковую степень и одинаковую характеристику цикла, когда шаблон прореживания определяется на групповой основе, гарантируется такая же производительность, как при нахождении оптимизированного шаблона прореживания на битовой основе. Таким образом, настоящее изобретение предусматривает определение шаблона прореживания на основе групп битов четности.

Шаблон сокращения и шаблон прореживания согласно варианту осуществления настоящего изобретения можно определить согласно нижеследующим правилам.

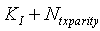

[Правило 1] В отношении кода данной длины

[Правило 2] Задаются шаблон сокращения и шаблон прореживания изменяющиеся на основании схемы модуляции.

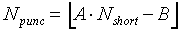

[Правило 3] Задаются другой шаблон сокращения и другой шаблон прореживания, изменяющиеся на основании отношения сокращения и прореживания. Например, соотношение между количеством сокращенных битов и количеством прореженных битов можно применять согласно уравнению (37). В этом случае, отношение сокращения и прореживания определяется на основании постоянной A и постоянной B.

где

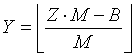

Согласно уравнению (37), количество

[Правило 4] Форма матрицы проверки четности, имеющей структуру, показанную на фиг. 6B, имеет основное допущение прореживания битов второй четности в первую очередь. Таким образом, предпочтительно определять шаблон прореживания для битов первой четности на основании первой матрицы проверки четности в первую очередь в структуре, показанной на фиг. 6B, и затем определять шаблон прореживания для битов второй четности на основании второй матрицы проверки четности.

В дальнейшем, настоящее изобретение подробно описан процесс для определения шаблона сокращения и шаблона прореживания.

[Этап 1] Настоящее изобретение предусматривает деление битов кодового слова LDPC на группы информационных битов, включающие в себя M битов, и группы битов четности, включающие в себя M битов.

[Этап 2] настоящее изобретение предусматривает определение группы сокращенных информационных битов среди множества групп информационных битов. Группа сокращенных информационных битов соответствует группе удаленных столбцов в матрице проверки четности. Когда надлежащая группа столбцов удалена, может поддерживаться оптимизированная производительность кодирования. Поэтому выбирается группа столбцов, где поддерживается наилучшая производительность кодирования, когда соответствующая группа столбцов удалена. Кроме того, задается шаблон сокращения, который сокращает группу информационных битов, соответствующую выбранной группе столбцов. При этом форма матрицы проверки четности основана на матрице проверки четности, показанной на фиг. 1, или 'первой матрице проверки четности' в матрице проверки четности, показанной на фиг. 6B.

[Этап 3] Настоящее изобретение предусматривает определение шаблона прореживания в отношении битов первой четности на основании сокращенных битов или групп сокращенных битов. Настоящее изобретение предусматривает определение количество битов прореживания согласно уравнению (37) и выбор группы битов четности для прореживания количества групп битов четности, соответствующего количеству битов прореживания. Таким образом, в случае, когда сокращено Z групп битов, поскольку сокращено

[Этап 4] Настоящее изобретение предусматривает повторение этапа 2 и этапа 3, пока не будут выбраны все группы битов.

[Этап 5] Шаблон прореживания для битов второй четности определяется на основании полученного ранее шаблона сокращения и шаблона прореживания для битов первой четности.

Группа столбцов частичной матрицы четности матрицы проверки четности означает группу, состоящую из столбцов матрицы проверки четности, соответствующих битам в группе битов четности, показанной на фиг. 5A и 5B, и фиг. 7A и 7B.

В дальнейшем, в настоящем изобретении пояснены примеры шаблона сокращения и шаблона прореживания, заданных, как описано выше, для множества матриц проверки четности, имеющих структуру, показанную на фиг. 1.

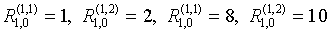

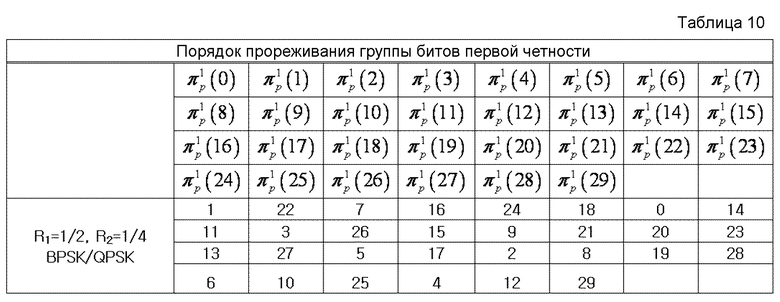

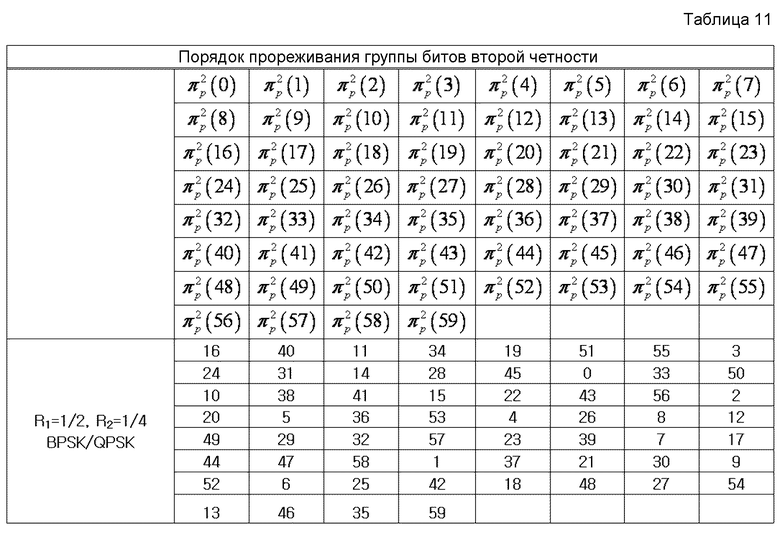

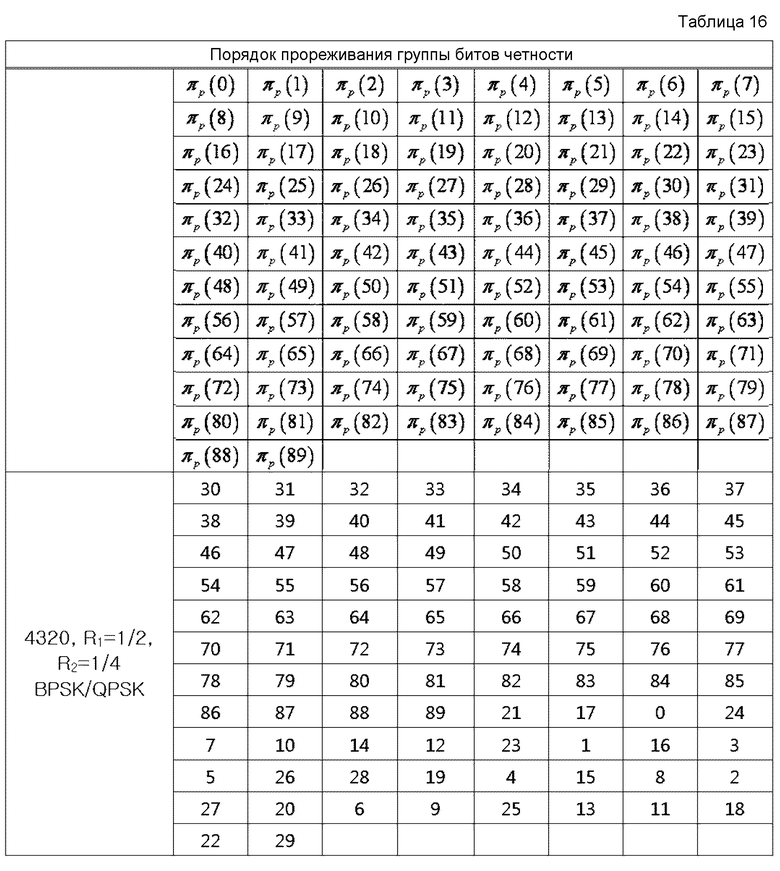

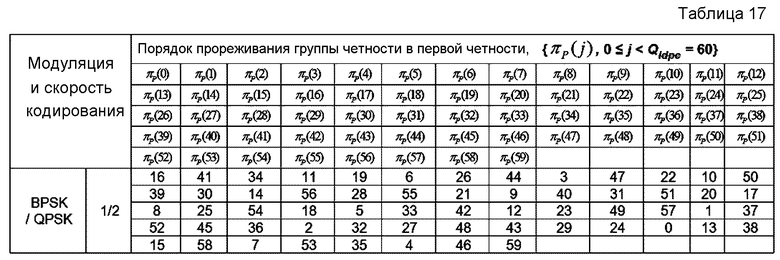

Согласно варианту осуществления настоящего изобретения, в случае использования схемы модуляции BPSK или QPSK на основании матрицы проверки четности, где

где

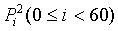

Как описано выше, в случае осуществления кодирования на основании структуры матрицы проверки четности, показанной на фиг. 1, или только части 'первой матрицы проверки четности', показанной на фиг. 6B, поскольку используются только биты первой четности, в случае использования схемы модуляции BPSK или QPSK на основании матрицы проверки четности, где

Кроме того, как описано выше, в случае использования структуры матрицы проверки четности, показанной на фиг. 6B, но без разделения битов первой четности и битов второй четности, как описано выше, можно задать единый шаблон прореживания таблицы 12, включающей в себя таблицу 10 и таблицу 11, и посредством которого задается группа битов четности выражается согласно уравнению (34) или уравнению (36). Согласно таблице 12, задается шаблон прореживания для прореживания битов второй четности с приоритетом, и для прореживания битов первой четности после прореживания всех битов второй четности.

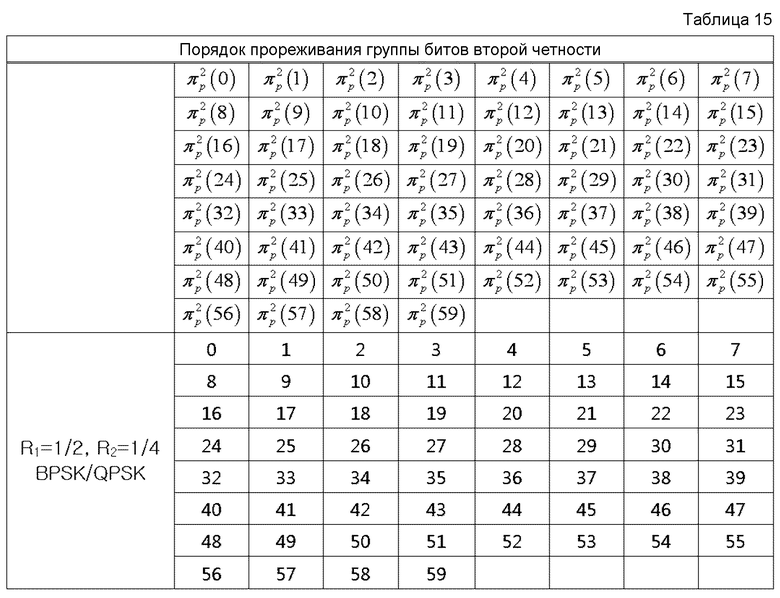

Согласно другому варианту осуществления настоящего изобретения, в случае использования схемы модуляции BPSK или QPSK на основании матрицы проверки четности, где

На Фиг. 16 показан вид, демонстрирующий производительность системы связи/широковещания согласно варианту осуществления настоящего изобретения. Фиг. 16 иллюстрирует производительность частоты ошибочных кадров (FER) для различных шаблонов прореживания в случае сокращения нулевого бита и прореживания 3320 битов. Согласно фиг. 16, по сравнению с различными формами шаблонов прореживания, выясняется, что случай использования шаблона прореживания таблицы 15 гарантирует высокую производительность.

Как описано выше, в случае осуществления кодирования на основании структуры матрицы проверки четности, показанной на фиг. 1, или только части 'первой матрицы проверки четности', показанной на фиг. 6B, поскольку используются только биты первой четности, в случае использования схемы модуляции BPSK или QPSK на основании матрицы проверки четности, где

Кроме того, как описано выше, в случае использования структуры матрицы проверки четности, показанной на фиг. 6B, но без разделения битов первой четности и битов второй четности, можно задать единый шаблон прореживания нижеприведенной таблицы 16, включающей в себя таблицу 14 и таблицу 15, и где группа битов четности выражается согласно уравнению (34) или уравнению (36). Согласно таблице 16, шаблон прореживания задается так, что биты второй четности прореживаются с приоритетом, и биты первой четности прореживаются после прореживания всех битов второй четности.

Согласно другому варианту осуществления настоящего изобретения, даже когда используются другие схемы модуляции помимо схемы модуляции BPSK и QPSK, применимы шаблоны сокращения и шаблоны прореживания таблицы 13, таблицы 14, таблицы 15 и таблицы 16.

Согласно другому варианту осуществления настоящего изобретения, в случае использования матрицы проверки четности, где

Фиг. 17 иллюстрирует производительность для случая использования шаблона прореживания таблицы 14 для битов первой четности и использования шаблона прореживания таблицы 15 для битов второй четности, и случая использования шаблона прореживания таблицы 14 для битов первой четности и использования шаблона прореживания таблицы 17 для битов второй четности в отношении различных длин сокращения и длин прореживания. На фиг. 17, 'случай 1' представляет, что длина

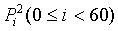

Как описано выше, в случае осуществления кодирования на основании структуры матрицы проверки четности, показанной на фиг. 1, или только части 'первой матрицы проверки четности', показанной на фиг. 6B, поскольку используются только биты первой четности, в случае использования схемы модуляции BPSK или QPSK на основании матрицы проверки четности, где

Кроме того, как описано выше, в случае использования структуры матрицы проверки четности, показанной на фиг. 6B, но без разделения битов первой четности и битов второй четности, то есть в случае задания группы битов четности согласно уравнениями (34) - (36), можно задавать единый шаблон прореживания таблицы 18, включающей в себя таблицу 14 и таблицу 17. Согласно таблице 18, задается, что биты второй четности прореживаются с приоритетом, и биты первой четности прореживаются после прореживания всех битов второй четности.

Далее описан процесс для осуществления сокращения и прореживания на групповой основе с использованием шаблона сокращения и шаблона прореживания таблиц 9-12, или шаблона сокращения и шаблона прореживания таблиц 13-18.

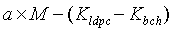

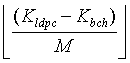

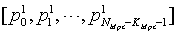

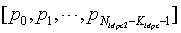

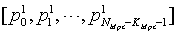

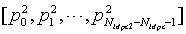

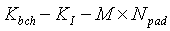

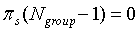

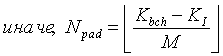

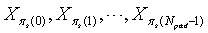

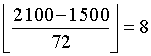

Контроллер 202 обеспечивает значение длины

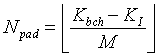

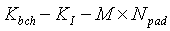

Блок 204 заполнения нулями заполняет, по меньшей мере, биты в соответствующих позициях нулями на основании значения

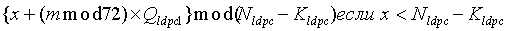

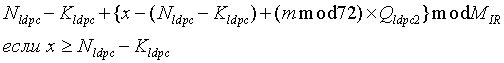

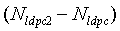

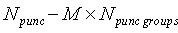

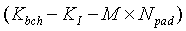

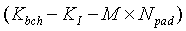

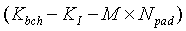

где

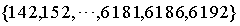

Таким образом, в отношении

В случае, когда количество

где

Таким образом, в отношении

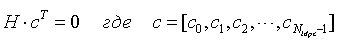

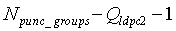

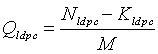

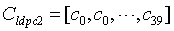

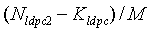

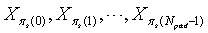

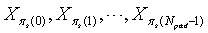

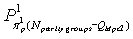

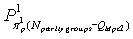

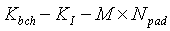

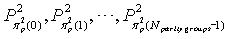

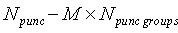

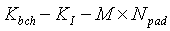

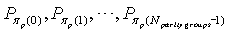

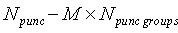

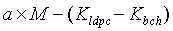

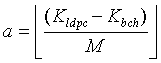

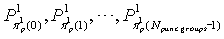

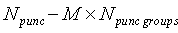

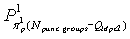

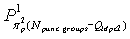

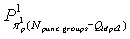

Блок 210 прореживания определяет количество групп битов четности, где все биты четности в группе подлежат прореживанию согласно уравнению (41) в отношении количества

где

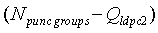

В случае, когда

Напротив, в случае, когда

Здесь,

Кроме того, блок 210 прореживания может удалять нулевой бит, заполненный блоком 204 заполнения нулями. Хотя в настоящем изобретении приведено описание с учетом сокращения и прореживания, сокращение и прореживание может осуществляться независимо.

Как описано выше, как показано в уравнении (34) и уравнении (35), группа битов четности может задаваться без различения групп битов первой четности и группы битов второй четности. В этом случае, блок 210 прореживания действует следующим образом.

Блок 210 прореживания определяет количество групп, подлежащих прореживанию, согласно уравнению (41) в отношении количества

Как описано выше, для определения шаблона сокращения и шаблона прореживания, которые являются последовательностями оптимизированных сокращенных битов и оптимизированных прореженных битов при сокращении

В случае совместного использования кода BCH и кода LDPC, предпочтительно, чтобы биты четности кода BCH, включенные в группу информационных битов, где присутствуют биты четности кода BCH, не сокращались. Поэтому группа информационных битов, включающая в себя биты четности кода BCH, имеет самую последнюю последовательность сокращения, и количество сокращенных битов в группе информационных битов, включающей в себя биты четности кода BCH, определяется как

Далее в настоящем изобретении описан процесс сокращения со ссылкой на фиг. 8. На Фиг. 8 показан вид, демонстрирующий процедуру заполнения в системе связи/широковещания согласно варианту осуществления настоящего изобретения.

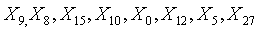

Согласно фиг. 8, на этапе 800,

Например, в случае, когда

Далее, в настоящем изобретении приведено описание со ссылкой на фиг. 9. Фиг. 9 иллюстрирует процедуру прореживания в системе связи/широковещания согласно варианту осуществления настоящего изобретения.

Согласно фиг. 9, на этапе 900,

В случае, когда используется первая матрица проверки четности, осуществляется этап 904, и прореживаются все биты в группах информационных битов

На этапе 902, в случае, когда первая матрица проверки четности не используется, и вторая матрица проверки четности используется, осуществляется этап 908 и производится определение, превышает ли

Когда

Когда

Согласно варианту осуществления, представленному на фиг. 9, этап 908 это этап для сравнения количества битов второй четности с количеством битов, подлежащих прореживанию, с использованием

Кроме того, процедура прореживания, представленная на фиг. 9, определяет форму матрицы проверки четности при осуществлении кодирования до прореживания, и предполагает, что кодирование осуществляется с использованием определенной матрицы проверки четности. Таким образом, в ходе кодирования используется первая матрица проверки четности или вторая матрица проверки четности. Таким образом, на этапе 902, в случае, когда используется первая матрица проверки четности, поскольку биты второй четности не генерируются, прореживание для битов второй четности не рассматривается.

Однако, согласно другому варианту осуществления настоящего изобретения, вторую матрицу проверки четности всегда можно использовать в ходе кодирования. В этом случае, в случае определения, передавать ли биты второй четности согласно вышеописанной процедуре прореживания, и затем, в случае отсутствия передачи битов второй четности, должны прореживаться все биты второй четности. В этом случае, до этапа 904, можно добавить этап для прореживания всех битов второй четности. Альтернативно, в этом случае, согласно другому варианту осуществления настоящего изобретения, этап 902, этап 904 и этап 906 можно опустить. В этом случае, процедура прореживания представлена на фиг. 10. Вариант осуществления, представленный на фиг. 10, исключает этапы 902-906 из фиг. 9. Таким образом, поскольку этап 1004 на фиг. 10 идентичен этапу 910, этап 1006 идентичен этапу 912, этап 1008 идентичен этапу 914, этап 1010 идентичен этапу 916, и этап 1012 идентичен этапу 918, ее подробное описание опущено.

Далее в настоящем изобретении описано процесс для определения матрицы проверки четности, подлежащей использованию со ссылкой на фиг. 11. Фиг. 11 иллюстрирует процедуру для определения формы матрицы проверки четности в системе связи/широковещания согласно варианту осуществления настоящего изобретения.

Согласно фиг. 11, на этапе 1100 производится определение, используется ли дополнительная четность (AP). В случае передачи дополнительного бита четности в (n-1)-й кадр помимо информационного слова и непрореженных битов четности, передаваемый в n-й кадр, дополнительный бит четности означает AP. AP можно использовать для эффекта разнесения и коэффициента усиления кодирования. В частности, AP может включать в себя информационные биты и непрореженные биты четности, и некоторые из прореженных битов четности. Использовать ли AP, определяется размером порога, используемым для определения формы матрицы проверки четности. Например, AP может включать в себя прореженные биты среды битов первой четности с приоритетом.

При использовании AP, осуществляется этап 1102, и производится определение, меньше ли количество

Напротив, когда AP не используется, осуществляется этап 1108, и определяется, меньше ли количество

Далее в настоящем изобретении подробно описаны принцип работы и конструкция передающей стороны и принимающей стороны, осуществляющей сокращение и прореживание, как описано выше со ссылкой на чертеж.

Фиг. 12A и 12B иллюстрируют рабочую процедуру передающей стороны в системе связи/широковещания согласно варианту осуществления настоящего изобретения.

Согласно фиг. 12A и 12B, передающая сторона определяет количество битов, подлежащих заполнению, на этапе 1200. Бит, подлежащий заполнению, это бит, подлежащий сокращению, возникающий, когда количество входных битов для кодирования, то есть количество информационных битов BCH больше количества обеспеченных информационных битов. Таким образом, передающая сторона определяет количество битов, подлежащих заполнению нулями, путем вычитания количества информационных битов из количества информационных битов BCH, которое является количеством входных битов для кодирования.

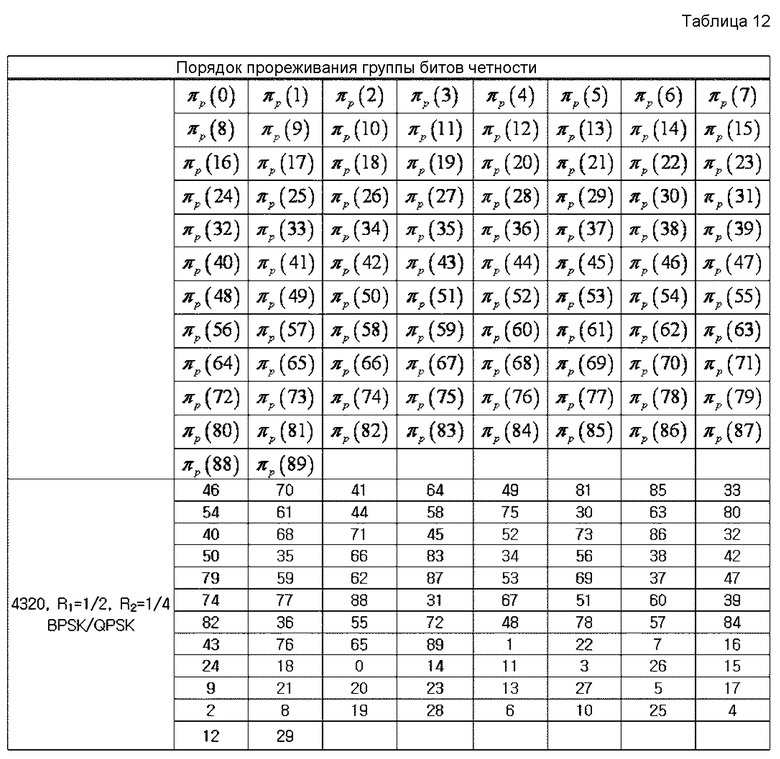

Затем передающая сторона переходит к этапу 1202 для определения шаблона сокращения. Таким образом, передающая сторона сохраняет, по меньшей мере, один заранее заданный шаблон сокращения, и выбирает шаблон сокращения, соответствующий текущему условию, из сохраненного, по меньшей мере, одного шаблона сокращения. Например, шаблон сокращения может задаваться на основании длины кодового слова, скорости кодирования, отношения сокращения и прореживания, схемы модуляции и т.д. Например, по меньшей мере, один шаблон сокращения задается на основе групп битов, который делит информационные биты на основе заранее определенного количества. Например, по меньшей мере, один шаблон сокращения может включать в себя таблицу 9 или таблицу 13. Согласно другому варианту осуществления настоящего изобретения, передающая сторона может заранее не сохранять шаблон сокращения, но может генерировать шаблон сокращения на основании текущего условия. Например, генерируемый шаблон сокращения может включать в себя таблицу 9 или таблицу 13.

После определения шаблона сокращения, передающая сторона переходит к этапу 1204 для определения количества

Затем передающая сторона переходит к этапу 1206 для определения, больше ли

Напротив, когда

После этого, передающая сторона переходит к этапу 1214 для осуществления кодирования на заполненных информационных битах, то есть информационных битах BCH. При этом передающая сторона может совместно осуществлять множество методов кодирования. Например, передающая сторона может последовательно осуществлять BCH-кодирование и LDPC-кодирование. В этом случае, передающая сторона может осуществлять BCH-кодирование на информационных битах BCH и осуществлять LDPC-кодирование на информационных битах LDPC, то есть кодовом слове BCH, генерируемый в результате BCH-кодирования. Согласно другому варианту осуществления настоящего изобретения, передающая сторона может осуществлять только LDPC-кодирование на информационных битах BCH, то есть информационных битов, заполненных нулями. В случае, когда осуществляется только LDPC-кодирование без BCH-кодирования, информационные биты BCH могут именоваться информационными битами LDPC. При использовании матрицы проверки четности, передающая сторона может использовать значение адреса накопителя, как представлено в уравнении 5, уравнении 7, уравнении 23 и уравнении 24.

Согласно другому варианту осуществления настоящего изобретения, передающая сторона может определять форму матрицы проверки четности с целью использования для кодирования до осуществления кодирования на этапе 1214. Таким образом, передающая сторона согласно варианту осуществления настоящего изобретения может использовать две или более матриц проверки четности. Например, две или более матриц проверки четности включают в себя первую матрицу проверки четности и вторую матрицу проверки четности, представленные на фиг. 6B. При этом принимающая сторона может сохранять первую матрицу проверки четности и вторую матрицу проверки четности отдельно, или сохранять только вторую матрицу проверки четности и извлекать первую матрицу проверки четности из второй матрицы проверки четности и использовать ее. Например, определение формы матрицы проверки четности для использования может осуществляться на основании, по меньшей мере, одной из длины информационного слова и скорости кодирования. Например, определение формы матрицы проверки четности для использования может осуществляться в процессе, показанном на фиг. 10. В случае, когда процесс определения формы матрицы проверки четности для использования не осуществляется, принимающая сторона может осуществлять кодирование с использованием второй матрицы проверки четности, которая является более крупной формой, и определять, удаляется ли после этого вторая четность на основании скорости кодирования.

После осуществления кодирования, передающая сторона переходит к этапу 1216 для определения количества битов, подлежащих прореживанию. Например, передающая сторона может определять количество битов, подлежащих прореживанию на основании значения, связанного с количеством сокращенных битов и скоростью кодирования, другими словами, отношения прореживания и сокращения. Например, значение, связанное с количеством сокращенных битов и скоростью кодирования, может задаваться уравнением (37). Кроме того, передающая сторона может определять количество битов, подлежащих прореживанию, с учетом структуры матрицы проверки четности или количества входных битов.

После определения количества битов, подлежащих прореживанию, передающая сторона может перейти к этапу 1218 для определения шаблона прореживания. Таким образом, передающая сторона сохраняет, по меньшей мере, один заранее заданный шаблон прореживания и выбирает шаблон прореживания, соответствующий текущему условию из сохраненного, по меньшей мере, одного шаблона прореживания. Например, шаблон прореживания может задаваться на основании формы матрицы проверки четности для использования, длины кодового слова, скорости кодирования, отношения сокращения и прореживания, схемы модуляции, и т.д. Например, на основе групп битов четности задается, по меньшей мере, один шаблон прореживания, который делит биты четности на основе заранее определенного числа. Например, по меньшей мере, один шаблон прореживания может включать в себя, по меньшей мере, одну из таблицы 10, таблицы 11, таблицы 12, таблицы 14, таблицы 15, таблицы 16, таблицы 17 и таблицы 18. Согласно другому варианту осуществления настоящего изобретения, передающая сторона может заранее не сохранять шаблон прореживания, но может генерировать шаблон прореживания на основании текущего условия. Например, генерируемый шаблон прореживания может включать в себя, по меньшей мере, одну из таблицы 10, таблицы 11, таблицы 12, таблицы 14, таблицы 15, таблицы 16, таблицы 17 и таблицы 18.

При этом передающая сторона должна учитывать форму матрицы проверки четности для использования. Например, форма матрицы проверки четности для использования может определяться на основании, по меньшей мере, одной из длины информационного слова и скорости кодирования. Например, определение формы матрицы проверки четности для использования может осуществляться в процессе, показанном на фиг. 10. В случае, когда матрица проверки четности для использования является первой матрицей проверки четности, представленной на фиг. 6B, шаблон прореживания определяется на основании таблицы 10 или таблицы 14. Напротив, в случае, когда матрица проверки четности для использования является второй матрицей проверки четности, представленной на фиг. 6B, шаблон прореживания определяется таблицей 12 или таблицей 16 или таблицей 18, или определяется таблицей 10 и таблицей 11, или таблицей 14 и таблицей 15, или таблицей 14 и таблицей 17. Согласно таблице 10 и таблице 11, или таблице 14 и таблице 15, или таблице 14 и таблице 17, передающая сторона сначала определяет шаблон прореживания согласно таблице 11 или таблице 15 или таблице 17, и затем, когда присутствует бит, подлежащий прореживанию, передающая сторона определяет остаток шаблона прореживания согласно таблице 10 или таблице 14.

После определения шаблона прореживания, передающая сторона переходит к этапу 1220 для определения количества

Затем передающая сторона переходит к этапу 1222 для определения, больше ли

Напротив, когда

Затем передающая сторона переходит к этапу 1226 для прореживания некоторых битов в

Этап 1226 снова описан согласно шаблону прореживания, показанному на фиг. 10, и процессу определения прореженного бита четности. На этапе 1226,

Затем передающая сторона переходит к этапу 1228 для удаления заполненных битов до осуществления кодирования. Другими словами, передающая сторона удаляет биты, заполненные нулями на этапе 1208 к этапу 1210. После этого, передающая сторона переходит к этапу 1230 для передачи прореженного и сокращенного кодового слова.

Фиг. 13A и 13B иллюстрируют рабочую процедуру принимающей стороны в системе связи/широковещания согласно варианту осуществления настоящего изобретения.

Согласно фиг. 13A и 13B принимающая сторона определяет, принято ли сокращенное и прореженное кодовое слово на этапе 1300.

Когда сокращенное и прореженное кодовое слово принято, принимающая сторона переходит к этапу 1302 для определения количества сокращенных битов. Сокращение происходит, когда количество входных битов для кодирования больше количества информационных битов. Таким образом, принимающая сторона определяет количество битов, заполненных нулями, путем вычитания количества информационных битов принятого прореженного и сокращенного кодового слова из количества информационных битов кодового слова LDPC.

Затем принимающая сторона переходит к этапу 1304 для определения применяемого шаблона сокращения. Таким образом, принимающая сторона сохраняет, по меньшей мере, один заранее заданный шаблон сокращения, и выбирает шаблон сокращения, соответствующий текущему условию, из сохраненного, по меньшей мере, одного шаблона сокращения. Например, шаблон сокращения может задаваться на основании длины кодового слова, скорости кодирования, отношения сокращения и прореживания, схемы модуляции и т.д. Например, по меньшей мере, один шаблон сокращения задается на основе групп битов, который делит информационные биты на основе заранее определенного количества. Например, по меньшей мере, один шаблон сокращения может включать в себя таблицу 9 или таблицу 13. Согласно другому варианту осуществления настоящего изобретения, принимающая сторона может не сохранять шаблон сокращения, но может генерировать шаблон сокращения на основании текущего условия. Например, генерируемый шаблон сокращения может включать в себя, по меньшей мере, одну из таблицы 9 и таблицы 13. Согласно еще одному варианту осуществления настоящего изобретения, принимающая сторона может использовать шаблон сокращения, указанный передающей стороной посредством отдельной сигнализации.

После определения шаблона сокращения, принимающая сторона переходит к этапу 1306 для определения количества

Затем принимающая сторона переходит к этапу 1308 для определения, больше ли

Напротив, когда

Затем принимающая сторона переходит к этапу 1312 для задания входного значения LDPC-декодера, соответствующего некоторым информационным битам переднего конца или заднего конца в

Кроме того, принимающая сторона переходит к этапу 1314 для задания входных значений LDPC-декодера, соответствующих информационным битам, не заполненным нулями, равными значениям, которые зависят от принятого прореженного и сокращенного кодового слова. Например, в случае, когда входное значение декодирования является значением LLR, значение, представляющее 0 бит, означает значение LLR случая, когда вероятность того, что LLR принимает значение 0, равна 1, и вероятность того, что LLR принимает значение 1, равна 0. Таким образом, принимающая сторона восстанавливает информационные биты среди кодового слова LDPC, генерируемого путем кодирования на передающей стороне на этапах 1310 - 1314.

После этого, принимающая сторона переходит к этапу 1316 для определения количества прореженных битов на основании значения, связанного со скоростью кодирования и количеством сокращенных битов, другими словами, отношения прореживания и сокращения. Например, значение, связанное со скоростью кодирования и количеством сокращенных битов, другими словами, отношением прореживания и сокращения, может задаваться уравнением (37).

После определения количества битов прореживания, принимающая сторона переходит к этапу 1318 для определения применяемого шаблона прореживания. Таким образом, принимающая сторона сохраняет, по меньшей мере, один заранее заданный шаблон прореживания и выбирает шаблон прореживания, соответствующий текущему условию из сохраненного, по меньшей мере, одного шаблона прореживания. Например, шаблон прореживания может задаваться на основании формы матрицы проверки четности для использования, длины кодового слова, скорости кодирования, отношения сокращения и прореживания, схемы модуляции, и т.д. Например, на основе групп битов четности задается, по меньшей мере, один шаблон прореживания, который делит биты четности на основе заранее определенного числа. Например, по меньшей мере, один шаблон прореживания может включать в себя, по меньшей мере, одну из таблицы 10, таблицы 11, таблицы 12, таблицы 14, таблицы 15, таблицы 16, таблицы 17 и таблицы 18. При этом принимающая сторона должна учитывать форму матрицы проверки четности для использования. Например, форма матрицы проверки четности для использования может определяться, по меньшей мере, одной из длины информационного слова и скорости кодирования. Например, определение формы матрицы проверки четности для использования можно осуществлять в процессе, показанном на фиг. 10. В случае, когда матрица проверки четности для использования является первой матрицей проверки четности, представленной на фиг. 6B, шаблон прореживания определяется таблицей 10 или таблицей 14. Напротив, в случае, когда матрица проверки четности для использования является второй матрицей проверки четности, представленной на фиг. 6B, шаблон прореживания определяется таблицей 12 или таблицей 16 или таблицей 18, или комбинацией таблицы 11 и таблицы 10 или комбинацией таблицы 14 и таблицы 15 или комбинацией таблицы 14 и таблицы 17. Согласно комбинации таблицы 11 и таблицы 10 или комбинации таблицы 14 и таблицы 15 или комбинации таблицы 14 и таблицы 17, принимающая сторона сначала определяет шаблон прореживания согласно таблице 11 или таблице 15 или таблице 17, и затем в случае, когда остается бит прореживания, принимающая сторона определяет остальные шаблоны прореживания согласно таблице 10 или таблице 14. Согласно другому варианту осуществления настоящего изобретения, принимающая сторона может заранее не сохранять шаблон прореживания, но может генерировать шаблон прореживания согласно текущему условию. Например, генерируемый шаблон прореживания может включать в себя, по меньшей мере, одну из комбинации таблицы 10, таблицы 11, таблицы 12, таблицы 14, таблицы 15, таблица 16, таблица 17, таблица 18, таблица 12, таблица 16, таблицы 18, таблицы 10 и таблицы 11 (в передней части таблицы 11 и дублировать), и комбинации таблицы 14 и таблицы 15, и комбинации таблицы 14 и таблицы 17. Согласно другому варианту осуществления настоящего изобретения, принимающая сторона может использовать шаблон прореживания, указанный передающей стороной посредством отдельной сигнализации.

После определения шаблона прореживания, принимающая сторона переходит к этапу 1320 для определения количества

Затем принимающая сторона переходит к этапу 1322 для определения, больше ли

Напротив, когда

Этап 1324 снова описан согласно шаблону прореживания, показанному на фиг. 10, и процессу определения прореженного бита четности. На этапе 1324, группы битов четности с 0-й по

Затем принимающая сторона переходит к этапу 1326 для задания входного значения LDPC-декодера, соответствующего некоторым битам переднего конца или заднего конца в

Этап 1326 снова описан согласно шаблону прореживания, показанному на фиг. 10, и процессу определения прореженного бита четности. На этапе 1326,

Затем принимающая сторона переходит к этапу 1328 для задания входных значений LDPC-декодера, соответствующих остатку непрореженных битов четности, на основании приемного значения сокращенного и прореженного кодового слова. Таким образом, принимающая сторона восстанавливает биты четности среди кодового слова LDPC, генерируемого путем кодирования передающей стороной на этапе 1324-1328.

После этого, принимающая сторона переходит к этапу 1330 для осуществления декодирование на восстановленном кодовом слове. При этом принимающая сторона может совместно осуществлять множество методов декодирование. Например, принимающая сторона может последовательно осуществлять LDPC-декодирование и BCH-декодирование. В этом случае, принимающая сторона может осуществлять LDPC-декодирование на восстановленном кодовом слове LDPC, и осуществлять BCH-декодирование на информационных битах LDPC, генерируемых в результате LDPC-декодирования. Согласно другому варианту осуществления настоящего изобретения, принимающая сторона может осуществлять только LDPC-декодирование на восстановленном кодовом слове LDPC.

Фиг. 14 иллюстрирует конструкцию передающей стороны в системе связи/широковещания согласно варианту осуществления настоящего изобретения.

Согласно фиг. 14, передающая сторона включает в себя блок 1410 заполнения нулями, кодер 1420, блок 1430 прореживания, передатчик 1440, хранилище 1460 и контроллер 1470.

Блок 1410 заполнения нулями генерирует информационные биты BCH для подачи на кодер 1420 путем заполнения некоторых информационных битов нулями. Блок 1410 заполнения нулями определяет количество битов, подлежащих заполнению нулями с использованием информации, поступающей от контроллера 1470, и заполняет нулями биты в позициях, которые зависят от информации шаблона сокращения, поступающей от контроллера 1470. Таким образом, блок 1410 заполнения нулями заполняет биты групп битов, которые зависят от последовательности, указанной шаблоном сокращения, и отображает каждый бит информационных битов в позицию остальных битов. Блок 1410 заполнения нулями может определять количество

Кодер 1420 осуществляет кодирование на информационных битах BCH, заполненных блоком 1410 заполнения нулями. Кодер 1420 может включать в себя только один блок кодирования или может иметь структуру, где множество блоки кодирования соединены. Например, хотя не показано, кодер 1420 может включать в себя BCH-кодер и LDPC-кодер. В этом случае, BCH-кодер может осуществлять BCH-кодирование на заполненных информационных битах BCH, и LDPC-кодер может осуществлять LDPC-кодирование на кодовом слове BCH, генерируемом в результате BCH-кодирования. Согласно другому варианту осуществления настоящего изобретения, кодер 1420 может осуществлять только LDPC-кодирование на информационных битах BCH. В случае осуществления только LDPC-кодирования без BCH-кодирования, информационные биты BCH могут именоваться информационными битами LDPC. Согласно еще одному варианту осуществления настоящего изобретения, помимо кодера 1420 к переднему концу блока 1410 заполнения нулями можно добавить еще один кодер (не показан). Например, кодер 1420 может осуществлять LDPC-кодирование, и еще один кодер (не показан) расположенный на переднем конце блока 1410 заполнения нулями, может осуществлять BCH-кодирование.

Согласно еще одному варианту осуществления настоящего изобретения, кодер 1420 может определять форму матрицы проверки четности с целью использования для кодирования до осуществления кодирования. Таким образом, передающая сторона согласно варианту осуществления настоящего изобретения может использовать две или более матриц проверки четности. Например, две или более матриц проверки четности включают в себя первую матрицу проверки четности и вторую матрицу проверки четности, представленные на фиг. 6B. При этом хранилище 1460 может сохранять первую матрицу проверки четности и вторую матрицу проверки четности отдельно, или сохранять только вторую матрицу проверки четности, и извлекать первую матрицу проверки четности из второй матрицы проверки четности. Например, определение формы матрицы проверки четности для использования может осуществляться согласно, по меньшей мере, одной из длины информационного слова и скорости кодирования. Например, определение формы матрицы проверки четности для использования может осуществляться в процессе, показанном на фиг. 10. В случае, когда процесс для определения форма матрицы проверки четности для использования не осуществляется, кодер 1420 может осуществлять кодирование с использованием второй матрицы проверки четности, которая является более крупной формой, и после этого определять, удалять ли вторую четность на основании скорости кодирования. Кроме того, при использовании матрицы проверки четности, кодер 1420 может использовать значение адреса накопителя, как представлено в уравнении (5), уравнении (7), уравнении (23) и уравнении (24).

Блок 1430 прореживания преобразует четность среди кодового слова LDPC, выводимого из кодера 1420, в биты четности, подлежащие передаче, путем прореживания некоторых битов из четности среди кодового слова LDPC, генерируемого кодером 1420. Блок 1430 прореживания определяет количество битов, подлежащих прореживанию, на основании значения, связанного со скоростью кодирования, поступающего от контроллера 1470, и количества сокращенных битов, другими словами, отношения прореживания и сокращения, и прореживает биты в позициях, которые зависит от информации шаблона прореживания, поступающей от контроллера 1470. Кроме того, блок 1430 прореживания может различать биты первой четности и биты второй четности на основании формы матрицы проверки четности, базирующейся в кодере 1420, от контроллера 1470. Таким образом, блок 1430 прореживания прореживает биты в группах битов четности, которые зависят от последовательности, указанной шаблоном прореживания. Например, значение, связанное со скоростью кодирования и количеством сокращенных битов, другими словами, отношением прореживания и сокращения, может задаваться уравнением (37). Кроме того, блок 1430 прореживания определяет количество

Описание снова приведено согласно шаблону прореживания, показанному на фиг. 10, и процессу определения прореженного бита четности. В случае, когда

Кроме того, блок 1430 прореживания может преобразовывать информационные биты среди кодового слова LDPC, выводимого из кодера 1420, в информационные биты в прореженное и сокращенное кодовое слово, подлежащее передаче, путем удаления битов, заполненных нулями, блоком 1410 заполнения нулями. В этом случае, блок 1430 прореживания может именоваться 'блоком прореживания и удаления нулей'.