Предпосылки создания изобретения

Настоящее изобретение относится к сфере обработки текста. Более точно изобретение относится к сфере эффективной обработки символьных данных.

При обработке текстовой информации часто требуется выполнить сравнение символьных данных, в том числе (но не ограничиваясь) сравнение символьных строк. Обычно команды, применяемые для сравнения символьных данных, в один момент времени выполняют сравнение одиночного байта данных.

Кроме того, при обработке текстовой информации часто требуются другие виды обработки символьных данных, в том числе поиск места завершения (например, конца строки), определение объема символьных данных, поиск определенного символа и т.д. Команды, применяемые в настоящее время для указанных видов обработки, становятся все менее эффективными.

Сущность изобретения

Для преодоления недостатков уровня техники предложен способ выполнения машинной команды в центральном процессорном устройстве, включающий следующие шаги: получение процессором машинной команды для выполнения, которая определена для выполнения компьютером в соответствии с архитектурой компьютера и содержит: по меньшей мере одно поле кода операции для указания кода операции, идентифицирующего операцию, выполняемую по команде векторного типа для поиска неравнозначного элемента (англ.: Vector Find Element Not Equal), поле расширения, используемое для обозначения одного или более регистров, поле первого регистра, объединяемое с первой частью указанного поля расширения для обозначения первого регистра, содержащего первый операнд, являющийся векторным операндом, содержащим заданное число элементов, поле второго регистра, объединяемое со второй частью указанного поля расширения для обозначения второго регистра, содержащего второй операнд, являющийся векторным операндом, содержащим заданное число элементов, поле третьего регистра, объединяемое с третьей частью указанного поля расширения для обозначения третьего регистра, содержащего третий операнд, являющийся векторным операндом, содержащим заданное число элементов, поле маски, которое содержит один или более управляющих флагов, предназначенных для использования во время выполнения машинной команды; выполнение машинной команды, включающее принятие решения о том (т.е. определение того), содержит ли поле маски флаг поиска нуля, указывающий на необходимость поиска в векторе равного нулю элемента, на основе поля маски, содержащего флаг поиска нуля, указывающий на необходимость поиска в векторе равного нулю элемента, т.е. при наличии указанного флага поиска нуля в поле маски, выполнение поиска во втором операнде равного нулю элемента, причем в результате поиска предоставляется индекс равного нулю элемента, содержащий индекс найденного в результате поиска равного нулю элемента или длину вектора, если равный нулю элемент не найден, выполняемое в параллельном режиме сравнение одного или более элементов второго операнда с каждым элементом третьего операнда на предмет неравенства их значений, причем в результате сравнения предоставляется индекс сравнения, основанный на направлении поиска и длине элементов вектора и содержащий индекс найденного в результате сравнения неравнозначного элемента или длину вектора, если неравнозначных элементов в результате сравнения не найдено, формирование результата, причем в зависимости от того, выполнялся ли поиск равного нулю элемента, результат содержит одно из двух: если поиск равного нулю элемента не выполнялся, то результат содержит индекс сравнения, а если поиск равного нулю элемента выполнялся, то результат содержит минимальное из значений индекса сравнения и индекса равного нулю элемента.

Объектами изобретения являются также машиночитаемый носитель данных, в котором хранится компьютерная программа, содержащая команды для выполнения всех шагов описанного выше способа при ее выполнении в компьютерной системе, а также компьютерная система для выполнения машинной команды в центральном процессорном устройстве, содержащая один или более процессоров, приспособленных для выполнения всех шагов описанного выше способа при выполнении компьютерной программы, хранящейся в машиночитаемом носителе данных.

Технический результат, достигаемый при осуществлении изобретения, заключается, в частности, в повышении эффективности обработки символьных данных.

Краткое описание чертежей

В описании и формуле изобретения указываются и отдельно формулируются в качестве примеров один или более аспектов настоящего изобретения. Вышеупомянутые и прочие объекты, особенности и преимущества настоящего изобретения раскрываются в последующем подробном описании, которое сопровождается чертежами. На чертежах показано:

на фиг. 1 - схема примера вычислительной среды, в состав которой могут входить и в которой могут использоваться один или более аспектов настоящего изобретения,

на фиг. 2А - схема другого примера вычислительной среды, в состав которой могут входить и в которой могут использоваться один или более аспектов настоящего изобретения,

на фиг. 2Б - более детальная схема запоминающего устройства из состава вычислительной среды, показанной на фиг. 2А, согласно варианту осуществления настоящего изобретения,

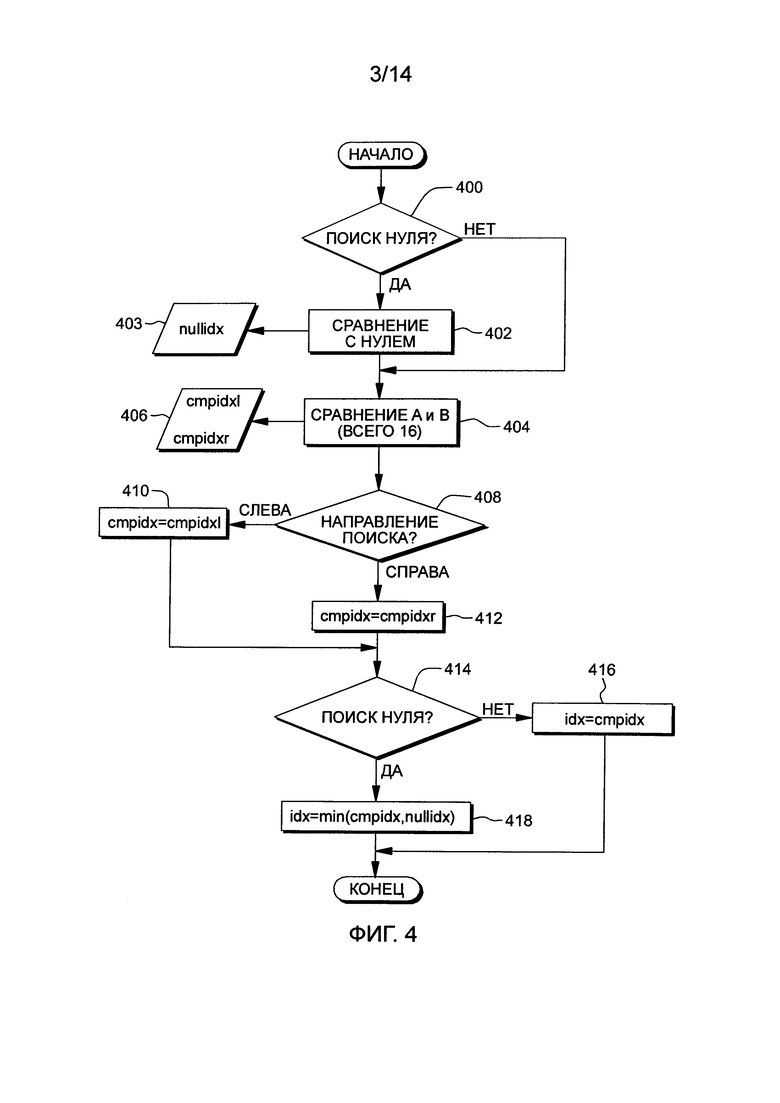

на фиг. 3 - схема варианта формата команды векторного типа для поиска неравнозначного элемента согласно варианту осуществления настоящего изобретения,

на фиг. 4 - схема варианта процедуры, связанной с командой векторного типа для поиска неравнозначного элемента, согласно варианту осуществления настоящего изобретения,

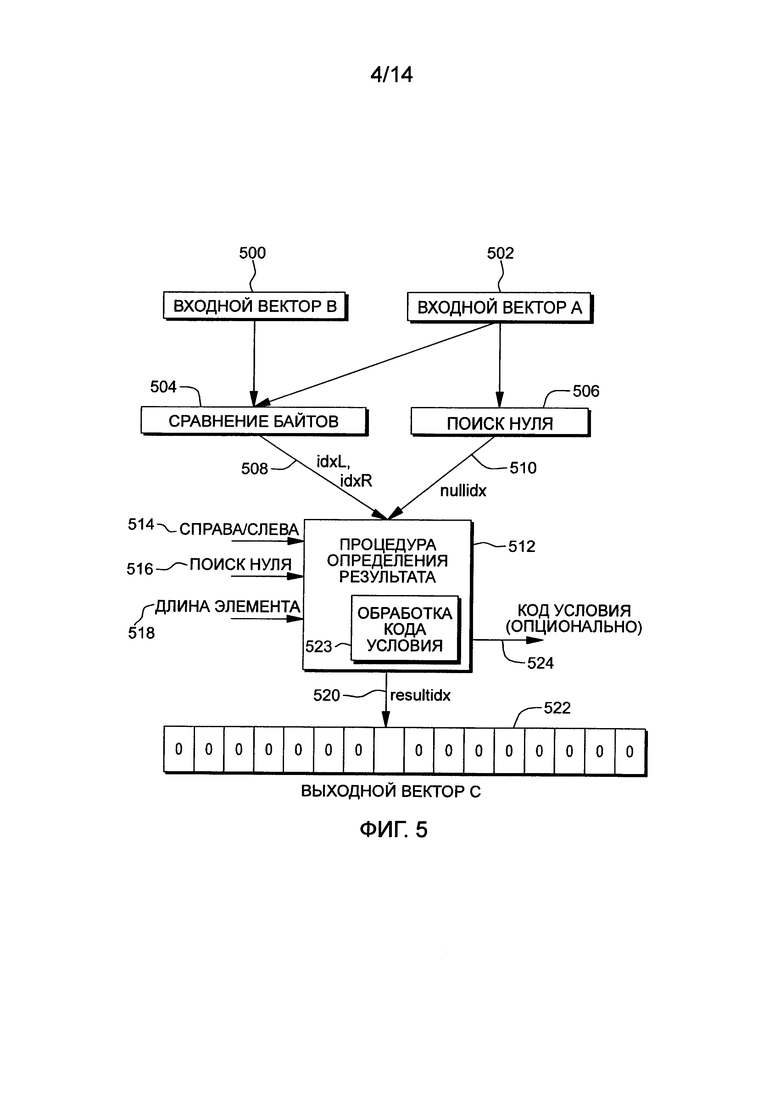

на фиг. 5 - схема взаимодействия узлов обработки, реализующая процедуру, показанную на фиг. 4, согласно варианту осуществления настоящего изобретения,

на фиг. 6 - схема примера файла регистра согласно варианту осуществления настоящего изобретения,

на фиг. 7 - графическое представление варианта осуществления компьютерного программного продукта, содержащего один или более аспектов настоящего изобретения,

на фиг. 8 - схема варианта осуществления хост-компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 9 - схема другого варианта осуществления компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 10 - схема другого варианта осуществления компьютерной системы, содержащей вычислительную сеть, для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 11 - схема варианта осуществления различных узлов компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 12А - схема варианта осуществления исполнительного устройства из состава компьютерной системы, показанной на фиг. 11, для внедрения и использования одного или более аспектов настоящего изобретения,

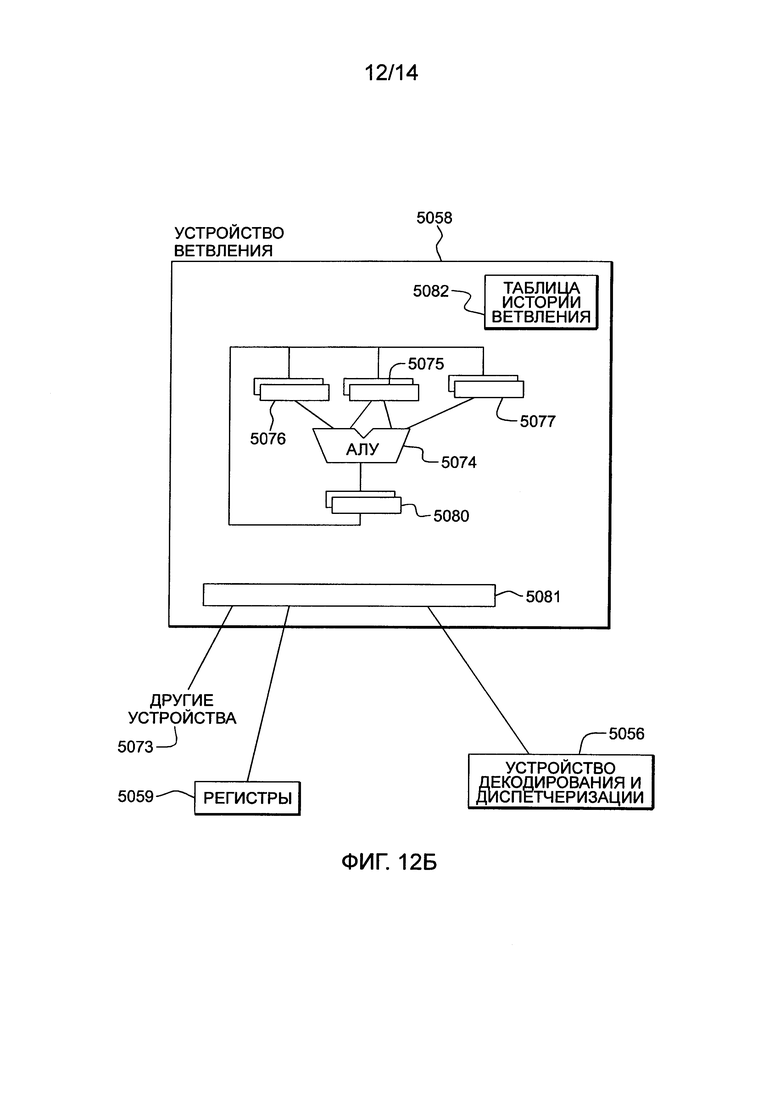

на фиг. 12Б - схема варианта осуществления устройства ветвления из состава компьютерной системы, показанной на фиг.11, для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 12В - схема варианта осуществления устройства загрузки-хранения из состава компьютерной системы, показанной на фиг.11, для внедрения и использования одного или более аспектов настоящего изобретения,

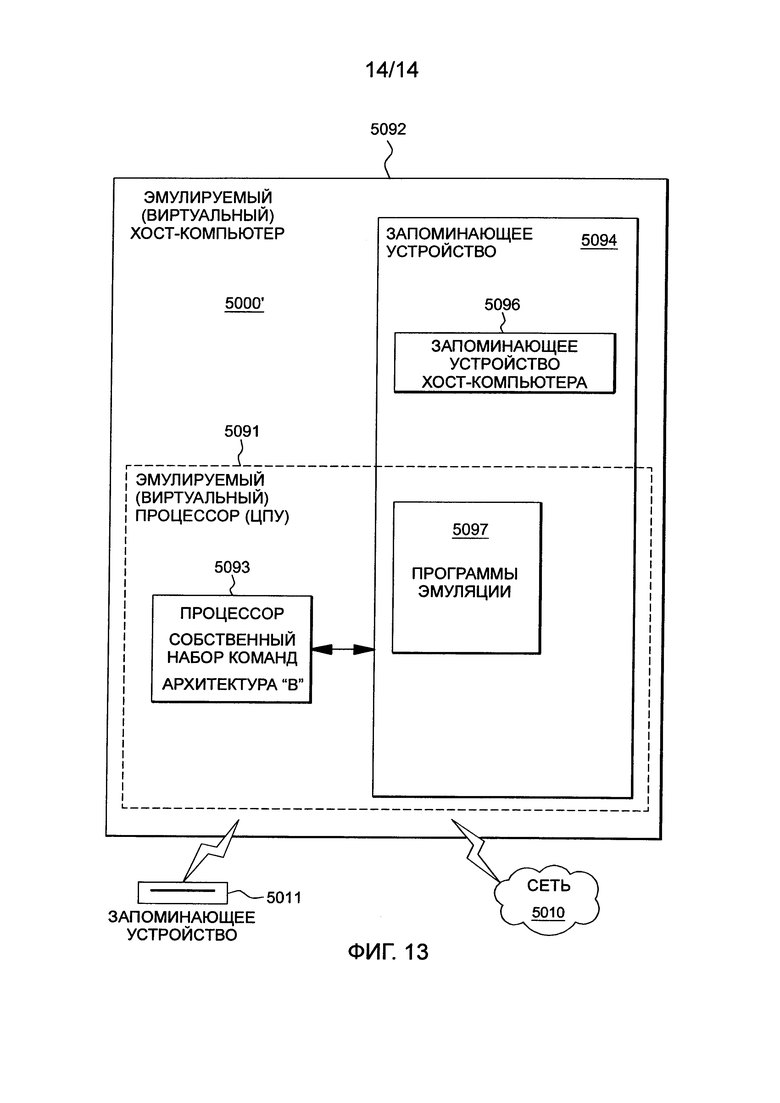

на фиг. 13 - схема варианта осуществления эмулируемой (виртуальной) хост-компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения.

Подробное описание

Согласно варианту осуществления настоящего изобретения, предоставляется возможность эффективной обработки символьных данных, в том числе (но не ограничиваясь) буквенных символов на любом языке, чисел, образованных из цифр, знаков пунктуации и/или прочих символов. Указанные символьные данные могут являться строками данных или не являться строками данных. С символьными данными связаны стандарты, примерами которых, в том числе, являются: ASCII (от английского American Standard Code for Information Interchange - Американский стандартный код обмена информацией); Юникод (стандарт Международной организации по стандартизации представления символов всех национальных алфавитов), в том числе (но не ограничиваясь) UTF 8 (от английского Unicode Transformation Format - формат преобразования Юникода); UTF16 и т.д.

Согласно одному из вариантов осуществления, вводится команда Find Element Not Equal, которая сравнивает данные многоэлементных векторов на предмет неравенства и формирует признак неравенства, если таковое имеет место. Согласно одному из вариантов осуществления, в специально предусмотренном векторном регистре сохраняется индекс, связанный с тем элементом, которому найден неравный элемент.

Согласно настоящей заявке, длина элемента векторного регистра (также используется термин ″вектор″) составляет, например, один, два или четыре байта; векторным операндом является, например, операнд типа SIMD (от английского Single Instruction, Multiple Data - одиночный поток команд, множественный поток данных), состоящий из множества элементов. Согласно другим вариантам осуществления, длина элементов может быть иной, и векторный операнд необязательно имеет тип SIMD и/или может содержать один элемент.

Согласно другому варианту осуществления, та же команда Find Element Not Equal также в выбранном векторе выполняет поиск элементов с нулевыми значениями (например, значения всех двоичных разрядов элемента равны нулю). Ноль или пустой символ (символ конца строки) указывает на окончание символьных данных, например, означает конец определенной строки данных. Результат выполнения команды зависит от того, выполнялся ли поиск равного нулю элемента или же выполнялось сравнение элементов.

Схема одного из вариантов осуществления вычислительной среды для внедрения и использования одного или более вариантов настоящего изобретения показана на фиг. 1. Вычислительная среда 100 содержит, например, процессор 102 [например, центральное процессорное устройство (ЦПУ)], запоминающее устройство 104 (например, основное запоминающее устройство) и одно или более устройств ввода-вывода и/или один или более интерфейсов 106, соединенных с другой вычислительной средой, например, через одну или более шин 108 и/или с помощью иных соединений.

Согласно варианту осуществления, процессор 102 основан на архитектуре z/Architecture (торговая марка, обозначающая архитектуру линейки мейнфреймов), предложенной корпорацией International Business Machines Corporation (корпорацией IBM) и являющейся частью сервера, такого как сервер System z (торговая марка, обозначающая линейку мейнфреймов), который также предлагается корпорацией International Business Machines Corporation и в котором реализована архитектура z/Architecture. Один из вариантов осуществления архитектуры z/Architecture описан в публикации IBM ″z/Architecture Principles of Operation″ (от англ.: ″Принцип действия архитектуры z/Architecture″, публикация IBM № SA 22-7832-08, 9-е издание, август 2010 г.). Согласно одному из вариантов осуществления, процессор выполняет команды операционной системы, такой как z/OS, также предлагаемой корпорацией IBM. IBM®, Z/ARCHITECTURE® и Z/OS® являются зарегистрированными торговыми марками корпорации International Business Machines Corporation, Армонк, штат Нью-Йорк, США. Прочие наименования, используемые в настоящей заявке, могут также быть зарегистрированными торговыми марками, торговыми марками или наименованиями продуктов корпорации International Business Machines Corporation или других компаний.

Согласно другому варианту осуществления, процессор 102 основан на архитектуре POWER Architecture (от английского Performance Optimization With Enhanced RISC - оптимизация производительности с применением улучшенной архитектуры RISC), предложенной корпорацией IBM. Одна из реализаций архитектуры POWER Architecture описана в публикации корпорации IBM ″Power ISA™ Version 2.06 Revision В″ от 23 июля 2010 г. POWER ARCHITECTURE® является зарегистрированной торговой маркой корпорации International Business Machines Corporation.

Согласно другому варианту осуществления, процессор 102 основан на архитектуре Intel, предложенной корпорацией Intel. Одна из реализаций архитектуры Intel описана в публикациях ″Intel® 64 and IA-32 Architectures Developer′s Manual: Vol. 2B, Команды Set Reference, A-L″, номер заказа 253666-041 US, декабрь 2011 г. и ″Intel® 64 and IA-32 Architectures Developer′s Manual: Vol. 2B, Команды Set Reference, M-Z″, номер заказа 253667-041 US, декабрь 2011 г. Intel® является зарегистрированной торговой маркой корпорации Intel Corporation, г. Санта-Клара, штат Калифорния, США.

Согласно другому варианту осуществления, схема компьютерного окружения для внедрения и использования одного или более аспектов настоящего изобретения показана на фиг. 2А. В данном примере компьютерное окружение 200 содержит, например, собственное ЦПУ 202, запоминающее устройство 204 и одно или более устройств ввода-вывода и/или интерфейсов 206, соединенных между собой, например, через одну или более шин 208 и/или соединений другого типа. Например, компьютерное окружение 200 может содержать: процессор PowerPC, сервер pSeries или сервер xSeries, предложенные корпорацией International Business Machines Corporation, Армонк, штат Нью-Йорк, США; сервер HP Superdome с процессорами Intel Itanium II, предложенный корпорацией Hewlett Packard Corporation, г. Пало-Альто, штат Калифорния, США; и/или другие электронно-вычислительные машины, основанные на архитектурах, предложенных корпорациями International Business Machines Corporation, Hewlett Packard, Intel, Oracle или другими компаниями и корпорациями.

Собственное ЦПУ 202 содержит один или более собственных регистров 210, таких как один или более регистров общего назначения и/или один или более регистров специального назначения, используемых при выполнении вычислений в компьютерном окружении. Перечисленные регистры содержат информацию, которая отражает состояние компьютерного окружения в каждый отдельно взятый момент времени.

Кроме того, собственное ЦПУ 202 выполняет команды и программный код, которые хранятся в запоминающем устройстве 204. Согласно одному из примеров, ЦПУ выполняет код 212 эмулятора, хранящийся в запоминающем устройстве 204. Этот код позволяет компьютерному окружению, сконфигурированному по одной архитектуре, эмулировать (т.е. имитировать) другую архитектуру. Например, код 212 эмулятора позволяет электронным вычислительным машинам, основанным на архитектурах, отличных от z/Architecture, таким как процессоры PowerPC, серверы pSeries, серверы xSeries, серверы HP Superdome или другим, имитировать архитектуру z/Architecture и выполнять программное обеспечение и команды, разработанные для архитектуры z/Architecture.

Использование кода 212 эмулятора показано более подробно на схеме фиг. 2Б. Гостевые команды 250 содержат команды программного обеспечения (например, машинные команды), которые были разработаны для выполнения на архитектуре, отличной от архитектуры собственного ЦПУ 202. Например, гостевые команды 250 могли быть разработаны для исполнения на процессоре 102, построенном по архитектуре z/Architecture, однако вместо этого эмулируются на собственном ЦПУ 202, которое может быть, например, процессором типа Intel Itanium II. В одном из примеров код 212 эмулятора содержит устройство 252 выборки команд, предназначенное для получения одной или более гостевых команд 250 из запоминающего устройства 204 и, возможно, для выполнения локальной буферизации (временного хранения) полученных команд. Этот код 212 эмулятора также содержит процедуру 254 трансляции команд, предназначенную для определения типа поступившей гостевой команды, и трансляции указанной гостевой команды в одну или более соответствующих собственных команд 256 (т.е. команд, предназначенных для исполнения собственным ЦПУ, построенным по собственной архитектуре). В состав процедуры трансляции входят, например, идентификация функции, которая должна выполняться гостевой командой, и выбор собственной команды или набора команд для выполнения этой функции.

Кроме того, эмулятор 212 содержит процедуру 260 управления эмуляцией, обеспечивающую исполнение собственных команд. Процедура 260 управления эмуляцией может заставить собственное ЦПУ 202 выполнять программу из собственных команд, которая имитирует одну или более ранее поступивших гостевых команд, и по окончании этого вычислительного процесса возвращать управление упомянутой процедуре выборки команд для имитации получения следующей гостевой команды или группы гостевых команд. Процесс выполнения собственных команд 256 может содержать загрузку данных в регистр из запоминающего устройства 204, передачу данных из регистра обратно в запоминающее устройство для хранения или выполнение некоторой арифметической или логической операции в соответствии с указаниями процедуры трансляции.

Каждая процедура реализована, например, в программном обеспечении, которое хранится в запоминающем устройстве и выполняется собственным ЦПУ 202. В других примерах одна или более процедур или операций реализованы в постоянном запоминающем устройстве (ПЗУ), в аппаратном или программном обеспечении или в их комбинации. Упомянутые регистры эмулируемого процессора могут имитироваться с использованием регистров 210 собственного ЦПУ или с использованием пространства памяти запоминающего устройства 204. Согласно вариантам осуществления, гостевые команды 250, собственные команды 256 и код 212 эмулятора могут располагаться в одном и том же запоминающем устройстве или могут храниться распределенно (т.е. в различных запоминающих устройствах).

В рассматриваемом примере ПЗУ хранит, например, микрокод, милликод и/или макрокод процессора. Код содержит, например, команды аппаратного уровня и/или структуры данных, используемые при реализации машинных кодов более высокого уровня. В одном из вариантов осуществления код содержит, например, проприетарный код, который обычно является микрокодом и содержит выверенное программное обеспечение или микрокод, специфический для окружающего аппаратного обеспечения и контролирующий доступ операционной системы к аппаратному обеспечению вычислительной системы.

В одном из примеров загружаемая, транслируемая и исполняемая гостевая команда 250 является одной из описанных в настоящей заявке команд. Такая команда, предназначенная для одной архитектуры (например, для архитектуры z/Architecture), извлекается из запоминающего устройства, транслируется и представляется набором собственных команд 256 другой архитектуры (например, архитектуры PowerPC, pSeries, xSeries, Intel и т.д.). Затем указанные собственные команды исполняются.

Согласно варианту осуществления, описанные команды являются командами векторного типа и являются частью векторного функционала (т.е. векторной среды, набора команд векторного типа и средств их обработки), предоставляемого согласно аспекту настоящего изобретения. Векторный функционал позволяет работать, например, с векторами фиксированной длины в пределах от одного до шестнадцати элементов. Каждый вектор содержит данные, которые обрабатываются векторными командами, определенными в векторном функционале. Согласно варианту осуществления, если вектор образован из набора элементов, то каждый элемент обрабатывается параллельно с другими элементами. Выполнение команды не завершено, пока не завершена обработка всех элементов.

Согласно настоящей заявке, векторные команды могут применяться в составе различных архитектур, в том числе (но не ограничиваясь) z/Architecture, Power, Intel и т.д. Несмотря на то, что описываемый в настоящей заявке вариант осуществления ориентирован на архитектуру z/Architecture, векторные команды и один или более аспектов настоящего изобретения могут базироваться и предназначаться для многих других типов архитектур. Архитектура z/Architecture используется исключительно в качестве одного из примеров.

Согласно варианту осуществления, по которому векторный функционал реализован как часть архитектуры z/Architecture, для того, чтобы использовать векторные регистры и команды, в специализированном управляющем регистре (например, управляющем регистре 0) флаги разрешения векторного функционала и векторных регистров должны быть установлены в состояние, например, логической единицы. Если векторный функционал инсталлирован, и векторная команда выполняется без разрешающих флагов, то возникает программное исключение (ошибка) данных. Если же векторный функционал не инсталлирован, и делается попытка выполнить векторную команду, то возникает программное исключение (ошибка) исполнения.

Векторные данные располагаются в запоминающем устройстве, например, в той же самой последовательности, слева направо, как и прочие форматы данных. Разряды формата данных с номерами от 0 до 7 образуют байт в крайней левой (с наименьшим номером) ячейке хранения байтов пространства памяти; разряды с номерами от 8 до 15 образуют байт в следующей за предыдущей ячейке памяти и т.д. В другом примере векторные данные могут располагаться в пространстве памяти запоминающего устройства в иной последовательности, например, справа налево.

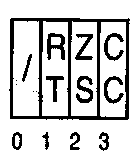

Многие векторные команды, поддерживаемые векторным функционалом, снабжены полем, состоящим из специальных разрядов. Такое поле, называемое полем RXB (от английского register extension bit - бит расширения регистра), содержит наиболее значимый разряд для обозначений (т.е. для адресов) векторных регистров операндов. Разряды обозначений векторных регистров операндов, не оговоренные спецификацией команды, являются зарезервированными и должны быть установлены в состояние логического нуля.

Согласно варианту осуществления, поле RXB состоит из четырех разрядов (например, с номерами от 0 до 3), и значения этих разрядов имеют следующее назначение:

разряд 0 - наиболее значимый разряд обозначения векторного регистра первого операнда;

разряд 1 - наиболее значимый разряд обозначения векторного регистра второго операнда, если такой операнд и соответствующий регистр предусмотрены командой;

разряд 2 - наиболее значимый разряд обозначения векторного регистра третьего операнда, если такой операнд и соответствующий регистр предусмотрены командой;

разряд 3 - наиболее значимый разряд обозначения векторного регистра четвертого операнда, если такой операнд и соответствующий регистр предусмотрены командой.

Каждый разряд устанавливается в состояние логического нуля или логической единицы, например, ассемблером, в зависимости от номера регистра. Например, в регистрах с номерами от 0 до 15 разряд устанавливается в состояние логического нуля, в регистрах с номерами от 16 до 31 разряд устанавливается в состояние логической единицы и т.д.

Согласно варианту осуществления, каждый разряд поля RXB является разрядом расширения определенного поля в составе команды, указывающего на один или более векторных регистров. Например, в одной или более векторных командах разряд с номером 0 поля RXB служит разрядом-расширением части команды с номерами позиций от 8 до 11, эта часть команды обозначается, например, как V1; разряд с номером 1 поля RXB служит разрядом-расширением части команды с номерами позиций от 12 до 15, эта часть команды обозначается, например, как V2, и т.д.

Согласно другому варианту осуществления, поле RXB содержит дополнительные разряды, и для указания на каждый вектор или регистр в качестве разрядов-расширений используются по два и более разрядов.

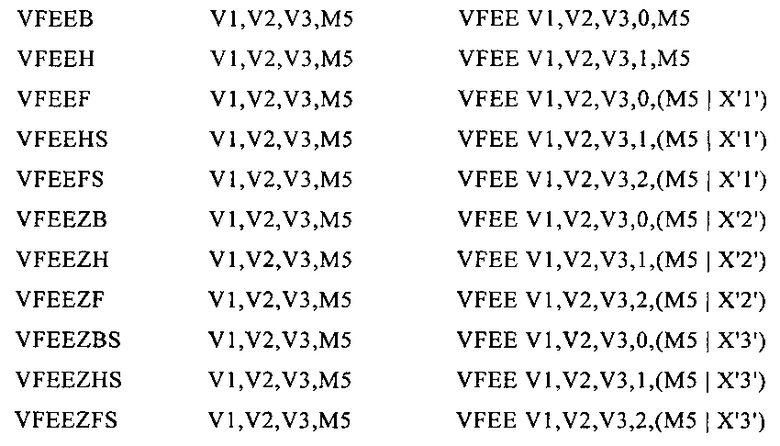

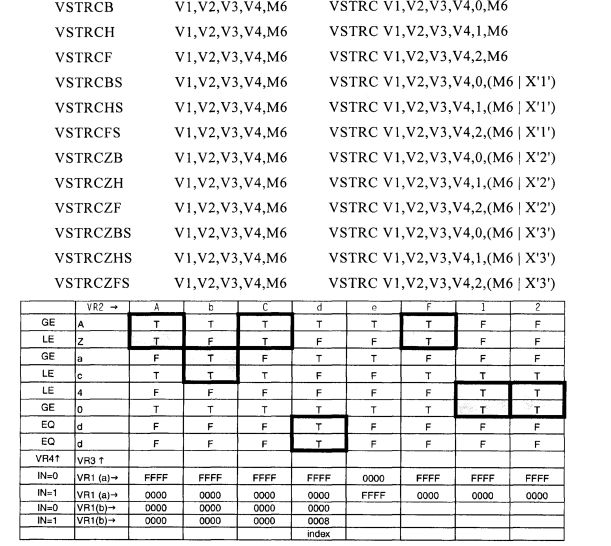

Согласно аспекту настоящего изобретения, одной из команд, содержащих поле RXB, является команда векторного типа для поиска неравнозначного элемента, структура (схема формата) которой показана на фиг. 3. В одном из примеров команда 300 векторного типа для поиска неравнозначного элемента содержит: поля кода операции 302а (например, разряды с номерами 0-7) и 302b (например, разряды 40-47), идентифицирующие операцию векторного типа для поиска неравнозначного элемента; поле 304 первого векторного регистра (например, разряды 8-11), используемое для обозначения первого векторного регистра (V1); поле 306 второго векторного регистра (например, разряды 12-15), используемое для обозначения второго векторного регистра (V2); поле 308 третьего второго векторного регистра (например, разряды 16-19), используемое для обозначения третьего векторного регистра (V3); поле 310 первой маски (М5) (например, разряды 24-27); поле 312 второй маски (М4) (например, разряды 32-35); поле 314 RXB (например, разряды 36-39). В одном из вариантов осуществления каждое из полей 304-314 является отдельным и независимым от поля (полей) кода оптации. Кроме того, согласно другому варианту осуществления, указанные поля являются отдельными и независимыми между собой; однако согласно другим вариантам осуществления, два и более полей могут быть объединенными. Далее приводятся сведения об использовании перечисленных полей.

Согласно варианту осуществления, определенные разряды (например, первые два разряда) кода операции из состава поля 302а кода операции определяют длину и формат команды. В рассматриваемом примере двоичное число в указанных разрядах означает, что длина составляет три полуслова и что формат - операция типа векторный регистр и регистр, с расширенным кодом операции. Каждое из векторных (V) полей совместно с соответствующим разрядом расширения регистра, содержащимся в поле RXB, обозначает некоторый векторный регистр. В частности, векторный регистр, содержащий операнд, обозначается (адресуется) с использованием, например, четырехразрядного поля обозначения регистра и разряда RXB как наиболее значимого. Например, если четырехразрядное поле содержит двоичное число 0110, и в разряде расширения содержится двоичное число 0, то пятиразрядное число 00110 указывает на регистр с номером 6 в десятичной системе счисления.

Нижний индекс в обозначении поля команды соответствует номеру операнда, к которому это поле относится. Например, нижний индекс ″1″ в обозначении ″V1″ векторного регистра указывает на соответствие регистра первому операнду и т.д. Операнд регистра имеет ту же длину, что и сам регистр, например, 128 бит.

Поле М4, состоящее, например, из четырех разрядов с номерами от 0 до 3, описывает спецификатор длины элемента, например, с помощью разрядов с 1-го по 3-й. Спецификатор длины элемента задает длину элементов операндов векторного регистра. Например, спецификатор длины элемента задает длину элемента равной одному байту, полуслову (например, два байта) или слову (например, четыре байта). Например, значение 0 обозначает длину в один байт, 1 обозначает полуслово, 2 - слово, называемое также полным словом. Если в поле использовано зарезервированное значение, то возникает программное исключение (ошибка) спецификации.

Поле М5 является, например, четырехразрядным, и его разряды с номерами от 0 до 3 имеют, например, следующие значения:

разряд 2 - поле флага ZS (от английского zero search - поиск нуля) поиска нуля: значение 1 указывает, что каждый элемент второго операнда дополнительно сравнивается с нулем (в следующем примере каждый элемент третьего операнда или иного операнда сравниваемого с нулем);

разряд 3 - поле флага СС (от английского condition code - код условия) установки кода условия: значение 0 указывает, что установка кода условия не требуется, значение кода условия остается неизмененным; значение 1 указывает, что код условия устанавливается, например, по следующему правилу:

значение 0: если флаг ZS поиска нуля установлен, то сравнение выявило в обоих операндах элемент с нулевым значением, и индекс этого элемента меньше, чем индекс неравнозначного элемента;

значение 1: сравнение выявило несовпадение некоторого элемента второго операнда с элементом третьего операнда, причем значение элемента V2 меньше значения элемента V3;

значение 2: сравнение выявило несовпадение некоторого элемента второго операнда с элементом третьего операнда, причем значение элемента V2 больше значения элемента V3;

значение 3: значения всех элементов совпадают. Если установлен флаг ZS поиска нуля, то во втором операнде (либо, согласно другому варианту осуществления, в других операндах) не выявлено элементов с нулевыми значениями.

Согласно одному из вариантов осуществления, при выполнении команды векторного типа для поиска неравнозначного элемента в направлении, по одному из вариантов осуществления, слева направо, беззнаковые целые двоичные элементы второго операнда (содержащиеся в регистре, определяемом значением поля V2 и соответствующим разрядом RXB) сравниваются с соответствующими им беззнаковыми целыми двоичными элементами третьего операнда (содержащимися в регистре, определяемом значением поля V3 и соответствующим разрядом RXB). Если два элемента в паре неравны (т.е. их значения различаются), то индекс первого байта крайнего левого неравного элемента помещается в специально предназначенный байт (например, в байт 7) первого операнда (содержащегося в регистре, определяемом значением поля V и соответствующим разрядом RXB). В оставшиеся байты первого операнда записываются нули.

В одном из вариантов возвращаемый (т.е. сохраняемый в определенном байте) индекс байта элемента является индексом первого байта крайнего левого неравнозначного элемента. Например, если длина элемента составляет один байт, то возвращается индекс байта крайнего левого неравнозначного элемента (например, если имеются 16 элементов с номерами от 0 до 15, и не совпадает элемент с номером 6, то возвращается значение 6 индекса байта). Аналогично, если длина элемента составляет полуслово, имеются восемь элементов с номерами от 0 до 7, и не совпадает один из байтов третьего элемента с номерами 6 и 7, то возвращается значение 6 индекса байта. Если же длина элемента составляет полное слово, имеются четыре элемента с номерами от 0 до 3, и один из байтов, с 4-го по 7-й, первого элемента не совпадает, то возвращается значение 4 индекса байта.

Если в поле M5 значение флага установки кода условия установлено равным, например, единице, то устанавливается код условия для указания, элемент какого из операндов имеет большее значение (если были выявлены неравнозначные элементы). Т.е. двоичный целый эквивалент, например, буквенного символа второго операнда сравнивается с двоичным целым эквивалентом неравнозначного буквенного символа третьего операнда, в результате чего устанавливается значение кода условия. Если все элементы совпали, то в специально предназначенный байт (например, в байт 7) первого операнда записывается значение индекса байта, равное длине вектора (в байтах, например, 16). В оставшиеся байты первого операнда записываются нули. При этом если значение флага установки кода условия равно единице, то устанавливается соответствующий код условия (например, значение 3).

Если в поле М5 установлен флаг поиска нуля, то каждый элемент второго операнда (либо, согласно другому варианту осуществления, третьего операнда или иного операнда) дополнительно проверяется на предмет равенства нулю (т.е. пустому элементу, символу окончания, символу конца строки). Если во втором операнде равный нулю элемент обнаружен прежде, чем выявлено несовпадение какого-либо иного элемента операнда, то в специально предназначенный байт (например, в байт 7) первого операнда записывается индекс первого байта равного нулю элемента. Во все прочие элементы первого операнда записываются нули и устанавливается соответствующее значение кода условия (например, значение ноль).

Согласно варианту осуществления, сравнение элементов ведется в параллельном режиме. Например, если сравниваемые векторные регистры имеют длину 16 байтов, то одновременно сравниваются 16 байтов. Согласно другому варианту осуществления, кроме того, во время исполнения задается направление векторов: слева направо или справа налево. Например, команда обращается к регистру, флагу состояния или другому объекту, который указывает направление обработки: например, либо слева направо, либо справа налево. Согласно варианту осуществления, указатель направления не встроен жестко в саму команду, он сообщается команде во время выполнения.

Согласно другому варианту осуществления, команда не содержит поле RXB: расширение не используется вовсе или расширение организовано иным способом, например, по внешнему по отношению к команде указанию, или же расширение содержится в другом поле той же команды.

Дальнейшие сведения об одном из вариантов осуществления команды векторного типа для поиска неравнозначного элемента поясняются схемой на фиг. 4. В одном из примеров процессор компьютерного окружения выполняет следующий алгоритм.

Вначале на шаге 400 принимается решение о том, должен ли быть выполнен поиск нуля (так называемого нулевого элемента, конца строки, символа окончания и т.п.). Если поиск нуля должен быть выполнен, то на шаге 402 выполняется сравнение с нулевыми символами, т.е. поиск равных нулю элементов, результат поиска присваивается выходной переменной nullidx (от английского null index - индекс нулевого символа) 403. Например, если длина элемента - байт, и в пятом байте найден равный нулю элемент, то индекс этого байта (например, 5) помещается в nullidx. Аналогично, если длина элемента составляет полуслово, имеются восемь элементов с номерами от 0 до 7, и значение третьего элемента (т.е. байты с номерами 6 и 7) равно нулю, то в nullidx помещается значение 6 (соответствует индексу байта 6). Аналогично, если длина элемента составляет полное слово, имеются четыре элемента с номерами от 0 до 3, и значение первого элемента (т.е. байты с 4-го по 7-й) равно нулю, то в nullidx помещается значение 4 (соответствует индексу байта 4). Если равный нулю элемент не выявлен, то согласно одному из примеров в nullidx помещается значение, равное длине вектора (например, в байтах; например, 16).

Кроме того, или даже если поиск нуля не должен выполняться, то на шаге 404 в параллельном режиме выполняется множество (например, 16) операций, состоящих в сравнении А и В операцией сравнения. В одном из примеров А - содержимое второго операнда, В - содержимое третьего операнда, и операция сравнения - неравенство.

Результат сравнения присваивается переменной 406, называемой либо левым индексом, cmpidxl (от английского comparison index left - индекс сравнения слева), либо правым индексом, cmpidxr (от английского comparison index right - индекс сравнения справа) в зависимости от того, в каком направлении велся поиск: слева или справа. Например, если операция сравнения - неравенство, поиск велся слева направо, а сравнение выявило одно или более несовпадений, то значение индекса, связанное с первым байтом младшего из различающихся элементов, помещается в cmpidxl. Например, если длина элемента - байт, вектор состоит из 16 элементов (с номерами от 0 до 15) и выявлено неравенство в элементе с номером 6, то в переменной cmpidxl сохраняется значение 6. Аналогично, если длина элемента - полуслово, вектор состоит из восьми элементов (с номерами от 0 до 7) и выявлено равенство в элементе с номером 3 (например, в байтах 6 и 7), то возвращается индекс первого байта данного элемента (т.е. значение 6). Аналогично, если длина элемента - полное слово, вектор состоит из четырех элементов (с номерами от 0 до 3) и выявлено равенство в элементе 1 (т.е. в байтах с 4-го по 7-й), то возвращается индекс первого байта данного элемента (т.е. значение 4). Если различий не выявлено, то согласно варианту осуществления переменной cmpidxl или cmpidxr (в зависимости от направления поиска) присваивается значение, равное длине вектора (например, в байтах; например, значение 16).

Затем на шаге 408 принимается решение, велся ли поиск слева или справа. Если поиск велся слева, то на шаге 410 переменной cmpidx присваивается значение cmpidxl, в противном случае на шаге 412 переменной cmpidx присваивается значение переменной cmpidxr.

После присвоения значения переменной cmpidx принимается решение, велся ли поиск нуля - шаг 414. Если поиск нуля не велся, то на шаге 416 переменной idx (от английского index - индекс) присваивается значение cmpidx. Если поиск нуля велся, то на шаге 418 переменной idx присваивается минимальное из значений индекса сравнения и индекса нуля (т.е. nullidx). Этим шагом работа алгоритма заканчивается.

На фиг. 5 показана схема, поясняющая выполнение операций по алгоритму, показанному на фиг. 4. В данном примере имеются два входных блока данных, вектор В 500 и вектор А 502. Оба этих вектора поступают на операцию 504 сравнения, которая выполняет сравнение (например, поиск неравенства) в параллельном режиме. Кроме того, один из входных векторов, а именно вектор А, поступает также на операцию 506 поиска нулевых символов.

Результаты работы операций сравнения - значение 508 переменных idxL или idxR, а также результат операции поиска нуля - значение 510 переменной nullidx поступают в процедуру 512 определения результата. Процедура 512 также принимает значения следующих управляющих переменных (флагов): справа/слева 514, указывающей направление поиска; поиск нуля 516, показывающей, велся ли поиск нуля; длина элемента 518, указывающей длину каждого элемента векторов (например, байт, полуслово, полное слово). Процедура 512 формирует результат обработки - значение переменной resultidx (от англ.: индекс-результат) 520, которое сохраняется в выходном векторе 522 (например, в его седьмом байте).

Процедура 512 определения результата также содержит операцию 523 обработки кода условия, которая опционально формирует код 524 условия.

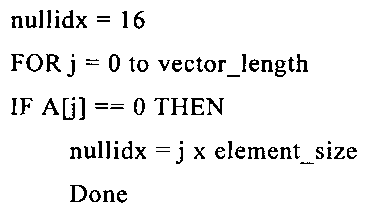

Пример псевдокода операции 504 сравнения:

Из данного примера видно, что переменные idxL или idxR (их имена соответствуют направлению поиска) инициализируются значением длины вектора (выраженным, например, в байтах; например, инициализируются значением 16). Затем каждый элемент вектора А сравнивается с соответствующим элементом вектора В. В одном из примеров сравнение ведется побайтно, так что сравнение выполняется для каждого i-го из шестнадцати байтов. В данном примере операция сравнения - неравенство, и если выявлено различие байтов, то при поиске в направлении слева направо значение индекса отличающегося байта присваивается переменной idxL, а при поиске в направлении справа налево значение индекса отличающегося байта присваивается переменной idxR.

Пример псевдокода операции 506 поиска нуля:

Из приведенного примера видно, что каждый j-й элемент вектора проверяется на предмет равенства его значения нулю. Если элемент равен нулю, то переменной nullidx присваивается значение индекса этого элемента, умноженное на длину элемента. Например, если длина элемента составляет полуслово (т.е. два байта) и в элементе 3 выявлен нулевой символ, то 3 умножается на 2, и переменной nullidx присваивается значение 6, что соответствует номеру байта 6. Аналогично, если длина элемента составляет полное слово (т.е. четыре байта), и в элементе 3 выявлен нулевой символ, то 3 умножается на 4, и переменной nullidx присваивается значение 12.

Пример псевдокода процедуры 512 определения результата:

ELSE значение CC не изменять

Из данного примера видно, что если переменная-флаг Left/Right направления поиска указывает направление поиска слева направо, то переменной cmpidx присваивается значение переменной idxL, в противном случае переменной cmpidx присваивается значение idxR. Далее, если переменная-флаг поиска нуля zero_detect находится в активном состоянии, то переменной resultidx присваивается минимальное из значений переменных cmpidx и nullidx. Затем, если переменная SetCC, т.е. флаг СС установки кода условия находится в активном состоянии, и значение переменной cmpidx превышает значение переменной nullidx, то переменной СС значения кода условия присваивается значение ноль. В противном случае (т.е. если поиск нуля не выполнялся) переменной resultidx присваивается значение cmpidx.

Затем: если длина элемента составляет байт, то маска element_size_mask длины элемента устанавливается в состояние 11111; если длина элемента составляет два байта, то маска длины элемента устанавливается в состояние НПО; если длина элемента составляет четыре байта, то маска длины элемента устанавливается в состояние 11100.

Далее переменной resultidx присваивается ее же значение (resultidx), логически умноженное на маску длины элемента. Например, если длина элемента составляет полуслово, и переменная resultidx содержит значение 7 индекса байта, то операция resultidx=00111 AND 11110 (AND - обозначение операции поразрядное логическое И) выдает значение 00110. В результате переменной resultidx присваивается значение 6 (т.е. 00110 в двоичной системе счисления), что совпадает с номером первого байта элемента.

Кроме того, опционально может устанавливаться код условия. Код условия устанавливается, если флаг установки кода условия в команде имеет активное значение, в противном случае код условия не устанавливается. Например, если флаг установлен, то при resultidx =16 коду условия присваивается значение 3; в противном случае если значение элемента вектора А с индексом resultidx меньше значения элемента вектора В с индексом resultidx, то коду условия присваивается значение 1, иначе коду условия присваивается значение 2.

Выше был рассмотрен пример векторной команды, используемой для повышения эффективности обработки символьных данных. Далее показано, как для 128-разрядного вектора процедура сравнения выполняет 16 сравнений байтов вместо, например, 256 сравнений, что дает возможность масштабировать более длинные векторы. Также показано, что направление сравнения (слева/справа) может задаваться во время исполнения, а не кодироваться внутри команды. Далее указывается, что возвращаемая в результате переменная содержит позицию байта, а не индекс элемента. Затем показано, что поддерживаются однобайтные, двухбайтные и четырехбайтные сравнения.

Согласно варианту осуществления, опционально, по указанию, поступающему вместе с командой, формируется код условия. Введение возможности не формировать код условия повышает эффективность планирования выполнения команды.

Согласно другому варианту осуществления, поиск нуля производится не в результате проверки условия, а каждый раз при выполнении команды векторного типа для поиска неравнозначного элемента. Процедура поиска нуля, выполняемая в зависимости от проверки условия или всякий раз при исполнении команды, возвращает позицию (например, индекс байта) равного нулю элемента и/или позицию (например, индекс байта) первого различающегося элемента.

Согласно одному из вариантов осуществления, число выполняемых сравнений для команды векторного типа для поиска неравнозначного элемента независимо от осуществления соответствует числу байтов в векторе. Например, если длина вектора, в котором ведется поиск или сравнение, составляет 16 байтов, то выполняется не более шестнадцати сравнений, например, в параллельном режиме. В другом варианте осуществления при обнаружении несовпадающего или равного нулю элемента процедура сравнения прекращается.

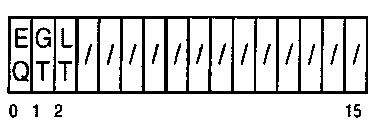

Согласно варианту осуществления, имеются 32 векторных регистра, а регистры других типов могут отображаться на область-квадрант векторных регистров. Как показано в примере на фиг.6, если имеется файл 600 регистров, содержащий 32 векторных регистра 602 длиной 128 разрядов каждый, то шестнадцать регистров 604 с плавающей запятой длиной 64 разряда каждый могут перекрываться с векторными регистрами. Таким образом, например, если изменится содержимое регистра 2 с плавающей запятой, то содержимое векторного регистра 2 также изменится. Для регистров других типов возможны и другие типы отображений.

В настоящей заявке термины ″запоминающее устройство″, ″главное запоминающее устройство″, ″пространство памяти″, ″главная память″ (первичная память, т.е. ближайший к ЦПУ уровень иерархии запоминающих устройств, быстродействующие запоминающие устройства, напрямую адресуемые ЦПУ: регистры и кэш-память процессора, а также ОЗУ и системное ПЗУ) используются взаимозаменяемо, если иное не указывается явно или не следует из контекста.

Далее как часть настоящего подробного описания осуществления изобретения приводятся дополнительные сведения, относящиеся к векторному функционалу, в том числе примеры иных команд.

Специалисту в данной области должно быть понятно, что один или более аспектов настоящего изобретения могут быть воплощены в форме системы, способа или компьютерного программного продукта. Соответственно, один или более аспектов настоящего изобретения могут быть осуществлены в виде чисто аппаратного обеспечения, чисто программного обеспечения (в том числе, в виде программы, записанной в ПЗУ, резидентного программного обеспечения, микрокода и т.п.) или в виде комбинации аппаратного и программного обеспечения; для обозначения всех этих вариантов в настоящей заявке могут в общем использоваться термины ″схема″, ″модуль″ или ″система″. Кроме того, один или более аспектов настоящего изобретения могут принимать форму компьютерного программного продукта, осуществленного на одной или более машиночитаемых средах, содержащих машиночитаемый программный код.

Может использоваться любая комбинация одной или более машиночитаемых сред. Машиночитаемой средой может являться машиночитаемая среда хранения данных. Машиночитаемой средой хранения данных может быть, в том числе (но не ограничиваясь): электронная, магнитная, оптическая, электромагнитная, инфракрасная или проводная система, средство, или устройство, или любая работоспособная комбинация перечисленных сред. Более специфическими примерами машиночитаемых сред хранения данных могут быть, в том числе (но не ограничиваясь): электрическое соединение, содержащее один или более проводников; портативная компьютерная дискета (накопитель на гибких дисках); накопитель на жестких дисках; оперативное запоминающее устройство (ОЗУ); ПЗУ; стираемое программируемое постоянное запоминающее устройство (СППЗУ) или флеш-память; оптоволокно; CD-ROM (от английского Compact Disc Read Only Memory - постоянное запоминающее устройство на компакт-диске); оптическое запоминающее устройство; магнитное запоминающее устройство; любая работоспособная комбинация перечисленных сред. Применительно к настоящей заявке машиночитаемой средой хранения данных может являться любая материальная среда, которая может содержать или хранить программу для использования или коммуникационное соединение с системой, средством или устройством, способным выполнять команды.

На фиг. 7 в одном из примеров компьютерный программный продукт 700 содержит, например, одну или более нестираемых машиночитаемых сред 702 хранения данных. Эта среда(среды) 702 предназначены для хранения средств или логики 704 машиночитаемого программного кода для предоставления и облегчения использования одним или более аспектами настоящего изобретения.

Программный код, хранящийся на машиночитаемой среде, может быть передан с использованием соответствующей среды, содержащей в том числе (но не ограничиваясь) беспроводную, проводную, кабельную оптоволоконную, радиочастотную и т.п. среду или любую работоспособную комбинацию перечисленных сред.

Компьютерный программный код для выполнения операций одного или более аспектов настоящего изобретения может быть написан на одном или любой комбинации нескольких языков программирования, в том числе на языках объектно-ориентированного программирования, таких как Java, Smalltalk, С++ или подобных, и на обычных языках процедурного программирования, таких как язык ″С″, ассемблера или подобных им языках программирования. Программный код может выполняться: полностью на компьютере пользователя; частично на компьютере пользователя как автономный программный пакет; частично на компьютере пользователя и частично на удаленном компьютере; полностью на удаленном компьютере или сервере. В приведенном далее сценарии удаленный компьютер может быть соединен с компьютером пользователя через коммуникационную сеть любого типа, в том числе локальную вычислительную сеть (ЛВС) или глобальную сеть связи, либо может быть реализовано соединение с внешним компьютером (например, через сеть Интернет при посредничестве поставщика услуг Интернет).

Один или более аспектов настоящего изобретения описываются в настоящей заявке с использованием изображений схем алгоритмов и/или структурных схем способов, средств (систем) и компьютерных программных продуктов согласно вариантам осуществления изобретения. Должно быть понятно, что каждая операция на чертежах схем алгоритмов и/или структурных схем, а также комбинации операций на чертежах схем алгоритмов и/или структурных схем могут быть реализованы командами компьютерной программы. Эти команды компьютерной программы могут выполняться процессором универсального компьютера, специализированного компьютера или иными средствами обработки данных с программным управлением, образующими машину (вычислительное устройство), таким образом, что команды, выполняемые процессором компьютера или иными средствами обработки данных с программным управлением, формируют среду для осуществления функций (действий), описанных схемой алгоритма и/или операцией или операциями структурной схемы.

Указанные команды компьютерной программы могут также храниться в машиночитаемой среде и могут заставлять компьютер, иное средство обработки данных с программным управлением или иные устройства действовать определенным образом, чтобы команды, хранящиеся в машиночитаемой среде, образовывали программное изделие, в том числе, реализующее команды, которые осуществляют функцию или действуют в соответствии со схемой алгоритма, и/или операцию или операции, показанные на структурных схемах.

Команды компьютерной программы могут также быть загружены в компьютер, иное средство обработки данных с программным управлением или иные устройства для выполнения последовательности операций компьютером, иным средством обработки данных с программным управлением или другими устройствами для организации вычислительного процесса, в результате которого команды, выполняемые на компьютере или ином средстве обработки данных с программным управлением, реализуют процессы для осуществления функции или действия в соответствии со схемой алгоритма и/или операцию или операции, показанные на структурных схемах.

Схемы алгоритмов и структурные схемы, показанные на чертежах, иллюстрируют архитектуру, функциональность и действие возможных вариантов осуществления систем, методов и компьютерных программных продуктов согласно различным вариантам осуществления одного или более аспектов настоящего изобретения. С учетом этого каждая операция (блок) на схемах алгоритмов или структурных схемах может представлять модуль, сегмент или фрагмент кода, содержащий одну или более исполнимых команд для осуществления определенной логической функции или функций. Следует также заметить, что в некоторых альтернативных вариантах осуществления функции, указанные в блоках, могут выполняться в иной последовательности, чем показано на прилагаемых чертежах. Например, две операции, показанные следующими одна за другой, могут фактически выполняться по существу одновременно, либо иногда операции могут выполняться в обратном порядке в зависимости от имеющихся функциональных возможностей. Также далее будет показано, что каждая операция на изображениях структурных схем и/или схем алгоритмов и каждая комбинация операций на изображениях структурных схем и/или схем алгоритмов может быть реализована специализированными аппаратными системами, которые выполняют определенные функции или действия, или комбинациями специализированного аппаратного обеспечения и компьютерных команд.

Кроме того, один или более аспектов настоящего изобретения могут предоставляться, предлагаться, размещаться, администрироваться, обслуживаться и т.п. поставщиком услуг, который предлагает администрирование пользовательских сред. Например, поставщик услуг может создать, поддерживать, обслуживать и т.п. компьютерный код и/или компьютерную инфраструктуру, которая воплощает один или более аспектов настоящего изобретения для одного или более пользователей. За это поставщик услуг может получать от потребителя плату, например, в соответствии с подпиской на услуги и/или договором об оплате. Кроме того или вместо того, поставщик услуг может получать плату от продажи или рекламы от третьих лиц.

Согласно варианту осуществления настоящего изобретения, для реализации одного или более аспектов настоящего изобретения может использоваться приложение (программное обеспечение). Как один из примеров, реализация приложения включает, в том числе, создание компьютерной инфраструктуры, позволяющей осуществить один или более аспектов настоящего изобретения.

Согласно другому варианту осуществления настоящего изобретения, вычислительная инфраструктура может быть организована встраиванием объединяющего машиночитаемого кода в вычислительную систему, и их комбинация позволяет осуществить один или более аспектов настоящего изобретения.

Согласно другому варианту осуществления настоящего изобретения, может быть предусмотрен порядок объединения вычислительной инфраструктуры, содержащий встраивание машиночитаемого кода в компьютерную систему. Компьютерная система имеет в своем составе машиночитаемую среду, которая содержит один или более аспектов настоящего изобретения. Указанный код совместно с компьютерной системой позволяют осуществить один или более аспектов настоящего изобретения.

Следует учитывать, что описанные выше различные варианты осуществления являются всего лишь примерами. Например, один или более аспектов настоящего изобретения могут содержаться в составе и использоваться вычислительными средами, построенными по иной архитектуре. Кроме того, могут использоваться векторы иных длин или другие регистры, а в команды могут вноситься изменения, что не приводит к выходу за пределы сущности настоящего изобретения. Кроме того, могут использоваться регистры, тип которых отличается от векторного типа, и/или тип данных может отличаться от символьного, например, быть целым или каким-либо иным.

Кроме того, преимущества от одного или более аспектов настоящего изобретения могут получить другие типы вычислительных сред. Пример подобной среды - система обработки данных, предназначенная для хранения и/или выполнения программного кода, которая содержит по меньшей мере два процессора, соединенных непосредственно или опосредованно с элементами запоминающего устройства через системную шину. Элементы запоминающего устройства содержат, например: локальное запоминающее устройство, используемое при фактическом выполнении программного кода; устройство массовой памяти (запоминающее устройство большого объема); кэш-память (быстродействующее буферное запоминающее устройство для временного хранения информации с целью повышения быстродействия вычислительной системы), обеспечивающую временное хранение по меньшей мере фрагмента программного кода для сокращения числа обращений к устройству массовой памяти для извлечения кода за интервал времени исполнения.

К системе либо непосредственно, либо через промежуточные контроллеры ввода-вывода могут быть подключены устройства ввода-вывода, в том числе (но не ограничиваясь) клавиатура, дисплеи, указательные устройства, запоминающее устройство с прямым доступом, ленточные накопители, CD-ROM, DVD-ROM (от английского Digital Video Disc Read-Only Memory - постоянное запоминающее устройство на цифровом видеодиске), внешние отключаемые запоминающие устройства и прочие запоминающие устройства. Для соединения системы обработки данных с другими системами обработки данных или удаленными принтерами или запоминающими устройствами через промежуточные приватные или публичные сетевые подключения к системе могут подключаться сетевые адаптеры. Примерами сетевых адаптеров могут служить, в том числе, телефонные модемы, кабельные модемы, платы адаптеров сети Ethernet.

На фиг. 8 представлены характерные компоненты хост-компьютерной системы 5000 для осуществления одного или более аспектов настоящего изобретения. Характерный хост-компьютер 5000 содержит одно или более ЦПУ 5001, соединенных линиями передачи данных с запоминающим устройством компьютера (т.е. с центральным запоминающим устройством) 5002, а также с интерфейсами ввода-вывода запоминающих устройств 5011 и сетей 5010 для связи с другими компьютерами или сетями хранения данных (специализированными высокоскоростными сетями, объединяющими устройства хранения данных и серверы) и т.п. ЦПУ 5001 совместимо с архитектурой, обладающей собственным набором команд и функциональными возможностями. ЦПУ 5001 может обладать средством 5003 динамического преобразования адресов для преобразования адресов, использующихся в программах (виртуальных адресов) в реальные адреса запоминающего устройства. Динамическое преобразование адресов обычно содержит буфер 5007 ассоциативной трансляции для кэширования (временного хранения) результатов трансляции, благодаря чему последующие обращения к блоку памяти центрального запоминающего устройства 5002 не приведут к задержке трансляции адресов. Как правило, кэш-память 5009 может быть организована иерархически, т.е. содержать большую по объему часть, доступную более чем одному ЦПУ, и меньшую по объему, более быстродействующую (более низкого уровня) часть, служащую буфером между большей частью кэш-памяти и каждым ЦПУ. В некоторых вариантах осуществления кэш-память более низкого уровня разделяется для организации нескольких низкоуровневых пространств кэш-памяти для выборки команд и доступа к данным. Согласно варианту осуществления, команда выбирается из запоминающего устройства 5002 устройством 5004 выборки команд через кэш-память 5009. Указанная команда декодируется в устройстве 5006 декодирования команд и направляется (в некоторых вариантах осуществления - совместно с другими командами) в устройство или устройства 5008 выполнения команд. Как правило, используются несколько устройств 5008 выполнения команд, например арифметическое устройство, устройство выполнения операций с плавающей запятой, устройство ветвления команд. Команда, выполняемая исполнительным устройством, по мере необходимости обращается к операндам команды, указанным регистрам или запоминающему устройству. Если требуется доступ (загрузка или хранение) к операндам из запоминающего устройства 5002, то доступ контролируется устройством 5005 загрузки-хранения под управлением выполняемой команды. Команды могут выполняться в аппаратных схемах или с помощью внутреннего микрокода (хранящегося в ПЗУ) или комбинацией этих двух способов.

Как было указано, в состав компьютерной системы входит информация, хранящаяся в локальном (или главном) запоминающем устройстве, а также средства адресации, защиты, ссылок и учета изменений. Некоторые варианты правил адресации содержат формат адресов, концепцию адресных пространств, различные типы адресов, а также способ, по которому адреса одного типа преобразуются в адреса другого типа. Часть главного запоминающего устройства содержит постоянно выделенные области памяти. Главное запоминающее устройство обеспечивает системе быстродействующее хранение данных с прямой адресацией. И данные, и программы должны быть загружены из устройств ввода в главное запоминающее устройство перед тем, как смогут быть обработаны.

Главное запоминающее устройство может содержать одно или более буферных запоминающих устройств меньшего объема с более быстрым доступом, которые иногда называются устройствами кэш-памяти. Устройство кэш-памяти обычно физически связано с ЦПУ или процессором ввода-вывода. Различия в физическом устройстве и использовании различных типов запоминающих устройств обычно незаметны для программы (за исключением различия в быстродействии).

Для операций с командами и данными могут использоваться отдельные устройства кэш-памяти. Информация в устройствах кэш-памяти содержится в виде непрерывной последовательности байтов в пределах целостного пространства памяти, называемого блоком данных кэш-памяти или строкой данных кэш-памяти (коротко - строкой). Модель может сформировать команду EXTRACT CACHE ATTRIBUTE (от англ.: получить атрибут кэш-памяти), которая возвращает длину строки кэш-памяти в байтах. Также модель может сформировать команды PREFETCH DATA и PREFETCH DATA RELATIVE LONG, которые влияют на выборку данных из запоминающего устройства в кэш-память данных или команд или на удаление данных из кэш-памяти.

Пространство памяти запоминающего устройства представляется в виде протяженных горизонтально ориентированных строк двоичных символов. Для большинства операций доступ к запоминающему устройству выполняется в последовательности слева направо. Строки двоичных символов подразделяются на группы по восемь бит. Группа из восьми бит называется байтом, байт является основным образующим элементом всех форматов представления информации. Каждое местоположение байта в запоминающем устройстве обозначается уникальным неотрицательным целым числом, называемым адресом местоположения данного байта или коротко - адресом. Адресация ячеек памяти - последовательная, т.е. адреса соседних ячеек хранения байтов отличаются на единицу. Адреса начинаются с нуля для крайней левой ячейки и возрастают слева направо. Адреса - беззнаковые двоичные целые числа длиной 24, 31 или 64 разряда.

Информация передается между запоминающим устройством и ЦПУ или подсистемой канала передачи данных по одному байту или по группе байтов в один момент времени. Если иное не оговорено, то, например, в архитектуре z/Architecture группа байтов в запоминающем устройстве адресуется по крайнему левому байту группы. Число байтов в группе либо определено заранее, либо однозначно указывается выполняемой операцией. В операциях с ЦПУ группа байтов называется полем. Внутри каждой группы байтов, например, в архитектуре z/Architecture, биты нумеруются в направлении слева направо. В архитектуре z/Architecture крайние левые биты иногда называют старшими, крайние правые биты - младшими. Следует учитывать, что номера битов не являются адресами запоминающего устройства, адресуются только байты. Для обращения к отдельным битам из состава байта осуществляется доступ к целому байту запоминающего устройства. Биты в байте нумеруются слева направо от нуля до семи (например, в архитектуре z/Architecture). Примеры нумерации битов в пределах адреса: 8-31 или 40-63 для 24-разрядного адреса; 1-31 или 33-63 для 31-разрядного адреса; 0-63 для 64-разрядного адреса. В любом другом формате групп байтов фиксированной длины разряды, образующие формат, нумеруются последовательно начиная с нуля. В целях обнаружения ошибок и, предпочтительно, их коррекции с каждым байтом или с каждой группой байтов может передаваться один или более дополнительных проверочных битов. Такие проверочные биты формируются внутри вычислительной системы автоматически, они не могут непосредственно контролироваться программой. Емкость запоминающего устройства выражается числом байтов. Если длина поля запоминающего устройства определяется кодом операции, входящим в состав команды, то считается, что поле имеет фиксированную длину, которая может составлять один, два, четыре, восемь или 16 байтов. В некоторых командах могут использоваться поля большей длины. Если длина поля запоминающего устройства не определена заранее, а явно указывается, то говорят, что поле имеет переменную длину. Длина операндов с переменной длиной может изменяться с инкрементом в один байт (или, для некоторых команд, с инкрементом, кратным двум байтам или кратным другому числу байтов). Когда информация помещается в запоминающее устройство, то заменяется содержимое только тех ячеек хранения байтов запоминающего устройства, которые входят в состав поля-получателя, причем это справедливо даже в том случае, когда ширина физического канала передачи данных к запоминающему устройству превышает длину сохраняемого поля.

Определенные элементы информации должны храниться в целостном пространстве памяти запоминающего устройства. Пространство памяти считается целостным применительно к элементу информации, если его адрес кратен длине элемента информации в байтах. Предусмотрены специальные названия для полей из двух, четырех, восьми и шестнадцати байтов. Полусловом называется элемент памяти из двух следующих друг за другом байтов, полуслово является основным составляющим элементом команд. Словом называется элемент памяти из четырех следующих друг за другом байтов. Двойным словом называется элемент памяти из восьми следующих друг за другом байтов. Четверным словом называется элемент памяти из шестнадцати следующих друг за другом байтов. Если адрес запоминающего устройства указывает на полуслово, слово, двойное слово или четверное слово, то в двоичном представлении адрес содержит справа соответственно один, два, три или четыре бита, равных нулю. Команды занимают двухбайтные целостные элементы памяти. Операнды большинства команд не имеют ограничений по размещению в памяти.

В устройствах, в которых используется раздельное кэширование команд и данных (операндов), может возникать значительная задержка, если программа выполняет запись в строку кэш-памяти, из которой производится последовательная выборка команд, причем вне зависимости от того, изменяются ли эти команды в результате записи.

Согласно варианту осуществления, изобретение может быть осуществлено программным обеспечением, называемым также лицензионным внутренним кодом, содержимым ПЗУ, микрокодом, милликодом, пикокодом и т.п., причем каждый из терминов может относиться к одному или более аспектам настоящего изобретения. На фиг. 8 процессор 5001 хост-компьютерной системы 5000 может обращаться к коду программного обеспечения, содержащему один или более аспектов настоящего изобретения и хранящемуся в долговременных запоминающих устройствах 5011, таких как привод CD-ROM, привод ленточного накопителя, накопитель на жестких дисках. Программный код может располагаться на любой из множества известных машиночитаемых сред, предназначенных для использования в системе обработки данных, таких как гибкий диск, накопитель на жестких дисках или CD-ROM. Код может распространяться на подобной машиночитаемой среде или поставляться пользователям из запоминающего устройства 5002 компьютера или из запоминающего устройства одного компьютера через сеть 5010 другим компьютерным системам для их пользователей.

Код программного обеспечения содержит операционную систему, которая управляет функционированием и взаимодействием различных компонентов компьютера и одной или более прикладных программ. Программный код обычно передается из долговременного запоминающего устройства 5011 в относительно более быстродействующее запоминающее устройство 5002 компьютера, из которого код доступен процессору 5001 для обработки. Приемы и способы размещения кода программного обеспечения в пространстве памяти запоминающего устройства, на физической машиночитаемой среде и/или передача кода программного обеспечения через сети передачи данных достаточно хорошо известны и в настоящей заявке далее обсуждаться не будут. Программный код, созданный и размещенный на материальном носителе, в том числе (но не ограничиваясь) на электронных модулях памяти (ОЗУ), запоминающих устройствах флеш-памяти, CD-ROM, DVD-ROM, магнитной ленте и т.п. часто называют компьютерным программным продуктом. Информация со среды-носителя компьютерного программного продукта обычно считывается схемой обработки предпочтительно в компьютерной системе с целью выполнения программного кода схемой обработки.

На фиг. 9 показана схема примера рабочей станции или аппаратной части сервера, в которых могут быть осуществлены один или более аспектов настоящего изобретения. На фиг. 9 система 5020 содержит типичную основную компьютерную систему 5021, например, персональный компьютер, рабочую станцию или сервер, в состав которой, в свою очередь, могут входить периферийные устройства. Основная компьютерная система 5021 содержит один или более процессоров 5026 и шину передачи данных, используемую для подключения и осуществления соединения между процессором или процессорами 5026 и другими компонентами системы 5021 по хорошо известной методике. Шина соединяет процессор 5026 с запоминающим устройством 5025 и запоминающим устройством 5027 длительного хранения, которое может содержать, например, дисковый накопитель (в свою очередь, содержащий, например, любые магнитные среды хранения данных, CD-ROM, DVD-ROM или устройства флеш-памяти) или ленточный накопитель. Система 5021 может также содержать адаптер интерфейса пользователя, который соединяет микропроцессор 5026 через шину с одним или более интерфейсными устройствами, такими как клавиатура 5024, мышь 5023, принтер или сканер 5030 и/или с устройствами интерфейса пользователя других типов, такими как сенсорный экран, устройство цифрового координатного ввода планшетного типа и т.п. Шина также обеспечивает подключение к микропроцессору 5026 через адаптер дисплея устройства 5022 отображения, такого как жидкокристаллический экран или монитор.

Система 5021 может обмениваться данными с другими компьютерами или сетями компьютеров с помощью сетевого адаптера, способного осуществлять соединение 5028 с сетью 5029 передачи данных. Примерами сетевых адаптеров являются адаптеры сетей типа Token ring (от англ.: маркерное кольцо) и Ethernet, а также модемы. Система 5021 может обмениваться данными с использованием беспроводного интерфейса, такого как адаптер CDPD (от английского Cellular Digital Packet Data - цифровая пакетная передача данных по сети сотовой связи). Система 5021 может быть соединена с другими компьютерами в ЛВС или глобальную вычислительную сеть либо система 5021 может выступать в качестве клиента в системе клиент-сервер вместе с другим компьютером и т.д. Все подобные конфигурации наряду с соответствующим коммуникационным аппаратным и программным обеспечением известны достаточно хорошо.

На фиг.10 показана схема сети 5040 обработки данных, с помощью которой могут быть осуществлены один ли более аспектов настоящего изобретения. Сеть 5040 обработки данных может содержать набор индивидуальных сетей, таких как беспроводные и проводные сети, в состав каждой из которых может входить множество индивидуальных рабочих станций 5041, 5042, 5043, 5044. Кроме того, специалисты в данной области техники должны понимать, что может быть задействована одна или более ЛВС, причем ЛВС могут содержать набор рабочих станций, соединенных с хост-процессором.

На фиг.10 сети могут также содержать компьютеры-мэйнфреймы или серверы, такие как компьютер-шлюз (клиентский сервер 5046) или сервер приложений (удаленный сервер 5048, который может обращаться к хранилищу данных и к которому может также осуществляться доступ непосредственно с рабочей станции 5045). Компьютер-шлюз 5046 служит точкой доступа в каждую индивидуальную сеть. Шлюз требуется при переходе от одного сетевого протокола на другой. Компьютер-шлюз 5046 предпочтительно может быть подключен к другой сети, например к сети 5047 Интернет с помощью канала передачи данных. Компьютер-шлюз 5046 также может быть непосредственно соединен с одной или более рабочих станций 5041, 5042, 5043, 5044 с использованием канала передачи данных. Компьютер-шлюз может быть реализован на основе сервера IBM eServer™ System z, предлагаемого корпорацией International Business Machines Corporation.

На фиг. 9 и 10 процессор 5026 системы 5020 может обращаться к коду программного обеспечения, в котором могут быть осуществлены один или более вариантов настоящего изобретения и который располагается на запоминающем устройстве 5027 долговременного хранения, таком как привод CD-ROM или накопитель на жестких дисках. Код программного обеспечения для его использования системой обработки данных может располагаться на любой из множества известных машиночитаемых сред, таких как гибкий диск, накопитель на магнитных дисках или CD-ROM. Код может предоставляться на такой машиночитаемой среде или может предоставляться пользователям 5050, 5051 компьютерным системам по сети передачи данных из запоминающих устройств другой компьютерной системы.

В другом варианте код программного обеспечения может располагаться в запоминающем устройстве 5025, и процессор 5026 может обращаться к этому коду по шине процессора. Такой код программного обеспечения содержит операционную систему, которая управляет функционированием и взаимодействием различных компонентов компьютера и одной или более прикладных программ 5032. Программный код обычно передается из запоминающего устройства 5027 в относительно более быстродействующее запоминающее устройство 5025 компьютера, из которого код доступен процессору 5026 для обработки. Приемы и способы размещения кода программного обеспечения в пространстве памяти запоминающего устройства, на физической машиночитаемой среде и/или передача кода программного обеспечения через сети передачи данных достаточно хорошо известны и в настоящей заявке далее обсуждаться не будут. Программный код, созданный и размещенный на материальном носителе, в том числе (но не ограничиваясь) на электронных модулях памяти (ОЗУ), запоминающих устройствах флеш-памяти, CD-ROM, DVD-ROM, магнитной ленте и т.п., часто называют компьютерным программным продуктом. Информация со среды-носителя компьютерного программного продукта обычно считывается схемой обработки, предпочтительно, в компьютерной системе с целью выполнения схемой обработки.

Процессору наиболее доступна кэш-память низшего уровня (первого уровня; обозначение первого уровня - L1), которая обычно обладает наибольшим быстродействием и меньшим объемом по сравнению с процессорной кэш-памятью других уровней. Уровень основного запоминающего устройства считается наивысшим (уровень 3, обозначение L3, если всего предусмотрены три уровня). Кэш-память низшего уровня часто разделяется на кэш-память команд I-кэш (от английского Instructions cache - кэш-память команд) для хранения предназначенных для исполнения команд и кэш-память данных D-кэш (от английского Data cache - кэш-память данных), предназначенную для хранения операндов.

На фиг. 11 показан пример осуществления процессора 5026. Как правило, для буферизации блоков информации запоминающего устройства используется одноуровневая или многоуровневая кэш-память 5053, что позволяет увеличить производительность процессора. Кэш-память 5053 представляет собой быстродействующий буфер, хранящий строки данных основного запоминающего устройства, которые, вероятно, должны использоваться в будущем. Как правило, длина строк данных в кэш-памяти составляет 64, 128 или 256 байтов. Часто применяются отдельные функциональные узлы кэш-памяти для буферизации команд и данных. Для поддержания когерентности содержимого кэш-памяти, т.е. для синхронизации копий строк данных в основном запоминающем устройстве и в кэш-памяти, часто применяются различные хорошо известные снуп-алгоритмы (от английского Snoop algorithm, специальный алгоритм поиска необходимых данных в кэш-памяти). Основное запоминающее устройство 5025 вычислительной системы часто также рассматривается как кэш-память. В вычислительной системе с четырьмя уровнями кэш-памяти 5053 основное запоминающее устройство 5025 иногда рассматривается как кэш-память пятого уровня (L5), поскольку оно обычно обладает большим быстродействием по сравнению с быстродействием большинства доступных вычислительной системе энергонезависимых запоминающих устройств - запоминающих устройств с прямым доступом, ленточных запоминающих устройств с последовательным доступом и т.п. и хранит только часть данных указанных устройств. Основное запоминающее устройство 5025 ″кэширует″ (буферизирует) страницы данных, которые загружаются и выгружаются из него операционной системой.

Программный счетчик (счетчик команд) 5061 содержит адрес следующей подлежащей исполнению команды. Программный счетчик в процессоре, построенном по архитектуре z/Architecture, является 64-разрядным, его длина может быть сокращена до 31 или до 24 разрядов для поддержки предыдущих ограничений на длину адреса. Как правило, программный счетчик входит в состав слова состояния процессора (ССП) компьютера, поскольку его содержимое требуется сохранять при переключении задач. Так, выполнение программы при некотором значении программного счетчика может быть прервано, например, операционной системой (выполнение переключается от окружения программы к окружению операционной системы). В то время, пока программа неактивна, значение счетчика программ сохраняется в ССП программы, и при выполнении задачи операционной системы используется счетчик программ ССП операционной системы. Как правило, программный счетчик увеличивается на величину, равную длине в байтах исполняемой в данный момент команды. Команды типа RISC (от английского Reduced Instruction Set Computing - вычисления с сокращенным набором команд), как правило, имеют фиксированную длину, в то время как команды типа CISC (от английского Complex Instruction Set Computing - вычисления со сложным набором команд), как правило, имеют переменную длину. Команды в архитектуре IBM z/Architecture относятся к типу CISC, их длина составляет 2, 4 или 6 байтов. Значение в программном счетчике 5061 изменяется либо операцией переключения задач, либо при выполнении алгоритмической операции ветвления, например, по команде ветвления. При операции переключения задачи текущее значение программного счетчика сохраняется в ССП вместе с другой информацией о состоянии выполнявшейся программы (в частности, коды состояния), после чего загружается новое значение программного счетчика, указывающее на команду нового программного модуля, подлежащего исполнению. Операция ветвления, используемая в программе при принятии решений или выполнении цикла, выполняется путем загрузки в программный счетчик 5061 результата команды ветвления.

Как правило, для выборки команд по указанию процессора 5026 применяется устройство 5055 выборки команд. Устройство выборки команд выбирает команду в порядке следования либо команду, на которую указывает команда ветвления, либо по указанию о переключении задачи - очередную команду программы. В современных устройствах выборки команд часто применяются упреждающие методы для спекулятивной выборки команд, основанные на гипотезе о том, что заблаговременно выбранные команды могут потребоваться в будущем. Например, устройство выборки может загрузить 16 байтов команд, в число которых входят следующая по очереди команда и, кроме того, байты команд, следующих за ней.

Затем выбранные команды выполняются процессором 5026. Согласно варианту осуществления, выбранная команда(команды) передаются на устройство 5056 диспетчеризации. Устройство диспетчеризации декодирует команду(команды) и передает информацию о декодированной команде(командах) далее на устройства 5057, 5058, 5060. Исполнительный блок 5057, как правило, принимает информацию о декодированных арифметических операциях от устройства 5055 выборки команд и выполняет арифметические операции над операндами согласно коду операции команды. Операнды передаются в исполнительное устройство 5057 предпочтительно либо из запоминающего устройства 5025, либо из регистров 5059, либо извлекаются из внутреннего поля выполняемой команды. Результат выполнения команды сохраняется либо в запоминающем устройстве 5025, либо в регистрах 5059, либо в ином аппаратном обеспечении вычислительной системы (в управляющих регистрах, регистрах ССП и т.п.).