Область техники, к которой относится изобретение

Настоящее изобретение относится, в общем, к компьютерным системам и в частности относится к системам и способам, обеспечивающим внешнюю сертификацию многопроцессорных платформ.

Уровень техники

Важность защищенного и безопасного исполнения и целостности приложений и данных в компьютерной системе продолжает расти. Разнообразные известные способы обеспечения безопасности не способны адекватно защитить приложения и данные гибким, но надежным способом.

Краткое описание чертежей

Настоящее изобретение иллюстрируется на примерах, и, не в качестве ограничений, может быть лучше понято со ссылками на последующее подробное описание, рассматриваемое вместе с чертежами, на которых:

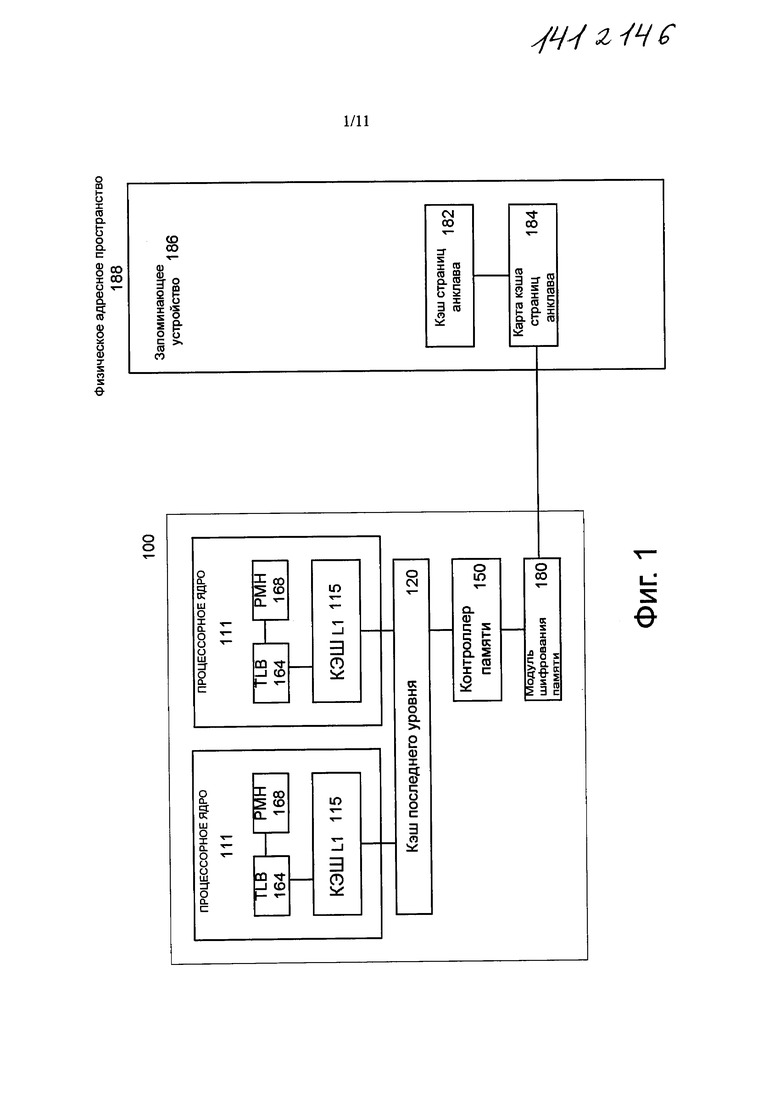

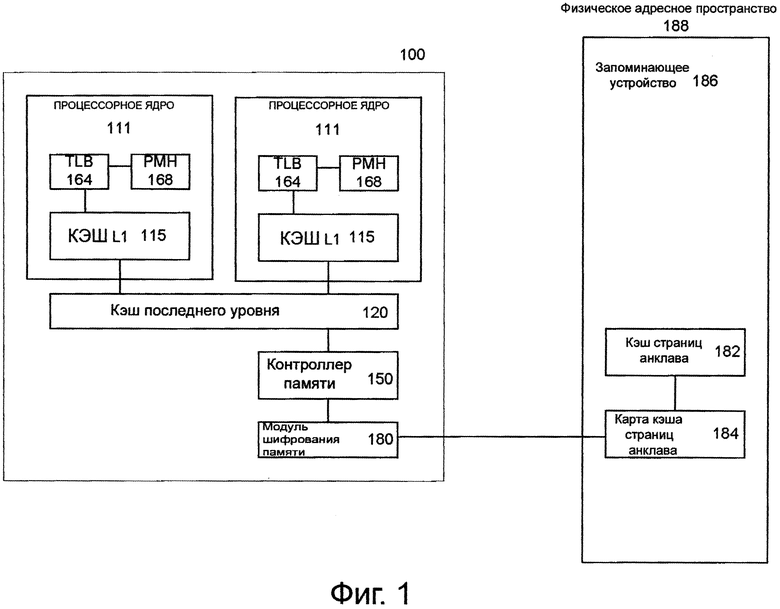

Фиг. 1 представляет компонентную схему высокого уровня для примера процессорной системы согласно одному или нескольким аспектам настоящего изобретения;

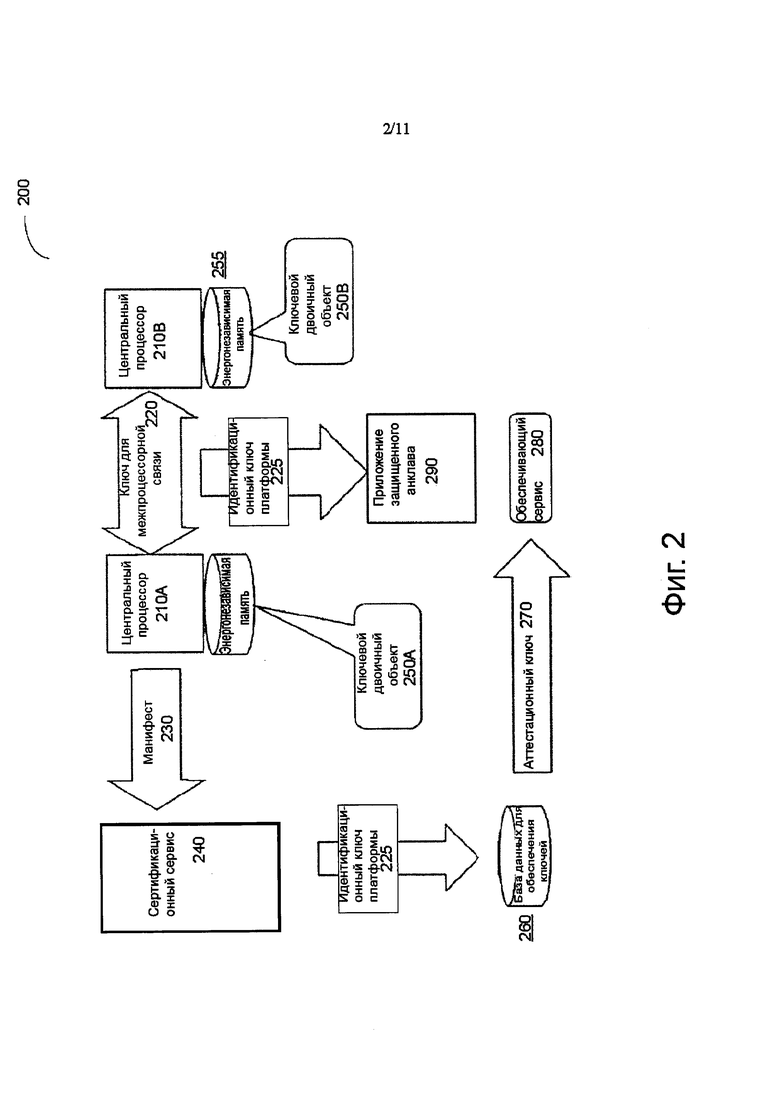

Фиг. 2 схематично иллюстрирует пример способа генерации манифеста платформы посредством многопроцессорной платформы согласно одному или нескольким аспектам настоящего изобретения;

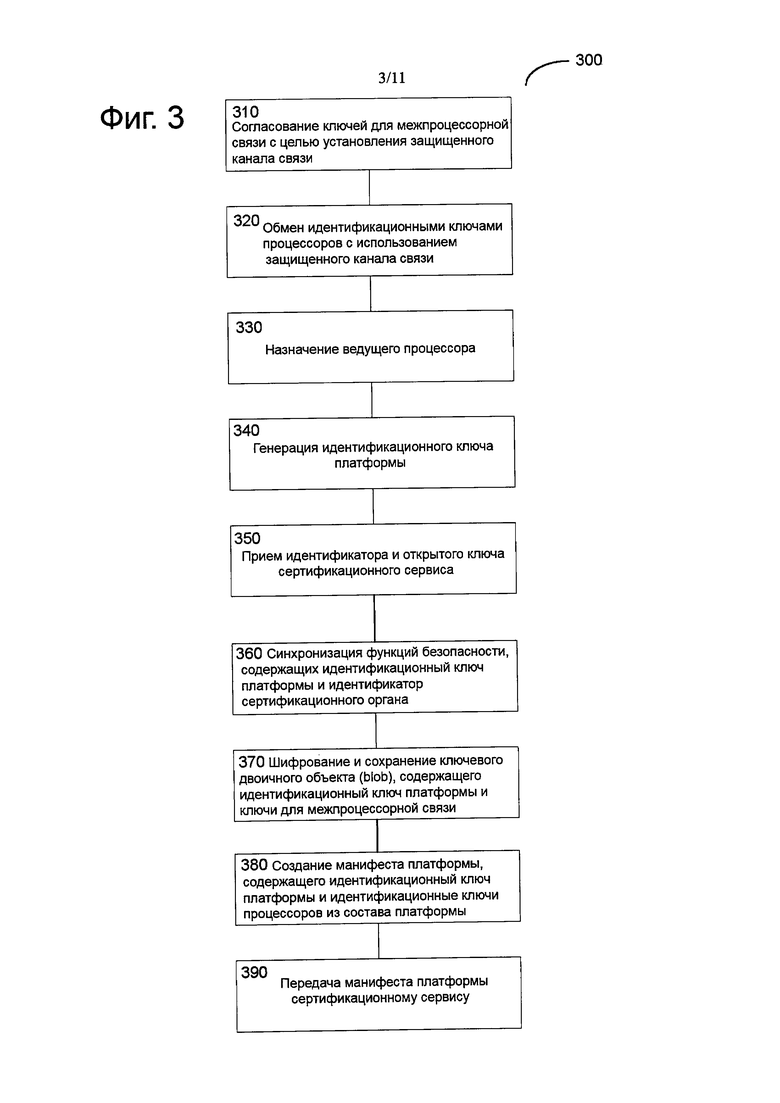

Фиг. 3 представляет логическую схему примера способа генерации манифеста платформы посредством многопроцессорной платформы согласно одному или нескольким аспектам настоящего изобретения;

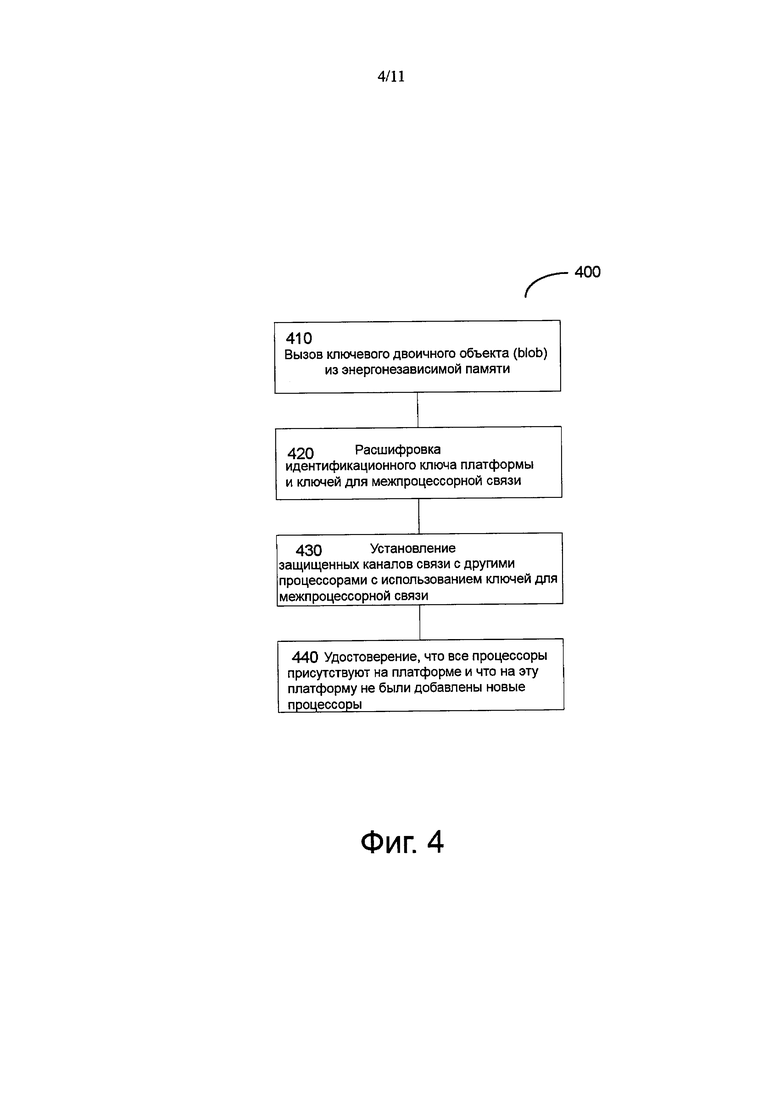

Фиг. 4 представляет логическую схему способа взаимной (перекрестной) аутентификации процессоров в составе многопроцессорной платформы после второй и последующих загрузок платформы согласно одному или нескольким аспектам настоящего изобретения;

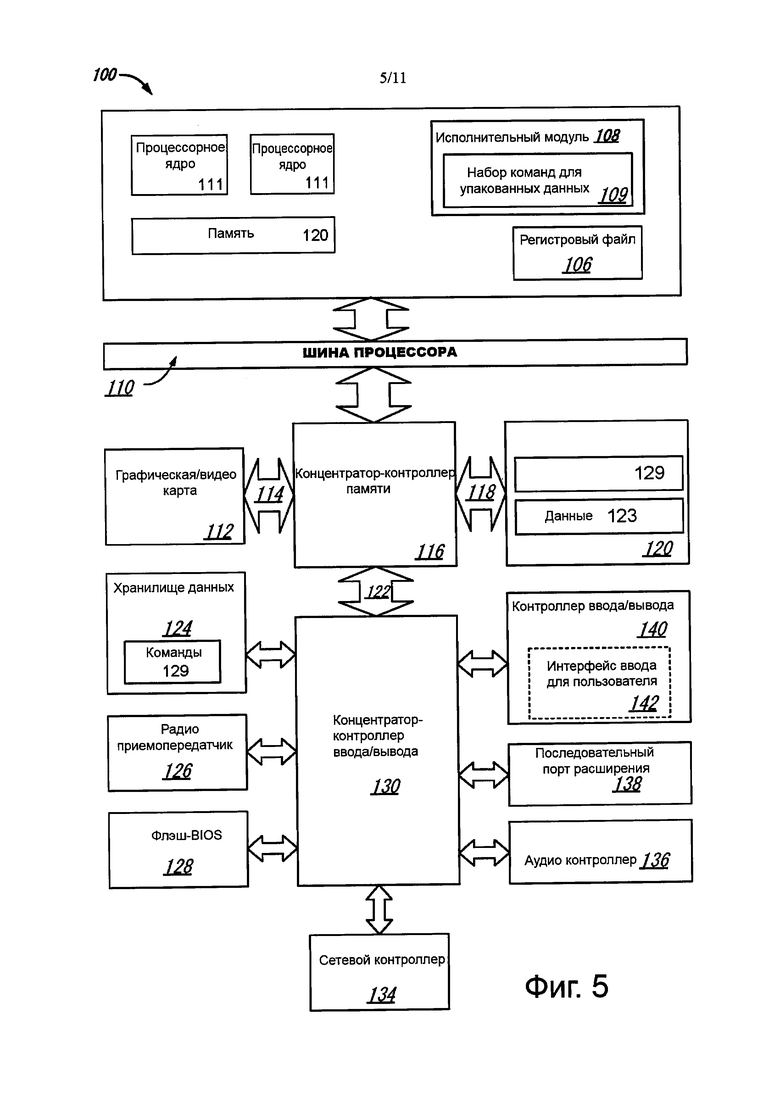

Фиг. 5 представляет компонентную схему высокого уровня для примера компьютерной системы согласно одному или нескольким аспектам настоящего изобретения;

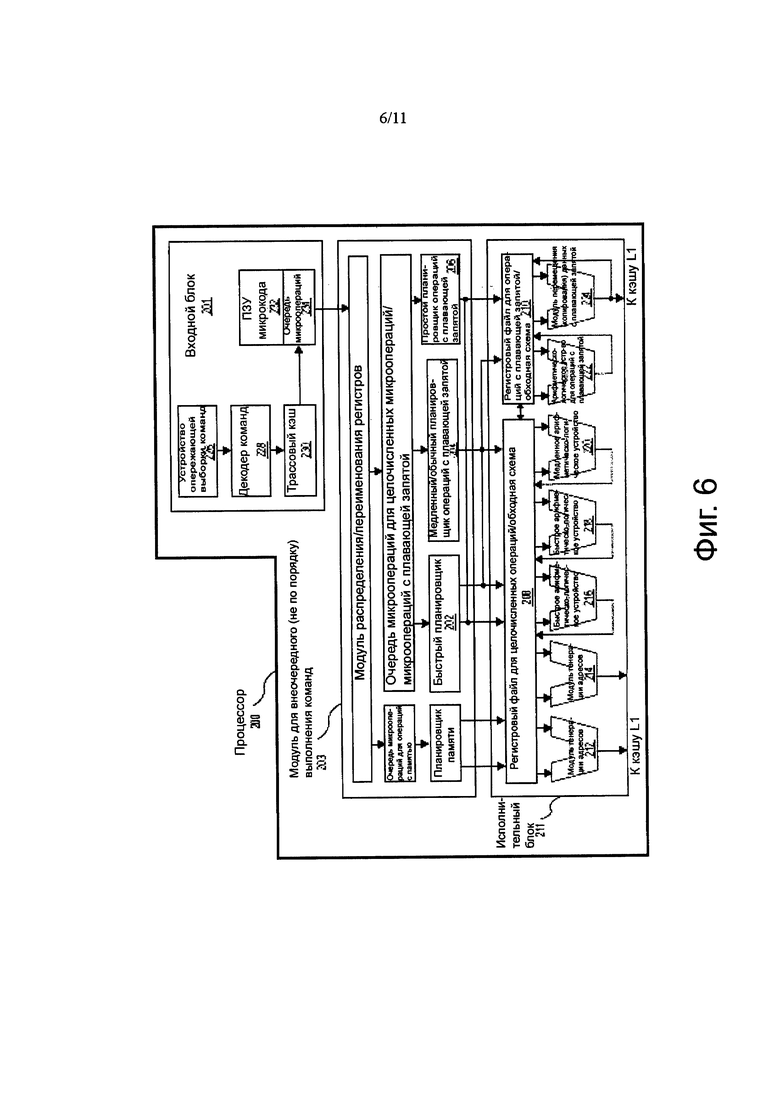

Фиг. 6 представляет блок-схему процессора согласно одному или нескольким аспектам настоящего изобретения;

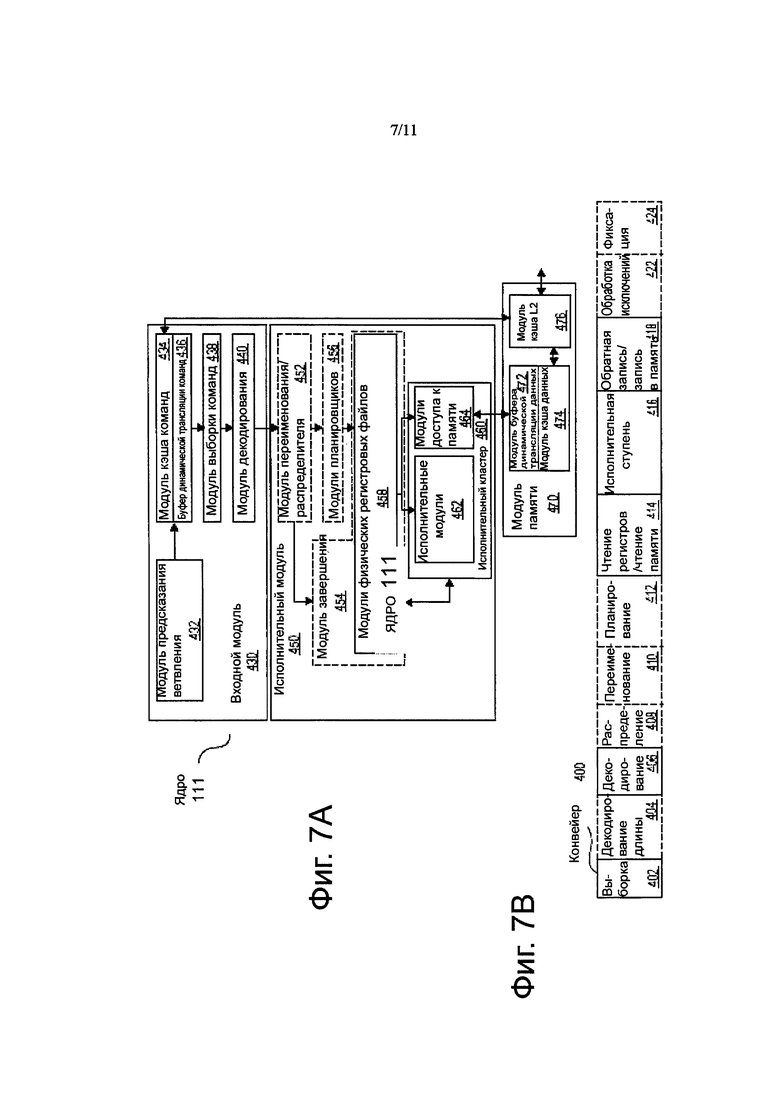

Фиг. 7а-7b схематично иллюстрируют элементы микроархитектуры процессора согласно одному или нескольким аспектам настоящего изобретения;

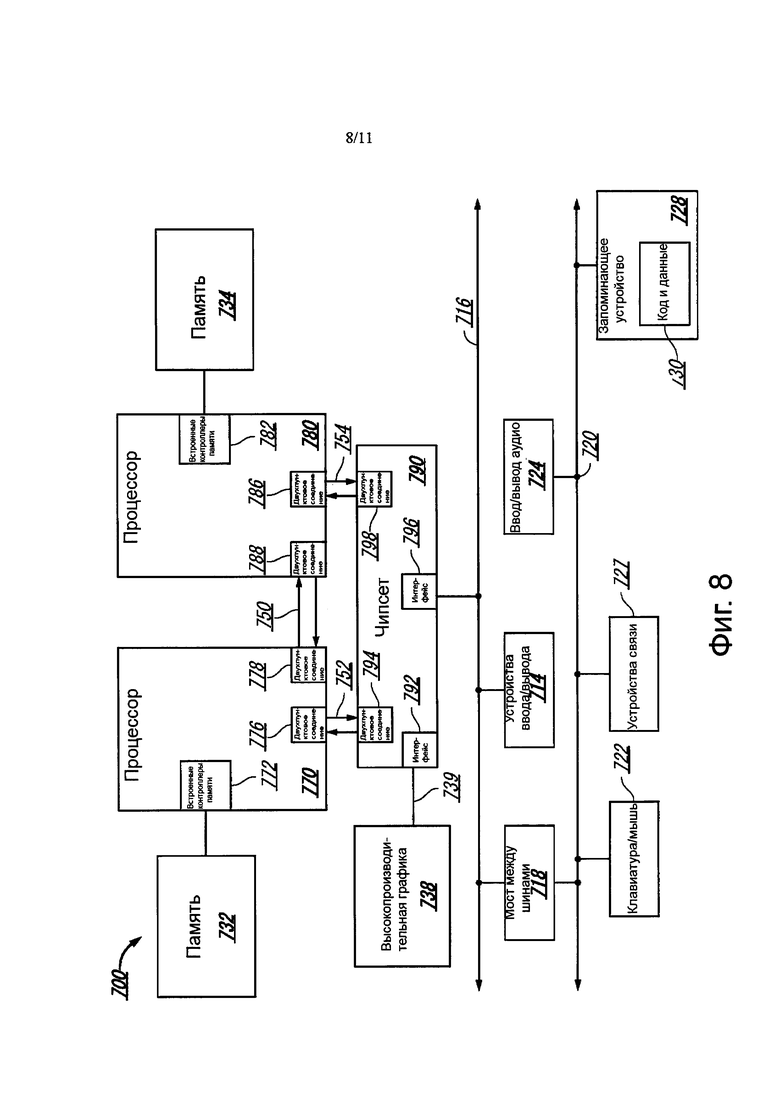

Фиг. 8 представляет блок-схему примера компьютерной системы согласно одному или нескольким аспектам настоящего изобретения;

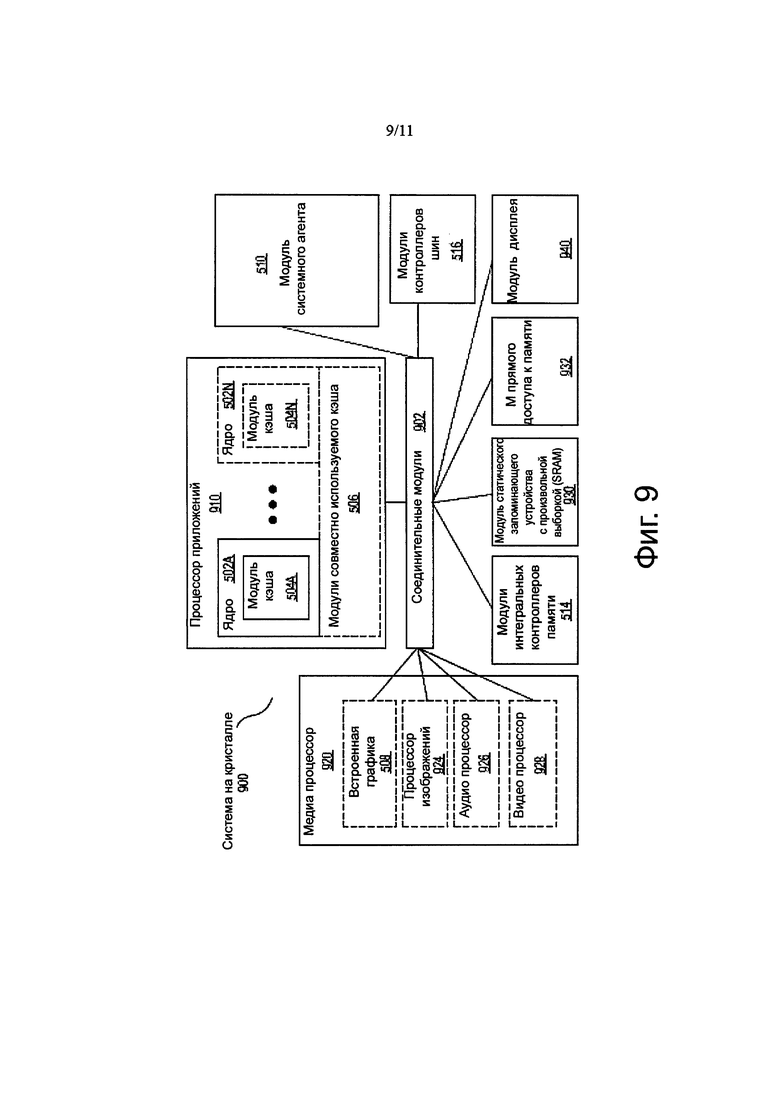

Фиг. 9 представляет блок-схему примера системы на кристалле (SoC) согласно одному или нескольким аспектам настоящего изобретения;

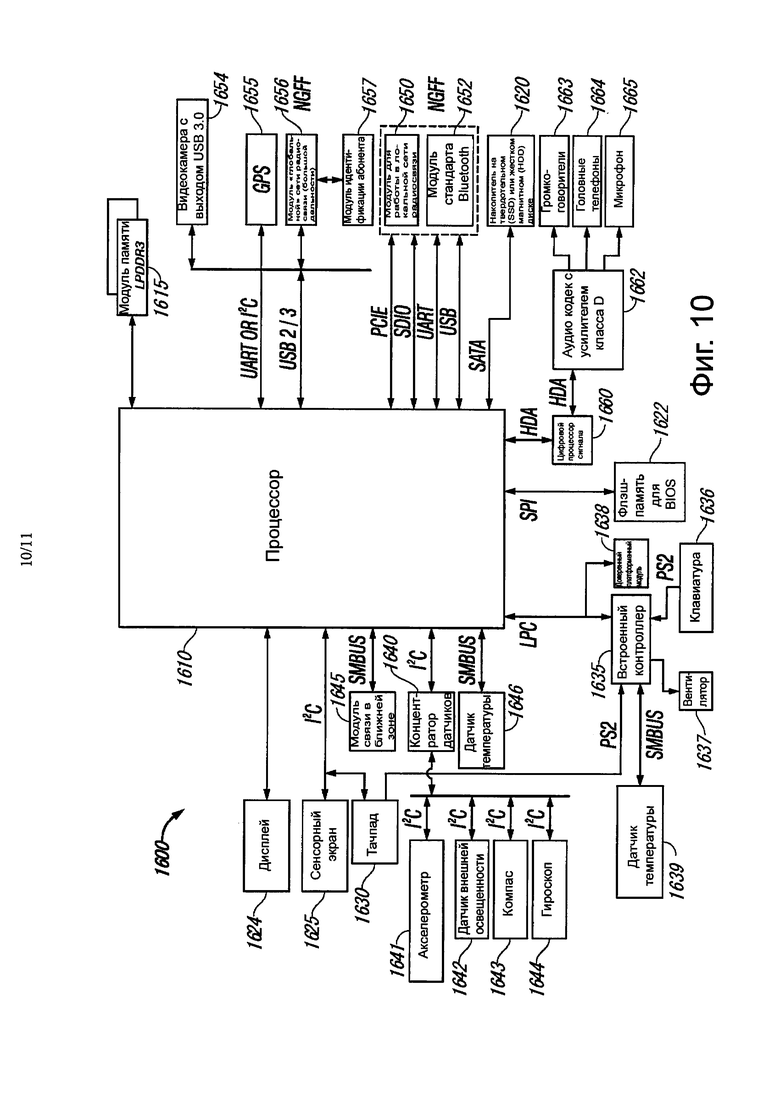

Фиг. 10 представляет блок-схему примера компьютерной системы согласно одному или нескольким аспектам настоящего изобретения; и

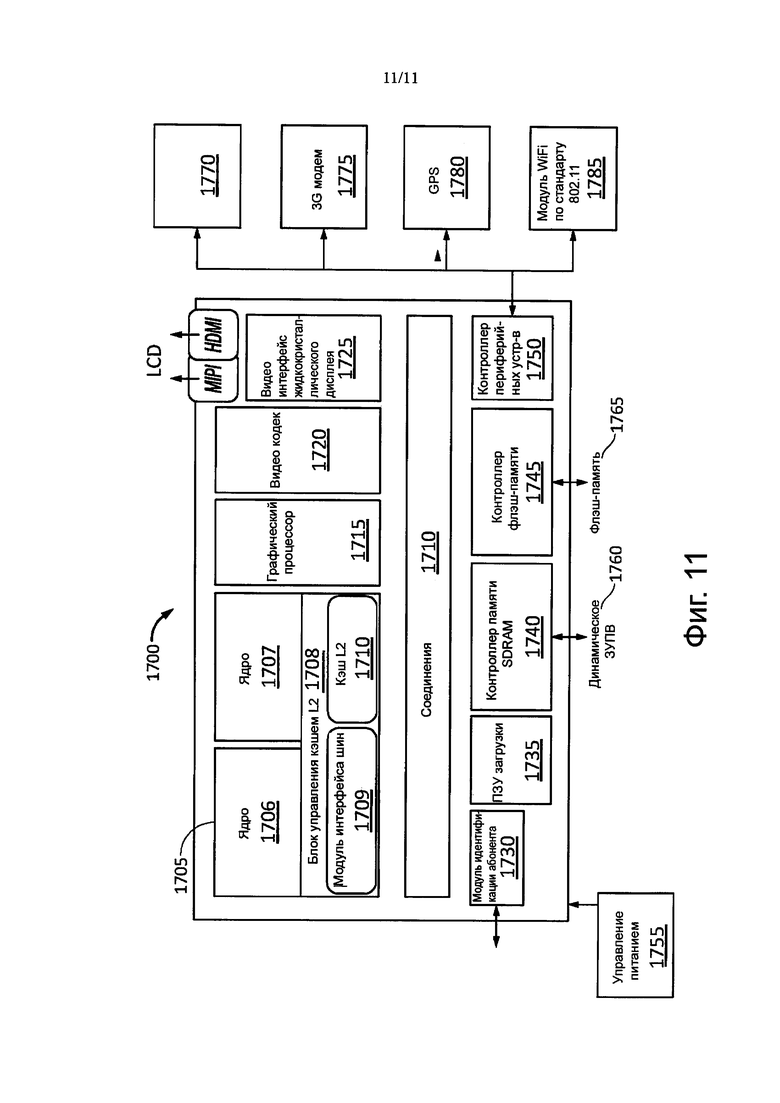

Фиг. 11 представляет блок-схему примера системы на кристалле (SoC) согласно одному или нескольким аспектам настоящего изобретения.

Подробное описание

Здесь описаны процессорные системы и соответствующие способы, обеспечивающие внешнюю сертификацию многопроцессорных платформ. Приложения, выполняемые процессорной системой, и данные, к которым обращаются и получают доступ эти приложения, могут быть защищены на микроархитектурном уровне, например, путем реализации защищенных анклавов, как это более подробно рассмотрено ниже.

Согласно одному или нескольким аспектам настоящего изобретения процессорная система может содержать процессорное ядро, связанное с архитектурно защищенной памятью. Это процессорное ядро может содержать управляющую логику, конфигурированную для предотвращения неавторизованного доступа к архитектурно защищенной памяти. Процессорное ядро может также содержать исполнительную логику, конфигурированную для реализации защищенного анклава путем выполнения команд для обращения и доступа к данным, находящимся в микроархитектурно защищенной памяти, как это будет более подробно описано ниже.

Каждый процессор в ходе его изготовления может быть оснащен идентификационным ключом. Идентификационный ключ процессора может храниться в энергонезависимом постоянном запоминающем устройстве в составе процессора, таком как группа программируемых перемычек. В случае однопроцессорной платформы идентификационный ключ процессора может быть использован в качестве идентификационного ключа платформы для передачи сервису сертификации и может быть также использован в качестве «ключевого» материала для генерации одного или нескольких шифровальных ключей для применения при создании защищенного анклава.

Следовательно, в случае многопроцессорных платформ анклав будет принимать различные ключи в зависимости от того, какой процессор работает с этим анклавом, что может привести к неисправимой ошибке, если активный анклав будет мигрировать от одного процессора к другому. Кроме того, для многопроцессорной платформы потребуется идентификатор платформы для представления сервису сертификации.

Один или несколько аспектов настоящего изобретения направлены на устранение перечисленных выше и других недостатков путем создания многопроцессорной платформы и способа генерации манифеста платформы, содержащего идентификационные ключи процессоров, входящих в состав платформы, и идентификационный ключ платформы, генерируемый и синхронизируемый этими процессорами, как будет более подробно рассмотрено ниже. Разнообразные аспекты упомянутых выше способов и систем будут более подробно рассмотрены ниже на примерах, а не посредством ограничений.

В последующем описании приведены многочисленные конкретные подробности, такие как примеры конкретных типов процессоров и конфигураций систем, конкретные структуры аппаратуры, конкретные архитектурные и микроархитектурные подробности, конкретные конфигурации регистров, конкретные типы команд, конкретные компоненты систем, конкретные размеры/высоты, конкретные ступени процессорных конвейеров и операций с целью предоставления полного понимания настоящего изобретения. Специалисты в рассматриваемой области должны, однако, понимать, что не обязательно использовать все эти конкретные подробности для практической реализации рассматриваемых здесь способов. В других случаях хорошо известные компоненты или способы, такие как конкретные и альтернативные архитектуры процессоров, конкретные логические схемы/программные коды для рассматриваемых алгоритмов, конкретные встроенные программные коды, конкретные логические конфигурации, конкретные производственные технологии и материалы, конкретные реализации компиляторов, конкретные выражения алгоритмов в виде программных кодов, конкретные способы/логические схемы снижения питания и стробирования, и другие конкретные подробности работы компьютерных систем, здесь не были рассмотрены подробно, чтобы избежать ненужного загромождения и затемнения настоящего описания.

Хотя последующие примеры описаны со ссылками на процессор, другие варианты реализации применимы к другим типам интегральных схем и логических устройств. Аналогично, технологии и рекомендации, рассмотренные здесь, могут быть применены к другим типам схем или полупроводниковых приборов, которые могут выиграть от более высокой производительности и пропускной способности конвейерных систем и улучшения характеристик. Рекомендации и особенности примеров, рассмотренных здесь, применимы к любому процессору или машине, осуществляющей манипуляции с данными. Однако настоящее изобретение не ограничивается процессорами или машинами, выполняющими операции с данными размером 512 бит, 256 бит, 128 бит, 64 бит, 32 бит или 16 бит, а может быть применено к процессору или машине, манипулирующей данными или управляющей ими.

Примеры, иллюстрирующие настоящее изобретение, и прилагаемые чертежи не следует толковать в ограничительном смысле, поскольку они предназначены быть только примерами вариантов, рассмотренных здесь, а не для создания исчерпывающего списка всех возможных реализаций описываемых здесь вариантов. Хотя приведенные ниже примеры описывают манипуляции с командами и распределение таких команд в контексте функциональных исполнительных модулей и логических схем, другие варианты реализации систем и способов, представленных здесь, могут быть созданы с использованием записанных на машиночитаемом материальном носителе данных или команд, при выполнении которых машиной эта машина осуществляет функции, согласованные по меньшей мере с одним из описанных здесь вариантов. В некоторых вариантах реализации функции, ассоциированные с вариантами реализации, рассматриваемыми здесь, воплощены в исполняемых машиной командах. Эти команды могут быть использованы для того, что процессор общего назначения или специализированный процессор, запрограммированный этими командами, осуществлял описываемые здесь способы. Рассматриваемые здесь варианты реализации могут содержать машиночитаемый или компьютерный носитель записи с сохраненными на нем командами, который может быть использован для программирования компьютера (или другого электронного устройства) с целью выполнения одной или нескольких операций согласно рассматриваемым здесь вариантам. В качестве альтернативы, операции системы и способы, рассматриваемые здесь, могут быть выполнены специализированными аппаратными компонентами, содержащими логические схемы с фиксированными функциями для выполнения таких операций, или посредством сочетания программируемых компьютерных компонентов и аппаратных компонентов с фиксированными функциями.

Команды, используемые для программирования логических устройств с целью осуществления рассматриваемых здесь способов, могут быть записаны в запоминающем устройстве системы, таком как динамическое запоминающее устройство с произвольной выборкой (DRAM), кэш-память, флэш-память или другое запоминающее устройство. Более того, команды могут быть переданы через сеть связи или посредством другого компьютерного носителя записи. Таким образом, машиночитаемый носитель записи может содержать любой механизм для хранения или передачи информации в форме, читаемой машиной (например, компьютером), но не ограничиваясь этим, - дискеты, оптические диски, компакт-диски, постоянные запоминающие устройства (CD-ROM) и магнитооптические диски, постоянные запоминающие устройства (ПЗУ (ROM)), запоминающие устройства с произвольной выборкой (ЗУПВ (RAM)), стираемые программируемые постоянные запоминающие устройства (СППЗУ (EPROM)), электрически стираемые программируемые постоянные запоминающие устройства (ЭСППЗУ (EEPROM)), магнитные или оптические карточки, флэш-память или материальные машиночитаемые носители, используемые при передаче информации через Интернет посредством электрических, оптических, акустических или распространяющихся сигналов другого вида (например, волн несущих, инфракрасных сигналов, цифровых сигналов и т.п.). Соответственно, компьютерный носитель записи содержит материальный машиночитаемый носитель любого типа, подходящий для хранения или передачи команд или информации в электронном виде, в форме, читаемой машиной (например, компьютером).

Термин «процессор» здесь будет обозначать устройство, способное выполнять команды, кодирующие арифметические операции, логические операции или операции ввода/вывода. В одном иллюстративном примере процессор может соответствовать модели фон-Неймана и может содержать арифметическо-логическое устройство (ALU), модуль управления и несколько регистров. В следующем аспекте процессор может содержать одно или несколько процессорных ядер и, соответственно, может быть одноядерным процессором, который обычно способен выполнять команды одного конвейерного потока, или многоядерным процессором, который может одновременно обрабатывать команды нескольких конвейерных потоков. В другом аспекте процессор может быть реализован в виде одной интегральной схемы, двух или более интегральных схем или может быть компонентом многокристального модуля (например, где кристаллы индивидуальных микропроцессоров смонтированы в одном общем корпусе интегральной схемы и вследствие этого используют одно гнездо (сокет)).

На Фиг. 1 представлена блок-схема примера процессорной системы согласно одному или нескольким аспектам настоящего изобретения. Как показано на Фиг. 1, процессорная система 100 может содержать одно или несколько процессорных ядер 111, с каждым процессорным ядром 111 ассоциирован локальный кэш 115 первого уровня (L1). Кэш L1 115 может быть связан с совместно используемым кэшем 120 последнего уровня (LLC). В иллюстративном примере иерархия кэшей, содержащая кэш L1 115 и кэш LLC 120 может быть конфигурирована в виде инклюзивной иерархии кэшей, так что по меньшей мере часть информации, хранящейся в кэше L1 115, может быть также сохранена в кэше LLC 120.

Процессорные ядра 111 в разнообразных реализациях могут представлять Собой ядра, выполняющие команды по порядку, или ядра, выполняющие команды не по порядку (с внеочередным выполнением команд). В иллюстративном примере процессорное ядро 111 может иметь микроархитектуру, содержащую процессорные логические схемы и схемы, используемые для реализации архитектуры набора команд (instruction set architecture (ISA)). Процессоры с различными микроархитектурами могут использовать по меньшей мере часть общего набора команд. Например, одна и также архитектура регистров для ISA может быть реализована различными способами в разных микроархитектурах с использованием различных технологий и в том числе - выделенных физических регистров, одного или нескольких динамически выделяемых регистров с применением механизма переименования регистров (например, с использованием таблицы псевдонимов регистров (register alias table (RAT)), буфера переупорядочения (reorder buffer (ROB)) и регистрового файла завершения (retirement register file)), как показано на Фиг. 6-7. В некоторых вариантах реализации процессорная система 100 может также содержать разнообразные другие компоненты, не показанные на Фиг. 1.

Согласно одному или нескольким аспектам настоящего изобретения процессорная система 100 может содержать архитектурно защищенную память. Процессорное ядро 111 может содержать процессорную логику, конфигурированную для реализации защищенного анклава путем выполнения команд, находящихся в защищенной памяти, и доступа к данным, находящимся в защищенной памяти, предотвращая при этом неавторизованный доступ к защищенной памяти даже для привилегированных приложений, как будет более подробно описано ниже.

Термин «защищенный (или безопасный) анклав» здесь будет обозначать защищенную область в пределах адресного пространства приложения. Доступ к анклаву памяти от приложений, не являющихся резидентными в этом анклаве, предотвращен, даже если попытку такого доступа предпринимает привилегированное приложение, такое как BIOS, операционная система или монитор виртуальной машины.

Активный защищенный анклав может быть разбит на зашифрованную часть и незашифрованную часть. Зашифрованная часть анклава может находиться в незащищенной памяти (такой как главное запоминающее устройство или диск). Незашифрованная часть находится в кэше страниц анклава (enclave page cache (ЕРС)) 182. Кэш ЕРС представляет собой защищенную память, используемую процессорной системой для временного хранения страниц анклава, когда они не являются защищенными криптографически. Кэш ЕРС может быть разбит на страницы заданного размера, которые могут именоваться страницами ЕРС. Кэш ЕРС защищен от любого доступа посредством программного обеспечения, резидентного за пределами анклава. Более того, неавторизованные стороны не смогут прочитать или как-то модифицировать принадлежащие анклавам данные открытого текста, загруженные в кэш ЕРС, посредством прямолинейных аппаратных атак. Кэш ЕРС расположен в физическом адресном пространстве процессорной системы, но доступен он может быть только с использованием привилегированных или непривилегированных команд анклава, служащих для построения и активизации анклава, входа/выхода из анклава, управления кэшем ЕРС и выполнения разнообразных других операций.

Есть несколько механизмов реализации кэша ЕРС. Кэш ЕРС может быть реализован в виде выполненного на кристалле статического ЗУПВ (SRAM) или динамического ЗУПВ (DRAM). В качестве альтернативы кэш ЕРС может быть построен путем секвестирования кэша последнего уровня в составе центрального процессора CPU. Другим механизмом реализации кэша ЕРС является модуль шифрования памяти (Memory Encryption Engine (МЕЕ)). Термин «модуль МЕЕ» здесь будет обозначать реализованную аппаратно процессорную логическую схему, шифрующую трафик между корпусом процессора и динамическим ЗУПВ (DRAM) платформы, создавая, таким образом, механизм образования криптографически защищенной энергозависимой памяти с использованием динамического ЗУПВ DRAM платформы. Модуль МЕЕ может перехватывать попытки доступа к памяти и направлять их криптографическому контроллеру, который может генерировать один или несколько случаев обращения к динамическому ЗУПВ DRAM платформы с целью выборки зашифрованного текста, обрабатывать этот зашифрованный текст для генерации открытого текста и удовлетворять исходный запрос доступа к памяти.

Как показано на Фиг. 1, кэш L1 115 может передавать данные в кэш LLC 120 и из него. С кэшем 120 последнего уровня и модулем МЕЕ 180 может быть соединен контроллер 150 памяти. Этот контроллер 150 памяти может обращаться и получать доступ к кэшу ЕРС 182, резидентному в запоминающем устройстве 186 для резервного копирования в физическом адресном пространстве 188.

Карта кэша страниц анклава (Enclave Page Cache Map (EPCM)) представляет собой защищенную структуру, используемую процессорной системой для отслеживания контента кэша ЕРС. Карта ЕРСМ может содержать несколько входных позиций, каждая из которых соответствует своей странице кэша ЕРС. Каждая входная позиция карты ЕРСМ может содержать, в зависящем от конкретной реализации формате, следующую информацию: действительна ли соответствующая страница кэша ЕРС или нет; идентификатор события анклава, которому принадлежит эта страница, тип страницы (REG, TCS, VA, SECS); виртуальный адрес, по которому анклаву разрешено обращаться к этой странице; разрешения для чтения/записи/исполнения применительно к этой странице; доступна ли эта страница или нет («Заблокирована» (BLOCKED) или «Не заблокирована) UNBLOCKED).

Карта ЕРСМ может быть использована процессорной системой в процессе трансляции адресов, чтобы усилить управление доступом к страницам анклава, загруженным в кэш ЕРС. Логически это создает дополнительный уровень защиты при управлении доступом в качестве дополнения к «старым» известным механизмам сегментации, таблиц страниц и расширенных таблиц страниц.

Кэш ЕРС, карта ЕРСМ и разнообразные другие специфичные для конкретной реализации структуры данных могут быть отображены в позиции внутри архитектурно защищенной памяти. Когда происходит генерация запроса на доступ в кэш ЕРС, процессорная система 100 может переотобразить этот запрос в позицию в запоминающем устройстве для резервного копирования, содержащую зашифрованные данные кэша ЕРС, и извлечь эти данные.

Разнообразные функции, относящиеся к анклаву, могут быть реализованы в микрокоде (микропрограммном коде), поддерживаемом аппаратными реализациями модуля МЕЕ и процессорной логикой, осуществляющей функциональные характеристики анклава. В некоторых вариантах процессорная логика может управлять доступом в кэш ЕРС 182 через буфер 164 динамической трансляции (translation lookaside buffer (TLB)) и модуль 168 обработки промахов страниц (page miss handler (РМН)).

В иллюстративном примере буфер TLB может быть реализован в виде таблицы, отображающей виртуальные адреса на физические адреса. Термин «попадание в буфер TLB» ("TLB hit") обозначает ситуацию, когда запрошенный виртуальный адрес присутствует в буфере TLB. Термин «промах буфера TLB» ("TLB miss") обозначает противоположную ситуацию: когда запрошенный виртуальный адрес отсутствует в буфере TLB, преобразование (трансляция) адресов может происходить путем просмотра таблицы страниц. После определения физического адреса преобразование виртуального адреса в физический адрес может быть введено в буфер TLB.

Каждая входная позиция буфера TLB может содержать один или несколько битов, идентифицирующих анклав, владеющий позицией в памяти, на которую «ссылается» эта входная позиция буфера TLB. В качестве альтернативы, если этих битов нет, может потребоваться сброс буфера TLB при выходе из защищенного анклава, чтобы предотвратить неавторизованный доступ к кэшу ЕРС. В иллюстративном примере, если произошел промах буфера TLB, дополнительный просмотр сможет выбрать из карты ЕРС данные относительно нескольких ссылок в память. Модуль РМН может осуществлять просмотр карты ЕРС.

Процессорная система 100 может реализовать механизм, именуемый «аттестация» ("attestation"), посредством которого эта процессорная система может продемонстрировать внешнему объекту (например, удаленной компьютерной системе), что некий модуль программного обеспечения был правильно инсталлирован и запущен в процессорной системе. В некоторых вариантах реализации процессорная система 100 может генерировать идентификационный ключ, обеспечивающий идентификацию аппаратной платформы. В иллюстративном примере приложение, исполняемое в анклаве, может направлять этот идентификационный ключ сервису сертификации. После проверки действительности идентификационного ключа сервис сертификации может выдать аттестационный ключ и может далее передать этот аттестационный ключ обеспечивающему сервису. Приложение защищенного анклава, исполняемой процессорной системой, может затем передать свой идентификационный ключ этому обеспечивающему сервису для извлечения данных, чувствительных с точки зрения безопасности.

Каждый процессор может быть оснащен идентификационным ключом во время изготовления этого процессора. Идентификационный ключ процессора может храниться в энергонезависимом постоянном запоминающем устройстве в составе процессора, таком как группа программируемых перемычек. В случае однопроцессорной платформы идентификационный ключ процессора может быть использован в качестве идентификационного ключа платформы для передачи сервису сертификации и может быть также использован в качестве «ключевого» материала для генерации одного или нескольких шифровальных ключей для применения при создании защищенного анклава. В некоторых вариантах каждый защищенный анклав может затребовать один или несколько ключей с использованием команды EGETKEY.

Следовательно, в случае многопроцессорных платформ анклав будет принимать различные ключи в зависимости от того, какой процессор работает с этим анклавом, что может привести к неисправимой ошибке, если активный анклав будет мигрировать от одного процессора к другому. Кроме того, для многопроцессорной платформы потребуется идентификатор платформы для представления сервису сертификации.

Согласно одному или нескольким аспектам настоящего изобретения многопроцессорная платформа может генерировать манифест платформы, содержащий идентификационные ключи процессоров, входящих в состав платформы, и идентификационный ключ платформы, сформированный и синхронизированный процессорами, как это будет более подробно описано ниже.

Пример способа генерации манифеста платформы рассмотрен со ссылками на Фиг. 2. Логическая схема этого примера способа представлена на Фиг. 3. Как схематично показано на Фиг. 2, платформа 200 может содержать несколько процессорных корпусов 210. Тогда как приведенное ниже описание рассматривает случай двух процессорных корпусов, предлагаемые здесь способы в равной степени применимы к процессорным платформам, содержащим произвольное число процессоров.

После первой загрузки или сброса платформы каждый из процессоров 210А-210В может удостовериться, записан ли манифест платформы в заданной позиции энергонезависимой памяти, доступной соответствующему процессору. Если манифест платформы потерян или недействителен, процессоры 210 могут согласовать долговременные ключи 220 для межпроцессорной (IPC) связи с целью защиты последующей межпроцессорной связи для генерации манифеста 230 платформы. В иллюстративном примере процессоры 210 могут выполнять протокол согласования неаутентифицированного ключа (например, протокол обмена ключами Диффи-Хелмана (Diffie-Hellman)).

После этого процессоры могут установить защищенный канал связи с применением согласованного ключа 220 межпроцессорной связи и использовать этот канал связи для обмена своими идентификационными ключами и синхронизации набора функций безопасности. К последним могут относиться идентификационный ключ 225 платформы и идентификатор сертификационного сервиса, которым должна пользоваться эта платформа. В иллюстративном примере идентификатор сертификационного сервиса может представлять собой открытый ключ этого сертификационного сервиса.

В некоторых вариантах реализации идентификационный ключ 225 платформы может генерировать ведущий процессор этой платформы. Последний может быть выбран на основании того, что каждый процессор считывает заранее заданные настройки BIOS. Ведущий процессор может генерировать идентификационный ключ платформы (например, с использованием генератора случайных чисел). В одном иллюстративном примере идентификационный ключ платформы может быть представлен 128-битовым числом. В другом иллюстративном примере идентификационный ключ платформы может содержать один или несколько симметричных и/или асимметричных ключей. Ведущий процессор может дополнительно принимать идентификатор и открытый ключ сертификационного сервиса 240, например, посредством считывания заранее заданных настроек BIOS. Ведущий процессор может сообщить идентификационный ключ платформы и идентификатор сертификационного сервиса другим процессорам своей платформы с использованием безопасного канала связи, защищенного долговременными ключами связи, согласованными процессорами платформы, как это было описано выше.

После синхронизации функций безопасности с другими процессорами платформы каждый процессор может зашифровать с применением своего идентификационного ключа, ключевой двоичный объект (blob) 250, содержащий идентификационный ключ платформы и долговременные ключи для межпроцессорной связи. В некоторых вариантах реализации ключевой двоичный объект может дополнительно содержать идентификатор сертификационного сервиса. Процессор может сохранять такой ключевой двоичный объект в заданной позиции энергонезависимой памяти 255 (например, во флэш-памяти или на жестком диске), и может вызывать этот ключевой двоичный объект при последующих загрузках платформы.

После синхронизации функций безопасности с другими процессорами платформы каждый процессор этой платформы может дополнительно создать манифест 230 платформы, содержащий идентификационный ключ платформы и идентификационные ключи процессоров этой платформы. Каждый процессор может затем зашифровать манифест с применением открытого ключа сертификационного сервиса и передать зашифрованный манифест этому сертификационному сервису 240.

Сертификационный сервис 240 может проверить действительность платформы путем расшифровки и аутентификации принятых манифестов платформы и проверить действительность идентификационного ключа каждого процессора путем сравнения с авторитетным источником данных, где хранятся все действительные идентификационные ключи процессоров (например, у изготовителя или дистрибьютора процессоров). Сертификационный сервис может дополнительно убедиться, что манифесты были приняты от всех процессоров, входящих в состав рассматриваемой платформы, предотвращая тем самым попытки процессоров скрыть свое присутствие в составе платформы.

В ответ на успешную проверку действительности всех процессоров в составе платформы сертификационный сервис может записать идентификационный ключ платформы 225 в базе 260 данных для обеспечения ключей и выдать аттестационный ключ 270. Сертификационный сервис может дополнительно передать аттестационный ключ платформы обеспечивающему сервису 280. Приложение 290 защищенного анклава, исполняемое процессорной системой 200, может затем передать идентификационный ключ 225 своей платформы 225 обеспечивающему сервису, чтобы вызвать данные, чувствительные с точки зрения безопасности.

В некоторых вариантах реализации доступность канала связи для внешнего сертификационного сервиса может потребоваться только при первой загрузке платформы. При последующих загрузках каждый процессор может вызывать ключевой двоичный объект (blob), хранящийся в заданной позиции энергонезависимой памяти и расшифровывать идентификационный ключ платформы и долговременные ключи для межпроцессорной связи. После этого каждый процессор может установить защищенные каналы связи с другими процессорами своей платформы с использованием этих долговременных ключей для межпроцессорной связи с целью повторной аутентификации других процессоров платформы. После того, как каждый процессор платформы удостоверится, что все процессоры, присутствовавшие на платформе прежде последней загрузки, по-прежнему присутствуют на платформе и что на эту платформу не были добавлены новые процессоры, платформа может декларировать, что она соответствует конфигурации, которая ранее была сертифицирована посредством сертификационного сервиса.

Новый процессор может быть добавлен к ранее сертифицированной платформе путем передачи сертификационному сервису, который ранее сертифицировал эту платформу, запроса, содержащего идентификационный ключ вновь добавляемого процессора. В ответ на подтверждение действительности идентификационного ключа вновь добавляемого процессора сертификационный сервис может передать утверждающее сообщение. Вновь добавленный процессор может сохранить это утверждающее сообщение в заданной позиции энергонезависимой памяти. При новой загрузке платформы вновь добавленный процессор может вызвать это утверждающее сообщение из указанной позиции энергонезависимой памяти и представить вызванное утверждающее сообщение другим процессорам своей платформы, чтобы обменяться долговременными ключами для межпроцессорной связи, как более подробно описано выше. Этот вновь добавленный процессор может затем принять идентификационный ключ платформы от уже присутствующих процессоров по каналу связи, защищенному посредством долговременного ключа для межпроцессорной связи.

В некоторых вариантах реализации разрешение процессорам быть добавленными на платформу или удаленными с нее может создать ситуацию, когда два процессора, ранее входившие в состав одной и той же общей платформы, разделились с образованием своих собственных платформ, причем на обе новые платформы были добавлены вторые процессоры. Поскольку первые процессоры обладают ключевыми двоичными объектами (blob), содержащими идентификационный ключ их первоначальной платформы, последний может оказаться совместно используемым указанными двумя новыми платформами. Этот процесс может быть повторен, что потенциально ведет к произвольному числу платформ, совместно использующих один и тот же идентификационный ключ платформы.

Для предотвращения возможного возникновения описанного выше сценария в рамки платформы может быть введен чипсет. Этот чипсет может устанавливать уникальный идентификатор платформы. Каждый процессор может сохранить идентификатор платформы в своем ключевом двоичном объекте (blob). При повторной загрузке процессор может запросить идентификатор платформы из чипсета и сравнить полученную величину с идентификатором платформы, вызванным из ключевого двоичного объекта (blob). Если эти два идентификатора совпадут, значит, ключевой двоичный объект (blob) принадлежит текущей платформе. В противном случае процессор может инициировать процесс сертификации платформы, как это было описано выше.

На Фиг. 3 показана логическая схема примера способа генерации манифеста многопроцессорной платформы согласно одному или нескольким аспектам настоящего изобретения. Способ 300 может быть осуществлен компьютерной системой, которая может содержать аппаратную часть (например, разного рода схемы, специализированные логические устройства и/или программируемые логические устройства), программное обеспечение (например, команды, выполняемые компьютерной системой для моделирования функций аппаратуры) или сочетания аппаратуры и программного обеспечения. Способ 300 и/или каждая из его функций, процедур или операций может быть осуществлен одним или несколькими физическими процессорами из состава компьютерной системы, реализующей этот способ. Две или более функции, процедуры или операции способа могут быть выполнены параллельно или в порядке, отличном от описанного выше порядка. В некоторых вариантах реализации способ 300 может быть осуществлен посредством одного процессорного потока. В качестве альтернативы способ 300 может быть реализован посредством двух или более процессорных потоков, так что каждый поток выполняет одну или несколько индивидуальных функций, процедур или операций, составляющих способ. В иллюстративном примере процессорные потоки, реализующие способ 300 могут быть синхронизированы (например, с использованием семафоров, критических сечений и/или других механизмов синхронизации потоков). В качестве альтернативы, процессорные потоки, реализующие способ 300, могут работать асинхронно один относительно другого. В одном из примеров, показанном на Фиг. 3, способ 300 может быть осуществлен компьютерными системами, описываемыми ниже и иллюстрируемыми посредством чертежей Фиг. 5-11.

Как показано на Фиг. 3, в блоке 310 два или более процессоров могут согласовать ключи для межпроцессорной связи с целью установления защищенного канала связи. В иллюстративном примере процессоры могут выполнять протокол согласования анонимного (неаутентифицированного) ключа (например, протокол обмена ключами Диффи-Хелмана (Diffie-Hellman)), более подробно описанный выше.

В блоке 320 процессоры в составе платформы могут использовать защищенный канал связи для обмена своими идентификационными ключами и синхронизации группы функций безопасности. Последние могут содержать идентификационный ключ платформы и идентификатор сертификационного сервиса, который должна использовать эта платформа.

В блоке 330 платформа может назначить ведущий процессор. В иллюстративном примере этот ведущий процессор может быть идентифицирован настройками BIOS.

В блоке 340 ведущий процессор может генерировать идентификационный ключ платформы (например, с использованием генератора случайных чисел). В иллюстративном примере идентификационный ключ платформы может представлять собой 128-битовое число.

В блоке 350 ведущий процессор может принять идентификатор и открытый ключ внешнего сертификационного сервиса, например, посредством считывания заданных настроек BIOS.

В блоке 360 процессоры из состава платформы могут синхронизировать функции безопасности платформы, содержащие идентификационный ключ платформы и идентификатор сертификационного органа. Ведущий процессор может сообщить идентификационный ключ платформы и идентификатор сертификационного сервиса другим процессорам своей платформы с использованием безопасных каналов связи, защищенных посредством долговременных ключей для связи, согласованных, как описано выше со ссылками на блок 310.

В блоке 370 каждый процессор платформы может зашифровать, с использованием идентификационного ключа, ключевой двоичный объект (blob), содержащий идентификационный ключ платформы и долговременный ключ для межпроцессорной связи. Процессор может сохранить этот ключевой двоичный объект в заданной позиции в энергонезависимой памяти, как это было более подробно описано выше.

В блоке 380 каждый процессор из состава платформы может создать манифест платформы, содержащий идентификационный ключ платформы и идентификационные ключи процессоров из состава платформы.

В блоке 380 каждый процессор в составе платформы может «подписать» манифест платформы и зашифровать его открытым ключом сертификационного сервиса, после чего передать зашифрованный манифест сертификационному сервису для проверки действительности, как это более подробно описано выше.

На Фиг. 4 показана логическая схема примера способа перекрестной (взаимной) аутентификации процессоров в составе многопроцессорной платформы при второй и последующих загрузках платформы согласно одному или нескольким аспектам настоящего изобретения. Способ 400 может быть осуществлен компьютерной системой, которая может содержать аппаратную часть (например, разного рода схемы, специализированные логические устройства и/или программируемые логические устройства), программное обеспечение (например, команды, выполняемые компьютерной системой для моделирования функций аппаратуры) или сочетания аппаратуры и программного обеспечения. Способ 400 и/или каждая из его функций, процедур или операций может быть осуществлен одним или несколькими физическими процессорами из состава компьютерной системы, реализующей этот способ. Две или более функции, процедуры или операции способа 400 могут быть выполнены параллельно или в порядке, отличном от описанного выше порядка. В некоторых вариантах реализации способ 400 может быть осуществлен посредством одного процессорного потока. В качестве альтернативы способ 400 может быть реализован посредством двух или более процессорных потоков, так что каждый поток выполняет одну или несколько индивидуальных функций, процедур или операций, составляющих способ. В иллюстративном примере процессорные потоки, реализующие способ 400 могут быть синхронизированы (например, с использованием семафоров, критических сечений и/или других механизмов синхронизации потоков). В качестве альтернативы, процессорные потоки, реализующие способ 400, могут работать асинхронно один относительно другого. В одном из примеров, показанном на Фиг. 4, способ 400 может быть осуществлен компьютерными системами, описываемыми ниже и иллюстрируемыми посредством чертежей Фиг. 5-11.

В блоке 410 после перезагрузки платформы каждый процессор из состава платформы может вызвать ключевой двоичный объект (blob), предварительно сохраненный в заданной позиции энергонезависимой памяти, как это более подробно описанный выше.

В блоке 420 каждый процессор из состава платформы может расшифровать свой ключевой двоичный объект (blob) для генерации идентификационного ключа платформы и долговременных ключей для межпроцессорной связи.

В блоке 430 каждый процессор платформы может установить защищенные каналы связи с другими процессорами платформы с использованием долговременного ключа для межпроцессорной связи с целью повторной аутентификации других процессоров платформы.

В блоке 440, после того как каждый процессор платформы удостоверится, что все процессоры, присутствовавшие на платформе прежде последней загрузки, по-прежнему присутствуют на платформе и что на эту платформу не были добавлены новые процессоры, платформа может декларировать, что она соответствует конфигурации, которая ранее была сертифицирована посредством сертификационного сервиса.

Хотя разнообразные системы и способы описаны здесь со ссылками на конкретные интегральные схемы, такие как процессоры, другие варианты реализации могут быть применимы к интегральным схемам и логическим устройствам других типов. Технологии и правила, относящиеся к системам и способам, описанным здесь, могут быть применимы к схемам и полупроводниковым приборам других типов, которые могут также получить выигрыш от более высокой эффективности и энергосбережения. Например, рассматриваемые варианты не ограничиваются каким-либо конкретным типом компьютерной системы и могут быть также использованы в других устройствах, таких как ручные устройства, системы на кристалле (SoC) и встроенные приложения. К некоторым примерам ручных устройств относятся сотовые телефоны, устройства Интернет-протокола, цифровые видеокамеры, персональные цифровые помощники (PDA) и ручные компьютеры. К встроенным приложениям могут относиться микроконтроллер, цифровой процессор сигнала (DSP), сетевые компьютеры (NetPC), разного рода приставки, сетевые концентраторы, коммутаторы глобальных сетей связи (WAN) или какие-либо другие системы, способные осуществлять рассматриваемые здесь функции и операции, описанные ниже. Более того, рассматриваемые здесь системы и способы не ограничиваются физическими компьютерными устройствами, а могут также относиться к способам, реализованным в программном обеспечении. Энергосбережение, реализуемое посредством рассматриваемых здесь систем и способов, может быть независимым от или в дополнение к механизмам на основе операционной системы (OS), таким как стандарт Улучшенного интерфейса для конфигурации и управления питанием (ACPI).

Рассматриваемые здесь способы и системы могут быть реализованы посредством компьютерных систем различной архитектуры, конструкции и конфигурации для портативных компьютеров, настольных компьютеров, ручных персональных компьютеров, персональных цифровых помощников, инженерных рабочих станций, серверов, сетевых концентраторов, коммутаторов, встроенных процессоров, цифровых процессоров сигнала (DSP), графических устройств, видео игровых устройств, приставок, микроконтроллеров, сотовых телефонов, портативных медиа плееров, ручных устройств и разнообразных других электронных устройств, подходящих для реализации описываемых здесь способов. В общем случае, самые разнообразные системы или электронные устройства, которые могут содержать процессоры и/или другие исполнительные устройства, аналогичные рассматриваемым здесь устройствам, в основном подходят для реализации описываемых здесь систем и способов.

Фиг. 5 представляет компонентную схему высокого уровня для одного примера компьютерной системы согласно одному или нескольким аспектам настоящего изобретения. Компьютерная система 100 может содержать два или более процессоров 110, содержащих процессорные логические устройства (логику), конфигурированные для осуществления способа генерации манифеста платформы, позволяющего произвести внешнюю сертификацию платформы согласно рассматриваемому здесь варианту. Система 100 является представителем процессорных систем на основе микропроцессоров PENTIUM III™, PENTIUM 4™, Xeon™, Itanium, XScale™ и/или StrongARM™, выпускаемых корпорацией Интел (Intel Corporation) из Санта-Клара, Калифорния, хотя также могут быть использованы и другие системы (и в том числе персональные компьютеры с другими микропроцессорами, инженерные рабочие станции, приставки и т.п.). В одном из вариантов в системе 100 работает версия операционной системы WINDOWS™, выпускаемой корпорацией Майкрософт (Microsoft Corporation) из Редмонда, Вашингтон, хотя могут быть использованы и другие операционные системы (например, UNIX и Linux), встроенное программное обеспечение и/или графические интерфейсы пользователей. Таким образом, рассмотренные здесь варианты не ограничиваются каким-либо конкретным сочетанием аппаратуры и программного обеспечения.

В иллюстративном примере процессор 110 содержит один или несколько исполнительных модулей 108 для реализации алгоритма, иными словами, для выполнения по меньшей мере одной команды. Один из вариантов может быть описан в контексте однопроцессорного настольного компьютера или серверной системы, но альтернативные варианты могут содержать многопроцессорную систему. Система 100 представляет собой пример системной архитектуры концентратора ′hub′. Процессор 110 в одном иллюстративном примере представляет собой микропроцессор с полным набором команд (CISC), микропроцессор с сокращенным набором команд (RISC), микропроцессор с очень длинным командным словом (VLIW), процессор, использующий сочетание наборов команд, или какое-либо другое процессорное устройство, такое как, например, цифровой процессор сигнала. Процессор 110 связан с процессорной шиной 110, передающей сигналы данных между процессором 110 и другими компонентами в системе 100. Элементы системы 100 (например, графический ускоритель 112, концентратор-контроллер 116 памяти, память 120, концентратор-контроллер 124 ввода/вывода, радио приемопередатчик 126, флэш-BIOS 128, сетевой контроллер 134, аудиоконтроллер 136, последовательный порт 138 расширения, контроллер 140 ввода/вывода и т.п.) выполняют свои обычные функции, хорошо известные специалистам в рассматриваемой области.

В одном из вариантов процессор 110 содержит внутренний кэш первого уровня (L1). В зависимости от архитектуры процессор 110 может иметь один внутренний кэш или несколько уровней внутренних кэшей. Другие варианты содержат сочетание внешних и внутренних кэшей в зависимости от конкретной реализации и потребностей. Регистровый файл 106 предназначен для хранения данных различных типов в разнообразных регистрах, включая целочисленные регистры, регистры с плавающей запятой, векторные регистры, банкированные регистры, теневые регистры, регистры контрольных цифр, регистры состояния и регистр указателя команд.

Исполнительный модуль 108, содержащий логические устройства для выполнения целочисленных операций и операций с плавающей запятой, также находится в процессоре 110. В одном из вариантов процессор 110 содержит ПЗУ ROM микрокодов (микрокоманд), предназначенное для сохранения микрокоманд, которые при исполнении осуществляют алгоритмы некоторых макрокоманд или обработку сложных сценариев. Здесь микрокод является потенциально обновляемым для обработки/устранения логических ошибок в процессоре 110. В одном из вариантов исполнительный модуль 108 содержит логику для работы с набором 109 команд для упакованных данных. Введение набора 109 команд для упакованных данных в набор команд процессора общего назначения вместе с соответствующими схемами для выполнения этих команд сделало возможным осуществление операций, используемых многими мультимедийными приложениями, с применением упакованных данных в процессоре 110 общего назначения. Таким образом, происходит ускорение работы многих мультимедийных приложений и более эффективное выполнение этих приложений за счет использования полной ширины шины данных процессора для осуществления операций над упакованными данными. Это потенциально исключает необходимость передачи небольших сегментов данных по шине данных процессора для выполнения одной или нескольких операций, по одному элементу данных за один раз. Альтернативные варианты такого исполнительного модуля 108 могут быть использованы также в микроконтроллерах, встроенных процессорах, графических устройствах, процессорах DSP и в логических схемах других типов.

Система 100 содержит память 120. Память 120 содержит динамическое запоминающее устройство с произвольной выборкой (DRAM), статическое запоминающее устройство с произвольной выборкой (SRAM), устройство флэш-памяти или другое запоминающее устройство. Память 120 сохраняет команды 129 и/или данные 123, представленные сигналами данных, для выполнения процессором 110. В некоторых вариантах реализации совокупность команд 129 может содержать команды, использующие исполнительную логику защищенного анклава, как это более подробно рассмотрено выше.

С шиной 110 процессора и памятью 120 соединена системная логическая интегральная схема 116. В иллюстрируемом варианте эта системная логическая интегральная схема 116 представляет собой концентратор-контроллер памяти (memory controller hub (МСН)). Процессор 110 может осуществлять связи с концентратором МСН 116 по шине 110 процессора. Концентратор МСН 116 создает широкополосный тракт 118 памяти для связи с памятью 120 с целью сохранения команд и данных и для сохранения графических команд, данных и текстур. Концентратор МСН 116 предназначен для направления сигналов данных между процессором 110, памятью 120 и другими компонентами системы 100 и для передачи в качестве моста сигналов данных между шиной 110 процессора, памятью 120 и сектором 122 ввода/вывода системы. В некоторых вариантах системная логическая интегральная схема 116 может создать графический порт для связи с графическим контроллером 112. Концентратор МСН 116 связан с памятью 120 через интерфейс 118 памяти. Графическая карта 112 связана с концентратором МСН 116 через соединение 114 ускоренного графического порта (Accelerated Graphics Port (AGP)).

Система 100 использует собственную шину 122 интерфейса концентратора для связи концентратора МСН 116 с концентратором-контроллером 130 ввода/вывода (I/O controller hub (ICH)). Концентратор ICH 130 создает прямые соединения для некоторых устройств ввода/вывода через локальную шину ввода/вывода. Эта локальная шина ввода/вывода представляет собой высокоскоростную шину ввода/вывода для соединения периферийных устройств с памятью 120, чипсетом и процессором 110. В качестве некоторых примеров можно указать аудиоконтроллер, концентратор 128 встроенных программ (флэш-BIOS), радио приемопередатчик 126, хранилище 124 данных, существующий контроллер ввода/вывода, содержащий интерфейсы для ввода данных и команд пользователем и для клавиатуры, последовательный порт расширения, такой как порт универсальной последовательной шины (USB), и сетевой контроллер 134. Хранилище 124 данных может содержать дисковод с жестким диском, дисковод для дискет, дисковод CD-ROM, устройство флэш-памяти или другое запоминающее устройство большой емкости.

Что касается других вариантов системы, команды согласно одному из вариантов могут быть использованы в системе на кристалле. Один из вариантов системы на кристалле содержит процессор и память. Память для одной такой системы представляет собой флэш-память. Флэш-память может быть расположена на том же кристалле, где находятся процессор и другие компоненты системы. Кроме того, в системе на кристалле могут располагаться и другие логические блоки, такие как контроллер памяти или графический контроллер.

Фиг. 6 представляет блок-схему микроархитектуры процессора 200, содержащего логические схемы для выполнения команд, согласно одному или нескольким аспектам настоящего изобретения. В некоторых вариантах команды могут быть построены для операций с элементами данных, имеющими размеры байта, слова, двойного слова, учетверенного слова и т.д., равно как и с данными разных типов, таких как целочисленные данные и данные с плавающей запятой с обычной и с двойной точностью. В одном из вариантов входной блок 201 для выполнения операций по порядку является частью процессора 200, осуществляющей выборку команд, которые нужно выполнить, и подготовку этих команд для последующего использования в процессорном конвейере. Этот входной блок 201 может содержать несколько модулей. В одном из вариантов устройство 226 опережающей выборки команд осуществляет выборку команд из памяти и передачу их в декодер 228 команд, который в свою очередь декодирует или интерпретирует команды. Например, в одном из вариантов декодер осуществляет декодирование принятой им команды и разбиение ее на одну или несколько операций, именуемых «микрокомандами» или «микрооперациями», которые машина может выполнить. В других вариантах декодер анализирует команду для разбиения ее на код операции и соответствующие поля данных и управления, используемые микроархитектурой для выполнения операций. В одном из вариантов трассовый кэш 230 принимает декодированные микрооперации и собирает их в упорядоченные в соответствии с программой последовательности или трассы в очереди 234 микроопераций для исполнения. Когда трассовый кэш 230 встречает сложную команду, ПЗУ ROM 232 предоставляет микрооперации, необходимые для завершения выполнения операции.

Некоторые команды преобразуются в одну микрооперацию, тогда как другим требуется несколько микроопераций для завершения полной операции. В одном из вариантов, если для завершения выполнения команды требуется больше четырех микроопераций, декодер 228 обращается в ПЗУ ROM 232 для формирования команды. В одном из вариантов команда может быть декодирована с разбиением на небольшое число микроопераций для обработки в декодере 228 команд. В другом варианте, если для осуществления операции требуется несколько микроопераций, команда может быть сохранена в ПЗУ ROM 232 микрокодов. Трассовый кэш 230 обращается в программируемую логическую матрицу (PLA) точки входа с целью определения правильного указателя микрокоманды для считывания, согласно одному из вариантов, последовательности микрокодов, чтобы завершить одну или несколько команд, из ПЗУ ROM 232 микрокодов. После того, как ПЗУ ROM 232 микрокодов завершает построение последовательности микроопераций для команды, входной блок 201 машины возобновляет выборку микроопераций из трассового кэша 230.

Исполнительный модуль 203 для выполнения команд не по порядку представляет собой пункт, где происходит подготовка команд к выполнению. Логическое устройство для выполнения команд не по порядку содержит несколько буферов для сглаживания и переупорядочения потока команд с целью оптимизации производительности при продвижении команд по конвейеру и планировании для выполнения. Распределительная логика выделяет буферы машины и ресурсы, которые нужны каждой операции для выполнения. Логическая схема псевдонимов регистров отображает логические регистры на входные позиции регистрового файла. Распределитель также назначает входные позиции для каждой микрооперации в одной из двух очередей микроопераций - одной очереди для операций с памятью и одной очереди для операций без использования памяти, перед планировщиками команд: планировщиком памяти, быстрым планировщиком 202, медленным/обычным планировщиком 204 операций с плавающей запятой и простым планировщиком 206 операций с плавающей запятой. Планировщики 202, 204, 206 микроопераций определяют, когда какая-либо микрооперация готова к выполнению, на основе готовности источников операндов для соответствующих входных регистров и доступности исполнительных ресурсов, необходимых для завершения микроопераций. Быстрый планировщик 202 в одном из вариантов может планировать в каждой половине главного тактового цикла, тогда как другие планировщики могут планировать один раз в каждом главном тактовом цикле процессора. Планировщики осуществляют арбитраж между диспетчерскими портами для планирования выполнения микроопераций.

Физические регистровые файлы 208, 210 располагаются между планировщиками 202, 204, 206 и исполнительными модулями 212, 214, 216, 218, 220, 222, 224 в исполнительном блоке 211. Система имеет отдельные регистровые файлы 208, 210 для целочисленных операций и для операций с плавающей запятой соответственно. Каждый регистровый файл 208, 210 в одном из вариантов содержит обходную схему, которая может обойти или быстро передать только что появившиеся результаты, которые еще не были записаны в регистровый файл, новым зависимым микрооперациям. Целочисленный регистровый файл 208 и регистровый файл 210 с плавающей запятой могут также обмениваться данными между собой. В одном из вариантов целочисленный регистровый файл 206 разделен на два отдельных регистровых файла - один регистровый файл для младших 32 битов данных и один регистровый файл для старших 32 битов данных. Регистровый файл 210 с плавающей запятой в одном из вариантов содержит 128 побитовых входов, поскольку команды с плавающей запятой обычно имеют операнды шириной от 64 до 128 бит.

Исполнительный блок 211 содержит исполнительные модули 212, 214, 216, 218, 220, 222, 224, где реально происходит выполнение команд. Эта секция содержит регистровые файлы 208, 210, где хранятся величины операндов целочисленных данных и данных с плавающей запятой, необходимые для выполнения микрокоманд. Процессор 200 в одном из вариантов содержит ряд исполнительных модулей: модуль 212 генерации адресов (address generation unit (AGU)), модуль AGU 214, быстрое арифметическо-логическое устройство (АЛУ (ALU)) 216, быстрое АЛУ ALU 218, медленное АЛУ ALU 220, АЛУ ALU 222 для операций с плавающей запятой, модуль 224 перемещения (копирования) данных с плавающей запятой. В одном из вариантов исполнительные модули 222, 224 для операций с плавающей запятой выполняют операции с плавающей запятой, ММХ, SIMD и SSE, либо другие операции. АЛУ ALU 222 для операций с плавающей запятой в одном из вариантов содержит делитель размером 64 бит × 64 бит для чисел с плавающей запятой для выполнения микроопераций деления, извлечения корня квадратного и вычисления остатка. В рассматриваемых здесь системах и способах команды с участием величины с плавающей запятой можно обрабатывать в аппаратуре для выполнения операций с плавающей запятой. В одном из вариантов операции АЛУ (ALU) направляют в высокоскоростные исполнительные модули 216, 218 ALU. Быстрые АЛУ ALU 216, 218 в одном из вариантов могут выполнять быстрые операции с эффективной задержкой, равной половине тактового цикла. В одном из вариантов наиболее сложные целочисленные операции направляют в медленное АЛУ ALU 220, поскольку это медленное АЛУ ALU 220 содержит аппаратуру для выполнения целочисленных операций, которым присуща большая задержка, таких как операции перемножения, сдвига, логические операции с флагами и обработка ветвлений. Операции загрузки/сохранения в памяти выполняют модули AGU 212, 214. В одном из вариантов, целочисленные АЛУ ALU 216, 218, 220 рассмотрены в контексте выполнения целочисленных операций над операндами данных размером 64 бит. В альтернативных вариантах АЛУ ALU 216, 218, 220 могут быть реализованы для поддержки операций с данными различного размера и в том числе размером 16, 32, 128, 256 бит и т.д. Аналогично, модули 222, 224 для операций с плавающей запятой могут быть реализованы для поддержки операндов различной ширины. В одном из вариантов, модули 222, 224 для операций с плавающей запятой могут работать с упакованными операндами данных шириной 128 бит в связи с командами типа SIMD (одна команда - несколько элементов данных) и мультимедийными командами.

В одном из вариантов, планировщики 202, 204, 206 микроопераций диспетчируют зависимые операции прежде, чем будет завершено выполнение исходной («родительской») загрузки. Поскольку микрооперации в процессоре 200 планируют и выполняют с упреждением, этот процессор 200 содержит также логику для обработки промахов в памяти. Если в кэше данных произошел промах, в конвейере могут находиться в процессе исполнения зависимые операции, которые оставили планировщику временно неправильные данные. Механизм повторного исполнения отслеживает и выполняет повторно команды, использовавшие неправильные данные. Зависимые операции следует выполнить повторно, а независимые операции могут быть завершены. Планировщики и механизм повторного исполнения в одном из вариантов процессора также рассчитаны на то, чтобы захватывать последовательности команд для операций сравнения текстовой строки.

Термин «регистры» может относиться к расположенным в самом процессоре областям памяти, используемым как часть команд для идентификации операндов. Другими словами, бывают такие регистры, которые могут использоваться извне процессора (с точки зрения программиста). Однако в одном из вариантов не следует ограничивать регистры по значению только конкретным типом схем. Напротив, регистры в одном из вариантов способны хранить и предоставлять данные и осуществлять описываемые здесь функции. Описываемые здесь регистры могут быть реализованы в виде схем в составе процессора с применением какого-либо числа различных технологий, таких как выделенные физические регистры, динамически назначаемые физические регистры, использующие псевдонимы, сочетание выделенных и динамически назначаемых физических регистров и т.п. В одном из вариантов, целочисленные регистры сохраняют целочисленные данные размером 32 бит.Регистровый файл в одном из вариантов также содержит восемь мультимедийных SIMD-регистров для упакованных данных. В последующем обсуждении под регистрами понимают регистры данных, предназначенные для хранения упакованных данных, такие как ММХ-регистры шириной 64 бит (именуемые также «′mm′-регистры» в некоторых случаях) в микропроцессорах по технологии ММХ™ от корпорации Intel Corporation, Санта-Клара, Калифорния. Эти ММХ-регистры, имеющиеся и в целочисленной форме, и в форме для данных с плавающей запятой, могут работать с упакованными элементами данных, сопровождающими команды типа SIMD и SSE. Аналогично ХММ-регистры шириной 128 бит, относящиеся к технологии SSE2, SSE3, SSE4 или выше (именуемой в общем случае "SSEx") также могут быть использованы для сохранения таких операндов упакованных данных. В одном из вариантов, при сохранении упакованных данных и целочисленных данных регистрам нет необходимости различать эти два типа данных. В одном из вариантов, целочисленных данные и данные с плавающей запятой могут находиться в одном и том же регистровом файле или в разных регистровых файлах. Более того, в одном из вариантов, данные с плавающей запятой и целочисленные данные могут находиться в разных регистрах или в одних и тех же регистрах.

Фиг. 7а-7b схематично иллюстрируют элементы микроархитектуры процессора согласно одному или нескольким аспектам настоящего изобретения. На Фиг. 7а процессорный конвейер 400 содержит ступень 402 выборки, ступень 404 декодирования длины, ступень 406 декодирования, ступень 408 распределения, ступень 410 переименования, ступень 412 планирования (известная также как ступень диспетчирования или выдачи), ступень 414 чтения регистров/чтения памяти, исполнительную ступень 416, ступень 418 обратной записи/записи в память, ступень 422 обработки исключении и ступень 424 фиксации, выполняющие соответствующие этапы.

На Фиг. 7b стрелки обозначают связи между двумя или более модулями, а направления стрелок указывают направление потока данных между этими модулями. На Фиг. 7b показано ядро 111 процессора, содержащее входной модуль 430, связанный с исполнительным модулем 450, причем оба модуля связаны с модулем 470 памяти.

Ядро 111 может представлять собой компьютерное ядро с уменьшенным набором команд (RISC), компьютерное ядро с полным набором команд (CISC), ядро с очень длинным командным словом (VLIW), либо ядро гибридного или какого-либо еще альтернативного типа. В качестве еще одной опции ядро 111 может представлять собой ядро специального назначения, такое как, например, сетевое ядро или ядро связи, автомат сжатия данных, графическое ядро или другое подобное ядро.

Входной модуль 430 содержит модуль 432 предсказания ветвления, связанный с модулем 434 кэша команд, который связан с буфером 436 динамической трансляции (TLB), связанным с модулем 438 выборки команд, соединенным с модулем 440 декодирования. Этот модуль декодирования или декодер может декодировать команды и генерировать на выходе одну или несколько микроопераций, входных точек микрокода, микрокоманд, других команд или других сигналов управления, которые являются результатом декодирования исходных команд, либо отражают эти команды иным образом, либо получены из исходных команд. Декодер может быть реализован с использованием самых разнообразных механизмов. К примерам таких механизмов относятся, не ограничиваясь этим, преобразовательные таблицы, разного рода аппаратные реализации, программируемые логические матрицы (PLA), ПЗУ (ROM) микрокода и т.п. Модуль 434 кэша команд дополнительно связан с модулем 476 кэша второго уровня (L2) в составе модуля 470 памяти. Модуль 440 декодирования связан с модулем 452 переименования/распределителя в составе исполнительного модуля 450.

Исполнительный модуль 450 содержит модуль 452 переименования/распределителя, соединенный с модулем 454 завершения и с группой из одного или нескольких модулей 456 планировщиков. Модули 456 планировщиков представляют произвольное число различных планировщиков, включая станции резервации, центральное окно команд и т.п. Модули 456 планировщиков связаны с модулями 458 физических регистровых файлов. Каждый из модулей 458 физических регистровых файлов представляет один или несколько физических регистровых файлов, так что разные файлы сохраняют один или несколько разных типов данных, включая скалярные целочисленные данные, скалярные данные с плавающей запятой, упакованные целочисленные данные, упакованные данные с плавающей запятой, векторные целочисленные данные, векторные данные с плавающей запятой и т.п., состояние (например, указатель команд, представляющий собой адрес следующей команды, подлежащей выполнению) и т.п. На модули 458 физических регистровых файлов наложен модуль 454 завершения для иллюстрации различных способов, какими могут быть реализованы псевдонимы регистров и внеочередное (не по порядку) исполнение (например, с использованием буферов переупорядочения и регистровых файлов завершения, с использованием будущих файлов, буферов предыстории и регистровых файлов завершения; с использованием карт регистров и пула регистров; и т.п.). В общем случае регистры архитектуры видны извне процессора или с точки зрения программиста. Возможные варианты регистров не ограничиваются какими-либо известными типами схем. Подходят самые разнообразные типы регистров, если только они способны сохранять и передавать данные, как описано здесь. К примерам подходящих регистров относятся, не ограничиваясь, выделенные физические регистры, динамически назначаемые физические регистры с использованием псевдонимов регистров, сочетания выделенных и динамически назначаемых физических регистров и т.п. Модуль 454 завершения и модули 458 физических регистровых файлов связаны с исполнительными кластерами 460. Исполнительный кластер 460 содержит группу из одного или нескольких исполнительных модулей 462 и группу из одного или нескольких модулей 464 доступа к памяти. Исполнительные модули 462 могут осуществлять различные операции (например, сдвиги, суммирование, вычитание, перемножение) над разнообразными типами данных (например, скалярными данными с плавающей запятой, упакованными целочисленными данными, упакованными данными с плавающей запятой, векторными целочисленными данными, векторными данными с плавающей запятой). Тогда как некоторые варианты могут содержать несколько исполнительных модулей, предназначенных для выполнения конкретных функций или групп функций, другие варианты могут содержать один исполнительный модуль или несколько исполнительных модулей, так что все эти модули выполняют все функции. На чертеже показано, что модулей каждого типа - модулей 456 планировщиков, модулей 458 физических регистровых файлов и исполнительных кластеров, может быть несколько, поскольку некоторые варианты создают отдельные конвейеры для некоторых типов данных/операций (например, конвейер для скалярных целочисленных данных, конвейер для скалярных данных с плавающей запятой/упакованных целочисленных данных/упакованных данных с плавающей запятой/векторных целочисленных данных/векторных данных с плавающей запятой и/или конвейер для доступа к памяти, так что каждый конвейер имеет свой собственный модуль планировщика, модуль физических регистровых файлов и/или исполнительный кластер, - а в случае отдельного конвейера для доступа к памяти, некоторые варианты реализованы так, что в них исполнительный кластер этого конвейера имеет модули 464 доступа к памяти). Следует также понимать, что в случае использования разных конвейеров один или несколько таких конвейеров могут осуществлять внеочередные выдачу/исполнение команд, а остальные - выполнять команды по порядку.

Группа модулей 464 доступа к памяти связана с модулем 470 памяти, который содержит модуль 472 буфера TLB данных, связанный с модулем 474 кэша данных, который связан с модулем 476 кэша второго уровня (L2). В одном примере варианта модули 464 доступа к памяти могут содержать модуль загрузки, модуль хранения адресов и модуль хранения данных, каждый из которых связан с модулем 472 буфера TLB данных в составе модуля 470 памяти. Модуля 476 кэша L2 связан с одним или несколькими другими уровнями кэша и, в конечном счете, с главной памятью.

В качестве примера, архитектура ядра с псевдонимами регистров и внеочередной выдачей/исполнением команд может реализовать конвейер 400 следующим образом: модуль 438 выборки команд выполняет этапы 402 и 404 выборки и декодирования длины; модуль 440 декодирования выполняет этап 406 декодирования; модуль 452 переименования/распределителя выполняет этап 408 распределения и этап 410 переименования; модули 456 планировщиков выполняют этап 412 планирования; модули 458 физических регистровых файлов и модуль 470 памяти выполняют этап 414 чтения регистров/чтения памяти; исполнительный кластер 460 выполняет исполнительный этап 416; модуль памяти 470 и модули 458 физических регистровых файлов выполняют этап 418 обратной записи/записи в память; различные модули могут участвовать в этапе 422 обработки исключений; а модуль 454 завершения и модули 458 физических регистровых файлов выполняют этап 424 фиксации.

Ядро 111 может поддерживать один или несколько наборов команд (например, набор команд х86 (с некоторыми расширениями, которые были добавлены в более новых версиях); набор команд MIPS от компании MIPS Technologies из Солнечной долины, Калифорния; набор команд ARM (с дополнительными расширениями, такими как NEON) от компании ARM Holdings из Солнечной долины, Калифорния).

В некоторых вариантах реализации ядро может поддерживать многопоточность (выполнение двух или более параллельных групп операций или потоков) и может делать это различными способами, включая многопоточность с разделением времени, одновременную многопоточность (когда одно физическое ядро создает свое логическое ядро для каждого из потоков, которые это физическое ядро выполняет одновременно) или сочетание этих подходов (например, выборку и декодирование осуществляют с разделением времени, а затем применяют одновременную многопоточность, как это делается согласно технологии Intel® Hyperthreading).

Хотя псевдонимы регистров рассмотрены здесь в контексте внеочередного выполнения, должно быть понятно, что такие псевдонимы регистров могут быть использованы также в архитектуре с выполнением команд по порядку. Хотя в иллюстративном примере процессор также содержит раздельные модули 4з4/474 кэшей команд и данных и совместно используемый модуль 476 кэша L2, альтернативные варианты могут иметь единый внутренний кэш и для команд, и для данных, такой, например, как внутренний кэш первого уровня (L1), или несколько уровней внутреннего кэша. В некоторых вариантах система может содержать сочетание внутреннего кэша и внешнего кэша, являющегося внешним относительно ядра и/или процессора. В качестве альтернативы, все кэши могут быть внешними относительно ядра и/или процессора.

В некоторых вариантах реализации процессорное ядро 111 может быть спроектировано в качестве ядра с внеочередным выполнением операций (out-of-order (ООО)), чтобы повысить производительность посредством выполнения команд сразу же, как станут доступными операнды для этих команд, а не в порядке, заданном программой. Однако такой выигрыш по производительности может быть «скомпенсирован» значительным увеличением потребляемой мощности. Когда в операционной системе доступно для планирования большое число выполняемых потоков, использование нескольких ядер с выполнением команд по порядку вместо больших ядер с внеочередным выполнением (ООО) может улучшить профиль энергопотребления процессора без ущерба для общей производительности. Таким образом, для улучшения масштабируемости производительности и энергопотребления процессора последний может быть рассчитан для поддержки переменного числа ядер в зависимости от потребностей работы и числа потоков, доступных для планирования операционной системе.

На Фиг. 8 представлена блок-схема примера компьютерной системы согласно одному или нескольким аспектам настоящего изобретения. Как показано на Фиг. 8, многопроцессорная система 700 представляет собой систему с двухпунктовым соединением и содержит первый процессор 770 и второй процессор 780, соединенные один с другим посредством двухпунктового соединения 750. Каждый из процессоров 770 и 780 может быть некой версией процессорной системы 100, способной осуществлять защищенную передачу растровых изображений дисплею, как более подробно описано выше. Хотя на чертеже показаны только два процессора 770, 780, должно быть понятно, что объем настоящего изобретения этим не ограничивается. В других вариантах в примере компьютерной системы могут быть представлены один или несколько дополнительных процессоров.

Процессоры 770 и 780 показаны с встроенными модулями 772 и 782, соответственно, контроллеров памяти. Процессор 770 содержит также в качестве части своих модулей контроллеров шин двухпунктовые (Р-Р) интерфейсы 776 и 778; аналогично, второй процессор 780 содержит интерфейсы Р-Р 786 и 788. Процессоры 770 и 780 могут обмениваться информацией через двухпунктовый (Р-Р) интерфейс 750 с использованием Р-Р интерфейсных схем 778, 788. Как показано на Фиг. 8 контроллеры IMC 772 и 782 связывают процессоры с соответствующими запоминающими устройствами, а именно памятью 732 и памятью 734, которые могут быть частями главной памяти, локально присоединенными к соответствующим процессорам.

Каждый из процессоров 770,780 может обмениваться информацией с чипсетом 790 через индивидуальные интерфейсы Р-Р 752, 754 с использованием двухпунктовых интерфейсных схем 776, 794, 786, 798. Чипсет 790 может также обмениваться информацией с высокопроизводительной графической схемой 738 через высокопроизводительный графический интерфейс 739.

Совместно используемый кэш (не показан) может входить в состав любого процессора или располагаться вне обоих процессоров, будучи, тем не менее, соединен с процессорами посредством двухпунктового соединения Р-Р, так что информация из локального кэша какого-либо одного или обоих процессоров может быть сохранена в совместно используемом кэше, если процессор переведен в режим пониженного питания.

Чипсет 790 может быть связан с первой шиной 716 через интерфейс 796. В одном из вариантов, первая шина 716 может представлять собой шину для соединения периферийных устройств (PCI), либо такую шину, как шина PCI Express или другая шина ввода/вывода третьего поколения, хотя объем настоящего изобретения этим не ограничивается.

Как показано на Фиг. 8 разнообразные устройства 714 ввода/вывода могут быть соединены с первой шиной 716 вместе с мостом 718, который связывает первую шину 716 со второй шиной 720. В одном из. вариантов, вторая шина 720 может представлять собой шину с небольшим числом контактов (low pin count (LPC)). Co второй шиной 720 могут быть соединены различные устройства, включая, например, клавиатуру и/или мышь 722, устройства 727 связи и запоминающее устройство 728, такое как дисковод или другое запоминающее устройство большой емкости, которое может содержать команды/код и данные 730, в одном из вариантов. Кроме того, со второй шиной 720 может быть соединено аудиоустройство 724 ввода/вывода.

На Фиг. 9 приведена блок-схема системы на кристалле (SoC) согласно одному или нескольким аспектам настоящего изобретения. Прикладной процессор 910, представляющий собой некоторую версию процессорной системы 100, способен осуществлять защищенную передачу растрового изображения дисплею, как это более подробно рассмотрено выше. Как схематично показано на Фиг. 9, соединительные модули 902 могут быть соединены с: прикладным процессором 910, содержащим группу из одного или нескольких ядер 902A-N и модули 906 совместно используемых кэшей; модуль 910 системного агента; модули 916 контроллеров шин; модули 914 интегральных контроллеров памяти; группу из одного или нескольких медиа процессоров 920, которые могут иметь встроенную графическую логику 908, процессор 924 изображений для реализации функций фотоаппарата и/или видеокамеры, аудиопроцессор 926 для осуществления аппаратного аудиоускорения и видео процессор 928 для реализации ускорения кодирования/декодирования видео; модуль 930 статического запоминающего устройства с произвольной выборкой (SRAM); модуль 932 прямого доступа к памяти (DMA); и модуль 940 дисплея для соединения с одним или несколькими внешними дисплеями.

На Фиг. 10 представлена блок-схема примера компьютерной системы согласно одному или нескольким аспектам настоящего изобретения. Процессор 1610 может представлять собой некоторую версию процессорной системы 100, способную осуществлять защищенную передачу растрового изображения дисплею, как это более подробно рассмотрено выше.

Система 1600, схематично изображенная на Фиг. 10, может содержать какое-либо сочетание компонентов, реализованных в виде интегральных схем, частей таких интегральных схем, дискретных электронных устройств или других модулей, логических устройств, аппаратуры, программного обеспечения, встроенных программ или сочетания перечисленных элементов, подходящего для компьютерной системы, или в виде компонентов, каким-то иным способом встроенных в шасси компьютерной системы. Блок-схема, изображенная на Фиг. 10, предназначена дать картинку высокого уровня для представления многих компонентов компьютерной системы. Однако должно быть понятно, что некоторые показанные здесь компоненты могут быть опущены, могут быть добавлены дополнительные компоненты, а в других вариантах реализации могут быть применены другие версии расположения и соединения компонентов.

Процессор 1610 может быть выполнен в виде микропроцессора, многоядерного процессора, многопоточного процессора, ультра низковольтного процессора, встроенного процессора или другого известного процессорного элемента. В показанном варианте реализации процессор 1610 действует в качестве главного процессорного модуля и центрального концентратора для связи со многими из разнообразных компонентов системы 1600. В качестве одного из примеров процессор 1610 может быть реализован в виде системы на кристалле (SoC). В качестве конкретного иллюстративного примера процессор 1610 содержит процессор на основе Intel® Architecture Core™, такой как i3, i5, i7 или другой подобный процессор, который можно приобрести у Intel Corporation, Санта-Клара, Калифорния.

Процессор 1610 может поддерживать связь с системной памятью 1615. В разнообразных вариантах реализации индивидуальные запоминающие устройства могут быть выполнены в корпусах различных типов, таких как однокристальный корпус (single die package (SDP)), двухкристалльный корпус (dual die package (DDP)) или четырехкристалльный корпус (quad die package (IP)). В некоторых вариантах реализации эти устройства могут быть непосредственно припаяны к материнской плате для создания конструкции, имеющей меньшую высоту, тогда как в других вариантах реализации такие устройства могут быть конфигурированы в виде одного или нескольких модулей памяти, которые в свою очередь соединены с материнской платой посредством соответствующих разъемов. Возможны также другие варианты реализации памяти, такие как модули памяти других типов, например, модули памяти с двухрядным расположением выводов (dual inline memory module (DIMM)) различных модификаций, включая, но не ограничиваясь, микроDIMM, миниDIMM. В одном иллюстративном примере память может иметь емкость от 2 Гбайт до 16 Гбайт и может быть конфигурирована в корпусе DDR3LM или LPDDR2 или LPDDR3, припаянном к материнской плате посредством матрицы шариковых выводов (ball grid array (BGA)).

Для постоянного хранения информации, такой как данные, приложения, одна или несколько операционных систем и т.п., с процессором 1610 может быть также соединено запоминающее устройство 1620 большой емкости. В некоторых вариантах реализации для достижения более тонкой и более легкой конструкции системы, а также для увеличения ее чувствительности и оперативности это запоминающее устройство 1620 большой емкости может реализовано в виде твердотельного SSD-накопителя. В других вариантах реализации запоминающее устройство большой емкости может содержать в первую очередь накопитель на жестком диске (HDD) вместе с SSD-накопителем меньшей емкости, действующим в качестве SSD-кэша, чтобы обеспечить энергонезависимое сохранение состояния контекста и другой подобной информации на время выключения питания и вследствие этого осуществлять быстрый запуск при возобновлении активности системы.

Как также показано на Фиг. 10, с процессором 1610 может быть соединено устройство 1622 флэш-памяти, например через последовательный интерфейс периферийных устройств (SPI). Это устройство 1622 флэш-памяти может быть использовано для энергонезависимого хранения системного программного обеспечения, включая программное обеспечение базовой системы ввода/вывода (BIOS), равно как других встроенных программ системы.