Область техники, к которой относится изобретение

Настоящая технология относится к устройству обработки данных, способу обработки данных и программе. Более конкретно, настоящая технология относится к устройству обработки данных, способу обработки данных и программе, выполняющим шифрование, например, с ключом коллективного пользования.

Уровень техники

В соответствии с прогрессом общества, ориентированного на информационное развитие, повышается потребность в технологиях защиты информации для надежной защиты используемой информации. Один из элементов конфигурации технологий защиты информации представляет собой технология шифрования, и такие технологии шифрования в настоящее время используются в различных продуктах и системах.

Существует множество различных алгоритмов обработки шифрования, и один основной пример такой технологии представляет собой, как известно, блочный шифр с общим ключом. Существуют два общих ключа с блочным шифром с общим ключом, ключ шифрования и ключ дешифрования. Во время обработки шифрования и дешифрования генерируется множество ключей, используя обработку общих ключей, и преобразование данных многократно выполняется в модулях с размером данных блока, таких как, например, модули блока размером 64 бита, 128 битов и 256 битов.

Наиболее распространенными из этих известных алгоритмов блочного шифра с общим ключом представляет собой Стандарт шифрования данных (DES), который представляет собой предыдущий стандарт США, и Усовершенствованный стандарт шифрования (AES), который представляет собой современный стандарт в США. Множество других блочных шифров с общим ключом существует или были предложены, включая в себя блочный шифр с общим ключом CLEFIA, предложенный Sony Corporation в 2007 г.

Алгоритм такого блочного шифра с общим ключом, в основном, имеет конфигурацию с узлом обработки шифрования, включающем в себя модуль исполнения раундовой функции, предназначенный для многократного исполнения преобразования входных данных, и узлом планирования ключа, предназначенным для генерирования раундовых ключей, применяемых для каждого раунда в модуле раундовой функции. Узел планирования ключа генерирует расширенный ключ с увеличенной величиной подсчета битов на основе основного секретного ключа (основного ключа) и затем генерирует раундовые ключи (вторичные ключи), применяемые для каждой функции модуля раунда узла обработки шифрования, на основе сгенерированного расширенного ключа.

Общеизвестная конкретная структура воплощения алгоритма такого рода многократно выполняет раундовую функцию, которая включает в себя модуль линейного преобразования и модуль нелинейного преобразования. Наиболее распространенные структуры такого рода представляют собой, например, структуру Фейстеля и обобщенную структуру Фейстеля. Структура Фейстеля и обобщенная структура Фейстеля преобразуют открытый текст в зашифрованный текст путем простого повторения раундовой функции, которая включает в себя F функцию, выполняющую функцию преобразования данных. F функция выполняет обработку линейного преобразования и обработку нелинейного преобразования. Дополнительные детали, раскрывающие обработку шифрования, с применением структуры Фейстеля, могут быть найдены, например, в NPL 1 и NPL 2.

Обработка нелинейного преобразования, исполняемая F функцией, выполняется, например, путем применения функции нелинейного преобразования, называемой S-блоком. S-блок представляет собой элемент конфигурации шифраторов блока и функций хеширования, и выполняет чрезвычайно важную функцию для определения характеристик безопасности и воплощения.

Такой S-блок должен иметь высокий уровень защиты. Однако возникает проблема, из-за которой размеры схемы становятся существенными для обеспечения высокого уровня защиты.

Список литературы

Не патентная литература

NPL 1: K. Nyberg, "Generalized Feistel Networks", ASIACRYPT′ 96, Springer Verlag, 1996, pp.91-104.

NPL 2: Yuliang Zheng, Tsutomu Matsumoto, Hideki Imai: On the Construction of Block Ciphers Provably Secure and Not Relying on Any Unproved Hypotheses. CRYPTO 1989:461-480.

NPL 3: US National Institute of Standards and Technology Advanced Encryption Standard, Federal Information Processing Standards Publications No. 197, 2001.

NPL 4: Aoki, Ichikawa, Kanda, Matsui, Moriai, Nakajima, Tokita, "128-bit Block Encryption Camellia Algorithm Specification", Version 2.0, 2001.

NPL 5: Chae Hoon Lim, "CRYPTON: A New 128-bit Block Cipher-Specification and Analysis (Version 0.5)".

NPL 6: Chae Hoon Lim, "CRYPTON: A New 128-bit Block Cipher-Specification and Analysis (Version 1.0)".

NPL 7: Paulo S.L. M Barreto, Vincent Rijmen "The WHIRLPOOL Hashing Function", 2003.

NPL 8: Pascal Junod and Serge Vaudenay, "FOX: a New Family of Block Ciphers", 2004.

NPL 9: Sony Corporation, "The 128-bit Blockcipher CLEFIA Algorithm Specification", Revision 1.0, 2007.

Раскрытие изобретения

Техническая задача

Настоящее раскрытие представляет собой результат учета описанной ранее ситуации, и оно нацелено на обеспечение устройства обработки данных, способа обработки данных и программы, предоставленных в миниатюрном S-блоке, имеющем высокий уровень защиты.

Решение задачи

Первый аспект настоящего раскрытия направлен на устройство обработки данных, включающее в себя: модуль обработки преобразования данных, выполненный с возможностью разделения и ввода битов конфигурации данных, подлежащих обработке во множестве линий, и многократного выполнения обработки преобразования данных для данных в каждой линии; при этом модуль обработки преобразования данных включает в себя модуль исполнения F функции, выполненный с возможностью ввода одной линии данных, конфигурирующей множество линий и генерирования данных преобразования; причем модуль выполнения F функции включает в себя модуль обработки нелинейного преобразования, выполненный с возможностью исполнения обработки нелинейного преобразования; при этом модуль обработки нелинейного преобразования включает в себя повторяющуюся структуру модуля нелинейного вычисления, состоящую из модуля вычисления, составленного из любого одного из модулей вычисления NAND или NOR, и любого одного из модулей вычисления XOR или XNOR, и модуль перестановки битов.

Что касается варианта осуществления устройства обработки данных, в соответствии с настоящим раскрытием, модуль перестановки битов включает в себя конфигурацию межсоединений, выполненную с возможностью перестановки входных и выходных битов в согласовании с модулем нелинейного вычисления.

Что касается варианта осуществления устройства обработки данных, в соответствии с настоящим раскрытием, модуль обработки нелинейного преобразования выводит один бит результата вычисления из модуля вычисления функции NAND или NOR с 2-битными входными и 1-битными выходными данными, на модуль вычисления функции XOR или XNOR, выполняет одно из вычисления XOR или XNOR для каждого второго бита входных данных, и выводит данные размером 1 бит, сгенерированные в результате вычислений одной из функций XOR или XNOR, в качестве бита конфигурации, в качестве результата обработки нелинейного преобразования.

Что касается варианта осуществления устройства обработки данных, в соответствии с настоящим раскрытием, модуль обработки нелинейного преобразования включает в себя повторяющуюся структуру, в которой конфигурация модуля нелинейного вычисления повторяется по меньшей мере n раз для вывода результата нелинейного преобразования, составляющего n битов данных.

Что касается варианта осуществления устройства обработки данных, в соответствии с настоящим раскрытием, модуль обработки нелинейного преобразования имеет конфигурацию, в которой модуль нелинейного вычисления установлен n раз, и модуль перестановки битов установлен n-1 раз между модулем нелинейного вычисления для n-кратного повторения конфигурации, для вывода результата нелинейного преобразования из n битов данных.

Что касается варианта осуществления устройства обработки данных, в соответствии с настоящим раскрытием, модуль обработки нелинейного преобразования генерирует результат вычисления для результата вычисления XOR или XNOR из результата вычисления любого одного из модулей вычисления NAND или NOR, соответствующего всем битам конфигурации данных, которые должны быть нелинейно преобразованы, и выводит результат вычисления, представляющий собой XOR или XNOR, в качестве бита конфигурации результата нелинейного преобразования.

Что касается варианта осуществления устройства обработки данных, в соответствии с настоящим раскрытием, модуль обработки нелинейного преобразования представляет собой конфигурацию, включающую в себя, как модуль вычисления XOR, так и модуль вычисления XNOR в повторяющейся структуре.

Что касается варианта осуществления устройства обработки данных, в соответствии с настоящим раскрытием, устройство обработки данных выполняет обработку шифрования для преобразования открытого текста, в качестве входных данных, в шифрованный текст, и для исполнения обработки дешифрования для преобразования шифрованного текста, в качестве входных данных, в открытый текст.

Кроме того, второй аспект настоящего раскрытия представляет собой устройство обработки данных, включающее в себя модуль обработки нелинейного преобразования, имеющий повторяющуюся структуру, состоящий из: модуля нелинейного вычисления, состоящего из любого одного из модулей вычисления NAND или NOR, и любого одного из модулей вычисления XOR или XNOR; и модуля перестановки битов.

Что касается варианта осуществления устройства обработки данных, в соответствии с настоящим раскрытием, модуль обработки нелинейного преобразования генерирует результат вычисления для одного из результата вычисления XOR или XNOR, из результата вычисления любого одного из модулей вычисления NAND или NOR, соответствующего всем битам конфигурации данных, предназначенных для нелинейного преобразования, и выводит результат вычисления XOR или XNOR, как бит конфигурации результата нелинейного преобразования.

Кроме того, третий аспект настоящего раскрытия представляет собой устройство обработки данных, включающее в себя: повторяющуюся структуру раундовой функции, которая включает в себя модуль исполнения нелинейной функции, выполненный с возможностью разделения битов данных входной конфигурации, подлежащей обработке, на множество линий и ввода одной линии данных, конфигурирующей множество линий, для генерирования данных преобразования.

Что касается варианта осуществления устройства обработки данных, в соответствии с настоящим раскрытием, модуль исполнения нелинейной функции генерирует результат вычисления по результату вычисления XOR или XNOR, из результата вычисления любого одного из модулей вычисления NAND или NOR, соответствующего всем битам конфигурации данных, которые должны быть нелинейно преобразованы, и выводит один из результатов вычисления XOR или XNOR в качестве бита конфигурации для результата нелинейного преобразования.

Кроме того, в четвертом аспекте настоящего раскрытия описан способ обработки данных, предназначенный для исполнения в устройстве обработки данных; в котором модуль обработки данных выполнен с возможностью разделения и ввода битов конфигурации данных, подлежащих обработке множеством линий, и многократно исполняет обработку преобразования данных для данных в каждой линии; при этом обработка преобразования данных содержит этап выполнения F функции, выполненной с возможностью ввода одной линии данных, конфигурирующей множество линий, и генерирования данных преобразования; причем обработка исполнения F функции содержит выполнение обработки нелинейного преобразования; при этом обработка нелинейного преобразования содержит выполнение вычисления с повторением, применяя модуль нелинейного вычисления, состоящий из модуля вычисления одной из функции NAND или NOR и модуля вычисления одной из функции XOR или XNOR, и модуля перестановки битов.

Кроме того, в пятом аспекте настоящего раскрытия представлена программа, предназначенная для исполнения обработки преобразования данных в устройстве обработки данных; при этом программа обеспечивает разделение модуля обработки данных и ввод битов конфигурации данных, подлежащих обработке во множество линий, и многократное исполнение обработки преобразования данных для данных в каждой линии; и, при обработке преобразования данных, исполнение F функции, выполненной с возможностью ввода одной линии данных, конфигурирующей множество линий и генерирования преобразованных данных; причем при исполнении F функции обеспечивается выполнение обработки нелинейного преобразования; и при обработке нелинейного преобразования обеспечивается выполнение повторяющейся структуры с использованием модуля нелинейного вычисления, составленного из любого одного из модулей вычисления NAND или NOR, или любого одного из модулей вычисления XOR или XNOR, и модуля перестановки битов.

Кроме того, программа, в соответствии с настоящим раскрытием, представляет собой программу, подаваемую в компьютерную систему, или устройство обработки информации, выполненное с возможностью, например, исполнения различного программного кода, с помощью, например, носителя записи. Обработка выполняется через программу путем исполнения такого рода программы модулем исполнения программы, в устройстве обработки информации или компьютерной системе.

Другие цели, свойства и преимущества настоящего раскрытия будут понятны после подробного описания изобретения на основе вариантов осуществления настоящего изобретения, которые описаны ниже, и из приложенных чертежей. Кроме того, система в отношении настоящего описания представляет собой конфигурацию логической комбинации из множества устройств, и, таким образом, каждая конфигурация устройств не ограничена размещением его в одном и том же физическом модуле.

Полезные эффекты изобретения

В соответствии с вариантом осуществления настоящего раскрытия, обеспечивается миниатюризированный модуль нелинейного преобразования.

В частности, включен узел обработки шифрования, выполненный с возможностью разделения и ввода битов конфигурации данных, предназначенных для обработки во множестве линий, и для многократного выполнения обработки преобразования данных, применяющей раундовую функцию, в качестве данных в каждой линии, в которой часть обработки шифрования включает в себя модуль исполнения F функции, выполненный с возможностью ввода одной линии данных, конфигурирующей множество линий, и для генерирования данных преобразования, в котором модуль исполнения F функции включает в себя модуль обработки нелинейного преобразования, выполненный с возможностью выполнения обработки нелинейного преобразования, и в котором модуль обработки нелинейного преобразования включает в себя структуру повторения модуля нелинейного вычисления, составленную из любого одного из модулей вычисления NAND или NOR или любого одного из модулей вычисления XOR или XNOR, и модуль перестановки битов. Миниатюризированный модуль нелинейного преобразования получается в результате такой конфигурации повторения.

Краткое описание чертежей

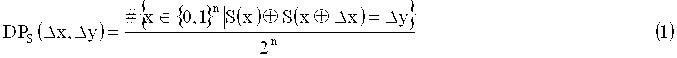

На фиг.1 показана схема, описывающая n-битный алгоритм блочного шифрования с общим ключом, соответствующий длине ключа k битов.

На фиг.2 показана схема, описывающая алгоритм дешифрования, соответствующий n-битному алгоритму блочного шифрования с общим ключом, соответствующему длине ключа k битов, представленному на фиг.1.

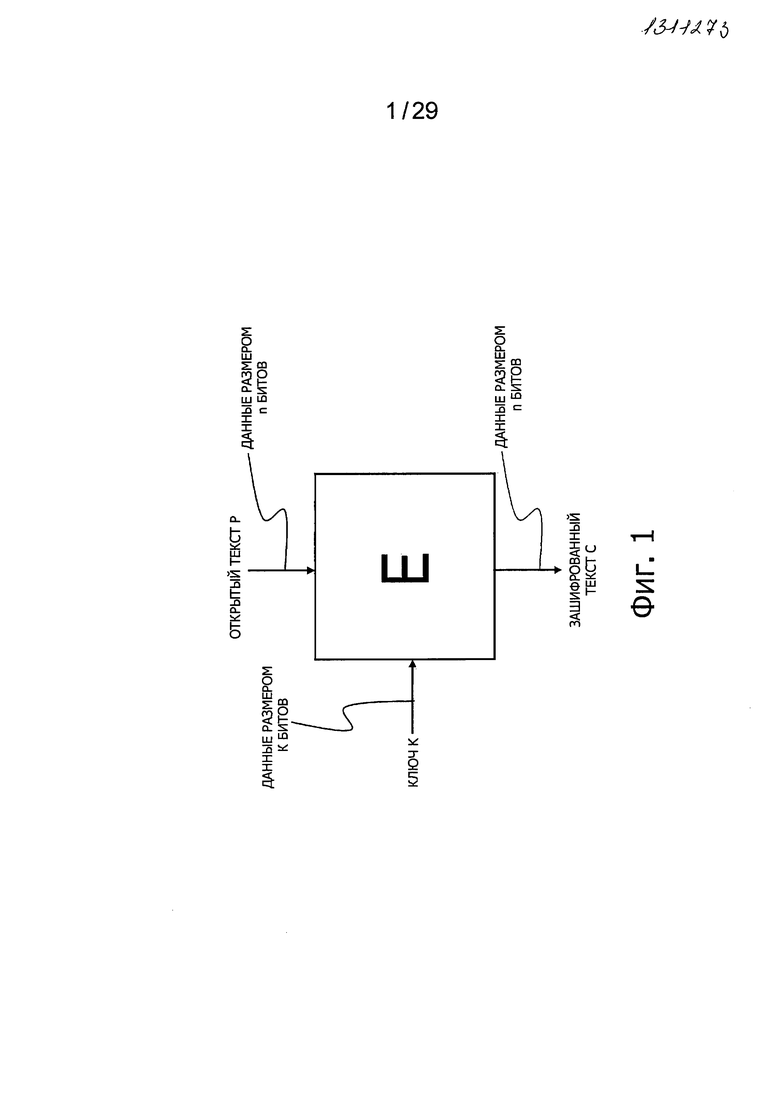

На фиг.3 показана схема, описывающая взаимосвязь между узлом планирования ключа и модулем шифрования данных.

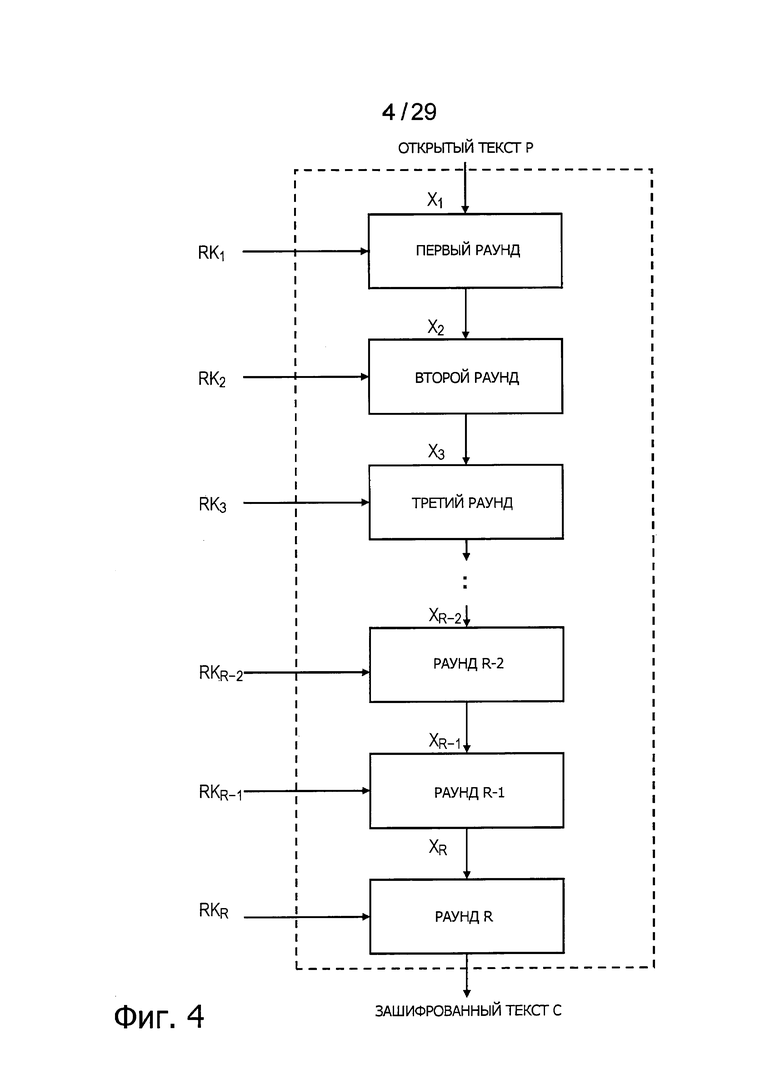

На фиг.4 показана схема, описывающая пример конфигурации модуля шифрования данных.

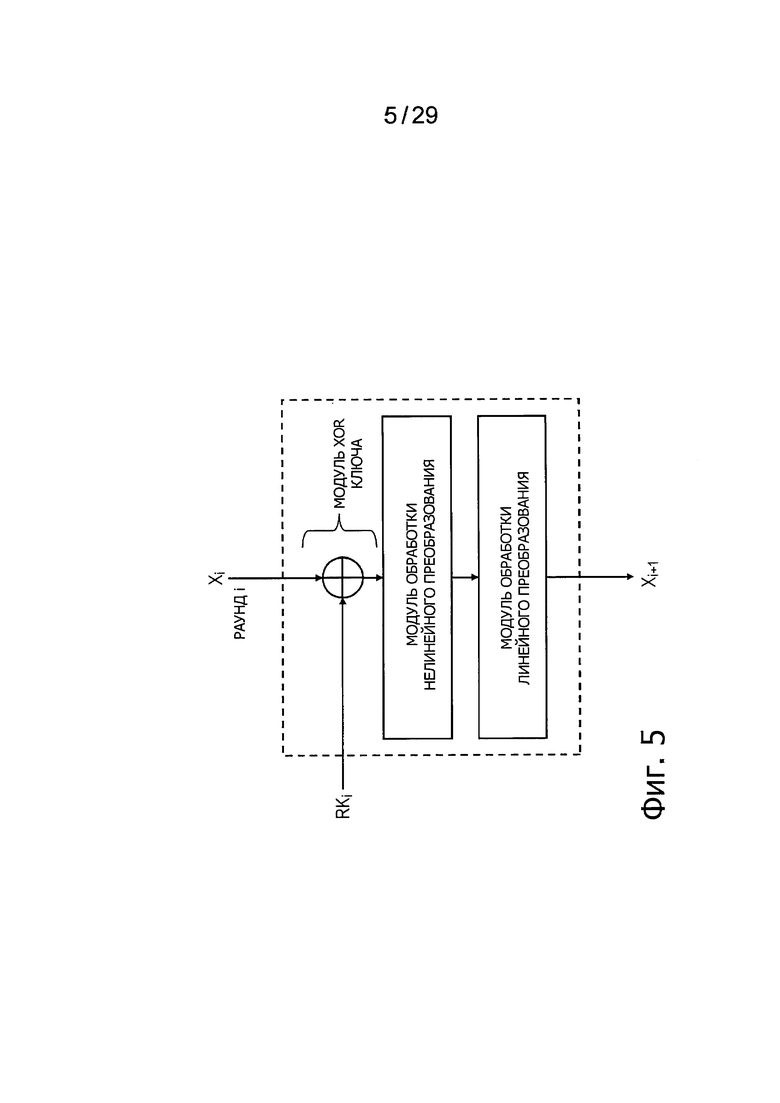

На фиг.5 показана схема, описывающая пример раундовой функции структуры SPN.

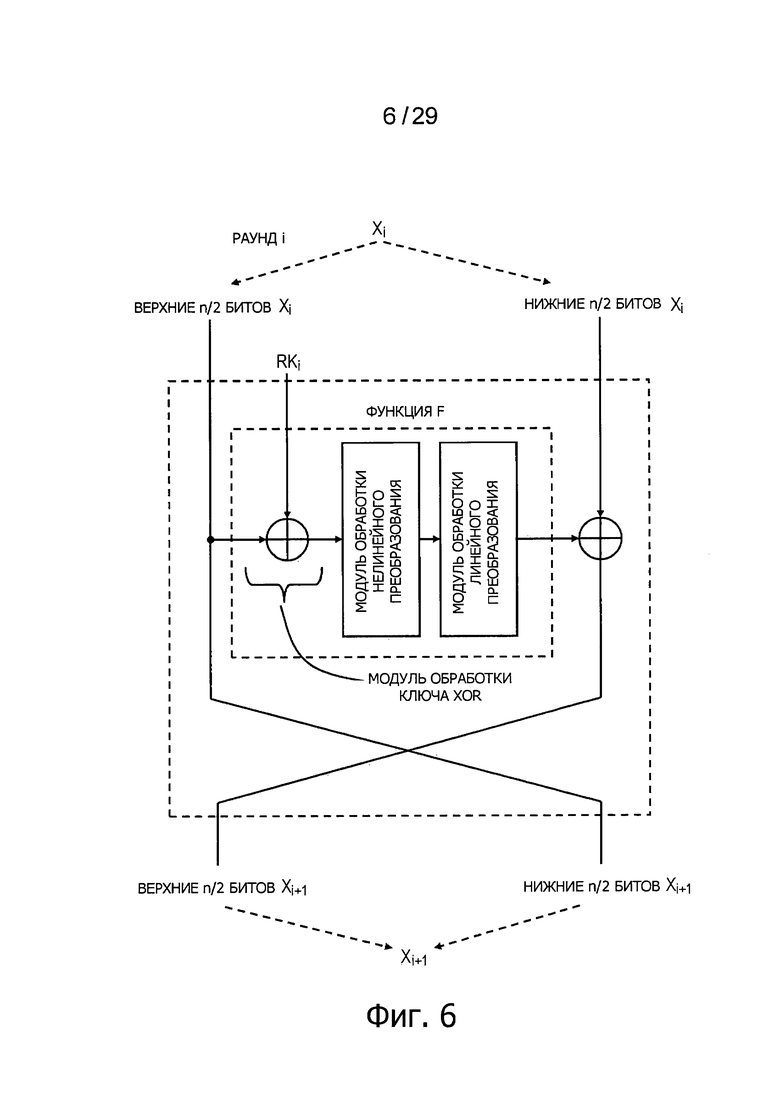

На фиг.6 показана схема, описывающая пример раундовой функции структуры Фейстеля.

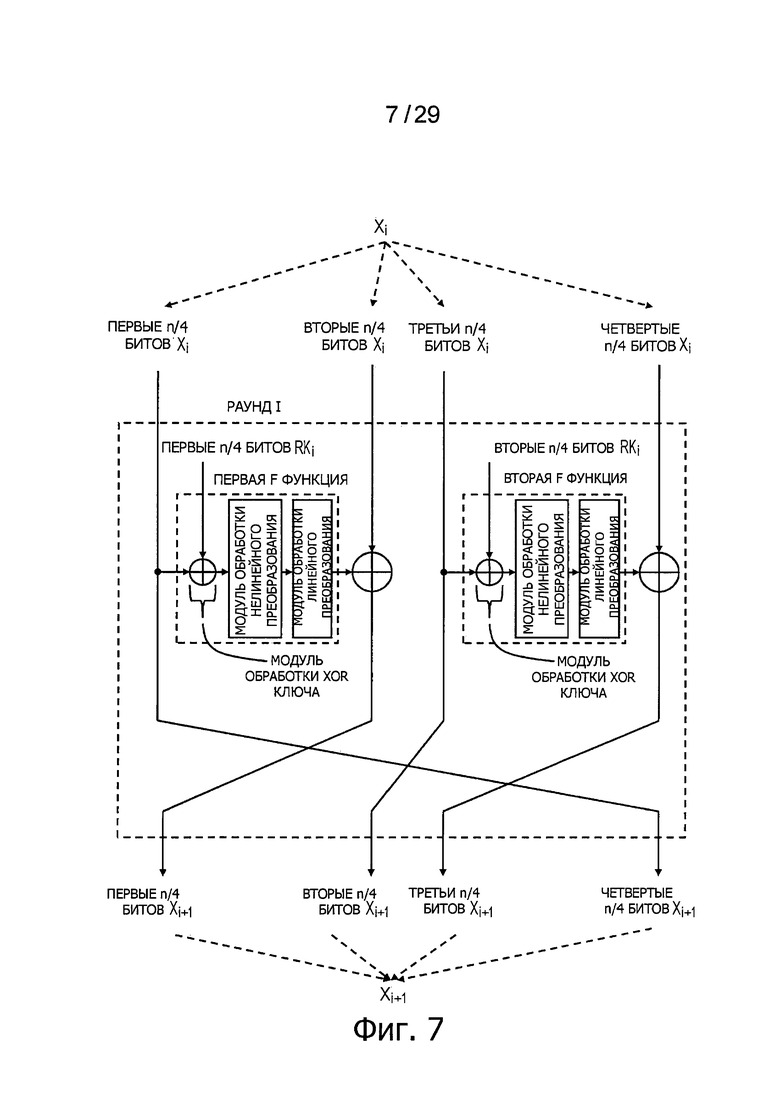

На фиг.7 показана схема, описывающая пример расширенной структуры Фейстеля.

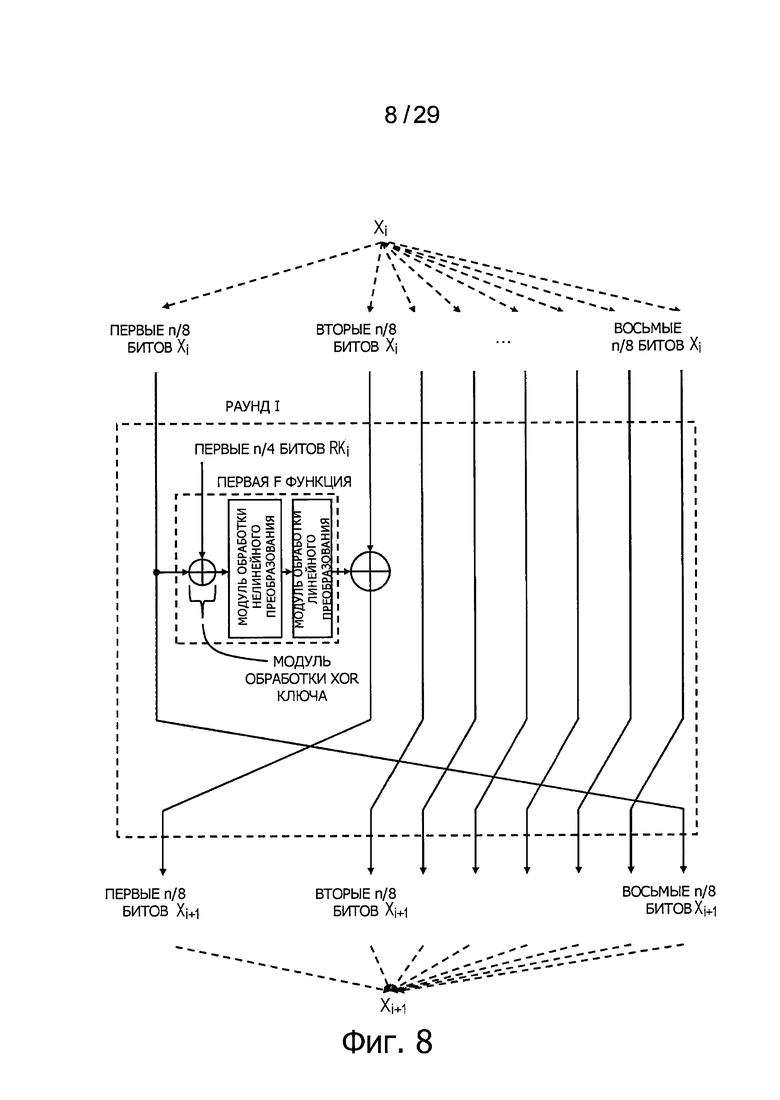

На фиг.8 показана схема, описывающая пример расширенной структуры Фейстеля.

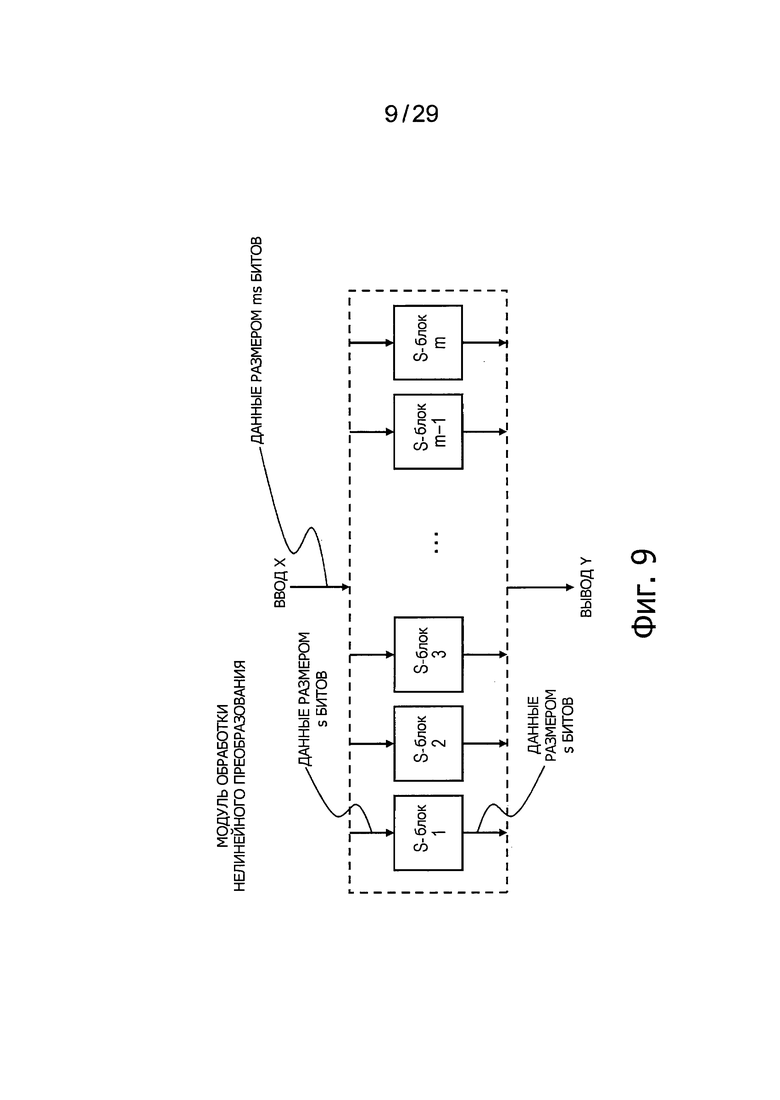

На фиг.9 показана схема, описывающая пример конфигурации нелинейного модуля преобразования.

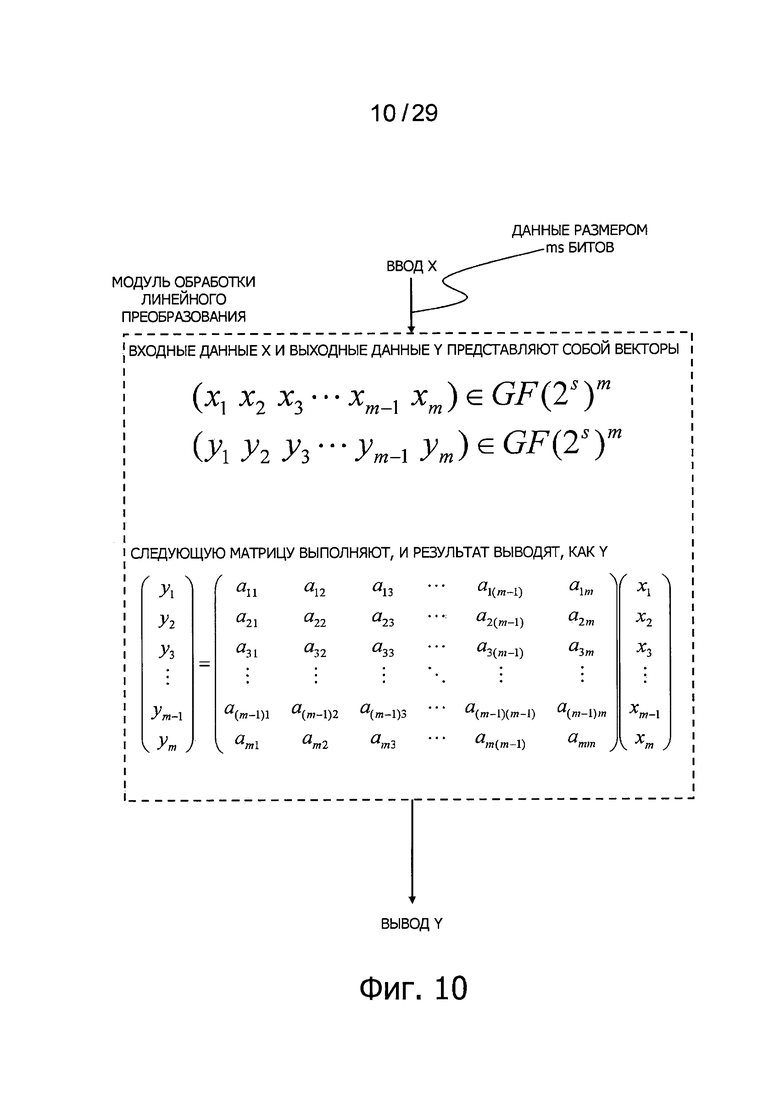

На фиг.10 показана схема, описывающая пример конфигурации модуля обработки линейного преобразования.

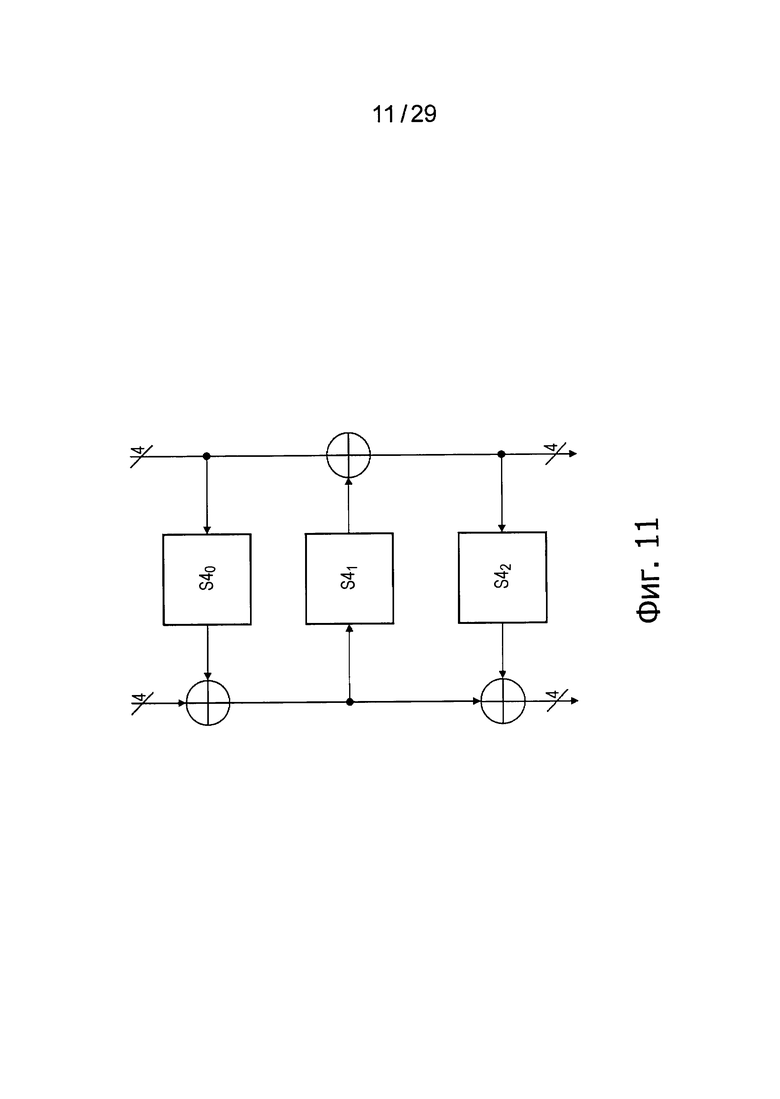

На фиг.11 показана схема, описывающая пример конфигурации для генерирования больших S-блоков путем комбинирования множества модулей S-блоков, имеющих входные-выходные данные небольшого размера.

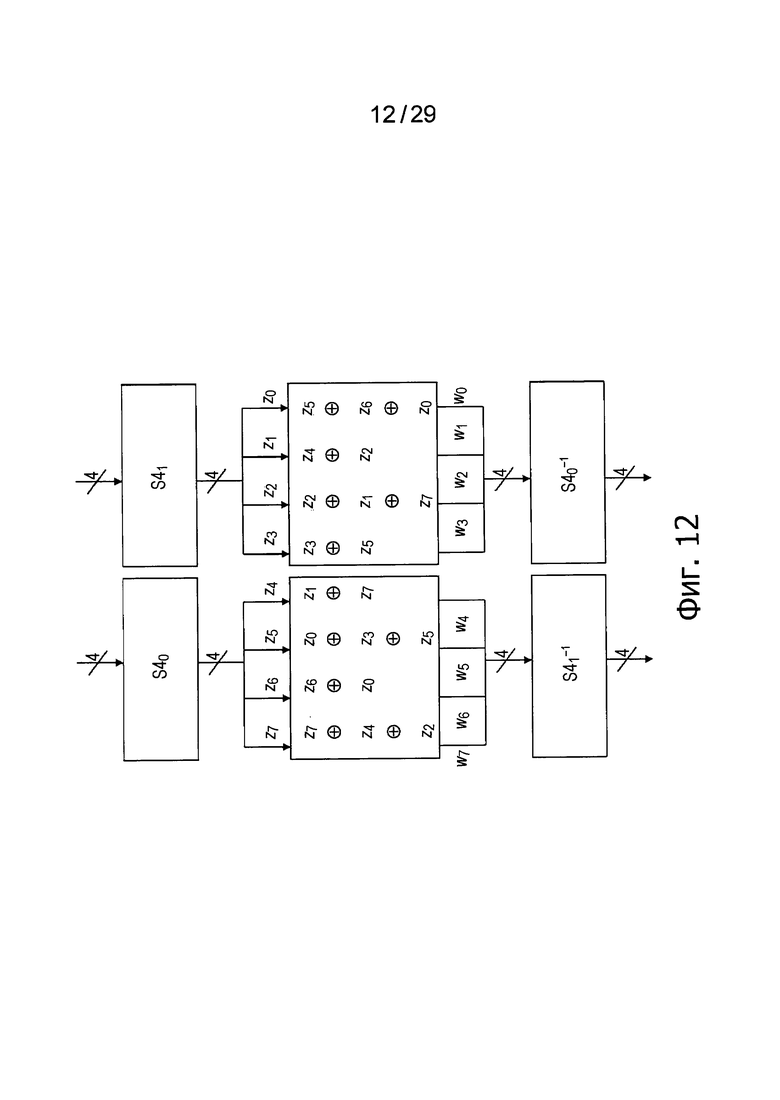

На фиг.12 показана схема, описывающая пример конфигурации для генерирования больших S-блоков путем комбинирования множества модулей S-блоков, имеющих входные-выходные данные небольшого размера.

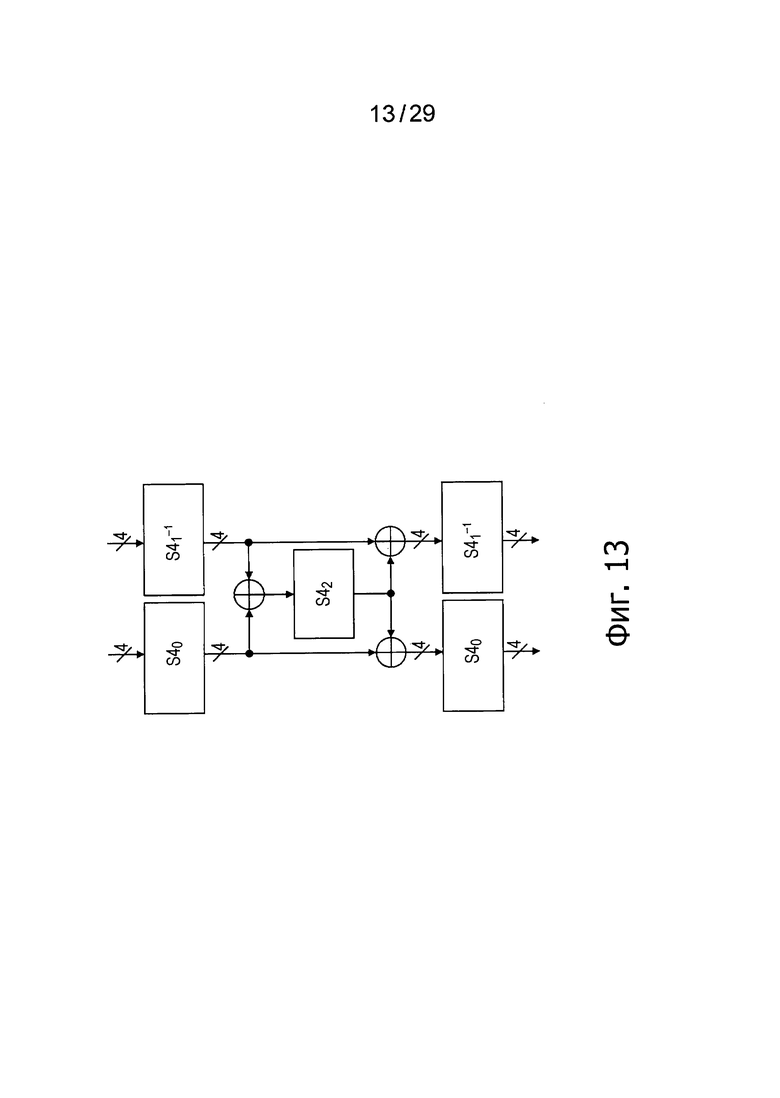

На фиг.13 показана схема, описывающая пример конфигурации для генерирования больших S-блоков путем комбинирования множества модулей S-блоков имеющих входные-выходные данные небольшого размера.

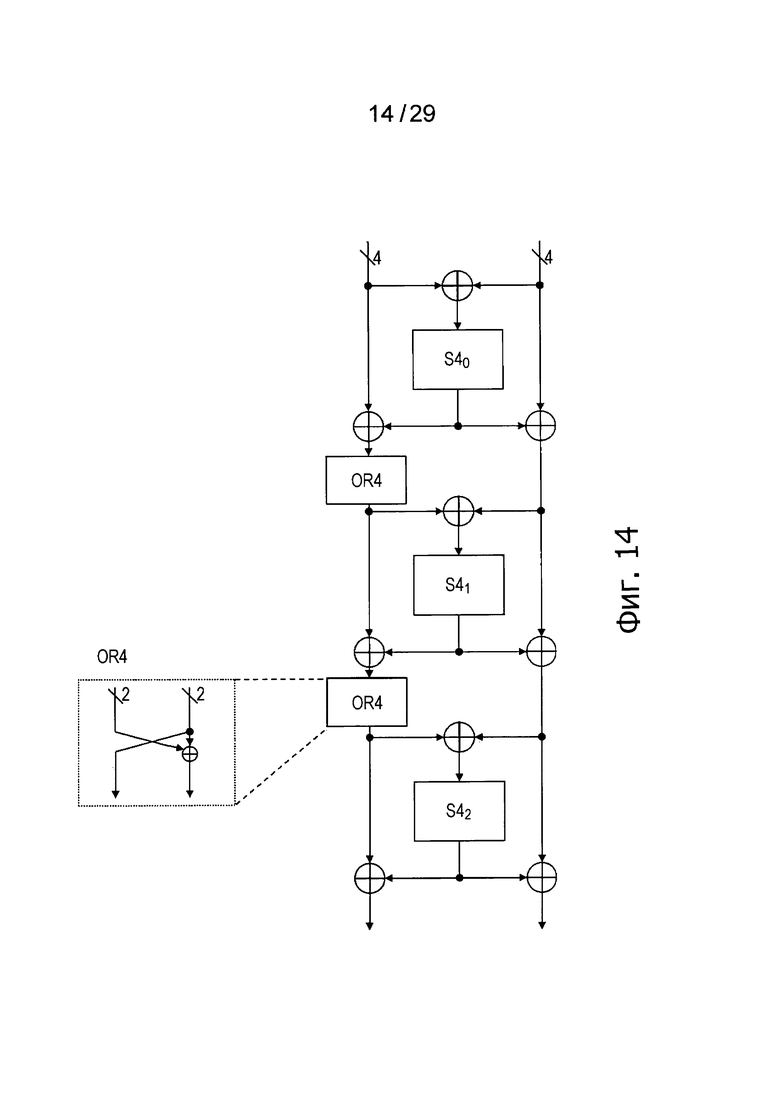

На фиг.14 показана схема, описывающая пример конфигурации для генерирования больших S-блоков путем комбинирования множества модулей S-блоков имеющих входные-выходные данные небольшого размера.

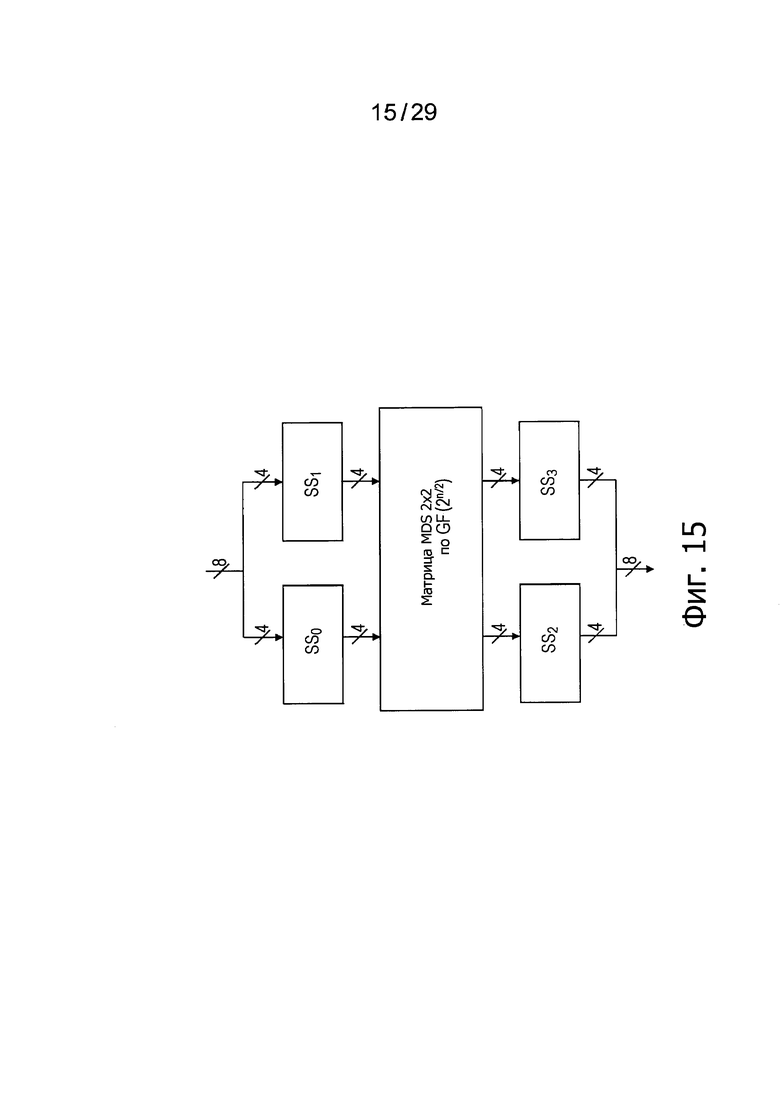

На фиг.15 показана схема, описывающая пример конфигурации для генерирования больших S-блоков путем комбинирования множества модулей S-блоков имеющих входные-выходные данные небольшого размера.

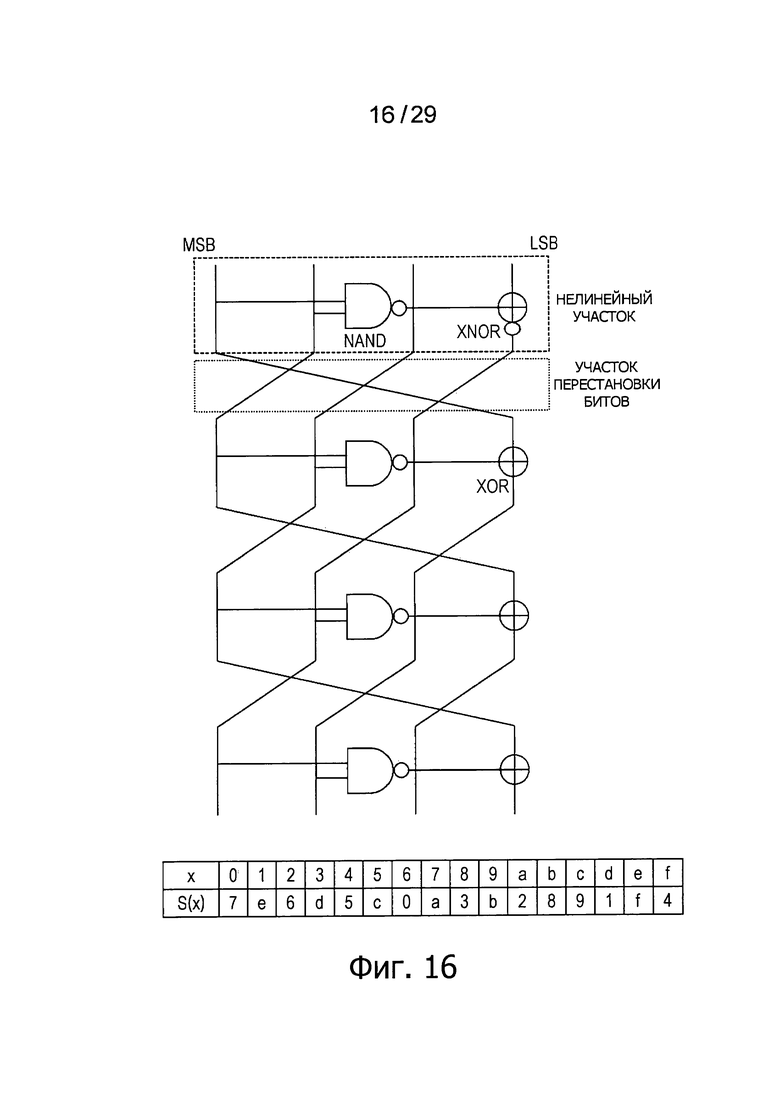

На фиг.16 показана схема, описывающая пример конфигурации 4-битных S-блоков из повторяющейся структуры логических вычислений и перестановки битов.

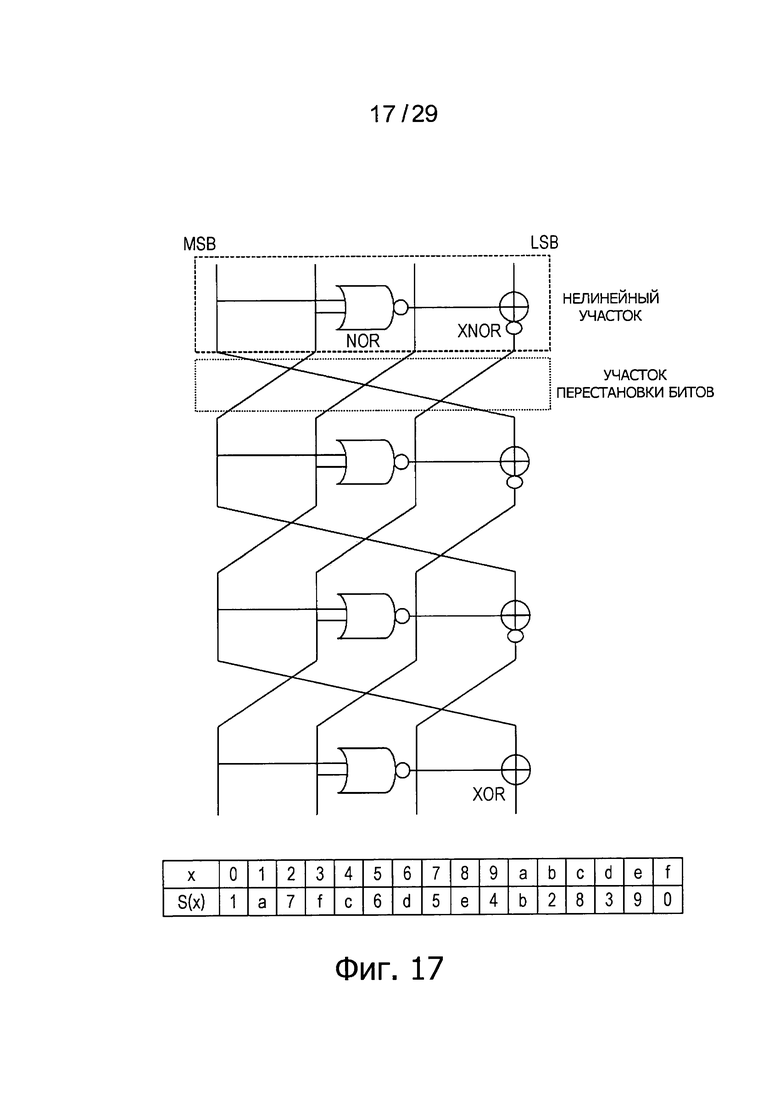

На фиг.17 показана схема, описывающая пример конфигурации 4-битных S-блоков из повторяющейся структуры логических вычислений и перестановки битов.

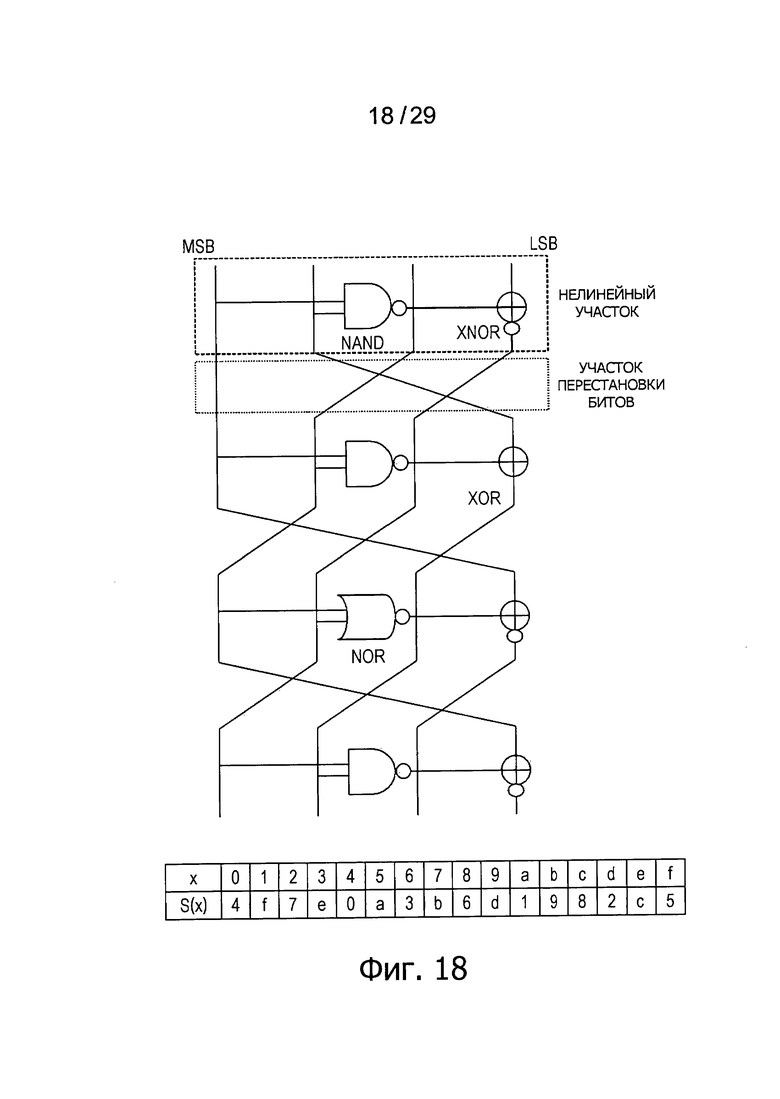

На фиг.18 показана схема, описывающая пример конфигурации 4-битных S-блоков из повторяющейся структуры логических вычислений и перестановки битов.

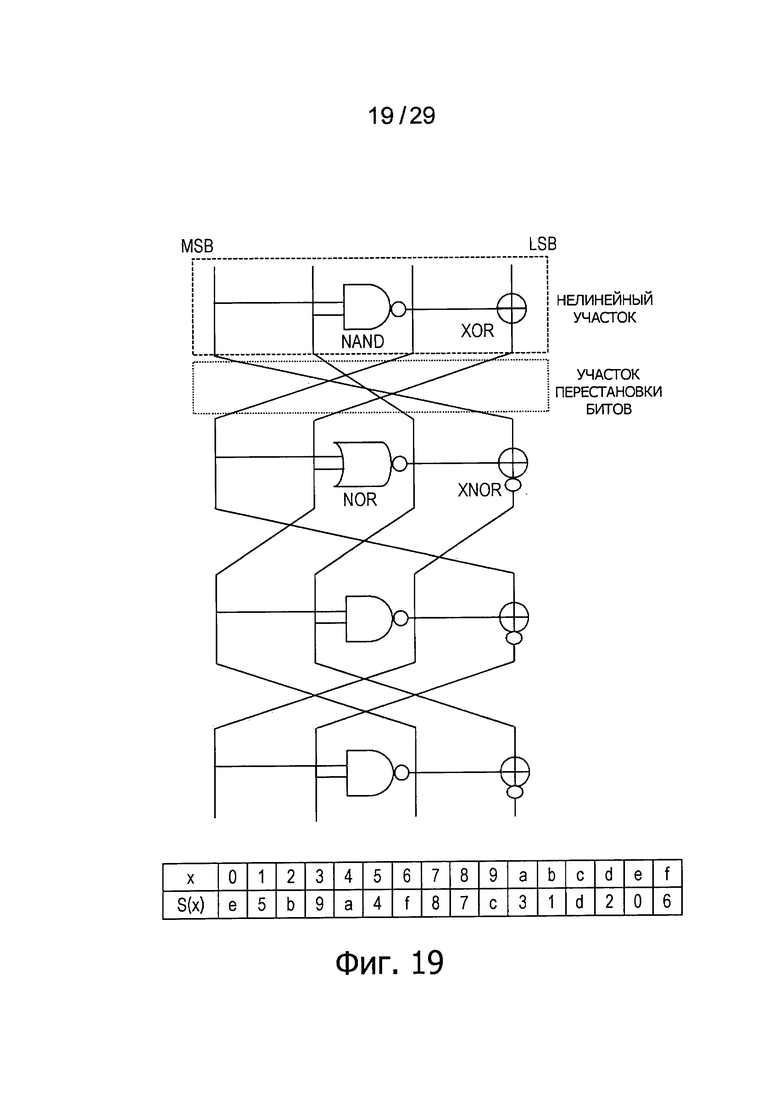

На фиг.19 показана схема, описывающая пример конфигурации 4-битных S-блоков из повторяющейся структуры логических вычислений и перестановки битов.

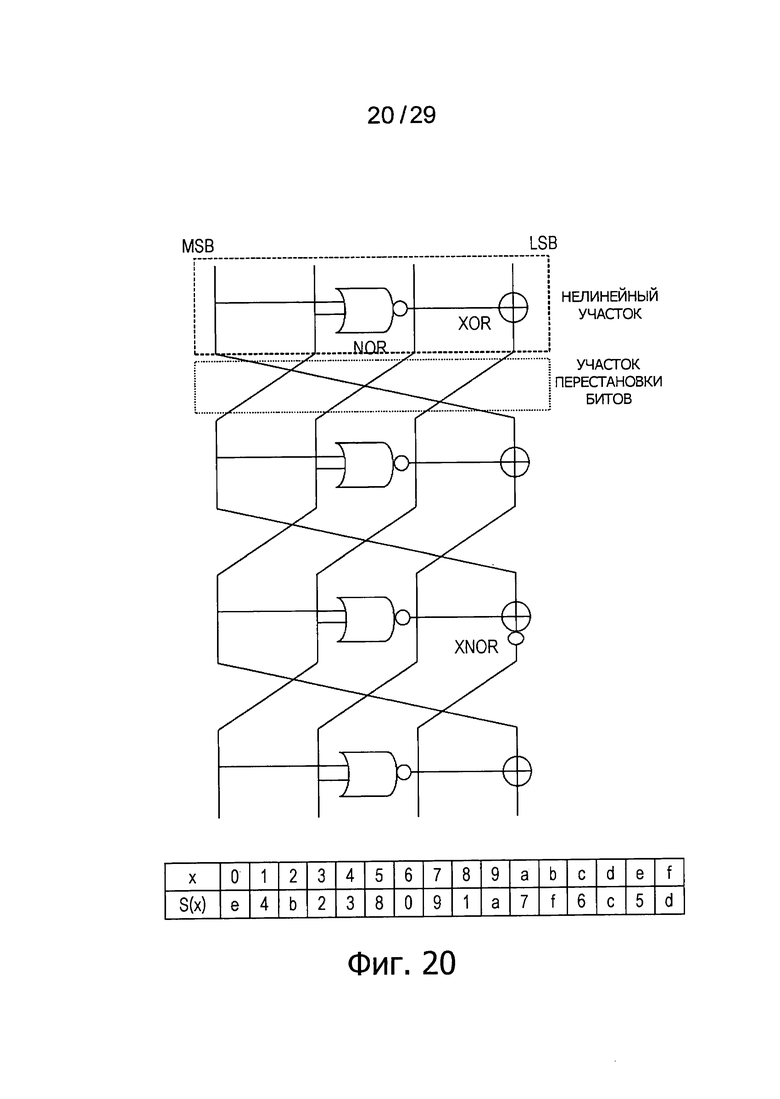

На фиг.20 показана схема, описывающая пример конфигурации 4-битных S-блоков из структуры повторения логических вычислений и перестановки битов.

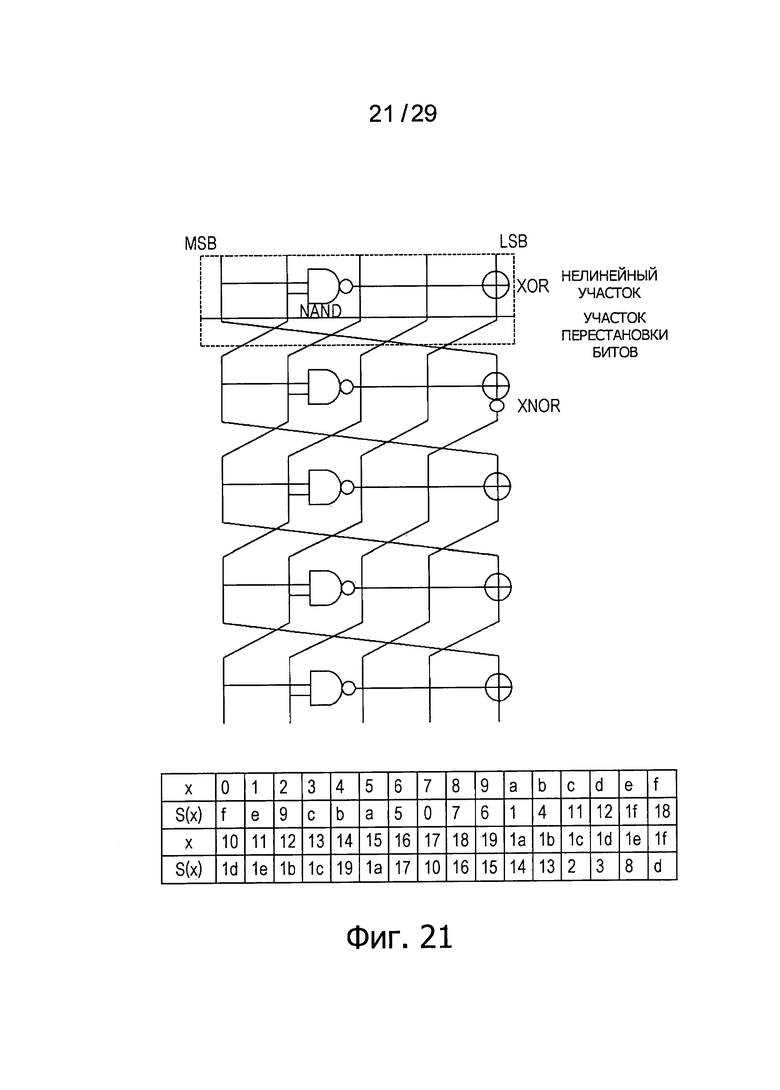

На фиг.21 показана схема, описывающая пример конфигурации 5-битных S-блоков из структуры повторения логических вычислений и перестановки битов.

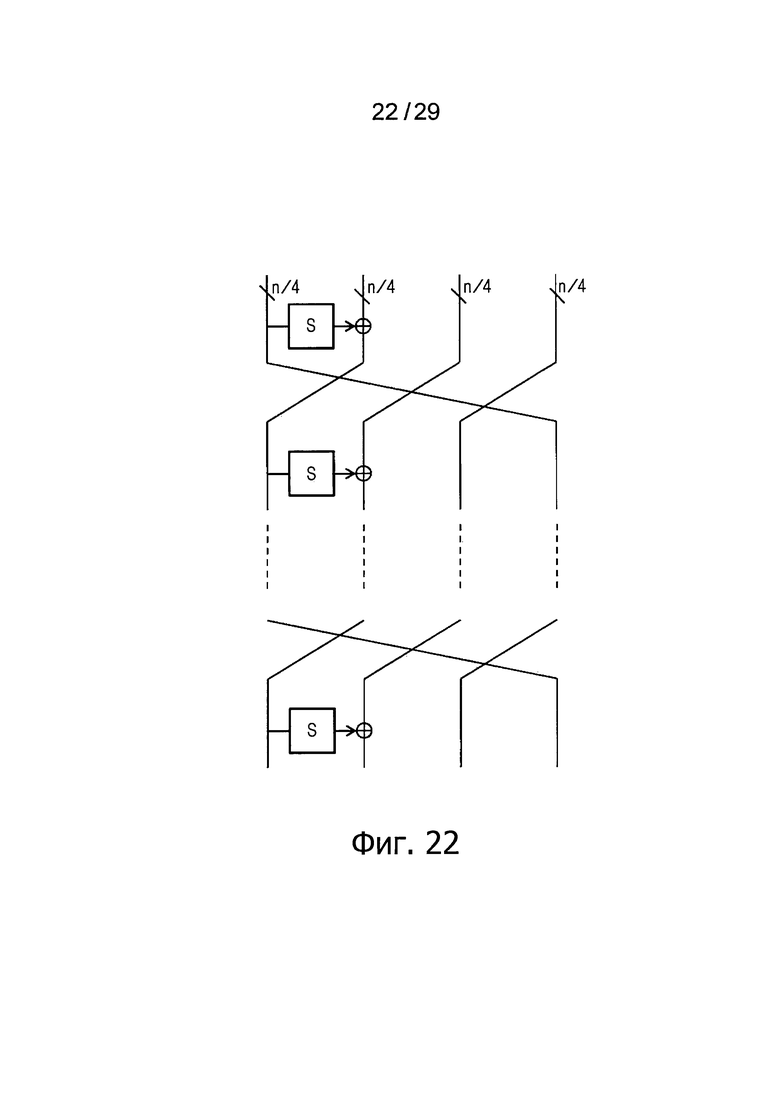

На фиг.22 показана схема, описывающая пример конфигурации больших S-блоков из повторяющейся обработки, используя малые S-блоки на основе GFN I типа (обобщенная сеть Фей стеля).

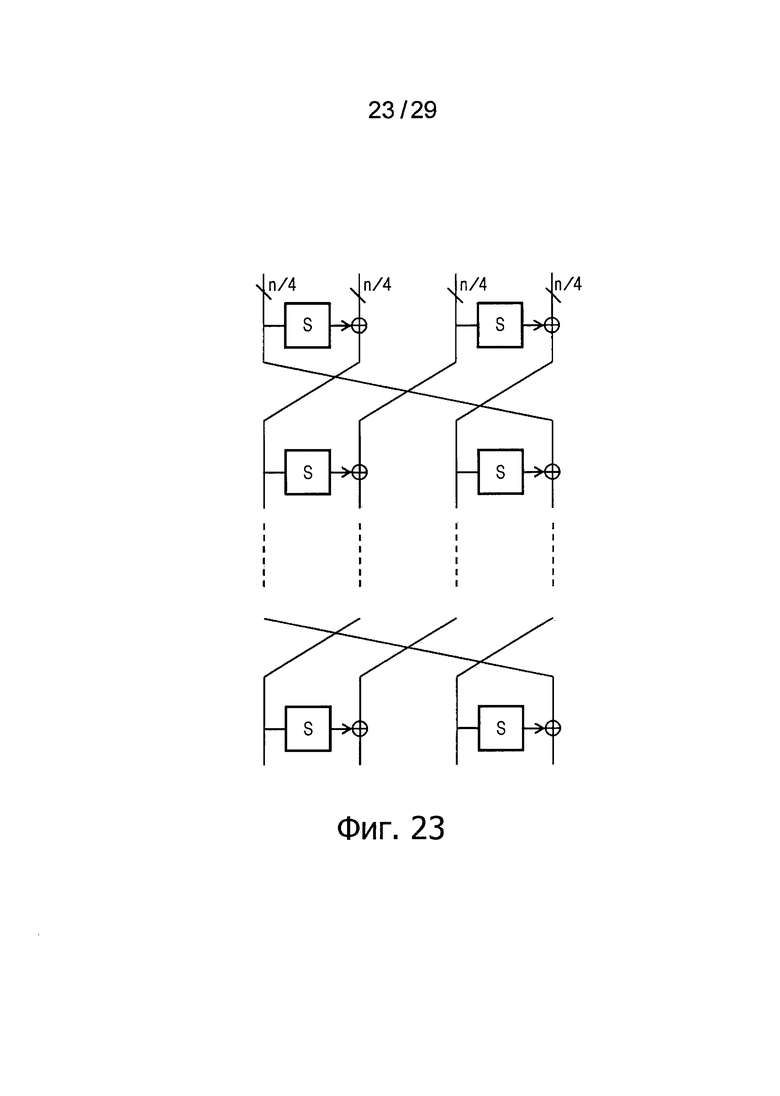

На фиг.23 показана схема, описывающая пример конфигурации больших S-блоков из повторяющейся обработки, используя малые S-блоки на основе GFN II типа.

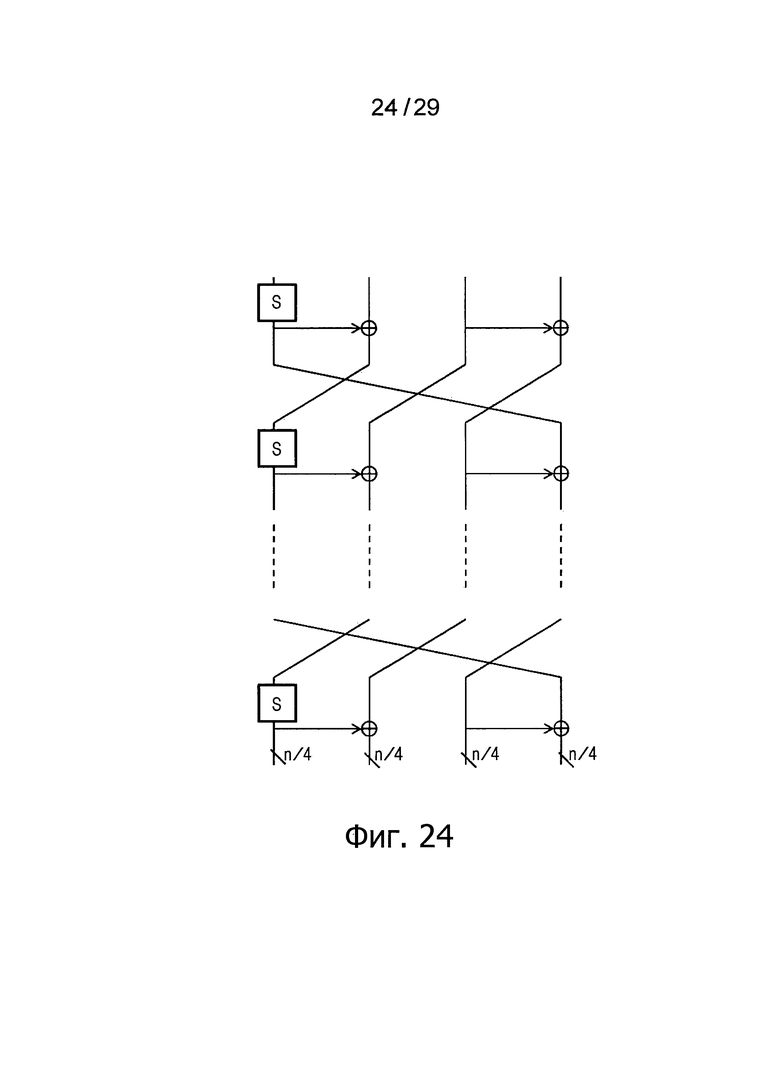

На фиг.24 показана схема, описывающая пример применения конфигурации больших S-блоков из повторяющейся обработки, используя малые S-блоки.

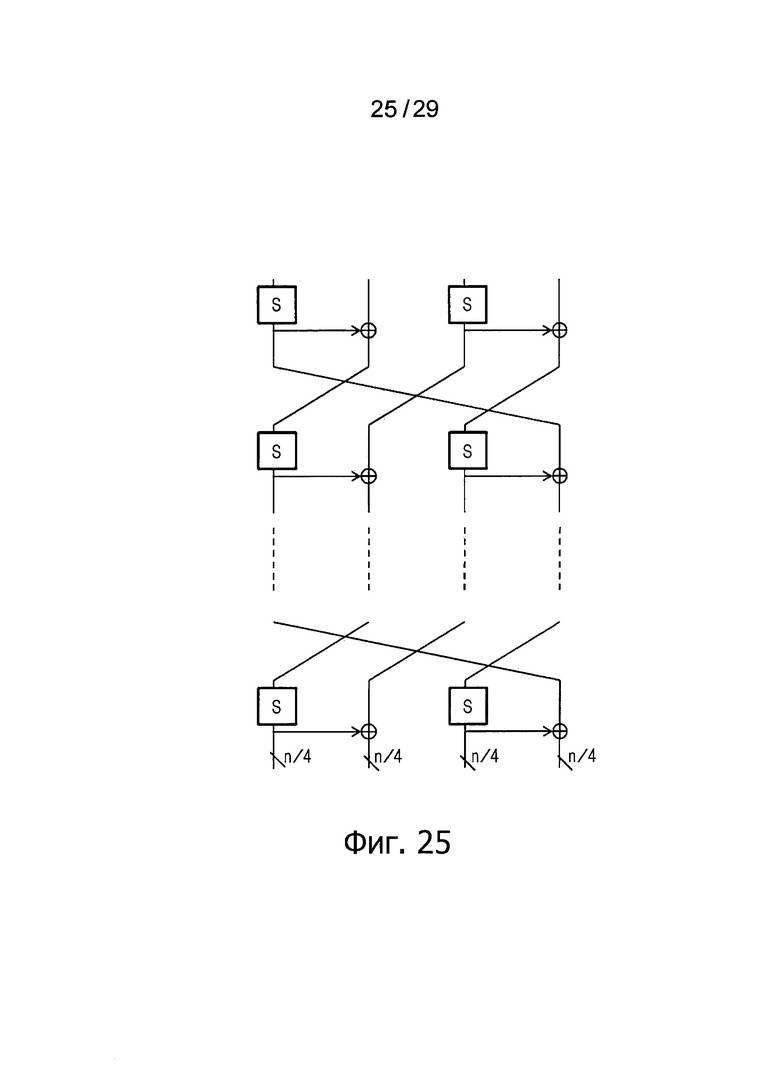

На фиг.25 показана схема, описывающая пример применения конфигурации больших S-блоков из повторяющейся обработки, используя малые S-блоки.

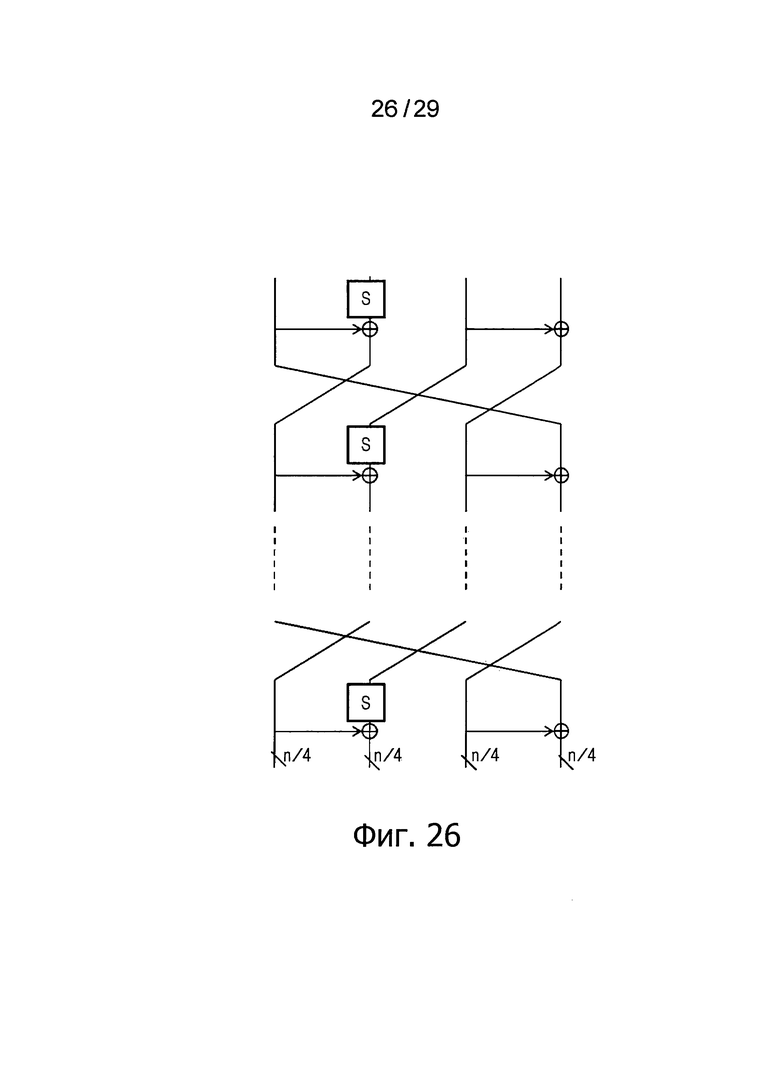

На фиг.26 показана схема, описывающая пример применения конфигурации больших S-блоков из повторяющейся обработки, используя малые S-блоки.

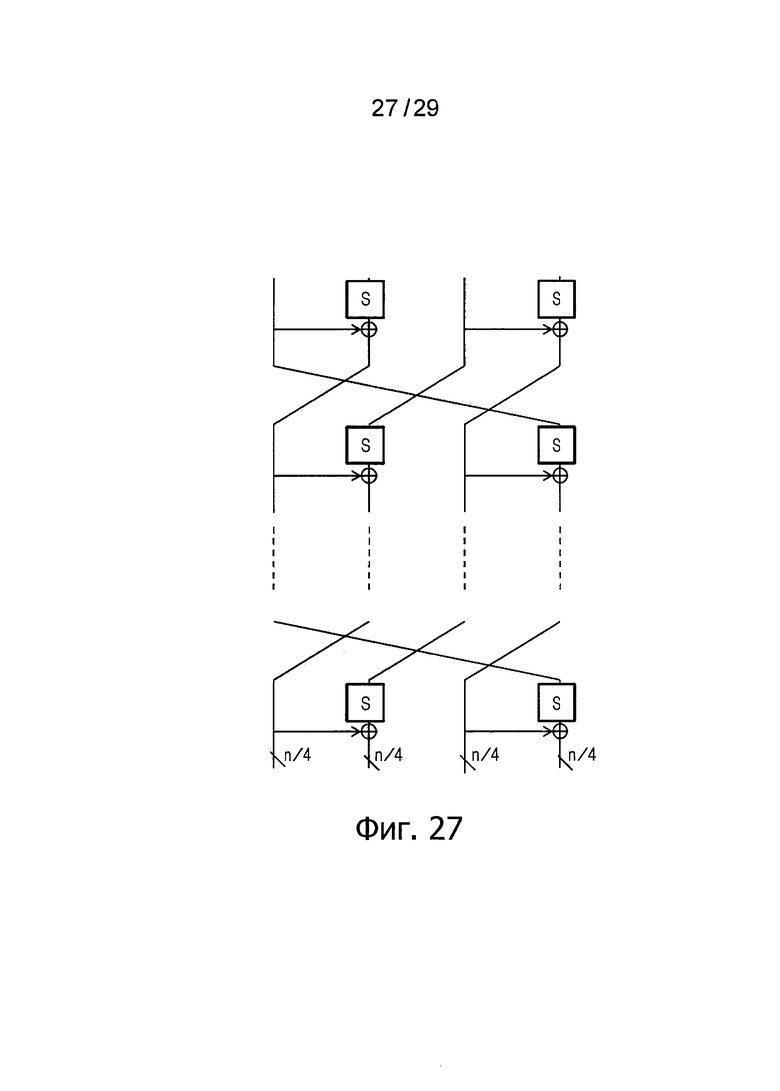

На фиг.27 показана схема, описывающая пример применения конфигурации больших S-блоков из повторяющейся обработки, используя малые S-блоки.

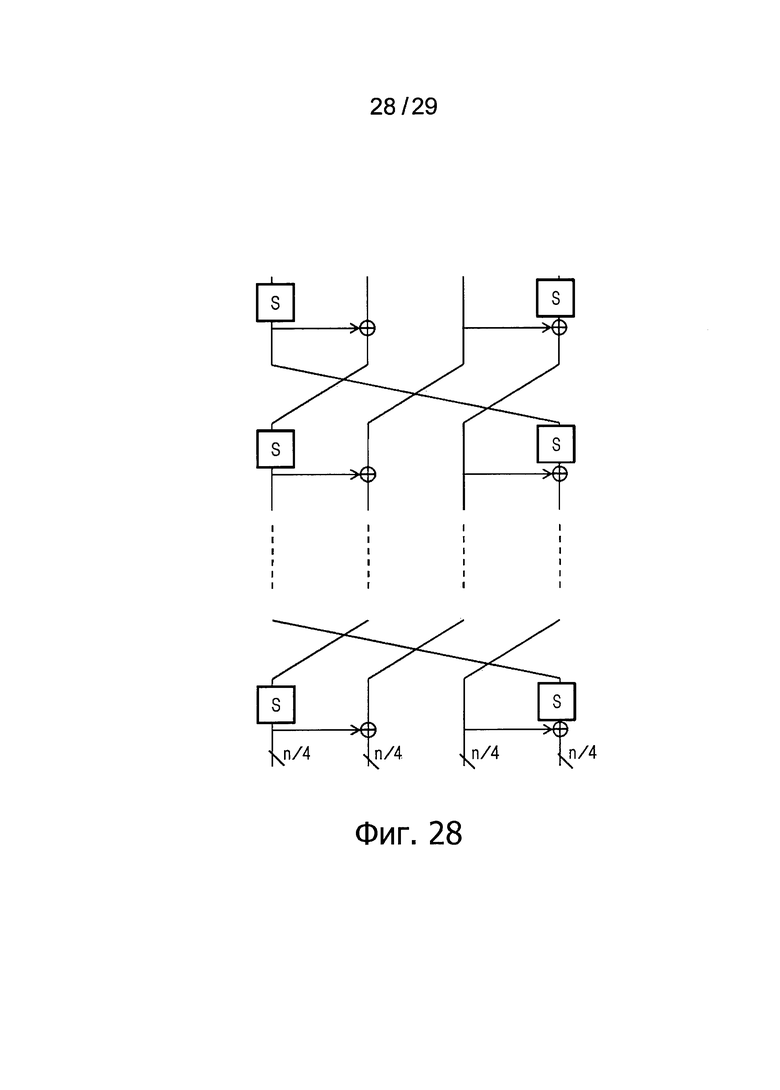

На фиг.28 показана схема, описывающая пример применения конфигурации больших S-блоков из повторяющейся обработки, используя малые S-блоки.

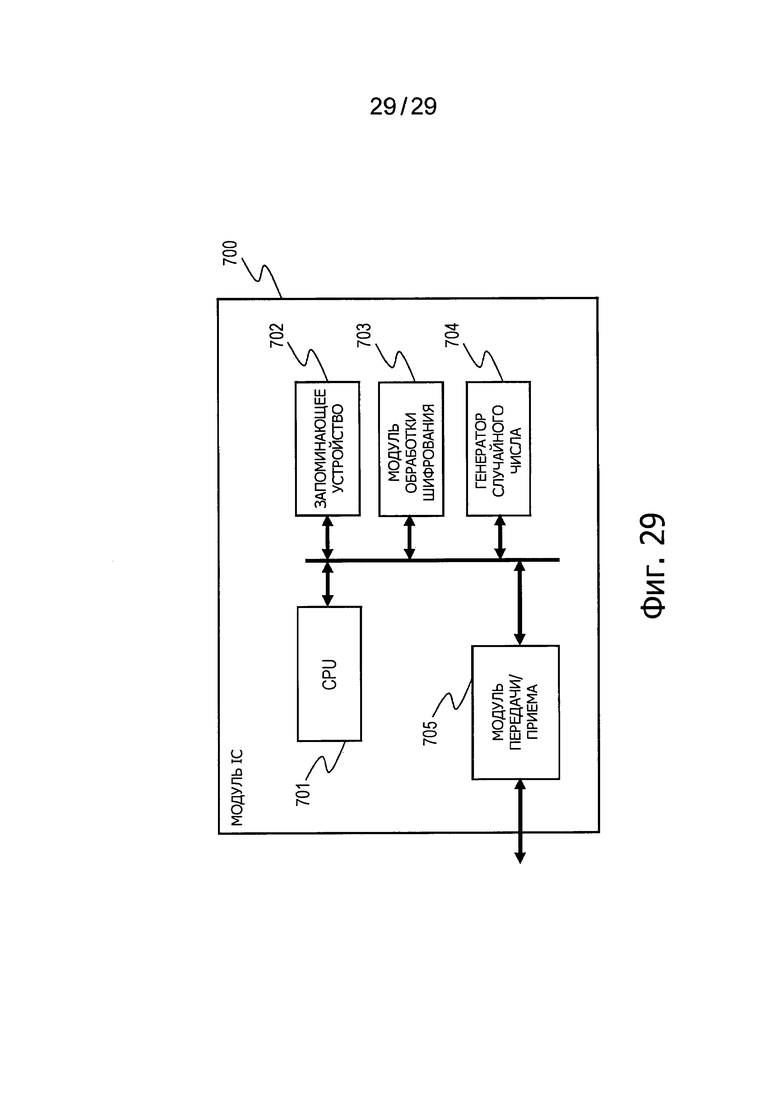

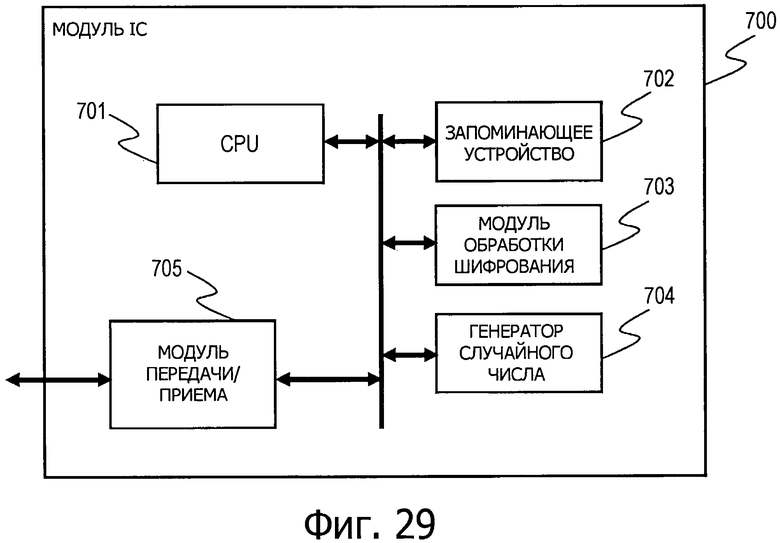

На фиг.29 показана схема, иллюстрирующая пример конфигурации модуля 700 IC, в качестве устройства обработки шифрования.

Осуществление изобретения

Далее устройство обработки данных, способ обработки данных и программа, относящиеся к настоящему раскрытию, будут подробно описаны со ссылкой на чертежи. Описание будет представлено в соответствии со следующими пунктами.

1. Общий обзор блочного шифрования с общим ключом

2. S-блоки

3. Общий обзор S-блока, относящегося к настоящему раскрытию

4. Примеры конфигурации устройств обработки шифрования

5. Заключение в отношении конфигурации настоящего раскрытия

1. Общий обзор блочного шифрования с общим ключом

Вначале будет описан общий обзор блока шифрования с общим ключом.

1-1. Шифрование блока общего ключа

В представленном ниже определении установлено обозначение блока шифрования с общим ключом (ниже называется блоком шифрования).

Блок шифрования получает открытый текст P и ключ K в качестве входных данных и выводит зашифрованный текст C. Длина в битах открытого текста и зашифрованного текста называется размером блока, который обозначен, как n. n представляет собой произвольное целое значение, которое обычно представляет собой одно значение, определенное заранее для каждого алгоритма блочного шифрования. Случай, в котором размер блока представляет блочное шифрование n, иногда называется блочным шифрованием размером n битов.

Длина ключа в битах выражена, как k. Ключ имеет произвольное целое значение. Алгоритм блочного шифрования с общим ключом может поддерживать один или множество размеров ключа. Например, для некоторого алгоритма A блочного шифрования, размер блока составляет n=128, и, таким образом, возможна конфигурация, которая поддерживает размер ключа k=128, k=192 или k=256.

Открытый текст P: n битов

Зашифрованный текст C: n битов

Ключ K: k битов

На фиг.1 иллюстрируется схема алгоритма E блочного шифрования с общим ключом размером n битов, соответствующего длине ключа k битов.

Алгоритм D дешифрования, соответствующий алгоритму E шифрования, может быть определен, как обратная функция E-1 алгоритма E шифрования, который принимает зашифрованный текст C и ключ K, в качестве входных данных, и выводит открытый текст P. На фиг.2 иллюстрируется схема алгоритма D дешифрования, соответствующая алгоритму E шифрования, показанному на фиг.1.

1-2. Внутренняя конфигурация

Блочное шифрование рассматривается, как разделенное на два узла. Один представляет собой "узел планирования ключа", в который вводят ключ K и из которого выводят расширенный ключ K′ (длина в битах k′), путем расширения длины в битах, в соответствии с некоторыми, ранее определенными этапами, и другой представляет собой "модуль шифрования данных", который принимает открытый текст P, и ключ K′, расширенный узлом планирования ключа, выполняет преобразование данных, и выводит зашифрованный текст C.

Взаимосвязь между этими двумя узлами представлена на фиг.3.

1-3. Модуль шифрования данных

Модуль шифрования данных, используемый в следующих вариантах осуществления, может быть разделен на модули обработки, называемые раундовыми функциями. Раундовая функция принимает два модуля данных, в качестве входных данных, выполняет внутреннюю обработку и выводит один модуль данных. Одна часть входных данных представляет собой n-битные данные, шифруемые в настоящее время, в результате чего получают конфигурацию, в которой выход из раундовой функции для определенного раунда подают, как вход для следующего раунда. Другая часть входных данных используется в качестве данных для узла расширенного ключа, выводимого из планировщика ключа, и эти данные ключа называются раундовым ключом. Кроме того, общее количество раундовых функций называется общим раундовым числом, и представляет собой значение, определяемое заранее для каждого алгоритма шифрования. Здесь общее раундовое число выражено, как R.

Общий обзор модуля шифрования данных показан на фиг.4, если смотреть со стороны ввода в модуль шифрования данных, в котором входные данные для первого раунда обозначены, как X1, данные, вводимые в раундовой функции номер I для всех раундов обозначены как Xi, и раундовый ключ обозначен, как RKi.

1-4. Раундовая функция

Раундовая функция может иметь различные формы, в зависимости от алгоритма блочного шифрования. Раундовая функция может быть классифицирована по структуре, принятой в этом алгоритме шифрования (структуре). Типичные структуры, используемые здесь в качестве примеров, представляют собой структуры SPN, структуры Фейстеля и расширенными структуры Фейстеля.

(A) Раундовая функция структуры SPN

В такой структуре применяют обработку линейного преобразования, обработку нелинейного преобразования и вычисления XOR для раундового ключа и всех n-битных входных данных. Порядок каждого вычисления не определен чем-либо конкретным. На фиг.5 иллюстрируется пример раундовой функции структуры SPN.

(B) Структура Фейстеля

n-битные входные данные разделяют на два модуля по n/2-битов данных. Функция (F функция) применяется к одной части этих данных и раундовый ключ, как входные данные, и выходные данные, и другую часть данных вычисляют, используя функцию XOR. Результат перестановки обеих сторон этих данных становится выходными данными. Хотя существуют различные типы внутренней конфигурации F функции, но они, в основном, достигаются аналогично структуре SPN с комбинированием вычислений XOR с данными раундового ключа, нелинейными вычислениями и линейными преобразованиями. На фиг.6 иллюстрируется пример раундовой функции структуры Фейстеля.

(C) Расширенная структура Фейстеля

Количество разделений данных, равное двум, в отношении структуры Фейстеля расширяют на формат из трех или больше разделений с расширенной структурой Фейстеля. Если количество разделений обозначено, как d, тогда различные расширенные структуры Фейстеля могут быть определены в зависимости от d. В связи с тем, что размер входной и выходной F функции является относительно малым, она пригодна для малых воплощений. На фиг.7 иллюстрируется пример расширенной структуры Фейстеля, в которой d=4, и две F функции применяют параллельно в пределах одного раунда. Кроме того, на фиг.8 иллюстрируется пример расширенной структуры Фейстеля, в которой d=8, и одна F функция применяется в пределах одного раунда.

1-5. Модуль обработки нелинейного преобразования

Стоимость воплощения проявляет тенденцию увеличения по мере увеличения размера входных данных для модулей обработки нелинейного преобразования. Для обхода этого используется множество конфигураций, в которых соответствующие данные разделяют на множество модулей, и выполняют нелинейное преобразование для этих данных. Например, когда входной размер обозначен, как ms битов, эти конфигурации разделяют на число m модулей данных через каждые s битов, и выполняют нелинейные преобразования этих данных, в которых входные и выходные данные составляют s битов. Нелинейные преобразования в этих модулях s-битов называются S-блоками. На фиг.9 иллюстрируется пример.

1-6. Модуль обработки линейного преобразования

Модули обработки линейного преобразования могут быть определены, как матрицы, в соответствии с их свойством. Элементы матрицы могут, в общем, быть выражены различными путями, например, как элемент основной части GF (28) и элемент GF (2). На фиг.10 иллюстрируется пример модуля обработки линейного преобразования, определенный, как матрица m×m, которая определяет входные данные размером ms битов и выходные данные, как GF (2S).

2. S-блоки

Вначале будет представлен общий обзор S-блоков, как модулей нелинейного преобразования, перед описанием конфигурации в соответствии с настоящим изобретением.

Обработку нелинейного преобразования, выполняемую F функцией, выполняют, например, применяя функцию нелинейного преобразования, называемую S-блоками. Такой S-блок представляет собой элемент конфигурации блочных шифров и функций хеширования и представляет собой чрезвычайно важную функцию для определения уровня безопасности и характеристик воплощения.

В общем, такой S-блок представляет собой функцию нелинейного преобразования, имеет входные данные в размере n битов и выходные данные в размере m битов, но описание продолжается ниже с обсуждением биективного S-блока с входом и выходом n битов. Здесь, биективный означает, что все выходные отображения представляют собой отображения одного входного значения.

Перспектива безопасности

Свойство S-блока оказывает существенное влияние на уровень безопасности всего шифрования. Общая оценка уровня безопасности в отношении общего шифрования и самой раундовой функции обычно затруднена, поскольку размер входных и выходных данных является существенным, но точная оценка возможна, поскольку размер входных и выходных данных S-блоков обычно меньше (вход и выход приблизительно восемь битов). Для повышения уровня безопасности общего шифрования, по меньшей мере, следующие свойства (1)-(4) желательно обеспечить в S-блоках.

(Свойство 1) Максимальная вероятность разности должна быть достаточно малой

Когда входную переменную x однородно выбирают в отношении произвольной входной разности Δx и выходной разности Δy, вероятность разности S-блока представляет собой вероятность, которая удовлетворяет S(x)+S(x+Δx)=Δy.

Однако, S(x) представляет выходные данные, соответствующие входным данным x для определенного S-блока S.

Максимальная вероятность разности определена, как наибольшая вероятность из комбинаций всех входных и выходных разностей. Каждая из них будет определена ниже соответствующим выражениями.

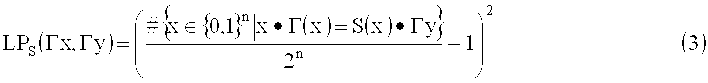

Если вероятность разности функции S, в которой предоставляют входную разность Δx и при выходной разности Δy определена, как DP (Δx, Δy), тогда DP ((Δx, Δy) определяется следующим образом.

Уравнение 1

где ⊕ представляет функцию XOR с последующим приращением в битах.

В это время максимальная вероятность разности MDP для этой функции определена следующим образом.

Уравнение 2

Такая вероятность разности может обладать устойчивость к атакам разности, путем разработки достаточно малого S-блока.

(Свойство 2) Максимальная линейная вероятность должна быть достаточно малой

Когда входную переменную x выбирают равномерно в отношении произвольной входной маски Гх и выходной маски Гу, линейная вероятность s блока представляет собой значение, получаемое из вероятности, которая удовлетворяет

Здесь · означает внутреннее умножение между n-битными векторами.

Максимальная линейная вероятность определена, как наибольшая вероятность из комбинации всех входных и выходных масок.

Далее определена каждая из них, в соответствии с выражением.

Если линейная вероятность функции S при предоставлении в нее входной маски Гх и выходной маски Гу определена, как LPs (Гх, Гу), тогда LPs (Гх, Гу), может быть выражено следующим образом.

Уравнение 3

Здесь максимальная вероятность разности MLP для функции S определена следующим образом.

Уравнение 4

Такая максимальная линейная вероятность может иметь устойчивость к линейным атакам, благодаря разработке достаточно малого S-блока.

(Свойство 3), Степень Булевой алгебры должна быть достаточно большой, при выполнении выражений с Булевым многочленом.

Степень Булевой алгебры означает степень при выражении выходных битов S-блока в виде входных Булевых битов. При разработке S-блока с достаточно большой степенью Булевой алгебры в отношении всех битов, становится возможным обеспечить устойчивость против атак, используя алгебраическое свойство более высоких дифференциальных атак или аналогичных.

(Свойство 4), количество членов должно быть достаточно большим при выполнении выражения многочлена для входных и выходных данных.

Благодаря существенному увеличению количества членов, при выполнении выражения многочленов выходных битов S-блока с входными битами, становится возможным обеспечить устойчивость к атакам интерполяции.

Перспектива воплощения

Помимо требований обеспечения уровня безопасности, S-блоки должны иметь высокие характеристики воплощения. Воплощение в виде программных средств обычно осуществляют, используя технологию, называемую справочной таблицей (воплощение на основе таблицы), и, таким образом, характеристики такого воплощения особенно не зависят от внутренней структуры S-блока. Однако на характеристику воплощения существенно влияет внутренняя структура S-блока при воплощении в виде аппаратных средств. Таким образом, внутренняя структура S-блока может быть особенно важной для возможностей воплощения в виде аппаратных средств.

Проблемы с технологией, в соответствии с предшествующим уровнем техники

В качестве технологии эффективного генерирования S-блока, удовлетворяющего этим требованиям, хорошо известен способ, в котором используется экспоненциальная функция в отношении поля расширения. Если множитель для экспоненты и степень для поля расширения будут выбраны соответствующим образом, в соответствии с такой технологией, S-блок с исключительно предпочтительными свойствами может быть сгенерирован.

Когда фактические входные и выходные данные размером n битов S-блока основаны на GF (2n) при x, в качестве входных данных и y, в качестве выходных данных, это может быть выражено следующим образом.

Уравнение 5

y=f(x) представляет собой либо y=x2t+1 или y=x-1

Когда обеспечивается такой подход, хорошо известно, что S-блок может быть сконфигурирован с оптимальной максимальной вероятностью разности и максимальной линейной вероятностью (однако, необходимо добавить соответствующее аффинное преобразование, поскольку количество членов становится малым при использовании этой технологии, для выполнения выражения многочленов для входных и выходных данных).

S-блоки в отношении AES (NPL 3: US National Institute of Standards and Technology Advanced Encryption Standard, Federal Information Processing Standards Publications No. 197, 2001.) and Camellia (NPL 4: Aoki, Ichikawa, Kanda, Matsui, Moriai, Nakajima, Tokita, "128-bit Block Encryption Camellia Algorithm Specification", Version 2.0, 2001.) используются, как примеры S-блока, выполненного в соответствии с таким видом технологии.

Поскольку S-блок может быть сконфигурирован, как обратная функция GF ((24)2), свойства с точки зрения безопасности являются чрезвычайно привлекательными, что обеспечивает то, что S-блоки AES и Camellia имеют даже большие и так чрезвычайно высокие характеристики при воплощении в виде аппаратных средств.

Однако в последнее время были идентифицированы проблемы, такие как атаки с использованием такого свойства алгебраической характеристики в отношении этого вида S-блока, и проблемы, относящиеся к такой чрезмерно однородной диффузивности.

Способ конфигурирования S-блоков, которые не имеют характеристическое алгебраическое свойство, были рассмотрены из этих проблем, и был предусмотрен способ случайного генерирования S-блоков, так, чтобы они не имели сильную алгебраическую структуру, или использовали технологию для выбора элемента, в соответствии с технологией, эквивалентной, как таковой. Если S-блоки генерируются с применением такого вида технологии, в большинстве случаев они не будут иметь характерную алгебраическую структуру, и они также не будут иметь однородную диффузию, такую как экспоненциальная функция в отношении полей расширения, и таким образом, можно сказать, что они будут представлять собой меру противодействия проблемам, описанным выше.

Однако поскольку количество входных и выходных данных S-блока, составляющего n битов, зависит от факториала 2n, трудно фактически генерировать S-блок с входными и выходными данными размером n битов случайным образом, для эффективного генерирования S-блока с предпочтительными характеристиками при некотором увеличении n, используя технологию, такую как проверка этих свойств одно за другим.

Кроме того, когда элементы являются абсолютно случайными, эффективность воплощения существенно снижается, поскольку технологии, называемые табличным воплощением, могут, в основном, использоваться для воплощения аппаратных средств.

С учетом этих проблем, были предприняты попытки генерировать случайно сгенерированные S-блоки с входными и выходными данными, имеющими малый размер, и комбинировать их множество, для генерирования большего S-блока.

Например, S-блоки, упомянутые в CRYPTON Ver. 0.5 (NPL 5: Chae Hoon Lim, "CRYPTON: A New 128-bit Block Cipher-Specification and Analysis (Version 0.5)"), CRYPTON Ver. 1.0 (NPL 6: Chae Hoon Lim, "CRYPTON: A New 128-bit Block Cipher-Specification and Analysis (Version 1.0)"), Whirlpool (NPL 7: Paulo S.L. M Barreto, Vincent Rijmen "The WHIRLPOOL Hashing Function", 2003), FOX (NPL 8: Pascal Junod and Serge Vaudenay, "FOX: a New Family of Block Ciphers", 2004), and CLEFIA (NPL 9: Sony Corporation, "The 128-bit Blockcipher CLEFIA Algorithm Specification", Revision 1.0, 2007), можно рассматривать, как примеры S-блоков, генерируемых на основе этого вида технологии.

Эти структуры представлены на фиг.11-фиг.15. Такие структуры имеют таблицы с меньшими размерами, и, поэтому, для них требуются меньшие затраты при воплощении в виде аппаратных средств, по сравнению со случаем, в котором случайно генерируют крупные S-блоки, как описано выше.

На фиг.11 показана конфигурация для выполнения обработки нелинейного преобразования для 8-битных входных данных.

Каждый из трех S-блоков для выполнения обработки нелинейного преобразования, используя 4-битные данные: S40, S41 и S42,

включает в себя три модуля позиционного логического вычисления для выполнения вычисления XOR по четырем битам, выводимым из каждых S-блоков и другим четырем битам.

8-битные входные данные подают в левую входную линию и прямую входную линию по четыре бита.

8-битные данные, как результат нелинейного преобразования трех S-блоков: S40, S41 и S42, выводят через левую выходную линию и прямую выходную линию по четыре бита.

Обработку выполняют в соответствии со следующей последовательностью обработки.

(1) Четыре бита из восьми входных битов (правая входная линия) подают на первый раундовый S-блок: S40 и выполняют нелинейное преобразование.

Вычисление XOR выполняют по этому результату нелинейного преобразования и другим четырем битам из входных восьми битов (левая входная линия).

(2) Такой результат вычисления XOR вводят во второй раундовый S-блок: S41, и выполняют нелинейное преобразование.

Вычисление XOR выполняют для такого результата нелинейного преобразования и четырех битов из восьми входных битов (правая входная линия).

Результат вычисления XOR выводят, как четыре бита из выходных восьми битов (правая выходная линия).

(3) Далее, такой результат вычисления XOR подают на третий раундовый S-блок: S42 и выполняют нелинейное преобразование.

Вычисление XOR выполняют для такого результата нелинейного преобразования и результат вычисления XOR в отношении обработки (1), описанный выше, и этот результат выводят, как четыре бита выходных восьми битов (Out-a).

На фиг.11 показана конфигурация для выполнения обработки нелинейного преобразования 8-битных входных данных с использованием описанной выше обработки.

Конфигурация, показанная на фиг.12, выполнена из

S-блоков: S40 и S41 для выполнения нелинейного преобразования 4-битных данных,

модуля выполнения вычислений для выполнения вычисления XOR в модулях из двух-трех битов в отношении 4-битов, выводимых из каждого S-блока,

и модулей нелинейного преобразования: S41 -1 и S40 -1 для выполнения обратного вычисления для предыдущих S-блоков: S40 и S41 в качестве выходных данных модуля выполнения вычисления.

Конфигурация, показанная на фиг.13, представляет собой конфигурацию обработки нелинейного преобразования, выполненной, как комбинация

S-блоков: S40 и S42 для выполнения нелинейного преобразования 4-битных данных,

модуля нелинейного преобразования: S41 -1 для выполнения обратного вычисления для S-блока: S41

и множества модулей вычисления XOR.

На фиг.14 показана конфигурация обработки нелинейного преобразования, выполненной, как комбинация

S-блоков: S40, S41 и S42 для выполнения нелинейного преобразования 4-битных данных,

множества модулей вычисления XOR

и множества модулей вычисления OR.

На фиг.15 показана конфигурация обработки нелинейного преобразования, выполненной, как комбинация

S-блоков: SS0, SS1, SS2 и SS3 для выполнения нелинейного преобразования 4-битных данных,

и модуля выполнения матричного преобразования для выполнения преобразования данных путем применения матрицы 2×2 (матрицы MDS).

Таким образом, несколько способов для конфигурирования крупных S-блоков на основе малых S-блоков, как показано на фиг.11-фиг.15, было предложено в соответствии с предшествующим уровнем техники. Эти виды конфигураций имеют таблицы с малыми размерами, и стоимость их воплощения в виде аппаратных средств меньше по сравнению со случаем случайного генерирования больших S-блоков.

Однако в соответствии со способами конфигурирования на основе малых S-блоков, в соответствии с предшествующим уровнем техники, таким образом, возникают проблемы в отношении способа разработки малых S-блоков и способа комбинирования малых S-блоков, которые представлены ниже.

(Проблема 1) Относительно конструкции малых S-блоков

В соответствии со способами предшествующего уровня техники, малые S-блоки формируют случайным образом. Таким образом, эти малые S-блоки требуют табличного воплощения, и размеры схем, необходимых для воплощения аппаратных средств, все еще велики.

(Проблема 2) В отношении способа комбинирования малых S-блоков

Способы, в соответствии с предшествующим уровнем техники, не имеют простых повторяющихся структур, и, таким образом, совместное использование схем является трудноосуществимым, даже когда выполняют S-блок во множестве циклов. Когда имеют простую повторяющуюся структуру, становится возможным совместное использование схем, и существует потенциал минимизации необходимого размера схемы, несмотря на необходимость выполнения множества циклов на практике. Однако, преимущества выполнения способа воплощения, таким образом, в соответствии с предшествующим уровнем техники, незначительны, и при этом трудно уменьшить размер схемы, даже когда можно использовать множество циклов.

3. Общий обзор S-блока, относящегося к настоящему раскрытию

Что касается проблем, описанных выше, далее представлен способ конфигурирования S-блока для достижения высокого уровня безопасности и обеспечения уменьшения размера схемы при воплощении в виде аппаратных средств, по сравнению с предшествующим уровнем техники.

Конфигурации, которые будут описаны ниже, обеспечивают существенное преимущество, в частности, в случаях, когда уменьшение необходимого размера схемы для воплощения требуется для вариантов воплощения с учетом фактической пропускной способности аппаратных средств. Кроме того, для упрощения, в следующем описании будут описаны только биективные S-блоки с входными и выходными данными размером n битов.

Далее будут описаны следующие два примера конфигурации S-блоков в следующем порядке.

(1) Способ для конфигурирования S-блока, в котором возможно воплощение, которое является одновременно безопасным и обеспечивает малый размер схемы, в результате повторения структуры логических вычислений и перестановки битов.

(2) Способ конфигурирования S-блока большого размера, имеющего повторяющуюся структуру, в котором возможно воплощение, которое является одновременно безопасным и обеспечивает малый размер схемы, на основе S-блоков малого размера.

Далее в пункте (1), описанном выше, используется конфигурация, которая позволяет решить (проблему 1), описанную выше, и в пункте (2) описана конфигурация, которая позволяет решить (проблему 2).

Также возможна комбинация (1) и (2), и, таким образом, можно одновременно решить (проблемы 1 и 2), используя такую комбинированную конфигурацию.

3-1. Способ конфигурирования S-блоков с повторяющейся структурой логических вычислений и перестановки битов

Вначале будет описан способ (1) для конфигурирования S-блока, в котором возможно воплощение, которое является одновременно безопасным и обеспечивает малый размер схемы, благодаря повторению структуры логических вычислений и перестановки битов.

3-1-1. Обзор конфигурации S-блока

S-блок может быть получен в результате комбинирования различных логических схем.

Здесь предложенный S-блок включает в себя два узла, "модуль нелинейного вычисления", основанный на основных логических вычислениях, таких как "И" (AND), "ИЛИ" (OR) и "НЕТ" (NOT), и "модуль перестановки битов", для выполнения перестановки положений битов, в качестве основных элементов конфигурации S-блока, путем повторения этих элементов.

Модуль нелинейного вычисления использует одно вычисление "НЕ-И" (NAND) или "НЕ-ИЛИ" (NOR), используя 2-битовый вход и 1-битовый выход, и одно вычисление, "исключающее ИЛИ" (XOR), или "исключающее НЕ-ИЛИ" (XNOR) с 2-битным входом и 1-битным выходом для обеспечения биекции и нелинейного преобразования, и включает в себя структуру для вычисления либо XOR, или XNOR по результатам выполнения вычислений либо NAND, либо NOR для произвольных двух битов в виде одного бита, отличающегося от этих двух битов.

Модуль перестановки битов выполняет простую перестановку положений битов.

S-блок генерируют путем многократного повторения такого модуля нелинейного вычисления и модуля перестановки битов.

Модуль нелинейного вычисления и модуль перестановки битов могут быть изменены при каждом повторении, или для них может использоваться один и тот же тип модуля.

В общем, для конфигурирования надежного S-блока из n битов, структура повторения n раз должна иметь минимальную конфигурацию, при которой не происходит существенная потеря безопасности при использовании такого способа конфигурации с повторением участка нелинейного вычисления, по меньшей мере, n раз, если необходимо. Кроме того, возможно не выполнять и исключить конечное повторение модуля перестановки битов, поскольку это не оказывает какого-либо влияния на уровень безопасности и размер схемы.

Кроме того, модуль нелинейного вычисления выполнен либо из модуля вычисления NAND, или модуля вычисления NOR и одного из модулей вычисления XOR или XNOR, как описано выше, и, таким образом, путем смешения модуля вычисления XOR и модуля вычисления XNOR в повторяющейся структуре для n раз, становится возможным исключить фиксированные точки при обработке нелинейного преобразования. Поэтому, желательно воплотить конфигурацию, в которой модули вычисления XOR и модули вычисления XNOR смешаны в структуре повторения для n раз модуля нелинейного вычисления для достижения обработки нелинейного преобразования, при которой не возникают фиксированные точки.

3-1-2. Преимущества настоящей технологии

Преимущества настоящей технологии, включают в себя следующие три преимущества (Преимущества 1-3). Первое решают (проблему 1) существующей технологии, и остальные два являются дополнительными преимуществами настоящего изобретения.

(Преимущество 1) Возможно воплощение с меньшим размером схемы, чем в способах, в соответствии с предшествующим уровнем техники.

Один модуль нелинейного вычисления выполнен с использованием только одного из вычисления NAND или NOR или одного из вычисления XOR или XNOR.

Даже среди основных логических вычислений, в которых выполняют нелинейную обработку на входе, известны вычисления NAND/NOR, которые обеспечивают возможность воплощения с использованием малого размера схем.

Помимо вычислений NAND/NOR, только вычисления XOR/XNOR используются для обеспечения биективных свойств. Таким образом, такой участок нелинейного вычисления, можно сказать, представляет собой минимальный класс среди биективных нелинейных функций при определенной стоимости воплощения в виде аппаратных средств (необходимый размер схемы).

Кроме того, модуль перестановки битов может быть воплощен только путем разводки межсоединений при воплощении в виде аппаратных средств, и не имеет какого-либо влияния на необходимый размер схемы. То есть, стоимость воплощения в виде аппаратных средств (необходимый размер схемы) равна нулю.

Что касается настоящей конфигурации, схемы, необходимые для воплощения, могут быть существенно уменьшены по сравнению со способами, в соответствии с предшествующим уровнем техники, конфигурация которого была выполнена с повторениями этого модуля нелинейного вычисления и модуля перестановки битов.

(Преимущество 2) Стоимость воплощения аппаратных средств может быть точно оценена.

В соответствии со способами предшествующего уровня техники, S-блок генерируют случайно, и, поэтому, оценку всегда необходимо выполнять, используя логические инструменты комбинирования, также и при оценке необходимого размера схемы.

Что касается способа, в соответствии с настоящей конфигурацией, при оценке количества логических операторов, то есть, количества повторений, стоимость воплощения в виде аппаратных средств (необходимый размер схемы) может быть легко оценена, без использования инструментов логического комбинирования, как таковых. В соответствии с предшествующим уровнем техники, трудно определить оптимальный S-блок из множества блоков для оценки необходимого размера схемы, для выполнения которой требуется много времени, но в соответствии с настоящей конфигурации, можно просто выбрать оптимальный S-блок, поскольку размер схемы может быть легко оценен.

(Преимущество 3) Возможно конфигурировать множество типов S-блоков при одной и той же стоимости воплощения аппаратных средств (необходимый размер схемы).

Обеспечивается свобода при выборе логической операции, используемой в модуле нелинейного вычисления, и типа перестановки битов, используемой в модуле перестановки бита, и этот тип может быть отличным для каждого повторения, и, таким образом, множество S-блоков могут быть сконфигурированы с одинаковым необходимым размером схемы.

Это позволяет выбирать оптимальные комбинации функций высокого порядка и других функций среди S-блоков с одинаковой стоимостью аппаратного воплощения (необходимый размер схемы).

(3-1-3. Конкретные примеры конфигурации)

Далее будут описаны конкретные примеры конфигурации S-блока с использованием повторяющейся структуры логических вычислений и перестановки битов.

На фиг.16 иллюстрируется конкретный пример конфигурации S-блока из четырех битов.

4-битные S-блоки, представленные на фиг.16, включают в себя повторяющуюся структуру из 4 раундов в виде комбинации модуля нелинейного вычисления и модуля перестановки битов, и модуль нелинейного вычисления выполнен из четырех NAND, трех XOR и одного XNOR. Кроме того, перестановка битов в последнем раунде не показана на чертеже, и при этом возможно получить конфигурацию, которая устанавливает перестановку битов в последнем раунде, или получить конфигурацию, в которой она исключена.

Модуль нелинейного вычисления для первого раунда выполнен с использованием NAND и XNOR.

Два бита из четырех входных битов подают на вход NAND в первом раунде, его выходные биты подают в XNOR в первом раунде, и вычисление XNOR выполняют с одним битом из четырех входных битов.

Результат выполнения вычисления XNOR в первом раунде устанавливают, как выходные биты, и затем подают в NAND для нелинейных участков третьего и четвертого раундов.

Модуль нелинейного вычисления во втором раунде выполнен с NAND и XOR.

Два бита из четырех входных битов подают в NAND во втором раунде, его выходные биты подают в XOR во втором раунде, и вычисление XOR выполняют с одним битом из четырех входных битов.

Результат выполнения вычисления XOR во втором раунде устанавливают, как выходные биты и затем подают на NAND для нелинейных участков четвертого раунда.

Модуль нелинейного вычисления для третьего раунда выполнен с использованием NAND и XOR.

Один бит из четырех входных битов и результат исполнения вычисления XNOR в первом раунде вводят в NAND в третьем раунде, его выходные биты подают на XOR в третьем раунде, и вычисление XOR выполняется с одним битом из четырех входных битов.

Результат выполнения для вычисления XOR, в третьем раунде устанавливают, как выходные биты.

Модуль нелинейного вычисления в четвертом раунде сконфигурирован с использованием NAND и XOR.

Результат исполнения для вычисления XNOR в первом раунде и результат исполнения для вычисления XOR во втором раунде подают в NAND в четвертом раунде, его выходные биты подают в XOR в четвертом раунде, и вычисление XOR выполняют с одним битом из четырех входных битов.

Результат выполнения вычисления XOR для четвертого раунда устанавливают, как выходные биты.

Максимальная вероятность разности и максимальная линейная вероятность, которые представляют собой состояния для S-блоков с высоким уровнем безопасности, как описано в предыдущем разделе [2. S-блоки], для этого 4-битного S-блока обе составляют 2-2. То есть, оптимальное значение для этого 4-битного S-блока и стоимость воплощения аппаратных средств меньше, чем по сравнению со случайно генерируемым 4-битным S-блоком.

Таким образом, можно сказать, что такой 4-битный S-блок имеет исключительные характеристики и безопасность при воплощении в виде аппаратных средств.

Другие конкретные примеры S-блоков, выполненных с определенным размером схемы (такое же количество повторений), имеющих одинаковую оптимальную вероятность разности и линейную вероятность, иллюстрируются на фиг.17-фиг.20. Кроме того, перестановка битов в последнем раунде не показана на фиг.16-фиг.20, поскольку возможно иметь конфигурацию, которая устанавливает перестановку битов в последнем раунде, или можно иметь конфигурацию, в которой она исключена.

4-битный S-блок, представленный на фиг.17, выполнен из четырех NOR, трех XNOR и одного XOR.

4-битный S-блок, представленный на фиг.18, выполнен из трех NAND, одного NOR, трех XNOR и одного XOR.

4-битный S-блок, представленный на фиг.19, выполнен из трех NAND, одного NOR, трех XNOR и одного XOR.

4-битный S-блок, представленный на фиг.20, выполнен из четырех NOR, одного XNOR и трех XOR.

Конфигурация и обработка 4-битного S-блока, представленного на каждом чертеже, будут описаны ниже.

4-битный S-блок, показанный на фиг.17, включает в себя структуру повторения в 4 раундах, как комбинацию модуля нелинейного вычисления и модуля перестановки битов, и модуль нелинейного вычисления выполнен из четырех NOR, трех XNOR и одного XOR. Кроме того, перестановка битов в последнем раунде не показана на чертеже, и при этом возможно иметь конфигурацию, которая устанавливает перестановку битов в последнем раунде, или иметь конфигурацию, в которой она исключена.

Модуль нелинейного вычисления для первого раунда выполнен из NOR и XNOR.

Два бита из четырех входных битов подают в XNOR для первого раунда, эти выходные биты подают в XNOR для первого раунда, и вычисление XNOR выполняют, используя один бит из четырех входных битов.

Результат исполнения для вычисления XNOR в первом раунде устанавливают, как выходные биты, и затем подают в NOR для нелинейных участков третьего и четвертого раундов.

Модуль нелинейного вычисления во втором раунде выполнен с использованием NOR и XNOR.

Два бита из четырех входных битов вводят в NOR во втором раунде, его выходные биты подают в XNOR во втором раунде, и вычисление XNOR выполняют с одним битом из четырех входных битов.

Результат исполнения для вычисления XNOR во втором раунде устанавливают, как выходные биты, и затем подают в NOR для нелинейных участков четвертого раунда.

Модуль нелинейного вычисления в третьем раунде выполнен с использованием NOR и XNOR.

Один бит из четырех входных битов и результат исполнения для вычисления XNOR в первом раунде вводят в NOR в третьем раунде, его выходные биты подают в XNOR в третьем раунде, и вычисление XNOR выполняют с использованием одного бита из четырех входных битов.

Результат исполнения вычисления XNOR в третьем раунде устанавливают, как выходные биты.

Модуль нелинейного вычисления в четвертом раунде выполнен с использованием NOR и XOR.

Результат исполнения вычисления XNOR в первом раунде и результат исполнения из вычисления XNOR во втором раунде, подают в NOR в четвертом раунде, его выходные биты подают в XOR в четвертом раунде, и вычисление XOR выполняют с одним битом из четырех входных битов.

Результат исполнения для вычисления XOR, в четвертом раунде, устанавливают, как выходные биты.

4-битный S-блок, показанный на фиг.18, включает в себя структуру повторения из 4 раундов как комбинацию модуля нелинейного вычисления и модуля перестановки битов, и модуль нелинейного вычисления выполнен из трех NAND, одного NOR, трех XNOR и одного XOR. Кроме того, перестановка битов в последнем раунде не показана на чертеже, поскольку возможно получить конфигурацию, которая устанавливает перестановку битов в последнем раунде, или иметь конфигурацию, в которой она исключена.

Модуль нелинейного вычисления в первом раунде выполнен с использованием NAND и XNOR.

Два бита из четырех входных битов подают в NAND в первом раунде, его выходные биты подают в XNOR в первом раунде, и вычисление XNOR выполняют с одним битом из четырех входных битов.

Результат исполнения вычисления XNOR в первом раунде устанавливают, как выходные биты и затем подают в NOR и в NAND для нелинейных участков третьего и четвертого раундов.

Модуль нелинейного вычисления во втором раунде выполнен с NAND и XOR.

Два бита из четырех входных битов подают в NAND во втором раунде, его выходные биты выводят в XOR во втором раунде, и вычисление XOR выполняют с одним битом из четырех входных битов.

Результат исполнения для вычислений XOR во втором раунде устанавливают, как выходные биты, и затем вводят в NAND для нелинейных участков четвертого раунда.

Модуль нелинейного вычисления для третьего раунда выполнен с использованием NOR и XNOR.

Один бит из четырех входных битов и результат исполнения для вычислений XNOR, в первом раунде, подают в NOR в третьем раунде, его выходные биты вводят в XNOR в третьем раунде, и вычисление XNOR выполняют с одним битом из четырех входных битов.

Результат исполнения для вычисления XNOR в третьем раунде, устанавливают, как выходные биты.

Модуль нелинейного вычисления в четвертом раунде выполнен с использованием NAND и XNOR.

Результат исполнения для вычисления XNOR в первом раунде и результат исполнения для вычисления XOR во втором раунде вводят в NAND в четвертом раунде, его выходные биты вводят в XNOR в четвертом раунде, и вычисление XNOR выполняют с одним битом из четырех входных битов.

Результат исполнения для вычисления XNOR в четвертом раунде устанавливают, как выходные биты.

4-битный S-блок, показанный на фиг.19, включает в себя структуру повторения в 4 раундах, как комбинацию модуля нелинейного вычисления и модуля перестановки битов, и модуль нелинейного вычисления выполнен из трех NAND, одной NOR, трех XNOR и одной XOR. Далее, перестановка битов в последнем раунде не показана на чертеже, поскольку возможно иметь конфигурацию, которая устанавливает перестановку битов в последнем раунде, или иметь конфигурацию, в которой она исключена.

Модуль нелинейного вычисления в первом раунде выполнен с использованием NAND и XOR.

Два бита из четырех битов подают в NAND в первом раунде, его выходные биты вводят в XOR в первом раунде, и вычисление XOR выполняют с одним битом из четырех входных битов.

Результат исполнения для вычисления XOR в первом раунде устанавливают, как выходные биты и затем подают в NOR и NAND для нелинейных участков второго и третьего раундов.

Модуль нелинейного вычисления во втором раунде выполнен с использованием NOR и XNOR.

Один бит из четырех входных битов и результат исполнения XOR в первом раунде подают в NOR во втором раунде, его выходные биты подают в XNOR во втором раунде, и вычисление XNOR выполняют с использованием одного бита из четырех входных битов.

Результат исполнения для вычисления XNOR, во втором раунде устанавливают, как выходные биты, и затем подают в NAND для нелинейного участка четвертого раунда.

Модуль нелинейного вычисления в третьем раунде выполнен с NAND и XNOR.

Один бит из четырех входных битов и результат исполнения для вычисления XNOR, в первом раунде подают в NAND в третьем раунде, его выходные биты подают в XNOR в третьем раунде, и вычисление XNOR выполняют с одним битом из четырех входных битов.

Результат исполнения для вычисления XNOR в третьем раунде, устанавливают, как выходные биты.

Модуль нелинейного вычисления в четвертом раунде выполнен с использованием NAND и XNOR.

Результат исполнения для вычисления XNOR, во втором раунде, и результат исполнения для вычисления XNOR в третьем раунде подают в NAND в четвертом раунде его выходные биты вводят в XNOR в четвертом раунде, и вычисление XNOR выполняют с одним битом из четырех входных битов.

Результат исполнения вычисления XNOR в четвертом раунде устанавливают, как выходные биты.

4-битный S-блок, представленный на фиг.20, включает в себя структуру повторения в 4 раундах, как комбинацию модуля нелинейного вычисления и модуля перестановки битов, и модуль нелинейного вычисления выполнен из четырех NOR, одной XNOR и трех XOR. Кроме того, перестановка битов в последнем раунде исключена на чертеже, и при этом возможно иметь конфигурацию, которая устанавливает перестановку битов в последнем раунде, или иметь конфигурацию, в которой она исключена.

Модуль нелинейного вычисления в первом раунде выполнен с использованием NOR и XOR.

Два бита из четырех входных битов подают в NOR в первом раунде, его выходные биты вводят в XOR в первом раунде, и вычисление XOR выполняют с использованием одного бита из четырех входных битов.

Результат выполнения для вычисления XOR, в первом раунде, устанавливают, как выходные биты, и затем подают в NOR для нелинейных участков третьего и четвертого раундов.

Модуль нелинейного вычисления во втором раунде выполнен с использованием NOR и XOR.

Два бита из четырех входных битов подают в NOR во втором раунде, его выходные биты подают в XOR во втором раунде, и вычисление XOR выполняют с использованием одного бита из четырех входных битов.

Результат исполнения для вычисления XOR во втором раунде устанавливают, как выходные биты, и затем подают в NOR для нелинейных участков четвертого раунда.

Модуль нелинейного вычисления в третьем раунде выполнен с использованием NOR и XNOR.

Один бит из четырех входных битов и результат исполнения XOR, в первом раунде, подают в NOR в третьем раунде, его выходные биты подают в XNOR в третьем раунде, и вычисление XNOR выполняют с одним битом из четырех входных битов.

Результат исполнения для вычисления XNOR в третьем раунде, устанавливают, как выходные биты.

Модуль нелинейного вычисления в четвертом раунде выполнен с использованием NOR и XOR.

Результат исполнения вычисления XOR в первом раунде и результат исполнения вычисления XOR во втором раунде подают в NOR в четвертом раунде, его выходные биты подают в XOR в четвертом раунде, и вычисление XOR выполняют с использованием одного бита из четырех входных битов.

Результат исполнения вычисления XOR в четвертом раунде, устанавливают, как выходные биты.

Кроме того, что касается 4-битного S-блока, который может быть воплощен с такими же размерами схемы, как 4-битный S-блок, показанный в примерах, описанных выше, существуют четыре типа вычисления модуля нелинейного вычисления (=2×2), и 24 типа перестановки битов модуля перестановки битов (=4!), и поскольку тип может отличаться для каждого повторения, следует понимать, что существуют 96 в степени четыре возможностей.

То есть большое количество 4-битных S-блоков с одинаковым размером схемы может быть сконфигурировано, таким образом, что оптимальный S-блок с этой целью может быть выбран во время разработки.

На фиг.21 иллюстрируется пример конфигурации 5-битного S-блока, в качестве другого примера конфигурации S-блока.

5-битный S-блок, показанный на фиг.21, включает в себя структуру повторения в 5 раундах, как комбинацию модуля нелинейного вычисления и модуля перестановки битов, и модуль нелинейного вычисления выполнен из пяти NAND, четырех XORS и одной XNOR. Кроме того, перестановка битов в последнем раунде исключена на чертеже, поскольку возможно иметь конфигурацию, которая устанавливает перестановку битов в последнем раунде, или иметь конфигурацию, в которой она исключена.

Модуль нелинейного вычисления в первом раунде выполнен из NAND и XOR.

Два бита из пяти входных битов подают в NAND в первом раунде, его выходные биты подают в XOR в первом раунде, и вычисление XOR выполняют с одним битом из пяти входных битов.

Результат исполнения вычисления XOR в первом раунде установлен, как выходные биты, и затем его подают в NAND для нелинейных участков четвертого и пятого раундов.

Модуль нелинейного вычисления во втором раунде выполнен с использованием NAND и XNOR.

Два бита из пяти входных битов подают в NAND во втором раунде, его выходные биты подают в XNOR во втором раунде, и вычисление XNOR выполняют с использованием одного бита из пяти входных битов.

Результат исполнения для вычисления XNOR во втором раунде устанавливают, как выходные биты, и затем подают в NAND для нелинейного участка пятого раунда.

Модуль нелинейного вычисления в третьем раунде выполнен с использованием NAND и XOR.

Два бита из пяти входных битов подают в NAND в третьем раунде, его выходные биты подают в XOR в третьем раунде, и вычисление XOR выполняют с одним битом из пяти входных битов.

Результат исполнения для вычисления XOR в третьем раунде, устанавливают, как выходные биты.

Модуль нелинейного вычисления в четвертом раунде выполнен с использованием NAND и XOR.

Один бит из пяти входных битов и результат исполнения для вычисления XOR, в первом раунде, подают в NAND в четвертом раунде, его выходные биты подают в XOR в четвертом раунде, и вычисление XOR выполняют с использованием одного бита из пяти входных битов.

Результат исполнения для вычисления XOR, в четвертом раунде, устанавливают, как выходные биты.

Модуль нелинейного вычисления в пятом раунде выполнен с использованием NAND и XOR.

Результат исполнения вычисления XOR в первом раунде, и результат исполнения вычисления XNOR во втором раунде, подают в NAND в пятом раунде, эти выходные биты подают в XOR в пятом раунде, и вычисление XOR выполняют с использованием одного бита из пяти входных битов.

Результат исполнения вычисления XOR в пятом раунде устанавливают, как выходные биты.

Вероятность разности и линейная вероятность для такого 5-битного S-блока составляет 2-2. Поскольку оптимальное значение для каждого участка 5-битного S-блока составляет 2-4, это не обеспечивает наивысший уровень безопасности, но размер схемы получается чрезвычайно малым по сравнению с размером при случайном генерировании. По этой причине такой подход можно применять в случаях, когда характеристики воплощения имеют приоритет.

3-2. Способ конфигурирования больших S-блоков с повторяющейся структурой, используя малые S-блоки

Далее будет описан способ конфигурирования больших S-блоков с повторяющейся структурой, используя малые S-блоки.

Конфигурация для конфигурирования большого S-блока из малого S-блока выполнена, как повторяющаяся структура с определенной функцией. В частности, большой S-блок, который имеет сравнительно низкую стоимость воплощения в аппаратных средствах (необходимый размер схемы) вначале генерируют из малого S-блоков, и такой большой S-блок включает в себя повторяющуюся структуру. В результате, большой S-блок, имеющий повторяющуюся структуру, может быть выполнен из малого S-блока.

3-2-2. Преимущества настоящей технологии

Настоящая технология имеет существенные преимущества при воплощениях в виде аппаратных средств, в частности, при таком воплощении, как последовательное выполнение с целью уменьшения необходимого размера схемы.

Что касается вычисления имеющейся повторяющейся структуры, нет необходимости воплощать все элементы при выполнении S-блока для последовательного выполнения, может быть воплощен модуль повторений, и его можно многократно выполнять произвольное число раз.

Таким образом, можно сказать, что такая структура может быть воплощена с меньшим размером схемы, чем S-блок в соответствии с предшествующим уровнем техники, который не имеет повторяющейся структуры.

3-2-3. Конкретные примеры конфигурации

Далее будут описаны конкретные примеры конфигурации большого S-блока, в котором используется повторяющаяся обработка с применением малого S-блока.

Ниже будут описаны детали в отношении конкретного способа конфигурации.

Кроме того, со ссылкой на фиг.22-фиг.28, будет описана прямоугольная область, обозначенная, как S на каждом из этих чертежей, например, малый S-блок, описанный со ссылкой на фиг.16-фиг.21, то есть, S-блок для выполнения обработки нелинейного преобразования, например, в модулях из четырех битов.

На каждой из фиг.22-фиг.28 показана конфигурация, в которой входные n битов разделяют на четыре части из n/4 битов, которые подают в четыре линии, обработку вычисления выполняют, используя модуль выполнения вычислений, составленный из малого S-блока и схемы XOR для данных в каждой линии, и множество раундов, состоящих из поворотов выполняемых модулем выполнения поворотов, многократно выполняют в модулях данных в каждой линии.

Конфигурация, показанная на фиг.22, имеет конфигурацию, в которой применяется один S-блок и одна схема XOR для каждого раунда, и имеет конфигурацию, в которой результат применения n/4-битного S-блока и схемы XOR генерируют в предыдущем раунде обработки, выполняют поворот данных в модулях линий n/4-битов для результата вычисления n/4-бита и других необработанных данных, и результат поворота выводят в следующий раунд обработки.

Конфигурация на фиг.23 имеет конфигурацию, в которой применяют два S-блока и две схемы XOR для каждого раунда, и имеет конфигурацию, в которой результат применения n/4-бита S-блока и схемы XOR для предыдущего раунда обработки генерируют, как данные в 2 линиях (2x(n/4) бита), выполняют поворот данных в модулях n/4-бита в линии для результата вычисления в 2 линиях и двух других линий необработанных данных, и результат поворота выводят в следующий раунд обработки.

Конфигурация, показанная на фиг.24, имеет конфигурацию, в которой применяется один S-блок и две схемы XOR для каждого раунда, и имеет конфигурацию, в которой, что касается обработки в предшествующем раунде,

результат применения S-блока n/4 битов,

результат применения S-блока n/4-битов и схемы XOR,

и результат применения схемы XOR n/4 битов

генерируют, выполняют поворот данных в модулях n/4 битов линий для трех результатов вычислений n/4 бита и других необработанных данных, и результаты поворота выводят в следующий раунд обработки.

Конфигурация, показанная на фиг.25, имеет конфигурацию, в которой применяется два S-блока и две схемы XOR для каждого раунда, и имеет конфигурацию, в который что касается предыдущего раунда обработки,

результат применения двух S-блоков n/4 бита

и результат применения двух S-блоков n/4 бита и двух схем\XOR

генерируют, выполняют поворот данных в модулях n/4 бита линий для четырех результатов вычислений n/4-битов, и результаты поворота выводят в следующий раунд обработки.

Конфигурация, показанная на фиг.26, имеет конфигурацию, в которой применяется S-блок и две схемы XOR для каждого раунда, и имеет конфигурацию, в которой, что касается предыдущего раунда обработки,

результат применения S-блока n/4 бита и схемы XOR,

и результат применения схемы XOR n/4 бита,

генерируют, выполняют поворот данных в модулях n/4 бита в линии в том, что касается двух результатов вычислений n/4 бита и других необработанных данных, и результаты поворота выводят в следующий раунд обработки.

Конфигурация, показанная на фиг.27, имеет конфигурацию, в которой применяются два S-блока и две схемы XOR для каждого раунда, и имеет конфигурацию, в которой, в отношении предыдущего раунда обработки,

результат применения двух n/4-битов S-блока и двух схем XOR,

генерируют, выполняют поворот данных в модулях n/4 бита линий для двух результатов вычислений размером n/4 бита и других необработанных данных, и результаты поворота выводят в следующий раунд обработки.

Конфигурация, показанная на фиг.28, имеет конфигурацию, в которой применяются два S-блока и две схемы XOR для каждого раунда, и имеет конфигурацию, в которой, что касается предыдущего раунда обработки,

результат применения S-блока n/4 бита,

результат применения S-блока n/4 бита и схема XOR,

и результат применения схемы XOR n/4 бита

генерируют, выполняют поворот данных в модулях n/4 бита линий для трех результатов вычисления n/4 бита и других необработанных данных, и результаты поворота выводят в следующий раунд обработки.

На фиг.22 и фиг.23 показаны повторяющиеся структуры, называемые типом-I GFN (обобщенная сеть Фейстеля) и типом II GFN, соответственно.

Обычно их используют вместе с секретным ключом, который используется на малом нелинейном участке, но в соответствии с настоящим вариантом осуществления секретный ключ не воплощен, с учетом эффективности воплощения.

В результате воплощения конфигурации, в которой не используется секретный ключ, таким образом, становится возможным воплотить его полностью, как одну фиксированную таблицу.

Разница между конфигурациями на фиг.22 и фиг.23 представлена количеством малых S-блоков для каждого раунда.

Тип-I GFN на фиг.22 выполнен из n-битного S-блока, одного n-битного XOR, и поворота в модулях по n битов.

В соответствии с примером, показанным на фиг.22, входные данные составляют n битов, разделенные на четыре части, и подаваемые в каждую линию в модулях n/4 битов.

Далее, количество разделений входных данных выбирают произвольно. То есть, возможно расширение произвольного числа r разделений (r>2), и оно может быть соответствующим образом определено в зависимости от необходимых входного и выходного размера больших S-блоков.

Тип II GFN, показанный на фиг.23, выполнен из двух малых n-битных S-блоков, двух n-битных XOR, и с поворотом в модулях n битов, с последовательным приращением для каждого раунда.

Особенности этих двух способов конфигурации состоят в том, что вычисление в нормальном порядке является практически таким же, как и вычисление в обратном порядке, и разница состоит только в участке поворота.

В результате, может быть обеспечено совместное использование схем, когда необходимо воплотить как упорядоченную функцию, так и обратную функцию. Что касается способа конфигурации, показанного на фиг.23, при генерировании 16-битного S-блока, используя 4-битный S-блок, как на фиг.16,

максимальная вероятность разности для шести повторении составляет 2-8.3,

и максимальная линейная вероятность составляет 2-7.83,

максимальная вероятность разности для семи повторении составляет 2-9.1,

и максимальная линейная вероятность составляет 2-8.

Эти значения не являются оптимальными значениями при 16 битах, но эти вероятности достаточно малы, и при этом формируется схема с чрезвычайно малыми размерами по сравнению с тем, что формируются произвольно.

На фиг.24-фиг.28 показаны структуры, на которых малые S-блоки расположены на участках, отличных от структур на фиг.22 и фиг.23. Различия между каждыми из них представляет собой только местоположение компоновки и количество S-блоков в модулях повторений.

В соответствии с этими структурами, ввод данных в малые S-блоки является ненужным при последующих вычислениях, и, таким образом, не требуются чрезмерные области для хранения данных, что обеспечивает возможность дополнительного необходимого уменьшения размера аппаратных средств при разделении и воплощении функции повторения даже на более мелкие участки.

Что касается способа конфигурации, как на фиг.25, при конфигурировании 16-битного S-блока, используя 4-битный S-блок, как на фиг.17,

максимальная вероятность разности для шести повторений составляет 2-8.3,

и максимальная линейная вероятность составляет 2-8,

максимальная вероятность разности для семи повторений составляет 2-9.1,

и максимальная линейная вероятность составляет 2-8.5.

Эти значения не являются оптимальными значениями при 16 битах, но эти вероятности являются достаточно низкими, и размер схемы получается чрезвычайно малым по сравнению с тем, что формируется при случайном подходе.

4. Примеры конфигурации устройства обработки шифрования

В конечном итоге, фактические примеры устройств обработки шифрования, выполняющих обработку шифрования, в соответствии с описанными ранее вариантами осуществления, будут описаны.

Устройства обработки шифрования, предназначенные для выполнения обработки шифрования, в соответствии с ранее описанными вариантами осуществления, могут быть установлены в различных устройствах обработки информации, выполняющих обработку шифрования. В частности, их можно использовать в различных критических ситуациях, при которых выполняется обработка шифрования вместе с обработкой данных и обработкой передачи данных устройствами, такими как PC, TV, устройства записи, устройства воспроизведения, устройства передачи данных, RFID, смарт-карты, устройства сенсорной сети, модули/батареи аутентификации батарей, устройства для здоровья и медицины, устройства независимой сети и т.д.

На фиг.29 иллюстрируется пример конфигурации IC модуля 700, в качестве примера устройства, выполняющего обработку шифрования, в соответствии с настоящим раскрытием. Описанная выше обработка может быть выполнена в различных устройствах обработки информации, таких как PC, IC-карты, устройства считывания-записи и других, и IC модуль 700, показанный на фиг.29, может быть сконфигурирован из этих различных устройств.

CPU (центральное процессорное устройство) 701, показанное на фиг.29, представляет собой процессор, исполняющий различные программы, такие как начало и прекращение обработки шифрования, управление передачей и приемом данных, управление передачей данных между каждым элементом конфигурации, и другие. Запоминающее устройство 702 состоит из ROM (постоянное запоминающее устройство), в котором содержатся фиксированные данные, такие как программа, исполняемая CPU 701, параметр вычисления и так далее, и RAM (оперативное запоминающее устройство), используемое, как рабочая область и область хранения программы, исполняемой в ходе обработки CPU 701, и параметры, которые произвольно изменяются во время обработки программы. Кроме того, запоминающее устройство 702 можно использовать, как область хранения для данных и в таком виде можно применять для матрицы преобразования и таблиц преобразования (таблиц перестановки), применяемых во время обработки шифрования, и для данных ключей, необходимых во время обработки шифрования. Кроме того, область хранения данных, предпочтительно, выполнена, как запоминающее устройство, имеющее структуру, устойчивую к вмешательству.

Часть 703 обработки шифрования выполняет обработку шифрования и обработку дешифрования, в соответствии с алгоритмом блочного шифрования с общим ключом, при которой применяются ранее описанные конфигурации обработки шифрования, то есть, например, обобщенные структуры Фейстеля или структуры Фейстеля.

Кроме того, в примерах, представленных здесь, средство обработки шифрования использовалось, как индивидуальные модели, вместо предоставления этих видов независимых модулей обработки шифрования, может быть воплощена конфигурация, в которой программа обработки шифрования может быть сохранена, например, в ROM, и CPU 701 считывает и выполняет программу, сохраненную в ROM.

Генератор 704 случайных чисел выполняет обработку генерирования случайного числа, необходимую во время генерирования ключей, необходимых во время обработки шифрования.