Назначение и область применения

Группа изобретений относится к области разработки, производства, эксплуатации и модернизации средств криптографической защиты информации в системах обработки информации различного назначения, в том числе, для защиты HD и 4K видеоконтента.

Предшествующий уровень техники

Известны способы итерационного криптографического преобразования (шифрования) сообщений фиксированной длины, представленных в цифровом виде, а именно в виде двоичных данных, выполняемые с использованием секретного ключа, например способ, реализованный в виде алгоритма блочного шифрования AES (Advanced Encryption Standard) [1].

Как следует из публикации [1] криптографтческие преобразования на основе блочного шифрования AES включают два режима использования: зашифрование и расшифрование. При этом, при построении алгоритмов шифрования и их практической реализации используют раундовые функции, состоящие из последовательности определенных действия (преобразований данных). Основная цель данных преобразований - придать шифру устойчивость к различным видам атак, на основе которых можно узнать ключ шифрования, т.е. полностью скомпрометировать криптосистему. Таким образом, при любом режиме использования формируют раундовые ключи шифрования, вычисляемые при помощи секретного ключа, а сообщения фиксированной длины преобразуют путем последовательного выполнения над ними обратимых линейных и нелинейных операций и побитового суммирования сообщения с раундовыми ключами. В качестве линейных операций используют перестановку байтов сообщения и умножение сообщения на фиксированную матрицу. В качестве нелинейных операций используют операции побайтовой подстановки. На этапе зашифрования после каждого нелинейного преобразования применяют линейное преобразование. На этапе расшифрования используют обратные преобразования, которые применяются в обратном порядке: после каждого линейного преобразования следует нелинейное преобразование.

Как известно, одним из важных свойств шифров, в том числе и реализованных на основе AES, являются их устойчивость к линейному и дифференциальному криптоанализу. Одним из инструментов, лежащих в основе алгоритма шифрования AES, позволяющим противостоять данным видам анализа, является преобразование данных на блоках замен SBOX, которое обладает свойствами нелинейности. Способам генерации SBOX, а также их защищенности в настоящее время посвящено множество различных работ, в том числе получивших в дальнейшем охрану в качестве изобретений.

Известны работы [2], в которых рассматривается генерация SBOX в зависимости от некоторого ключа и рассматриваются криптографические свойства генерируемых SBOX. При этом в данных работах не ставится целью замедление программной реализации, а наоборот, выбирается способ генерации SBOX в зависимости от ключа, минимально влияющий на производительность. Это достигается за счет вычисления величины сдвига на основе ключа (XOR всех байт раундового ключа) и выполнения сдвигов SBOX оригинального алгоритма AES на полученную величину. Данный способ также предполагает, что свойства исходных SBOX, влияющие на криптостойкость шифра AES, сохраняются при сдвиге SBOX.

Вместе с тем, к способам шифрования и преобразованиям, на основе которых они строятся, предъявляются также требования по их эффективной реализации в аппаратных блоках устройств их осуществляющих.

Из публикации [3] известны схемы построения SBOX, которые эффективны с точки зрения реализации в аппаратном блоке и которые обладают устойчивостью к криптоанализу по сторонним каналам (side channel). Повышенная защищенность достигается за счет использования пороговый схемы реализации SBOX, и позволяет избежать утечки данных на SBOX по сторонним каналам.

В патентной публикации [4] заявки США на изобретение раскрыт способ и устройство, реализующие защиту внутренних состояний AES (данные между раундами) за счет комбинированного использования программного и аппаратного блоков обработки. Раскрытое в публикации решение способа шифрования, по меньшей мере, включает следующие этапы преобразований: содержащий преобразование исходных данных в структуру S состоящую из 16-байтных блоков с последующим ее преобразованием по множеству раундов обратимых преобразований выполняемых циклически и включающих последовательно выполняемые этапы формирования (KeySchedule) раундовых ключей шифрования нелинейным расширением секретного ключа шифра AES, преобразования структуры S заменой(подстановкой) каждого байта структуры с помощью сгенерированной таблицы подстановок SBOX (SubBytes), с последующими преобразованиями структуры S сдвигом строк и перемешиванием столбцов, а также преобразования добавлением раундного ключа на каждом раунде. При этом, устройство, реализующее раскрытый в публикации способ шифрования, по меньшей мере, включает схему преобразования по AES, реализованную программно-аппаратным образом на основе программируемого микропроцессора содержащую, по меньшей мере, блок расширения ключа шифрования AES, генерирующий раундовые ключи шифра AES на основе ключа AES, соединенный со входом блока, реализующего предварительный раунд AES, путем выполнения функции сложения с первым раундовым ключом массива исходных данных в виде структуры S состоящей из 16-байтных блоков, поступающих на первый вход блока, реализующего предварительный раунд AES, а его, выход соединен со входом блока, реализующего раундовые операции, состоящие из блоков нелинейного преобразования SBOX; сдвига рядов матрицы состояния, сформированной из 16 блока данных; перемешивания столбцов матрицы состояния; функции сложения с очередным раундовым ключом, последовательно соединенного с блоком финального раунда, сопряженные с блоком памяти данных и блоком памяти ключей. Программная обработка использует специальные дополнительные преобразования для защиты состояний (removal function and a protection function), аппаратная содержит меньше инструкций и не вносит доп. преобразования (т.е. фактически это криптоакселератор раунда обычного AES) и не искажает использованные преобразования в программном блоке. Преобразования основываются на особых свойствах SBOX (SubBytes operations) - классах сопряженности. Строятся дополнительные таблицы замен (lookup table) на основе этих свойств, которые используются для сокрытия входа/выхода оригинальной таблицы SBOX. Схема эффективна по производительности за счет комбинирования программного и аппаратного блоков. Данный патент относится к защите данных в криптографии "белого ящика" (white-box cryptography).

Однако, все рассмотренные вышеуказанные аналоги не позволяют обеспечить возможность реализации способа и устройства шифрования (криптографических преобразований), обладающих существенно более сложной программной реализацией алгоритма шифрования, требующего существенно больших затрат времени и средств на криптоанализ данных, при сохранении простой аппаратной реализации шифра и возможностью защиты от программной расшифровки данных, поступающих с большими битрейтами.

Более того, поскольку время и средства, затрачиваемые на криптоанализ, зависят от длины ключа и сложности алгоритма шифрования, все вышеуказанные аналоги для защиты от программной расшифровки данных, поступающих с большими битрейтами, требуют существенного усложнения не только программной реализации алгоритма шифрования, но и его аппаратной реализации, что ограничивает возможности применения данных решений, в том числе для защиты HD и 4K видеоконтента.

Таким образом, к числу недостатков вышеуказанных известных решений можно отнести невозможность реализации способа криптографических преобразований (шифрования) и устройства для его осуществления, обеспечивающих существенно более сложную программную реализацию алгоритма шифрования, с увеличением времени и средств затрачиваемых на криптоанализ информации, при сохранении простой аппаратной реализации шифра и возможностью защиты от программной расшифровки данных, поступающих с большими битрейтами.

Сущность заявленного изобретения.

Техническая задача (проблема), решаемая заявленной группой изобретений, заключается в устранении вышеуказанные недостатков известных из предшествующего уровня техники решений и предложении способа криптографического преобразования (в частности, шифрования) и устройства для его реализации, обеспечивающих увеличение времени и средств затрачиваемых на криптоанализ зашифрованных данных, при сохранении простой аппаратной реализации алгоритма шифрования и необходимой производительности при обработке потока данных, поступающего на высоких скоростях, в частности, таких как HD видео, 4K видео)

Технический результат, достигаемый заявленной группой изобретений, заключается в повышения надежности защиты от программного расшифрования потока данных, поступающего с большими битрейтами, на микропроцессорах общего назначения для встраиваемых устройств, в том числе, при известном ключе шифрования, в результате применения расширений преобразования AES, зависящих от дополнительного ключа режима и изменяющих функцию генерации SBOX, с обеспечением зависимости SBOX от ключа режима и замедления программной реализации, а также в расширении арсенала известных технических средств, за счет вышеуказанных технических решений..

Заявленный технический результат достигается использованием способа криптографического преобразования для обработки большого массива, пакетов или потоков данных, на основе программно-аппаратной реализации в микропроцессоре, алгоритма блочного шифрования AES, содержащего преобразование исходных данных в структуру S, состоящую из 16-байтных блоков, с последующим ее преобразованием по множеству раундов обратимых преобразований выполняемых циклически и включающих последовательно выполняемые этапы формирования (KeySchedule) раундовых ключей шифрования нелинейным расширением секретного ключа шифра AES, преобразования структуры S заменой (подстановкой) каждого байта структуры с помощью сгенерированной таблицы подстановок SBOX (SubBytes), с последующими преобразованиями структуры S сдвигом строк и перемешиванием столбцов, а также преобразования добавлением раундного ключа на каждом раунде, характеризующиеся при этом тем, что вводят дополнительный исходный ключ режима Kr0 и дополняют исходный шифр AES сопряженным преобразованием, зависящим от дополнительного 128-битного ключа режима Kr, который генерируют из исходного ключа режима Kr0 с использованием двухстадийного преобразования с параметрами степени замедления программных вычислений ключа режима на процессорах общего назначения (CPU) на основе входных данных, путем последовательного формирования в цикле с числом раундов Nc, массива промежуточных ключей режима mKrс=(σ1(mKrc-1)), где с=1…Nc - очередной шаг цикла, σ1 – первое преобразование замедления, а mKr0 = Kr0, с последующим формированием из них массива актуальных ключей режима aKrc = σ2(mKrc), где с=0…Nc - очередной шаг цикла, а σ2 – второе преобразование замедления, из каждого aKrс строят преобразование, которое задается матрицей и вектором переноса, после чего используют комбинацию построенных преобразований, которая образует ключ режима Kr, а генерирование SBOX осуществляют сопряженным преобразованием, зависящим от ключа режима, примененным к преобразованию SubBytes исходного AES для генерации SBOX.

В предпочтительном варианте осуществления изобретения генерацию SBOX осуществляют преобразованием, основанным на функции, принадлежащей к семейству биективных трудно обратимых функций и построенном на афинном преобразовании, примененном к функции генерации S-блоков, используемой в оригинальном алгоритме AES. Причем, в одном из вариантов осуществления, при задании нулевого ключа режима получают SBOX, идентичный оригинальному шифру AES.

В возможном варианте осуществления, заявленного изобретения для генерации массива актуальных ключей режима aKr на основе исходных данных, предпочтительно, используют функцию, основанную на преобразовании Фробениуса. Предпочтительно, для генерации массива актуальных ключей aKr используют функции, основанные на преобразовании Фробениуса, выполненные в разных полях Галуа, где σ1 - преобразование (автоморфизм) Фробениуса в кольце многочленов, факторизуемом на поле GF(2127), а σ2 - преобразование (автоморфизм) Фробениуса в кольце многочленов, факторизуемом на поле GF(2128). При этом, функцию для генерации массива актуальных ключей, также предпочтительно, параметризируют числом, обеспечивающим возможность варьировать число раундов цикла, с возможностью адаптировать алгоритм под тактовую частоту устройства, на котором выполняется аппаратная реализация алгоритма.

В еще одном возможном варианте осуществления заявленного изобретения, при любой реализации заявленного способа шифрования в процессе генерации актуального ключа режима все данные, вычисляемые на каждом раунде цикла, используют в финальном преобразовании, результат которого и является ключом режима. При этом, преобразования для генерации SBOX и актуального ключа режима могут быть применены для каждого 16-байтного блока входных данных или каждого раунда AES, выполняемого в ходе обработки 16-байтного блока данных.

Заявленный технический результат достигается также использованием устройства криптографического преобразования для обработки большого массива, пакетов или потоков данных, на основе программно-аппаратной реализации в микропроцессоре алгоритма блочного шифрования AES, включающее, по меньшей мере, блок расширения ключа шифрования AES, выполненного с обеспечением возможности формирования раундовых ключей шифра AES на основе ключа AES, соединенный с одним из входов блока, реализующего предварительный раунд AES, выполненного с обеспечением возможности реализации функции сложения массива исходных данных в виде структуры S, состоящей из 16-байтных блоков, с первым раундовым ключом блока расширения ключа шифрования, при этом выход блока предварительного раунда AES соединен со входом блока, реализующего раундовые операции, включающего последовательно соединенные блоки: нелинейного преобразования SBOX; сдвига рядов матрицы состояния, сформированной из байт блока данных; перемешивания столбцов матрицы состояния; функции сложения с очередным раундовым ключом AES; последовательно сопряженного с блоком финального раунда, сопряженные с блоками памяти данных и ключей шифрования, характеризующегося тем, что дополнительно включает, по меньшей мере, блок, реализующий преобразования SBOX по способу, в соответствии с п.1 формулы, выполненный с обеспечением возможности дополнения шифра AES сопряженным преобразованием, зависящим от дополнительного 128-битного ключа режима Kr и замедления программных вычислений ключа режима на процессорах общего назначения (CPU) на основе входных данных, включающий последовательно соединенные блок формирования массива актуальных ключей режима aKr из исходного ключа режима Kr0, параметром которого является число раундов цикла Nc, формируемый задающим блоком Nc, выход которого соединен с одним из входов блока формирования массива актуальных ключей 12, и блок формирования SBOX шифра из массива актуальных ключей aKr, выполненный с обеспечением возможности формирования SBOX сопряженным преобразованием, зависящим от ключа режима и в зависимости от выбора режима работы устройства, устанавливаемого задающим блоком режима, выход которого соединен с одним из входов блока формирования SBOX, , при этом выход блока, реализующего преобразования SBOX соединен со входом блока хранения сформированного сопряженным преобразованием блока замен SBOX, соединенного с одним из входов блока нелинейного преобразования SBOX, с обеспечением возможности передачи данных блока замен SBOX..

В одном из возможных вариантов осуществления заявленного устройства блок 10 устройства, реализующего описанный способ, представляет собой программно-аппаратный модуль в составе, реализованных программно-аппаратным образом на основе микропроцессора, блока генерации массива промежуточных ключей режима mKr, на основе циклического применения преобразования Фробениуса в GF(2127) и сохранения результата в последовательно соединенном блоке регистров, данные с выхода которого поступают на вход блока генерации актуальных ключей, представляющий собой статическую комбинационную схему, интегрируемый в схему генерации блока замен SBOX, образуя единый блок в виде комбинационной схемы, реализующий применение преобразования Фробениуса в GF(2128), с формированием массива 128-битных актуальных ключей режима aKr, при этом выход блока генерации актуальных ключей последовательно соединен с блоком формирования SBOX шифра, обеспечивающим программно-аппаратную реализацию функции генерации SBOX на основе массива актуальных ключей режима. При этом, в еще одном возможном варианте осуществления, блок формирования SBOX шифра может быть выполнен с обеспечением возможности генерации различных таблиц замен, каждая из которых используется в очередном раунде.

Заявленные способ шифрования и устройство для его осуществления могут быть реализованы программно-аппаратным образом на компьютере или иных программируемых устройствах, в том числе, под управлением программируемых процессоров, микропроцессоров, в качестве реализуемого программируемым процессором способа или в выделенных аппаратных средствах либо в комбинации вышеозначенного.

В предшествующем уровне техники не выявлены близкие аналоги (прототип) обеспечивающие решение заявленной технической проблемы и достижение заявленного технического результата указанным способом и аппаратной реализацией.

Краткое описание графических материалов:

Заявленная группа изобретений поясняется следующими графическими материалами:

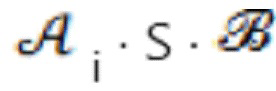

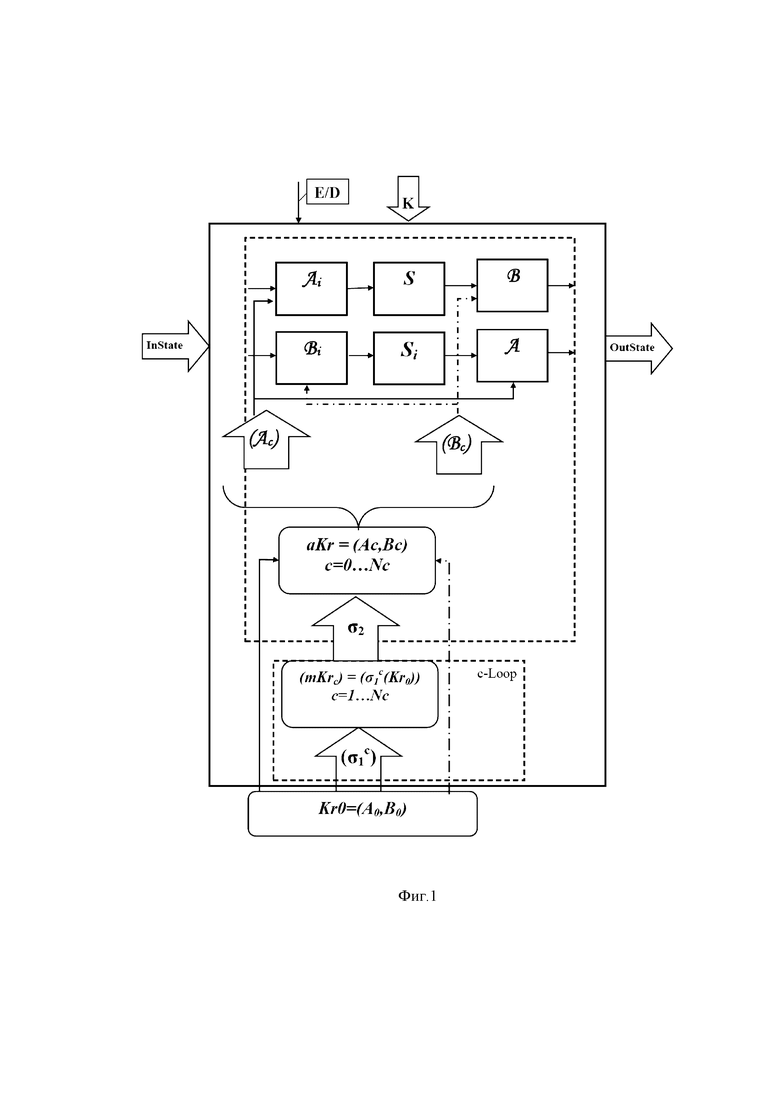

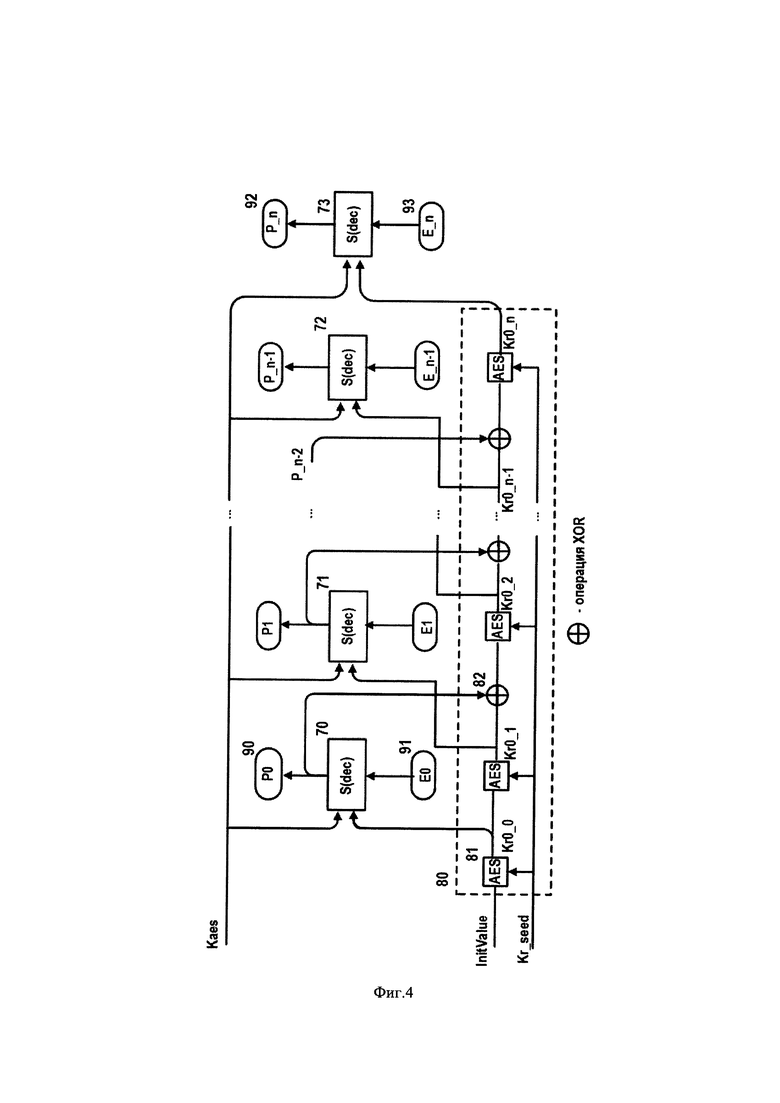

фиг.1 – схема операции SubBytes алгоритма шифрования согласно заявленному способу шифрования;

фиг.2 – блок-схема устройства шифрования согласно заявленному изобретению;

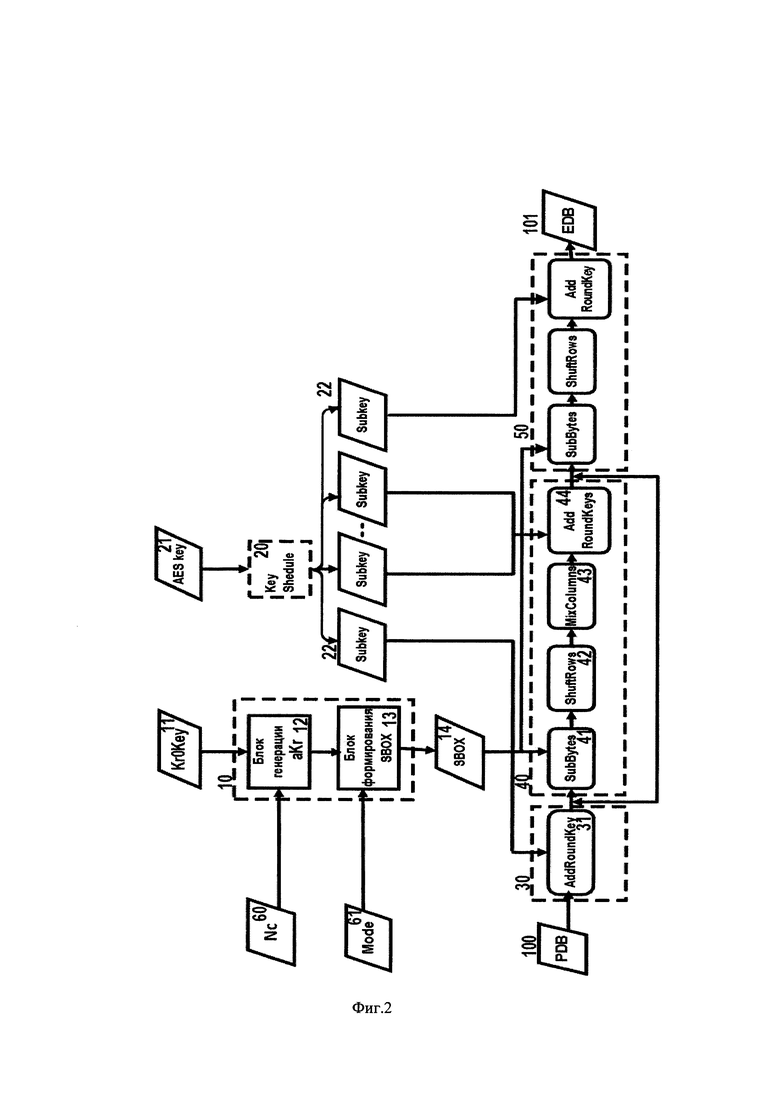

фиг.3 – блок-схема блока реализующего преобразования SBOX, согласно заявленной группы изобретений

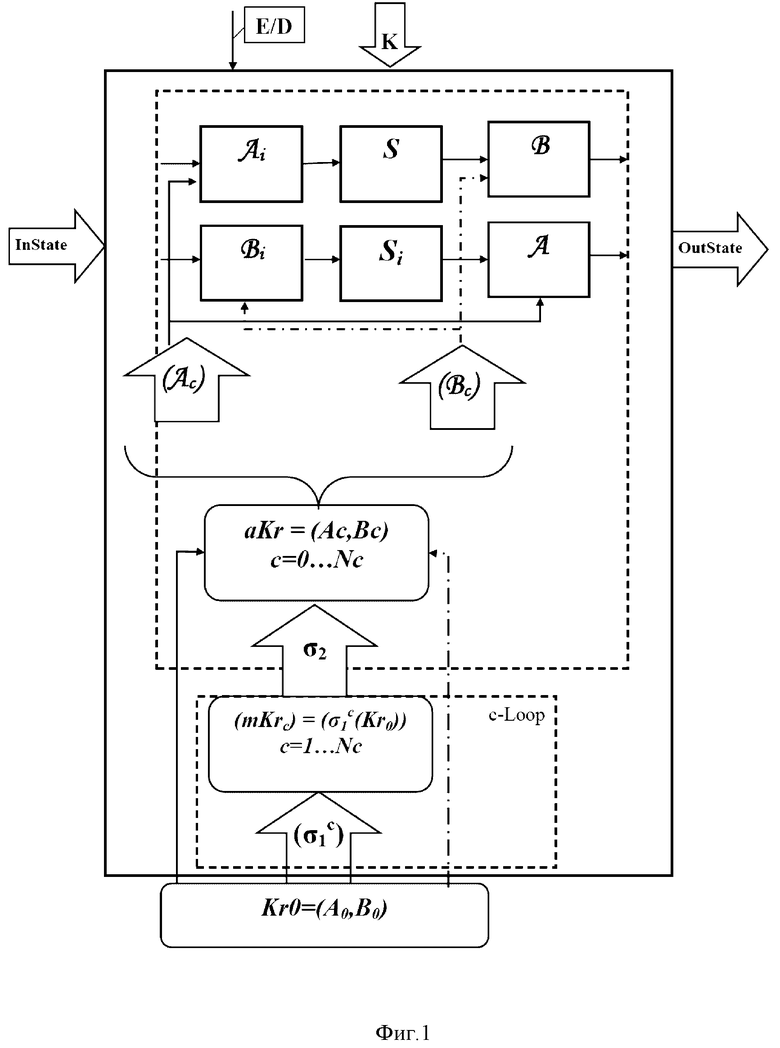

фиг.4 – блок-схема устройства обработки потока данных, включающего формирователь ключей Kr0 из Kr_seed.

Следует отметить, что прилагаемые графические материалы иллюстрируют только некоторые из наиболее предпочтительных вариантов осуществления группы изобретений и не могут рассматриваться в качестве ограничений их содержания, которое, очевидным образом, включает и другие варианты осуществления.

Осуществимость изобретения.

Согласно представленным на фиг.1-4 графическим материалам, заявленная группа изобретений обеспечивает построение расширений преобразования AES, которые зависят от дополнительного ключа, а также построение преобразований, которые вносят весомые задержки при программных вычислениях дополнительного ключа на процессорах общего назначения (CPU), но легко реализуется в комбинационных микросхемах. Данное свойство (медленная программная реализация алгоритма) сохраняется даже при известном ключе шифрования и известном дополнительном ключе.

В заявленном решении в качестве базового алгоритма шифрования используется AES (Rijndael). Данный алгоритм имеет фиксированный список преобразований блока данных и прост как в программной, так и в аппаратной реализации, что позволяет добиться высоких скоростей обработки данных на аппаратном и на программном уровне.

В предлагаемом способе и устройстве, реализующем шифрование потока данных с большими битрейтами, используются две дополнительные операции, которые отличают его от исходного AES, известного из предшествующего уровня техники:

- дополнение исходного шифра AES специализированным преобразованием, которое позволяет изменить функцию генерации SBOX, что делает SBOX зависящем от дополнительного 128-битного ключа (далее - ключ режима);

- использование дополнительного специализированного алгоритма с параметром степени замедления, который на основе выборочных и предустановленных в памяти процессора входных данных генерирует ключ режима, используемый для генерации SBOX и является основной для замедления программной реализации.

При этом, указанное выше специализированное преобразование, используемое в генерации SBOX, основано на функции, принадлежащей к семейству биективных трудно обратимых функций и строится на афинном преобразовании, примененном к функции генерации S-блоков (SBOX), используемой в оригинальном алгоритме шифрования AES. Данный подход позволяет сохранить свойства SBOX оригинального AES, а также позволяет при задании нулевого ключа режима получить SBOX, идентичный оригинальному AES.

Для целей замедления программной реализации шифра, основанного на AES, с сохранением эффективной (простой) аппаратной реализации, в предлагаемом изобретении используется генерация SBOX в зависимости от дополнительного ключа режима, для чего предлагается использовать сопряженное преобразование, примененное к преобразованию SubBytes исходного AES для генерации SBOX, а также специализированное преобразование, которое формирует ключ генерации SBOX (далее, ключ режима Kr) из начального (входного) ключа режима Kr0. В качестве вышеуказанного специализированного преобразования используют функцию, основанную на преобразовании Фробениуса. При этом функция параметризируется числом, которое позволяет варьировать число раундов цикла генерации массива актуальных ключей режима aKr, используемых для генерации ключа режима Kr. Такая параметризация позволяет адаптировать алгоритм под тактовую частоту устройства, на котором выполняется аппаратная реализация алгоритма. Поскольку все данные, вычисляемые на каждом раунде цикла, используются в финальном преобразовании, результатом которого и является ключ режима, алгоритм генерации актуального ключа режима построен таким образом, что он не может быть распараллелен. Таким образом, суммарно на расчет таблицы замен SBOX для обработки каждого блока данных происходит основная трата времени в программной реализации, при этом за счет свойств выбранных преобразований аппаратная реализация может быть выполнена эффективно как для функции вычисления ключа режима, так и для построения SBOX на его основе. Данная функция является основной для замедления программной реализации.

Указанные выше преобразования для генерации S-блоков и актуального ключа режима могут применяться для каждого 16-байтного блока входных данных либо для каждого раунда AES, выполняемого в ходе обработки 16-байтного блока данных, что позволяет как получить необходимую задержку в производительности при программной реализации алгоритма, так и обеспечить криптостойкость и конфиденциальность данных.

Количество раундов цикла преобразований определяется параметром Nc, позволяющим выбрать оптимальное соотношение сложности программной и аппаратной реализаций при заданной тактовой частоте микропроцессора.

Построение преобразования, изменяющего SBOX в зависимости от ключа согласно заявленному изобретению, в общем случае осуществляют следующим образом:

1. Вводят дополнительный 128-битный дополнительный ключ режима Kr , который может быть представлен как 2х-клеточная матрица Kr=(A|B), где A и B представляют собой сумму (L + D + U), где L - левая нижне-треугольная матрица с нулевыми диагоналями, D - диагональная матрица, U - правая верхне-треугольная с нулевыми диагоналями;

2. Синтезируют обратимую матрицу M=(L+E) (E+U), где E - единичная матрица 8x8 бит, а также 8-битный вектор t переноса;

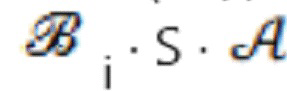

3. Формируют аффинное преобразование T: T(b)=M*b+t пространства F28, представленного подстановкой T на множестве {0..255} значений байта. Подстановка T•S•T-1, сопряженная подстановке S оригинального S-блока (SBOX), даёт клон шифра AES с зависимостью от дополнительного ключа длиной 64 бита, что соответствует одной подматрице ключа режима.

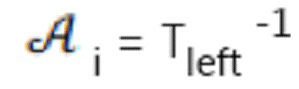

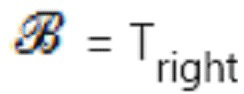

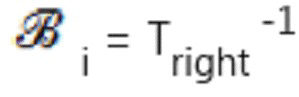

4. Для использования 128-битного ключа формируют двустороннюю модификацию подстановок: Tleft-1•S•Tright (при зашифровании) и Tright-1•S-1•Tleft (при расшифровании), т.е. используют разные аффинные преобразования, синтезированные из половинок ключа режима (подматрицы A и B), которые можно записать для простоты как:  для зашифрования, и как

для зашифрования, и как  для расшифрования, где:

для расшифрования, где:

и

и  - преобразования, построенные на подматрице Ас ключа режима Kr;

- преобразования, построенные на подматрице Ас ключа режима Kr;

и

и  - преобразования, построенные на подматрице Вс ключа режима Kr;

- преобразования, построенные на подматрице Вс ключа режима Kr;

S - sbox(x), преобразование оригинального алгоритма AES.

Очевидно, что раскрытое выше преобразование обладает следующим свойством: при нулевом ключе режима данное преобразование будет совпадать с исходным преобразованием S оригинального алгоритма AES.

Для практической реализации заявленного способа шифрования необходимо осуществление двух последовательно выполняемых этапов:

1 этап - построение преобразования для вычисления актуальных ключей режима aKr на основе исходного Kr0,

2 этап - построение финального преобразования, SBOX заявленного способа шифрования, на основе массива актуальных ключей режима aKr.

Выполнения данных этапов осуществляют следующим образом:

Этап 1. Преобразование для вычисления актуальных ключей режима aKr на основе исходного Kr0:

1. На основе исходного ключа режима Kr0 в цикле формируется массив актуальных ключей режима aKrс , где с=0...Nc – очередной шаг цикла, а Nc - число раундов цикла . При этом, выполняются следующие преобразования:

a) вычисляется очередной промежуточный ключ режима mKrc=(σ1(mKrc-1)), где σ1 - преобразование (автоморфизм) Фробениуса в кольце многочленов, факторизуемом на поле GF(2127) (блок 1, фиг.3), т.е. σ1(x)=x2 в GF(2127), причем устанавливается начальное значение промежуточного ключа mКr0 = Кr0 для c=0, далее mKrc опрделяется на каждом шаге цикла для с = 1… Nc .

b) вычисляется очередной актуальный ключ режима aKrc = σ2(mKrc), где с - очередной шаг цикла (с=0…Nc), а σ2 - преобразование (автоморфизм) Фробениуса в кольце многочленов, факторизуемом на поле GF(2128), т.е. σ2(х) =х2 в GF(2128).

Этап 2. Построение финального преобразования - SBOX шифра на основе ключей aKr.

1. Для массива актуальных ключей режима aKrc, где с=0...Nc, выполняют построение массива аффинных преобразований Tс, где каждое преобразование Tc строится по описанному выше способу построения преобразования, изменяющего SBOX в зависимости от ключа: Tс: T(b)=M*b+t пространства F28.

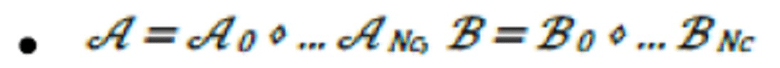

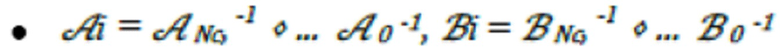

2. Преобразования комбинируют между собой следующим образом:

– составные отображения пространства F28

– составные отображения пространства F28

– их обратные отображения.

– их обратные отображения.

3. Осуществляют генерацию (формирование) SBOX, параметризированную 128-битным исходным ключом режима Kr0 и числом раундов цикла замедления Nc, зависящую от массива актуальных ключей режима aKrс, c=0..Nc, как:

SBOX =  для зашифрования, и SBOX-1=

для зашифрования, и SBOX-1=  для расшифрования, где S – исходное преобразование алгоритма AES.

для расшифрования, где S – исходное преобразование алгоритма AES.

Описываемый способ криптографического преобразования (шифрования), основанный на модификации базового алгоритма AES представлен на блок-схеме фиг.1, отражающей порядок осуществления преобразования SubBytes согласно заявленному способу криптографического преобразования, принимая во внимание, что остальные операции раунда алгоритма AES, а также схемы вычисления ключей шифрования для каждого раунда AES (key schedule) остаются без изменений.

Согласно представленной блок-схеме (фиг.1) в качестве входных данных для реализации заявленного способа шифрования используются:

• Режим работы: зашифрования/расшифрования (E/D)

• Исходный 128-битный ключ режима Kr0

• Обрабатываемые, входные, данные (InState)

Выходными данными алгоритма является преобразованные шифром данные (OutState).

Более наглядно заявленная группа изобретений может быть рассмотрена на примере организации устройства шифрования, согласно заявленному изобретению, и порядка его работы. В частности, на схемных решениях фиг.2-4 представлены примеры осуществимости заявленного решения.

Заявленный технический результат достигается за счет устройства, реализующего указанные преобразования в составе шифратора AES. Блок, генерирующий массив актуальных ключей режима aKr и блок, реализующий вычисление SBOX на основе ключей режима, встраиваются в устройство шифрования, представленное на блок-схеме фиг.2. В частности, согласно представленной блок-схеме, устройство для реализации заявленного способа шифрования включает:

• блок 10, реализующий заявленный способ, в составе: блок 12 генерации массива актуальных ключей режима aKr из исходного ключа Kr0 (11), параметром которого является число раундов цикла (Nc), формируемое задающим блоком 60, и блок 13 формирования SBOX шифра из ключей aKr, зависящий от режима работы - шифрование или расшифрование, заданным блоком 61 режима (Mode). Параметр Nc может задаваться программно-аппартным образом, в зависимости от необходимой степени замедления и ресурсов аппаратного блока, реализующего заявленный алгоритм шифрования.

• Блок расширения (Key schedule) 20 ключа 21 шифрования Kaes (AES key), генерирующий раундовые 22 ключи шифра AES: subkey1... subkey11 на основе ключа AES (21)

• Блок, реализующий предварительный 30 раунд AES (ADDRoundKey), состоящий из блока 31, реализующего функцию сложения с первым раундовым ключом, представленной в виде операции "исключающее или" (XOR)

• Блок 40, реализующий раундовые операции, состоящие из последовательно соединенных:

• блока 41 нелинейного преобразования SBOX (SubBytes), сформированного на основе заявленного способа формирования SBOX, реализованного в блоке 10,

• блока 42 сдвига рядов матрицы состояния, сформированной из 16 блока данных,

• блока 43 перемешивания столбцов матрицы состояния

• блока 44 функции сложения с очередным раундовым ключом, представленной в виде операции "исключающее или" (XOR)

• блока 50 финального раунда, состоящего из трех посдледовательно сединенных блоков, реализующих последовательно следующие 3 операции:

• нелинейного преобразования SBOX (блок SubBytes, аналогичный блоку 41), сформированного на основе заявленного способа шифрования, реализованного в блоке (10),

• сдвига рядов матрицы состояния, сформированной из 16 блока данных (блок ShiftRows, аналогичный блоку 42),

• функции сложения с последним раундовым ключом (блок AddRoundKey, анлогичный блоку 44), представленной в виде операции "исключающее или" (XOR).

Входными значениями для устройства являются: ключ шифрования Kaes (блок 21 (AES key)), исходный ключ режима Kr0, формируемый блоком 11, режим работы (зашифрование/расшифрование), определяемый блоком 61 режима, 16-байтный блок данных 100(Plain data block), который необходимо обработать. Выходными данными является преобразованный 16-байтный блок, представленный на схеме фиг.2, как блок 101 выходных данных EDB (Encrypted data block).

В результате выполнения вышеуказанной последовательности действий в устройстве, выполняется операция шифрования данных, в ходе которой исходный блок 100 данных зашифровывается с помощью заявленного способа криптографического преобразования.

Как следует из представленой блок-схемы заявленного устройства (фиг.2) блок 20 расширения ключа шифрования AES, генерирующий (формирующий) раундовые ключи 22 шифра AES на основе ключа AES 21, выполнен соединенным со вторым входом блока 30, реализующего предварительный раунд AES, с обеспечением возможности выполнения функции сложения с первым раундовым ключом массива исходных данных в виде структуры S состоящей из 16-байтных блоков, поступающих на первый вход блока 31 (AddRoundKey) предварительного раунда. Выход блока 31 (AddRoundKey) блока 30 предварительного раунда соединен со входом блока 40, реализующего раундовые операции AES, состоящего из: последовательно соединенных блоков 41 нелинейного преобразования SBOX; сдвига рядов матрицы состояния 42, сформированной из 16 блока данных; перемешивания столбцов 43 матрицы состояния; функции сложения с очередным раундовым ключом 44, последовательно сопряженного с блоком 50 финального раунда. При этом, блок 10, реализующий преобразования SBOX согласно заявленному способу шифрования, включающий последовательно соединенные блок 12 формирования (генерации) массива актуальных ключей режима aKr из исходного ключа Kr0 (11), параметром которого является число циклов Nc, поступающий на первый вход блока 12 и блок 13 формирования SBOX шифра из ключей aKr и зависящий от текущего режима работы, заданного блоком 61 режима, данные о котором поступают на первый вход модуля, при этом выход блока 10 соединен со входом модуля хранения сформированного (сгенерированного) блока замен SBOX, данные которого поступают на второй вход блока 41 нелинейного преобразования SBOX.

При этом, блок 10 устройства, реализующего описанный способ, представляет собой программно-аппаратный модуль (фиг.3)в составе, реализованных программно-аппаратным образом на основе микропроцессора, блока 1 генерации (формирования) массива промежуточных ключей режима mKr, на основе циклического применения преобразования Фробениуса (σ1) в GF(2127) и сохранения результата в последовательно соединенном блоке регистров 2, используемого для конфигурации блока формирования актуальных ключей режима. Данные с выхода блока регистров 2 поступают на вход блока 3 формирования (генерации) актуальных ключей, представляющий собой статическую комбинационную схему, интегрируемую в схему формирования (генерации) блока 4 замен SBOX, образуя единый блок 5 в виде комбинационной схемы, реализующий применение преобразования Фробениуса (σ2) в GF(2128), с формированием массива 128-битных актуальных ключей режима aKr. При этом выход блока формирования актуальных ключей последовательно соединен с блоком 4 формирования SBOX, обеспечивающим программно-аппаратную реализацию функции формирования SBOX на основе массива актуальных ключей режима.

Промежуточные ключи режима mKrc, согласно заявленному изобретению, в микросхеме последовательно (цикл за циклом) записываются в матрицу из Nc 128-битных регистров, настраивая статическую (комбинационную) логическую схему на нужный режим.

Полная последовательность актуальных ключей режима aKrc представляется в микросхеме только текущим состоянием потенциалов промежуточных соединительных проводников, а не регистром памяти. При этом, благодаря последовательному вычислению актуальных ключей режима aKrc (c = 0…Nc), например, при числе раундов цикла Nc = 20, полная последовательность актуальных ключей режима аКrc будет существовать в микросхеме только в течение 1/3 доли рабочего времени обработки 16-байтного блока. Начальные 2/3 времени будут «истрачены» на последовательную подготовку полной последовательности актуальных ключей режима, пространственно распределённых в микросхеме.

Поскольку все обратимые аффинные преобразования пространства F28, реализуемые в блоках 3, 4, выражаются через две операции алгебры Жегалкина: «&» (and - умножение) и «+» (XOR - сложение бит по модулю 2), они могут быть реализуемы комбинационными схемами на основе этих операций, требующими для выполнения всего аффинного преобразования не более одного такта процессора. Программная же эмуляция этих преобразований требует числа тактов, пропорционального количеству логических операций.

Указанные на блок-схемах фиг. 2 и 3 модули и блоки устройства обрабатывают 16-байтный блок, используя одну таблицы замен SBOX, сформированную описанным способом. Однако, блок устройства может быть сконфигурирован для генерации различных таблиц замен, в частности, генерации 11 таблиц замен, каждая из которых используется в очередном раунде.

В устройстве, реализующем заявленный способ шифрования большого массива данных, состоящих из последовательно шифрованных 16-байтных блоков, также может быть применена схема формирования начальных ключей режима Kr0 для каждого блока данных на основе исходного значения Kr_seed, т.е значения ключа, сгенерированного случайным образом. Данная схема позволяет избежать избыточной передачи Kr0 в потоке и использовать уникальные значения Kr0 для каждого 16-байтного блока данных.

Практическая реализация способа обработки потока данных, включающего формирователь ключей Kr0 из Kr_seed, и устройство для его осуществления, представлены на блок-схеме (фиг. 4). На данной схеме для наглядности действия раскрытого выше заявленного способа криптографического преобразования и устройства для его реализации, представлена работа устройства, согласно заявленному изобретению, работающего в режиме расшифрования, дающая представление, каким образом в формирователе ключей используется зависимость от расшифрованного на предыдущем шаге блока, что, в конечном итоге, позволяет избежать распараллеливания в программной реализации, т.к. начальные ключи режима Kr0_i не могут быть вычислены заранее. В данном случае, Kr0_i указывает на обработку не единичного блока данных, а очередного пакета данных, состоящих из последовательности 16-байтных блоков, каждому из которых подаются свой начальный ключ режима, при этом i- порядковый номер блока в пакете данных и соответствующего ему начального ключа режима.

Устройство на блок-схеме (фиг. 4) состоит из следующих блоков и модулей:

• формирователь 80 ключей режима Kr0_i для обработки каждого блока пакета 90 шифрованных данных, в составе:

• блока 81 шифра AES

• блока 82 выполняющего операцию "исключающее ИЛИ" (XOR)

• программно-аппаратного модуля 70 реализующего заявленный способ криптографического преобразования блока данных, приведенного в деталях на блок схеме фиг. 2

Схема работы устройства для расшифрования последовательности данных реализуется следующим образом.

Устройство предварительно настраивают на работу в режиме расшифрования и задают число раундов цикла Nc в модуле генерации актуального ключа режима aKr в составе формирователя ключей 80 для обеспечения необходимой степени замедления. На вход подают:

• последовательность блоков шифрованных данных Ei, i=0...n;

• ключ шифрования Kaes;

• ключ Kr_seed;

• начальное значение InitValue, из которого формируются ключи Kr0_i, где InitValue некоторое значение, случайное (идеальный случай) или не случайное, но которое изменяется довольно часто, используемое для генерации различных ключей режима Kr0_0 для каждого 16-байтного блока пакета данных.

Формирователь 80 ключей режима Kr0_i шифрует InitValue в аппаратном блоке AES 81 с использованием в качестве ключа значение Kr_seed, тем самым формируя ключ Kr0_0 для первого модуля 70 реализующего заявленный способ криптографического преобразования. Далее модуль 70, использует полученный из формирователя 80 ключ Kr0_0, ключ Kaes и расшифровывает данные E0 (блок 91), получая расшифрованный блок 90 данных P0, который сохраняется в выходном буфере устройства, а также подается в формирователь ключей (80) для вычисления следующего Kr0_i.

Далее аналогичным образом происходит подготовка ключа Kr0_1 и расшифровка блока данных E1 посредством модуля 71, аналогичного модулю 70, реализующего очередной этап криптографического преобразования.

После этого формирователь, начиная с третьего блока E2, использует операции AES (81) и XOR (82) с ключом Kr_seed, расшифрованными на предыдущем шаге данными P_i-2 и предыдущим ключом режима Kr0_i-1 для последовательного вычисления Kr0_j, который, в свою очередь, передается в блок, реализующий указанный способ, для расшифровки очередных данных E_j (на блок схеме фиг.4, все позиции, связанные с блоками 71-73, 92, 93).

В общем случае работу формирователя ключей Kr0_i можно описать выражениями:

• Kr0_0 = AES_enc(Kr_seed, InitValue)

• Kr0_1 = AES_enc(Kr_seed, Kr0_0)

• Kr0_i = AES_enc(Kr_seed, Kr0i-1 XOR Pi-2 ) for i=2...n

где:

• data_enc = AES_enc(key, data) - операция шифрования 'data' ключом 'key' алгоритмом AES-128 в режиме электронной кодовой книги (ECB)

• InitValue - некоторое произвольно (псевдо)случайное значение

• n - число 16-байтных блоков в последовательности данных.

Очевидным образом, реализованный в заявленной группе изобретений способ криптографического преобразования обеспечивает исключение процесса распараллеливания в программной реализации способа.

Описанный выше алгоритм устройства приведен для режима шифрования ECB и, очевидно, может быть распространен для других режимов: CBC и CTR.

Таким образом, заявленный способ криптографического преобразования и устройство для его осуществления, за счет применения дополнительного преобразования, усложняющего программную реализацию алгоритма шифрования, при сохранении простой аппаратной реализации, позволяет достичь поставленной цели защиты от программной расшифровки данных, поступающих с большими битрейтами, на микропроцессорах без аппаратной поддержки нового преобразования, даже при известном ключе шифрования.

Данный способ и устройство могут быть применены для защиты HD и 4K видеоконтента: контент может быть расшифрован и воспроизведен только на специализированных микропроцессорах с поддержкой алгоритма, при этом на других микропроцессорах, которые оптимизированы на обработку, расшифровку, декодирование видеопотока и аппаратно поддерживают только стандартные алгоритмы, будет недостаточно процессорной мощности для расшифровки программными средствами видеопотока, поступающего в режиме реального времени (он-лайн трансляции сигнала).

Источники информации

1. National Institute of Standards and Technology, U.S. Department of Commerce. "Advanced Encryption Standard", Federal Information Processing Standards Publication 197, Washington, DC, November 2001.

2. Julia Juremi, Ramlan Mahmod, Salasiah Sulaiman, Jazrin Ramli. Enhancing Advanced Encryption Standard S-Box Generation Based on Round Key/International Journal of Cyber-Security and Digital Forensics (IJCSDF) 1(3): 183-188 The Society of Digital Information and Wireless Communications (SDIWC) 2012 (ISSN: 2305-0012)

3. Erik Boss, Vincent Grosso, Tim Guneysu, Gregor Leander, Amir Moradi, and Tobias Schneider. Strong 8-bit Sboxes with Efficient Masking in Hardware/ IACR-CHES-2016, 22 Jun 2016

4. Farrugia et al. Patent No: US2015/0349951 A1. Protecting cryptographic operations using conugacy class functions.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ НЕЛИНЕЙНОГО ТРЕХМЕРНОГО МНОГОРАУНДОВОГО ПРЕОБРАЗОВАНИЯ ДАННЫХ RDOZEN | 2015 |

|

RU2591015C1 |

| СПОСОБ НЕЛИНЕЙНОГО ТРЕХМЕРНОГО МНОГОРАУНДОВОГО ПРЕОБРАЗОВАНИЯ ДАННЫХ DOZEN | 2012 |

|

RU2503994C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ В ВИДЕ УЛЬТРАСЖАТОГО НАНОБАР-КОДА (ВАРИАНТЫ) | 2013 |

|

RU2656734C2 |

| СПОСОБ ПРИМЕНЕНИЯ КОНТРМЕР ПРОТИВ АТАК ПО СТОРОННИМ КАНАЛАМ | 2012 |

|

RU2586020C2 |

| СПОСОБ ИТЕРАТИВНОГО КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ ДАННЫХ | 2012 |

|

RU2504911C1 |

| СПОСОБ НЕЛИНЕЙНОГО ТРЕХМЕРНОГО МНОГОРАУНДОВОГО ПРЕОБРАЗОВАНИЯ ДАННЫХ | 2017 |

|

RU2683689C1 |

| ЭЛЕКТРОННОЕ УСТРОЙСТВО БЛОЧНОГО ШИФРОВАНИЯ, ПОДХОДЯЩЕЕ ДЛЯ ОБФУСКАЦИИ | 2014 |

|

RU2666281C2 |

| СПОСОБ БЛОЧНОГО ПРЕОБРАЗОВАНИЯ ЦИФРОВЫХ ДАННЫХ НА ОСНОВЕ РЕГИСТРА СДВИГА ДЛИНЫ ВОСЕМЬ С 32-БИТОВЫМИ ЯЧЕЙКАМИ И С ТРЕМЯ ОБРАТНЫМИ СВЯЗЯМИ | 2022 |

|

RU2796629C1 |

| ЗАЩИТА ОТ ПАССИВНОГО СНИФФИНГА | 2011 |

|

RU2579990C2 |

| СПОСОБ КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ БЛОКОВ ЦИФРОВЫХ ДАННЫХ | 2007 |

|

RU2359415C2 |

Изобретение относится к области вычислительной техники. Технический результат заключается в повышения надежности защиты от программного расшифрования потока данных, поступающего с большими битрейтами, на микропроцессорах общего назначения для встраиваемых устройств, в том числе при известном ключе шифрования, в результате применения расширений преобразования AES, зависящих от дополнительного ключа режима и изменяющих функцию генерации SBOX, с обеспечением зависимости SBOX от ключа режима и замедления программной реализации, а также в расширении арсенала известных технических средств за счет вышеуказанных технических решений. Раскрыт способ криптографического преобразования для обработки большого массива, пакетов или потоков данных на основе программно-аппаратной реализации в микропроцессоре алгоритма блочного шифрования AES, включающий преобразование исходных данных в структуру S, состоящую из 16-байтных блоков, с последующим ее преобразованием по множеству раундов обратимых преобразований, выполняемых циклически и включающих последовательно выполняемые этапы формирования (KeySchedule) раундовых ключей шифрования нелинейным расширением секретного ключа шифра AES, преобразования структуры S заменой (подстановкой) каждого байта структуры с помощью сгенерированной таблицы подстановок SBOX (SubBytes), с последующими преобразованиями структуры S сдвигом строк и перемешиванием столбцов, а также преобразования добавлением раундного ключа на каждом раунде, характеризующийся при этом тем, что предустанавливают дополнительный исходный ключ режима Kr0 и дополняют исходный шифр AES сопряженным преобразованием, зависящим от дополнительного 128-битного ключа режима Kr, который генерируют из исходного ключа режима Kr0 с использованием двухстадийного преобразования с параметрами степени замедления программных вычислений ключа режима на процессорах общего назначения (CPU) на основе входных данных, путем последовательного формирования в цикле с предустановленным числом раундов цикла Nc, массива промежуточных ключей режима mKrc=(σ1(mKrc-1)), где c=1…Nc - очередной шаг цикла, σ1 - первое преобразование замедления, а mKr0=Kr0, с последующим формированием из них массива актуальных ключей режима aKrc=σ2(mKrc), где c=0…Nc - очередной шаг цикла, а σ2 - второе преобразование замедления, на основе исходных данных с использованием функции, основанной на преобразовании Фробениуса, причем из каждого aKrc далее строят преобразование, которое задается матрицей и вектором переноса, после чего используют комбинацию построенных преобразований, которая образует ключ режима Kr, а генерирование SBOX осуществляют сопряженным преобразованием, зависящим от ключа режима, примененным к преобразованию SubBytes исходного AES для генерации SBOX, основанным на функции, принадлежащей к семейству биективных трудно обратимых функций, и построенным на аффинном преобразовании, примененном к функции генерации S-блоков, используемой в оригинальном алгоритме AES. 2 н. и 7 з.п. ф-лы, 4 ил.

1. Способ криптографического преобразования для обработки большого массива, пакетов или потоков данных на основе программно-аппаратной реализации в микропроцессоре алгоритма блочного шифрования AES, включающий преобразование исходных данных в структуру S, состоящую из 16-байтных блоков, с последующим ее преобразованием по множеству раундов обратимых преобразований, выполняемых циклически и включающих последовательно выполняемые этапы формирования (KeySchedule) раундовых ключей шифрования нелинейным расширением секретного ключа шифра AES, преобразования структуры S заменой (подстановкой) каждого байта структуры с помощью сгенерированной таблицы подстановок SBOX (SubBytes), с последующими преобразованиями структуры S сдвигом строк и перемешиванием столбцов, а также преобразования добавлением раундного ключа на каждом раунде, характеризующийся при этом тем, что предустанавливают дополнительный исходный ключ режима Kr0 и дополняют исходный шифр AES сопряженным преобразованием, зависящим от дополнительного 128-битного ключа режима Kr, который генерируют из исходного ключа режима Kr0 с использованием двухстадийного преобразования с параметрами степени замедления программных вычислений ключа режима на процессорах общего назначения (CPU) на основе входных данных, путем последовательного формирования в цикле с предустановленным числом раундов цикла Nc, массива промежуточных ключей режима mKrc=(σ1(mKrc-1)), где c=1…Nc - очередной шаг цикла, σ1 - первое преобразование замедления, а mKr0=Kr0, с последующим формированием из них массива актуальных ключей режима aKrc=σ2(mKrc), где c=0…Nc - очередной шаг цикла, а σ2 - второе преобразование замедления, на основе исходных данных с использованием функции, основанной на преобразовании Фробениуса, причем из каждого aKrc далее строят преобразование, которое задается матрицей и вектором переноса, после чего используют комбинацию построенных преобразований, которая образует ключ режима Kr, а генерирование SBOX осуществляют сопряженным преобразованием, зависящим от ключа режима, примененным к преобразованию SubBytes исходного AES для генерации SBOX, основанным на функции, принадлежащей к семейству биективных трудно обратимых функций, и построенным на аффинном преобразовании, примененном к функции генерации S-блоков, используемой в оригинальном алгоритме AES.

2. Способ по п. 1, отличающийся тем, что при задании нулевого ключа режима получают SBOX, идентичный оригинальному шифру AES.

3. Способ по п. 1, отличающийся тем, что для генерации массива актуальных ключей aKr используют функции, основанные на преобразовании Фробениуса, выполненные в разных полях Галуа, где σ1 - преобразование (автоморфизм) Фробениуса в кольце многочленов, факторизуемом на поле GF(2127), а σ2 - преобразование (автоморфизм) Фробениуса в кольце многочленов, факторизуемом на поле GF(2128).

4. Способ по п. 1, отличающийся тем, что функцию для генерации массива актуальных ключей параметризируют числом, обеспечивающим возможность варьировать число раундов цикла, с возможностью адаптировать алгоритм под тактовую частоту устройства, на котором выполняется аппаратная реализация алгоритма.

5. Способ по любому из пп. 1-4, отличающийся тем, что в процессе генерации актуального ключа режима все данные, вычисляемые на каждом раунде цикла, используют в финальном преобразовании, результат которого и является ключом режима.

6. Способ по п. 5, отличающийся тем, что преобразования для генерации SBOX и актуального ключа режима применяют для каждого 16-байтного блока входных данных или каждого раунда AES, выполняемого в ходе обработки 16-байтного блока данных.

7. Устройство криптографического преобразования для обработки большого массива, пакетов или потоков данных на основе программно-аппаратной реализации в микропроцессоре алгоритма блочного шифрования AES, включающее, по меньшей мере, блок расширения ключа шифрования AES, выполненный с обеспечением возможности формирования раундовых ключей шифра AES на основе ключа AES, соединенный с одним из входов блока, реализующего предварительный раунд AES, выполненного с обеспечением возможности реализации функции сложения массива исходных данных в виде структуры S, состоящей из 16-байтных блоков, с первым раундовым ключом блока расширения ключа шифрования, при этом выход блока предварительного раунда AES соединен со входом блока, реализующего раундовые операции, включающего последовательно соединенные блоки: нелинейного преобразования SBOX; сдвига рядов матрицы состояния, сформированной из байт блока данных; перемешивания столбцов матрицы состояния; функции сложения с очередным раундовым ключом AES; последовательно сопряженного с блоком финального раунда, сопряженные с блоками памяти данных и ключей шифрования, характеризующееся тем, что дополнительно включает, по меньшей мере, блок, реализующий преобразования SBOX по способу в соответствии с п. 1 формулы, выполненный с обеспечением возможности дополнения шифра AES сопряженным преобразованием, зависящим от дополнительного 128-битного ключа режима Kr, и замедления программных вычислений ключа режима на процессорах общего назначения (CPU) на основе входных данных, включающий последовательно соединенные блок формирования массива актуальных ключей режима aKr из исходного ключа режима Kr0, параметром которого является число раундов цикла Nc, формируемое задающим блоком Nc, выход которого соединен с одним из входов блока формирования массива актуальных ключей, и блок формирования SBOX шифра из массива актуальных ключей aKr, выполненный с обеспечением возможности формирования SBOX сопряженным преобразованием, зависящим от ключа режима, и в зависимости от выбора режима работы устройства, устанавливаемого задающим блоком режима, выход которого соединен с одним из входов блока формирования SBOX, при этом выход блока, реализующего преобразования SBOX, соединен с входом блока хранения сформированного сопряженным преобразованием блока замен SBOX, соединенного с одним из входов блока нелинейного преобразования SBOX, с обеспечением возможности передачи данных блока замен SBOX.

8. Устройство по п. 7, отличающееся тем, что блок устройства, реализующий преобразования SBOX по способу в соответствии с п. 1 формулы, представляет собой программно-аппаратный модуль в составе реализованных программно-аппаратным образом на основе микропроцессора блока формирования массива промежуточных ключей режима mKr, на основе циклического применения преобразования Фробениуса в GF(2127) и сохранения результата в последовательно соединенном блоке регистров, данные с выхода которого поступают на вход последовательно соединенного блока формирования актуальных ключей, представляющий собой статическую комбинационную схему, интегрируемую в схему генерации блока замен SBOX, образуя единый блок в виде комбинационной схемы, выполненной с обеспечением возможности реализации применения преобразования Фробениуса в GF(2128) с формированием массива 128-битных актуальных ключей режима aKr, при этом выход блока формирования актуальных ключей последовательно соединен с блоком формирования SBOX, выполненным с обеспечением возможности программно-аппаратной реализации функции формирования SBOX на основе массива актуальных ключей режима.

9. Устройство по п. 7, отличающееся тем, что блок формирования SBOX выполнен с обеспечением возможности формирования различных таблиц замен, каждая из которых используется в очередном раунде.

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| СПОСОБ ПРИМЕНЕНИЯ КОНТРМЕР ПРОТИВ АТАК ПО СТОРОННИМ КАНАЛАМ | 2012 |

|

RU2586020C2 |

Авторы

Даты

2020-12-11—Публикация

2018-09-20—Подача