Область техники

Изобретение относится к области цифровых систем приема и обработки сигналов и предназначено для идентификации и компенсации инверсии входного битового потока при декодировании LDPC кодов.

Уровень техники

Задача идентификации и компенсации инверсии входного битового потока является актуальной для радиосистем связи и беспроводных систем передачи данных.

Причиной инверсии фазы принимаемого сигнала с фазовой или амплитудно-фазовой модуляцией могут являться, например, скачки фазы системы фазовой синхронизации, использующей схему Костаса, при когерентной демодуляции принимаемого сигнала и небольших отношениях сигнал-шум.

Наиболее эффективным способом борьбы с неконтролируемыми скачками фазы является использование относительных (дифференциальных) методов модуляции, например ΟΦΜ/DPSK.

Однако в некоторых случаях переход от фазовой модуляции к относительной (дифференциальной) фазовой модуляции невозможен.

В частности с такой ситуацией приходится сталкиваться при модернизации существующих систем связи.

Так при переходе к итеративным методам декодирования, например, LDPC кодов инверсия битового потока приводит к появлению большого пакета ошибок в кодовом слове, для исправления которых может не хватить корректирующей способности кода.

При этом все последующие кодовые слова до следующего перескока фазы будут инвертированы и также не могут быть правильно декодированы.

Кроме того, в этом случае декодер будет пытаться выполнить весь объем разрешенных итераций декодирования, что существенно увеличивает вычислительную нагрузку на систему.

В этом случае актуальной является задача идентификации факта инверсии битового потока и разработки методов ее компенсации.

Известны способы и устройства декодирования LDPC кодов, описанные, например, в патентах: US 7281192, US 7475103, US 8255758, US 8381079, US 8489957, US 8601352, US 8689092, US 2009/0070659, US 2009/0249159, US 2014/0089766 и др.

Кроме того, известны технические решения, обеспечивающие идентификацию инверсии входного битового потока: US 7701391, US 8255758, US 2011/0200059, ЕР 1324530, US 7221292, US 6563745, US 7549011 и др.

В патенте США US 7701391 описан способ кодирования и декодирования сигналов GPS с использованием LDPC кодов.

Устройство, реализующее заявленный способ, включает LDPC декодер, обнаружитель инверсии, буфер.

Однако в материалах патента не раскрывается техническая реализация блока обнаружитель инверсии (510).

В патенте США US 8255758 предлагается способ борьбы с инверсией ограниченного числа бит, основанный на инверсии определенного числа бит при отсутствии успешного декодирования за заданной число итераций.

Недостатком данного способа является необходимость выполнения большого числа итераций для обнаружения факта инверсии бит кодового слова.

В US 2011/0200059 описаны способ и устройство, обеспечивающие нахождение инвертированных бит в принятом и предыдущем пакетах данных с использованием индикатора инверсии.

Патент ЕР 1324530 содержит описание системы передачи данных, использующей инверсию бит и включающей блок определения инверсии и блок инверсии данных, а также другие блоки.

Однако для определения факта инверсии используется специализированный блок определения инверсии, что усложняет реализацию системы.

Система обнаружения инверсии бит данных описана в US 7221292 и основана на сравнении числа различающихся бит в двух соседних словах пакета данных.

Однако данное техническое решение основывается на конкретной структуре данных в пакетах и поэтому имеет ограниченное применение.

Наиболее близким к заявленному решению является патент US 2007/0118790, в котором описан способ и устройство для остановки итеративного декодирования в системах мобильной связи.

Способ включает в себя выполнение итеративного декодирования принимаемого сигнала и вычисление условия остановки декодирования.

А соответствующее устройство включает итеративный декодер и блоки, обеспечивающие вычисление условия остановки декодирования.

Однако данные способ и устройство не могут быть использованы в случае декодирования LDPC кодов.

Целью заявляемого решения является устранение недостатков известных технических решений.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Целью заявленного технического решения является повышение помехоустойчивости и эффективности использования вычислительных ресурсов систем связи путем идентификации и компенсации инверсии входного битового потока при декодировании LDPC кодов.

К области применения предложенных технических решений относятся цифровые системы радиосвязи, использующие сигналы с LDPC кодами.

Технический результат, получаемый от использования данного изобретения, заключается в повышении помехоустойчивости передачи информации, достигаемой за счет того, что уменьшается объем потерянных из-за инверсии данных.

Кроме того, снижается нагрузка на вычислительные средства за счет того, что для обнаружения факта инверсии не требуется выполнения всего допустимого количества итераций.

Заявленная цель достигается посредством анализа сходимости веса синдрома.

В случае когда в процессе декодирования фиксируется возрастание веса синдрома заданное количество раз, принимается решение об обнаружении факта инверсии битового потока.

После чего прекращается декодирование текущего кодового слова, из буферной памяти считывается и инвертируется следующее кодовое слово, которое передается в LDPC декодер для декодирования.

Известный способ включает в себя выполнение итеративного декодирования принимаемого сигнала и вычисление условия остановки декодирования.

Особенностью заявленного способа идентификации и компенсации инверсии входного битового потока при декодировании LDPC кодов является то, что

- с выхода демодулятора получают и записывают в буферную память кодовое слово LDPC кода,

- осуществляют декодирование LDPC кодового слова,

- в процессе декодирования для каждой итерации рассчитывают синдром,

- проводят анализ сходимости веса синдрома,

- на основании этого анализа формируют признак инверсии входного битового потока,

- в случае когда признак инверсии входного битового потока не свидетельствует об обнаружении инверсии, продолжают декодирование,

- в случае когда признак инверсии входного битового потока свидетельствует об обнаружении инверсии, осуществляют сброс LDPC декодера и параметров анализа сходимости веса синдрома,

- считывают из буферной памяти следующее кодовое слово,

- осуществляют инверсию этого кодового слова и передают его на вход LDPC декодера для осуществления следующей операции декодирования.

Кроме того, анализ сходимости веса синдрома осуществляют в следующем порядке:

- для каждой итерации декодирования от LDPC декодера получают вектор синдрома,

- вычисляют вес синдрома,

- сравнивают рассчитанный вес синдрома с весом, полученным для предыдущей итерации, и формируют признак увеличения веса синдрома,

- подсчитывают количество увеличений веса синдрома на заданном интервале времени (окне подсчета),

- сравнивают текущее количество увеличений веса синдрома с заданным пороговым уровнем,

- в случае превышения порогового уровня формируют признак инверсии входного битового потока, который используют для управления процессом декодирования.

Заявленный способ идентификации и компенсации инверсии входного битового потока при декодировании LDPC кодов технически может быть реализован в виде соответствующего устройства.

Известное устройство включает итеративный декодер и блоки, обеспечивающие вычисление условия остановки декодирования.

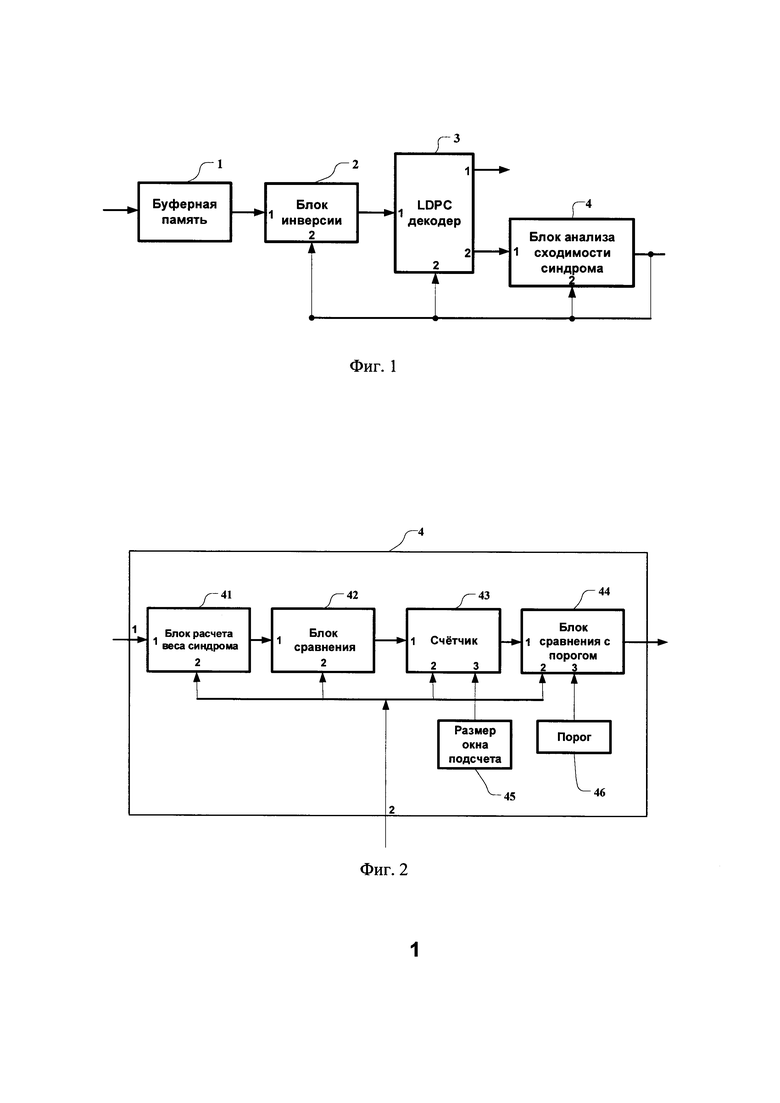

Заявленное устройство идентификации и компенсации инверсии входного битового потока при декодировании LDPC кодов содержит буферную память 1 и LDPC декодер 3, и в него введены блок инверсии 2 и блок анализа сходимости синдрома 4, причем вход буферной памяти 1 является входом устройства, выход буферной памяти 1 соединен с первым входом блока инверсии 2, выход которого соединен с первым входом LDPC декодера 3, первый выход которого является первым выходом устройства и с него снимаются декодированные информационные слова, второй выход LDPC декодера 3 соединен с первым входом блока анализа сходимости синдрома 4, выход которого является вторым выходом устройства и соединен со вторыми входами блока инверсии 2, LDPC декодера 3 и блока анализа сходимости синдрома 4.

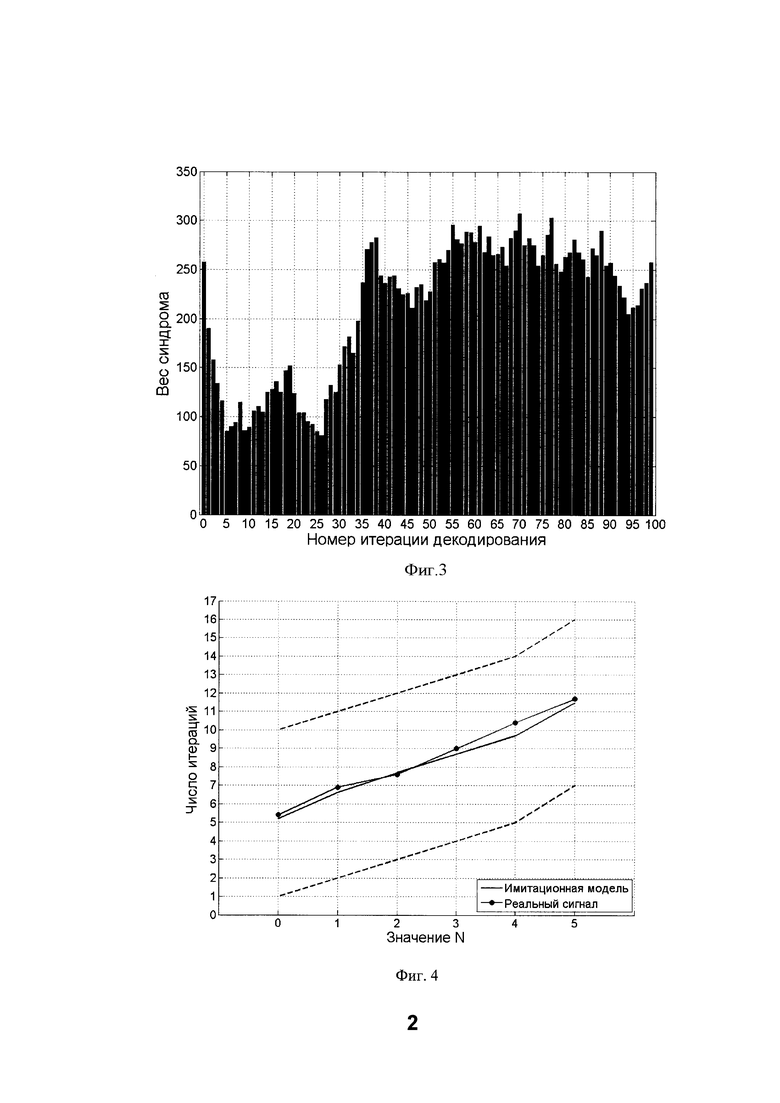

Вариантом реализации заявленного устройства является случай, когда блок анализа сходимости синдрома 4 выполнен в виде последовательно соединенных блока расчета веса синдрома 41, блока сравнения 42, счетчика 43 и блока сравнения с порогом 44, а также блока задания размера окна подсчета 45 и блока формирования порога 46, причем первый вход блока расчета веса синдрома 41 является первым входом блока анализа сходимости синдрома 4, а выход блока сравнения с порогом 44 является выходом блока анализа сходимости синдрома 4, вторые входы блока расчета веса синдрома 41, блока сравнения 42, счетчика 43 и блока сравнения с порогом 44 соединены со вторым входом блока анализа сходимости синдрома 4, выход блока задания размера окна подсчета 45 соединен с третьим входом счетчика 43, а выход блока формирования порога 46 соединен с третьим входом блока сравнения с порогом 33.

ПЕРЕЧЕНЬ ФИГУР

На Фиг. 1 приведена общая структурная схема заявленного устройства.

На Фиг. 2 приведена структурная схема варианта реализации блока анализа сходимости синдрома.

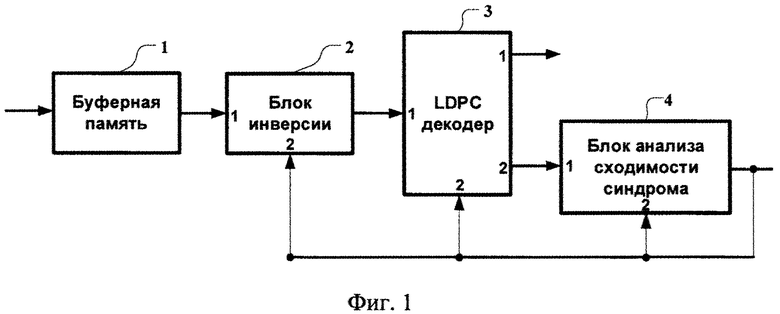

На Фиг. 3 приведен пример изменения веса синдрома при декодировании в зависимости от номера итерации и при наличии инверсии.

На Фиг. 4 приведена зависимость среднего числа итераций, необходимых для принятия решения об инверсии битового потока при использовании заявленного устройства, от N - величины порога.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Таким образом, сущность заявленного способа идентификации и компенсации инверсии входного битового потока при декодировании LDPC кодов заключается в выполнении следующих операций:

- с выхода демодулятора получают и записывают в буферную память кодовое слово LDPC кода,

- осуществляют декодирование LDPC кодового слова,

- в процессе декодирования для каждой итерации рассчитывают синдром,

- проводят анализ сходимости веса синдрома,

- на основании этого анализа формируют признак инверсии входного битового потока,

- в случае когда признак инверсии входного битового потока не свидетельствует об обнаружении инверсии, продолжают декодирование,

- в случае когда признак инверсии входного битового потока свидетельствует об обнаружении инверсии, осуществляют сброс LDPC декодера и параметров анализа сходимости веса синдрома,

- считывают из буферной памяти следующее кодовое слово,

- осуществляют инверсию этого кодового слова и передают его на вход LDPC декодера для осуществления следующей операции декодирования.

При этом анализ сходимости веса синдрома может осуществляться в следующем порядке:

- для каждой итерации декодирования от LDPC декодера получают вектор синдрома,

- вычисляют вес синдрома,

- сравнивают рассчитанный вес синдрома с весом, полученным для предыдущей итерации, и формируют признак увеличения веса синдрома,

- подсчитывают количество увеличений веса синдрома на заданном интервале времени (окне подсчета),

- сравнивают текущее количество увеличений веса синдрома с заданным пороговым уровнем,

- в случае превышения порогового уровня формируют признак инверсии входного битового потока, который используют для управления процессом декодирования.

Техническая реализация предложенного способа в виде устройства может быть осуществлена в соответствии со структурными схемами, представленными на Фиг. 1-2.

С выхода демодулятора для декодирования последовательно поступают LDPC кодовые слова с мягкими или жесткими решениями.

Эти кодовые слова (Фиг. 1) записываются в буферную память 1, из которой через блок инверсии 2 передаются для декодирования в LDPC декодер 3.

Блок инверсии 2 каждый раз после получения по второму входу управляющего сигнала, соответствующего обнаружению факта инверсии фазы во входном потоке, осуществляет изменение знака входных символов кодового слова.

После получения первого или нечетного числа управляющих сигналов знак символов выходного кодового слова меняется на противоположный по сравнению с входным кодовым словом.

После получения второго или четного числа управляющих сигналов знак выходных символов кодового слова по сравнению с входными не меняется.

Кодовое слово с выхода блока инверсии 2 поступает в LDPC декодер 3, где осуществляется его итерационное декодирование.

В процессе итерационного декодирования на каждой итерации декодер осуществляет вычисление текущего синдрома, который через второй выход LDPC декодера 3 подается на вход блока анализа сходимости синдрома 4.

После завершения процесса декодирования декодированное кодовое слово подается на первый выход LDPC декодера 3, который является первым выходом устройства.

В блоке анализа сходимости синдрома 4 (Фиг. 2) на основании полученного вектора синдрома в блоке расчета веса синдрома 41 осуществляется расчет текущего веса синдрома.

В блоке сравнения 42 проводится сравнение текущего значения веса синдрома с аналогичным значением на предыдущей итерации.

В случае когда текущее значение веса синдрома больше, чем на предыдущем шаге, блок сравнения 42 формирует выходной импульс.

Счетчик 43 подсчитывает количество таких импульсов в пределах окна, задаваемого блоком размер окна подсчета 45 и отсчитываемого от первого импульса в пачке, формируемой блоком сравнения 42.

В случае когда текущее время выходит за пределы окна подсчета, показания счетчика обнуляются и подсчет импульсов начинается заново.

Текущее значение счетчика 43 в блоке сравнения с порогом 44 сравнивается с пороговым значением, задаваемым блоком порога 46.

В случае превышения порога блок сравнения с порогом 44 формирует сигнал, соответствующий обнаружению инверсии битового потока.

Этот сигнал поступает на вторые входы блоков инверсии 2, LDPC декодера 3 и блока анализа сходимости синдрома 4, обеспечивая изменение режима работы блока инверсии 2, сброс LDPC декодера 3, сброс состояния блока расчета веса синдрома 41, блока сравнения 42, счетчика 43 и блока сравнения с порогом 44.

После чего система начинает декодирование следующего кодового слова из буферной памяти 1.

Выход блока сравнения с порогом 44 является выходом блока анализа сходимости синдрома 4 и вторым выходом устройства идентификации и компенсации инверсии входного битового потока при декодировании LDPC кодов.

Общая структурная схема устройства идентификации и компенсации инверсии входного битового потока при декодировании LDPC кодов представлена на Фиг. 1 и содержит буферную память 1, блок инверсии 2, LDPC декодер 3 и блок анализа сходимости синдрома 4, причем вход буферной памяти 1 является входом устройства, выход буферной памяти 1 соединен с первым входом блока инверсии 2, выход которого соединен с первым входом LDPC декодера 3, первый выход которого является первым выходом устройства и с него снимаются декодированные информационные слова, второй выход LDPC декодера 3 соединен с первым входом блока анализа сходимости синдрома 4, выход которого является вторым выходом устройства и соединен со вторыми входами блока инверсии 2, LDPC декодера 3 и блока анализа сходимости синдрома 4.

Блок анализа сходимости синдрома 4 выполнен в виде последовательно соединенных (Фиг. 2) блока расчета веса синдрома 41, блока сравнения 42, счетчика 43 и блока сравнения с порогом 44, а также блока задания размера окна подсчета 45 и блока формирования порога 46, причем первый вход блока расчета веса синдрома 41 является первым входом блока анализа сходимости синдрома 4, а выход блока сравнения с порогом 44 является выходом блока анализа сходимости синдрома 4, вторые входы блока расчета веса синдрома 41, блока сравнения 42, счетчика 43 и блока сравнения с порогом 44 соединены со вторым входом блока анализа сходимости синдрома 4, выход блока задания размера окна подсчета 45 соединен с третьим входом счетчика 43, а выход блока формирования порога 46 соединен с третьим входом блока сравнения с порогом 33.

Работоспособность предложенных технических решений подтверждается результатами моделирования.

На Фиг. 3 приведен пример изменения веса синдрома в зависимости от номера итерации при наличии инверсии.

Максимальное число итераций ограничено значением 100.

Видно, что сходимость синдрома отсутствует, но этот факт будет обнаружен только после 100 итераций.

На Фиг. 4 приведена зависимость среднего числа итераций, необходимых для принятия решения об инверсии битового потока при использовании заявленного устройства, в зависимости от N - величины порога в блоке сравнения с порогом 44, при подсчете числа превышений с бесконечным окном подсчета.

Видно, что решение принимается существенно более оперативно и выигрыш по числу итераций составляет в среднем до 10 раз.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ВОССТАНОВЛЕНИЯ ЦИФРОВОЙ ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ В УСЛОВИЯХ ВОЗМОЖНОЙ ИНВЕРСИИ СИГНАЛА | 2023 |

|

RU2799892C1 |

| СПОСОБ ДЕКОДИРОВАНИЯ LDPC-КОДОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2017 |

|

RU2651222C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ТЕКУЩЕГО ОТНОШЕНИЯ СИГНАЛ/ШУМ ПРИ ДЕКОДИРОВАНИИ LDPC-КОДОВ (ВАРИАНТЫ) | 2013 |

|

RU2573243C2 |

| ДЕКОДИРОВАНИЕ ВЫСОКОИЗБЫТОЧНЫХ КОДОВ С КОНТРОЛЕМ ЧЕТНОСТИ С ИСПОЛЬЗОВАНИЕМ МНОГОПОРОГОВОГО ПРОХОЖДЕНИЯ СООБЩЕНИЯ | 2004 |

|

RU2337478C2 |

| СПОСОБ И УСТРОЙСТВО ПОМЕХОУСТОЙЧИВОГО ДЕКОДИРОВАНИЯ СИГНАЛОВ, ПОЛУЧЕННЫХ С ИСПОЛЬЗОВАНИЕМ КОДА ПРОВЕРКИ НА ЧЕТНОСТЬ С НИЗКОЙ ПЛОТНОСТЬЮ | 2013 |

|

RU2522299C1 |

| Способ декодирования LDPC-кодов и устройство для его осуществления | 2016 |

|

RU2628459C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ LDPC-КОДОВ | 2013 |

|

RU2549134C1 |

| СПОСОБЫ И УСТРОЙСТВО LDPC-ДЕКОДИРОВАНИЯ | 2005 |

|

RU2392737C2 |

| СПОСОБ ДЕКОДИРОВАНИЯ LDPC-КОДОВ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 2014 |

|

RU2575399C1 |

| Способ декодирования данных на основе LDPC кода | 2020 |

|

RU2747050C1 |

Группа изобретений относится к области кодирования и может быть использована в системах приема и обработки сигналов. Техническим результатом является повышение помехоустойчивости передачи информации. Устройство содержит буферную память, блок инверсии, LDPC декодер, блок анализа сходимости синдрома. 2 н. и 2 з.п. ф-лы, 4 ил.

1. Способ идентификации и компенсации инверсии входного битового потока при декодировании LDPC кодов, при котором:

- с выхода демодулятора получают и записывают в буферную память кодовое слово LDPC кода,

- осуществляют декодирование LDPC кодового слова,

отличающийся тем, что

- в процессе декодирования для каждой итерации рассчитывают синдром,

- проводят анализ сходимости веса синдрома,

- на основании этого анализа формируют признак инверсии входного битового потока,

- в случае когда признак инверсии входного битового потока не свидетельствует об обнаружении инверсии, продолжают декодирование,

- в случае когда признак инверсии входного битового потока свидетельствует об обнаружении инверсии, осуществляют сброс LDPC декодера и параметров анализа сходимости веса синдрома,

- считывают из буферной памяти следующее кодовое слово,

- осуществляют инверсию этого кодового слова и передают его на вход LDPC декодера для осуществления следующей операции декодирования.

2. Способ по п. 1, отличающийся тем, что анализ сходимости веса синдрома осуществляют в следующем порядке:

- для каждой итерации декодирования от LDPC декодера получают вектор синдрома,

- вычисляют вес синдрома,

- сравнивают рассчитанный вес синдрома с весом, полученным для предыдущей итерации, и формируют признак увеличения веса синдрома,

- подсчитывают количество увеличений веса синдрома на заданном интервале времени (окне подсчета),

- сравнивают текущее количество увеличений веса синдрома с заданным пороговым уровнем,

- в случае превышения порогового уровня формируют признак инверсии входного битового потока, который используют для управления процессом декодирования.

3. Устройство идентификации и компенсации инверсии входного битового потока при декодировании LDPC кодов, содержащее буферную память 1 и LDPC декодер 3, отличающееся тем, что дополнительно введены блок инверсии 2 и блок анализа сходимости синдрома 4, причем вход буферной памяти 1 является входом устройства, выход буферной памяти 1 соединен с первым входом блока инверсии 2, выход которого соединен с первым входом LDPC декодера 3, первый выход которого является первым выходом устройства и с него снимаются декодированные информационные слова, второй выход LDPC декодера 3 соединен с первым входом блока анализа сходимости синдрома 4, выход которого является вторым выходом устройства и соединен со вторыми входами блока инверсии 2, LDPC декодера 3 и блока анализа сходимости синдрома 4.

4. Устройство по п. 3, отличающееся тем, что блок анализа сходимости синдрома 4 выполнен в виде последовательно соединенных блока расчета веса синдрома 41, блока сравнения 42, счетчика 43 и блока сравнения с порогом 44, а также блока задания размера окна подсчета 45 и блока формирования порога 46, причем первый вход блока расчета веса синдрома 41 является первым входом блока анализа сходимости синдрома 4, а выход блока сравнения с порогом 44 является выходом блока анализа сходимости синдрома 4, вторые входы блока расчета веса синдрома 41, блока сравнения 42, счетчика 43 и блока сравнения с порогом 44 соединены со вторым входом блока анализа сходимости синдрома 4, выход блока задания размера окна подсчета 45 соединен с третьим входом счетчика 43, а выход блока формирования порога 46 соединен с третьим входом блока сравнения с порогом 33.

| US 2007118790 A1, 24.05.2007 | |||

| US 8935601 B1, 13.01.2015 | |||

| US 2009187803 A1, 23.07.2009 | |||

| US 2006261919 A1, 23.11.2006 | |||

| ДЕКОДЕР С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК | 2008 |

|

RU2370887C1 |

Авторы

Даты

2017-01-11—Публикация

2015-03-25—Подача