Сбоеустойчивое запоминающее устройство относится к вычислительной технике и может быть использовано для повышения достоверности функционирования работы, устройств хранения и передачи информации.

Известно устройство памяти с контролем на четность [1], содержащее узел памяти, входной блок формирования дополнительного разряда проверки на четность, выходной блок формирования дополнительного разряда проверки на четность, элемент неравнозначности, информационные входы устройства подключены к узлу памяти и к входам входного блока формирования дополнительного разряда проверки на четность, выходы узла памяти являются информационными выходами устройства и подключены к входам выходного блока формирования дополнительного разряда проверки на четность, выход которого подключен к первому входу элемента неравнозначности, второй вход элемента неравнозначности соединен с выходом входного блок формирования дополнительного разряда проверки на четность, и с его выхода снимается сигнал при возникновении ошибки.

Недостатком устройства является низкая достоверность функционирования устройства, так как обнаруживаются только одиночные (нечетные) ошибки, т.е. обнаруживается 50% возможных ошибок.

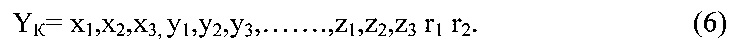

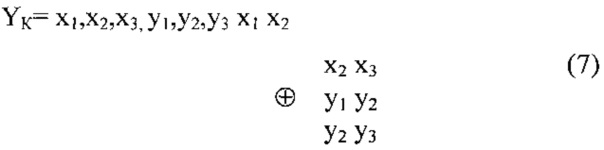

Наиболее близким по техническому решению является устройство хранения и передачи информации с обнаружением двойных ошибок [2], содержащее узел памяти, входной блок кодирования, формирующий значения контрольных разрядов r1 и r2 путем сложения по модулю 2 информационных символов x1, x2, x3, y1, y2, y3, поступающих на входы входного блока кодирования, в соответствии с правилом: r1=х1⊕х2⊕y1⊕y2; r2=х2⊕х3⊕y2⊕y3, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1П, r2П путем сложения по модулю 2 информационных символов x1C, x2C, x3C, y1C, y2C, y3C, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом: r1П=х1C⊕x2C⊕y1C⊕y2C; r2П=x2C⊕x3C⊕y2C⊕y3C, блок выявления ошибки, первый блок элементов ИЛИ, первый блок элементов И, элемент И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки.

Недостатком устройства является его низкая сбоеустойчивость, так как отсутствует возможность выявления перемежающихся ошибок типа "сбой".

Целью изобретения является обеспечение сбоеустойчивости устройства за счет различения перемежающихся и константных ошибок.

Поставленная цель достигается тем, что устройство, содержащее узел памяти, входной блок кодирования, формирующий значения контрольных разрядов r1 и r2 путем сложения по модулю 2 информационных символов x1, x2, x3, y1, y2, y3, поступающих на входы входного блока кодирования, в соответствии с правилом: r1=х1⊕х2⊕y1⊕y2; r2=х2⊕х3⊕y2⊕y3, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1П, r2П путем сложения по модулю 2 информационных символов x1C, х2C, x3C, y1C, y2C, y3C, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом: r1П=x1C⊕x2C⊕y1C⊕y2C; r2П=х2C⊕x3C⊕y2C⊕y3C, блок выявления ошибки, первый элемент ИЛИ, блок элементов И, первый элемент И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки, дополнительно содержит второй элемент ИЛИ, второй элемент И, первый триггер, второй триггер, элемент НЕ, элемент задержки, транспарант "Отказ устройства", выход "Повторное считывание", причем вход установки в нулевое состояние, вход записи, вход считывания, адресные входы подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, информационные входы подключены к пятым входам узла памяти и к входам входного блока кодирования, выходы которого подключены к шестым входам узла памяти, вход синхронизации подключен к седьмому входу узла памяти, к первому входу блока элементов И и к первому входу первого элемента И, первые выходы узла памяти подключены ко вторым входам блока элементов И и к входам выходного блока кодирования, выходы которого подключены к первым входам блока выявления ошибки, вторые входы блока выявления ошибки подключены ко вторым выходам узла памяти, выходы блока выявления ошибки подключены к входам первого элемента ИЛИ, выход которого подключен ко второму входу первого элемента И, выход первого элемента И подключен к единичному входу первого триггера, к первому входу второго элемента И и через элемент НЕ к третьему входу блока элементов И, единичный выход первого триггера подключен ко второму входу второго элемента И, через элемент задержки подключен к первому входу второго элемента ИЛИ и является выходом "Повторное считывание", выход второго элемента И подключен к единичному входу второго триггера, вход установки устройства в нулевое состояние подключен к нулевому входу второго триггера и ко второму входу второго элемента ИЛИ, выход которого подключен к нулевому входу первого триггера, единичный выход второго триггера является выходом "Отказ устройства" и подключен к транспаранту.

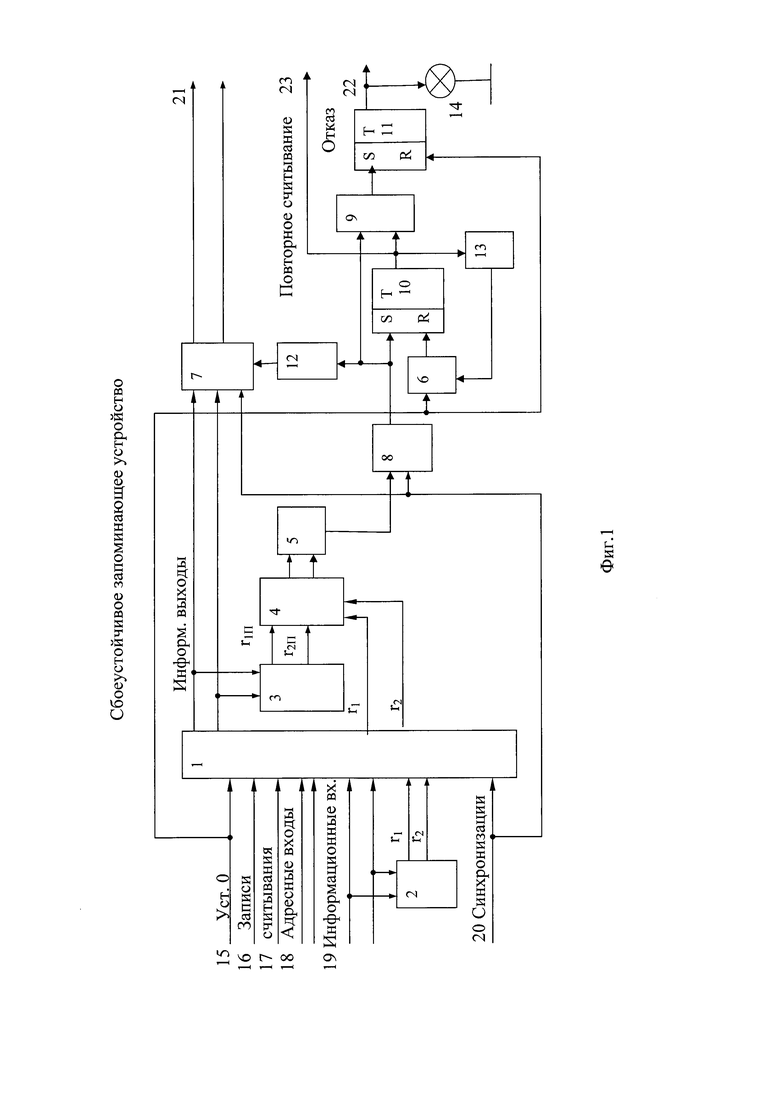

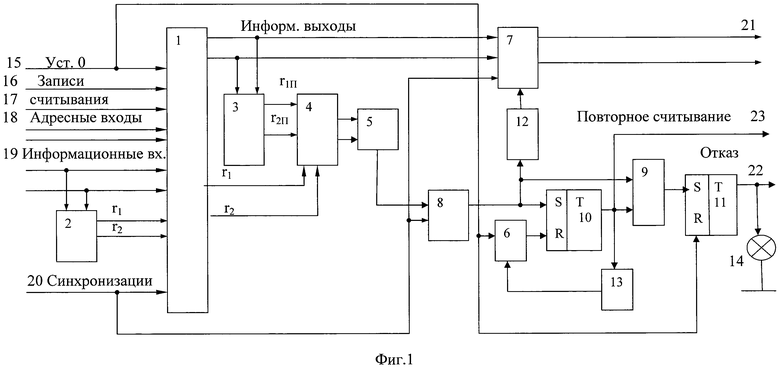

На фиг. 1 представлена блок-схема устройства. Сбоеусточивое запоминающее устройство содержит: узел 1 памяти, входной блок 2 кодирования, выходной блок 3 кодирования, блок 4 выявления ошибки, первый элемент 5 ИЛИ, второй элемент 6 ИЛИ, блок 7 элементов И, первый элемент 8 И, второй элемент 9 И, первый триггер 10, второй триггер 11, элемент 12 НЕ, элемент 13 задержки, транспарант 14 "Отказ устройства", вход 15 установки в нулевое состояние, вход 16 записи, вход 17 считывания, адресные входы 18, информационные входы 19, вход 20 синхронизации, информационные выходы 21, выход 22 "Отказ устройства", выход 23 "Повторное считывание".

Вход 15 установки в нулевое состояние, вход 16 записи, вход 17 считывания, адресные входы 18 подключены соответственно к первому, второму, третьему и четвертому входам узла 1 памяти, информационные входы 19 подключены к пятым входам узла 1 памяти и к входам входного блока 2 кодирования, выходы которого подключены к шестым входам узла 1 памяти, вход 20 синхронизации подключен к седьмому входу узла 1 памяти, к первому входу блока 7элементов И и к первому входу первого элемента 8 И, первые выходы узла 1 памяти подключены ко вторым входам блока 7 элементов И и к входам выходного блока 3 кодирования, выходы которого подключены к первым входам блока 4 выявления ошибки, вторые входы блока выявления ошибки подключены ко вторым выходам узла 1 памяти, выходы блока 4 выявления ошибки подключены к входам первого элемента 5 ИЛИ, выход которого подключен ко второму входу первого элемента 8 И, выход первого элемента 8 И подключен к единичному входу первого триггера 10, к первому входу второго элемента 9 И и через элемент 12 НЕ к третьему входу блока 7 элементов И, единичный выход первого триггера 10 подключен ко второму входу второго элемента 9 И, через элемент 13 задержки подключен к первому входу второго элемента 6 ИЛИ и является выходом "Повторное считывание", выход второго элемента 9 И подключен к единичному входу второго триггера 11, вход 15 установки устройства в нулевое состояние подключен к нулевому входу второго триггера 11 и ко второму входу второго элемента 6 ИЛИ, выход которого подключен к нулевому входу первого триггера 10, единичный выход второго триггера является выходом 22 "Отказ устройства" и подключен к транспаранту 14.

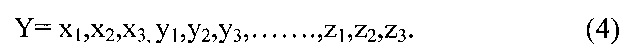

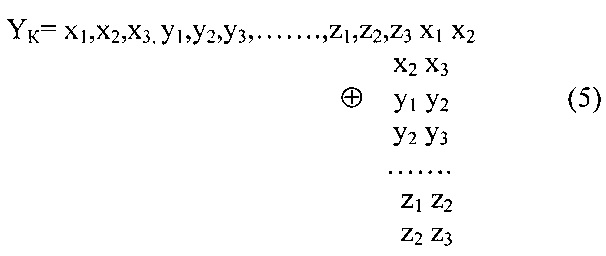

Узел 1 памяти, в данном случае, представляет собой статическое полупроводниковое оперативное устройство памяти и предназначен для хранения кодовых наборов: УК=x1x2x3y1y2y3r1r2, полученных при кодировании исходных двоичных наборов: У=x1, x2, x3, y1, y2, y3.

Входной блок 2 кодирования предназначен для формирования значений контрольных разрядов r1, r2 путем сложения по mod2 информационных символов в соответствии с правилом:

r1=x1⊕x2⊕y1⊕y2;

r2=х2⊕х3⊕y2⊕y3.

Выходной блок 3 кодирования предназначен для формирования значений проверочных контрольных разрядов r1П, r2П путем сложения по mod2 информационных символов (xiC, yiC), полученных при считывании информации с узла 1 памяти в соответствии с правилом:

r1П=x1С⊕x2С⊕y1C⊕y2C;

r2П=х2C⊕x3C⊕y2C⊕y3C.

Блок 4 выявления ошибки предназначен для обнаружения ошибки в кодовом наборе при считывании информации с узла 1 памяти путем сложения по mod2 значений контрольных разрядов r1C и r2С, считываемых с вторых выходов узла 1 памяти, соответственно с значениями контрольных разрядов r1П и r2П, сформированных на выходах выходного блока 3 кодирования:

λ1=r1C⊕r1П;

λ2=r2C⊕r2П.

Нулевой результат суммы свидетельствует об отсутствии ошибки и ее наличии в противном случае.

Выходы λ1 и λ2 блока 3 сравнение объединены в один выход первым элементом 5 ИЛИ, значение сигнала на данном выходе поступает на второй вход первого элемента 8 И.

Считывание выходной информации с выходов 21 устройства проводится при поступлении сигнала с входа 20 синхронизации на первые входы блока 7 элементов И и первого элемента 8 И.

Устройство работает следующим образом. Перед началом работы устройства на вход 15 "Установки в нулевое состояние" подается единичный сигнал, который переводит устройство и триггеры 10, 11 в нулевое состояние.

При записи информации в узел 1 памяти подается единичный сигнал на вход 16 записи, адресные входы 18 и информационные входы 19.

Например, на информационные входы поступает кодовая комбинация: x1x2x3 y1y2y3, соответствующая значению -000110

В этом случае входной блок 2 кодирования формирует вектор:

r1=x1⊕x2⊕y1⊕y2=0; r2=x2⊕x3⊕y2⊕y3=1.

Соответственно в узел 1 памяти запишется информация:

00011001.

При считывании информации на вход 17 считывания и адресные входы 18 подаются сигналы, разрешающие считывание информации с узла 1 памяти по указанному адресу. Считываемая информация подается на вторые входы блока 7 элементов И и входы выходного блока 3 кодирования информации. Выходной блок 3 кодирования относительно информационных разрядов формирует значения: r1П=0 и r2П=1, которые при отсутствии ошибки равны соответственно значениям r1С и r2C, поэтому на выходе блока 4 выявления ошибки имеем значения: λ1=0, λ2=0.

Допустим, произошла ошибка в первом информационном разряде: 1* 00 110 01. В этом случае на выходах выходного блока 3 кодирования получим значения сигналов: r1П=1 и r2П=1. Так как значение r1П≠r1С (1≠0), то на выходе блока 4 выявления ошибки получим значения сигналов: λ1=1, λ2=0, соответственно на выходе первого 5 ИЛИ появится единичное значение сигнала, которое при поступлении сигнала с входа 20 синхронизации поступит на выход первого элемента 8 И.

Сигнал с выхода первого элемента 8 И через элемент 12 НЕ закрывает блок 7 элементов И (запрещает выдачу информации) и переводит в единичное состояние первый триггер 10. Значение сигнала, снимаемого с единичного выхода первого триггера 10, поступает в устройство управления для организации повторного считывания информации.

Если возникла перемежающаяся ошибка, то через время, необходимое для повторного считывания информации (определяемое элементом 13 задержки), первый триггер 10 переводится в нулевое состояние и разрешается считывание информации.

Если при повторном считывании появляется единичное значение сигнала на выходе первого элемента 8 И, то это свидетельствует о наличии константной ошибки. В этом случае открывается второй элемент 9 И и переводится в единичное состояние второй триггер 11. С единичного выхода второго триггера 11 снимается сигнал "Отказ устройства" и обеспечивается загорание соответствующего транспаранта.

Аналогичным образом устройство работает при появлении других ошибок.

Таким образом, предлагаемое устройство позволяет обеспечит сбоеустойчивость устройства памяти и выявлять константные ошибки.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Б.М. Коган, И.Б. Мкртумян Основы эксплуатации ЭВМ. – М.: Энергоатом издат., 1988, 430 с, рис. 4.17.

2. Патент на изобретение №2403615 "Устройство хранения и передачи информации с обнаружением двойных ошибок" / Павлов А.А., Царьков А.Н. и др. от 27.01.2009 г.

Приложение

Эффективность автоматизированных систем управления, информационных комплексов, средств вычислительной и измерительной техники, устройств хранения и передачи информации в значительной степени определяется достоверностью информации, которая обрабатывается в данных системах [1].

В свою очередь, достоверность функционирования цифровых устройств существенно зависит от выбранного метода обнаружения ошибок (обнаруживающей способности выбранного метода контроля информации и аппаратурных затрат, необходимых для реализации данного метода). В настоящее время для этой цели наиболее широко используется метод контроля на четность, который требует минимальных аппаратурных затрат для обнаружения ошибок двоичного набора. Недостатком данного метода является низкая обнаруживающая способность, так как обнаруживаются только нечетные ошибки. В то же время опыт эксплуатации дискретных устройств показывает, что наиболее вероятным событием является возникновение одиночных и двойных ошибок (соответственно на одиночные ошибки приходится 80-85%, на двойные ошибки 25-20% и ошибки прочей кратности до 2%) [1], т.е. основным недостатком метода контроля на четность является невозможность обнаружения двойных ошибок.

Гораздо большую обнаруживающую способность имеет метод контроля информации по mod3, однако реализация данного метода требует больших аппаратурных затрат на построение схем сверток и временных затрат, связанных с задержкой прохождения сигнала.

В связи с этим возникает необходимость в разработке метода контроля информации, обнаруживающего 100% одиночных ошибок и максимального количества двойных ошибок, при минимальных аппаратурных и временных затратах на декодирование.

Обоснование метода кодирования информации

Пусть исходный двоичный набор представлен тремя информационными разрядами:

Для обнаружения ошибок заданной кратности необходимо обеспечить выполнение условия для кодового расстояния d [1]:

где t - число ошибочных разрядов в кодовом наборе.

Для обнаружения двойной ошибки необходимо обеспечить кодовое расстояние d≥3, соответственно для этой цели необходимо использовать два контрольных разряда.

Так как достоверность функционирования и скорость обработки контролируемой информации существенно зависит от аппаратурных затрат, связанных с формированием значений контрольных разрядов, то возникает необходимость выбора метода кодирования информации, обеспечивающего минимальные аппаратурные затраты.

В связи с тем, что контроль на четность, по отношению к известным методам обнаружения ошибок, требует минимальных временных и аппаратурных затрат, то для обнаружения двойных ошибок целесообразно использовать метод кодирования информации, требующий для своей реализации аппаратурных и временных затрат, соизмеримых с затратами, необходимыми при использовании метода контроля на четность.

Проведенные для этой цели исследования показали, что для поставленной задачи целесообразно использовать независимые ортогональные проверки. Так, для трехразрядного двоичного набора Y=x1, х2, x3 формирование значений двух контрольных разрядов можно осуществить двумя проверками: r1=x1⊕x2 и r2=x2⊕x3.

Соответственно кодовый набор представляется в виде:

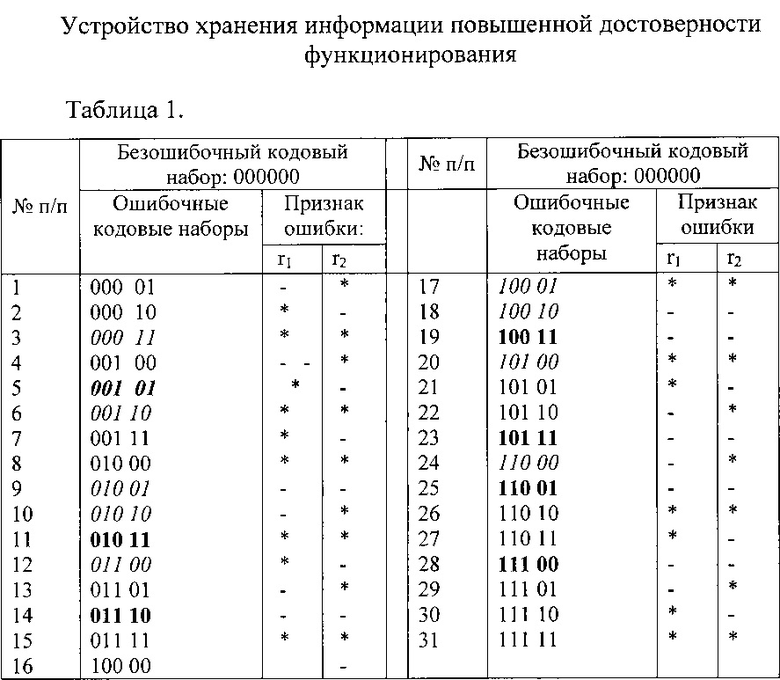

В Табл. 1 представлена обнаруживающая способность полученного кода относительно безошибочного кодового набора: YК=000 00.

Примечание: Символом "*" обозначен признак обнаруживаемой ошибки в соответствующем контрольном разряде, символом "-" - не обнаруживаемой; жирным шрифтом выделены не обнаруживаемые ошибки; наклонным шрифтом представлены двойные ошибки.

Анализ Табл. 1, показывает, что из тридцати одного ошибочного кодового набора не обнаруживается семь ошибочных наборов, при этом обнаруживается 100% одиночных ошибок, а из десяти двукратных ошибок не обнаруживается одна ошибка.

Если учесть, что 80% ошибок приходится на одиночную ошибку, а ≈20% - на двойную, то предлагаемый метод кодирования позволяет существенно повысить вероятность обнаружения возникающих ошибок.

Для кодирования трехразрядной информации предлагаемым методом потребуется два сумматора по mod2, т.е. такое же количество сумматоров, как и для контроля на четность.

Для декодирования информации (сравнения значений контрольных разрядов переданной и полученной информации) для предлагаемого метода, по отношению к контролю на четность потребуется на один сумматор больше, при этом скорость обработки информации не только не снижается, но и уменьшается, т.к. на пути прохождения сигналов, при кодировании и декодировании информации предлагаемым методом, находится по одному сумматору (при контроле на четность по два).

При кодировании двоичного набора с произвольным числом информационных разрядов (пусть число информационных разрядов кратно трем) разобьем двоичный набор на блоки информации, по три разряда в каждом блоке:

В результате кодирования рассматриваемого двоичного набора предлагаемым методом получим кодовый набор:

или:

Пример: Пусть число информационных разрядов равно шести, тогда для рассматриваемого числа информационных разрядов имеем кодовый набор:

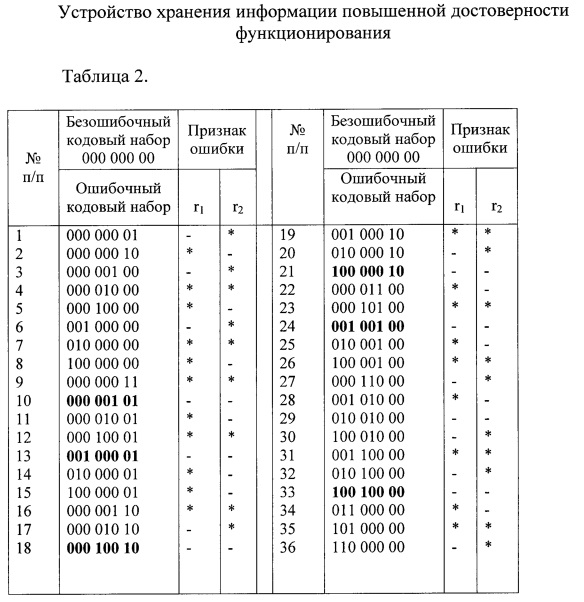

В табл. 2. представлены ошибочные кодовые наборы для одиночных и двойных ошибок относительно безошибочного кодового набора: 000000 00.

Анализ Табл. 2 показывает, что одиночные ошибки обнаруживаются 100%, из двадцати шести двойных ошибок не обнаруживаются шесть. На кодирование двоичного набора предлагаемым методом потребуется шесть сумматоров по mod2 (при контроле по методу четности - пять сумматоров по mod2). На декодирование кодового набора для предлагаемого метода потребуется восемь сумматоров по mod2 (при контроле на четность шесть сумматоров по mod2).

Общие аппаратурные затраты для предлагаемого метода кодирования составят четырнадцать сумматоров по mod2, а для контроля на четность - одиннадцать сумматоров по mod2.

В этом случае для предлагаемого метода при декодировании информации на пути прохождения сигнала находится четыре сумматора по mod2 (формирование значений двух контрольных разрядов осуществляется параллельно), а для контроля на четность - шесть сумматоров по mod2.

Следует отметить, что вероятность возникновения перемежающихся ошибок типа "сбой" на порядок выше, чем константных ошибок. Для различения перемежающихся и константных ошибок в предлагаемом устройстве организовано повторное считывание информации при возникновении ошибки. Если ошибка повторяется при повторном считывании, то это свидетельствует о наличии константной ошибки и перемежающейся в противном случае.

Таким образом, в предлагаемом устройстве хранения информации обнаруживаются все одиночные ошибки и максимальное количество двойных ошибок при незначительном увеличении аппаратурных затрат и обеспечено выявление перемежающихся ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ОДИНОЧНЫХ И ДВОЙНЫХ ОШИБОК | 2011 |

|

RU2450332C1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2421786C1 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2579954C2 |

| КОНТРОЛИРУЕМОЕ УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ | 2015 |

|

RU2618388C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2422923C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2009 |

|

RU2403615C2 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ОШИБОК | 2016 |

|

RU2621284C1 |

| РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК В ДУБЛИРУЕМЫХ КАНАЛАХ | 2022 |

|

RU2826990C2 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ ОШИБОК | 2016 |

|

RU2637426C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ПРОИЗВОЛЬНЫХ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2450331C1 |

Изобретение относится к вычислительной технике и может быть использовано для повышения достоверности функционирования работы, устройств хранения и передачи информации. Технический результат заключается в обеспечении сбоеустойчивости за счет различения перемежающихся и константных ошибок. Технический результат достигается за счет кодирования исходной двоичной информации на основе организации независимых проверок и за счет введения входного блока кодирования, выходного блока кодирования, блока выявления ошибки, первого элемента ИЛИ, второго элемента ИЛИ, блока элементов И, первого элемента И, второго элемента И, первого триггера, второго триггера, элемента НЕ, элемента задержки, транспаранта "Отказ устройства". 1 ил., 2 табл.

Сбоеустойчивое запоминающее устройство, содержащее узел памяти, входной блок кодирования, формирующий значения контрольных разрядов r1 и r2 путем сложения по модулю 2 информационных символов x1, x2, x3, y1, y2, y3, поступающих на входы входного блока кодирования, в соответствии с правилом: r1=x1⊕х2⊕y1⊕y2; r2=х2⊕х3⊕y2⊕y3, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1П, r2П путем сложения по модулю 2 информационных символов x1C, x2C, x3C, y1C, y2C, y3C, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом: r1П=x1C⊕x2C⊕y1C⊕y2C; r2П=x2C⊕x3C⊕y2C⊕y3C, блок выявления ошибки, первый элемент ИЛИ, блок элементов И, первый элемент И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки, вход установки в нулевое состояние, вход записи, вход считывания, адресные входы подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, информационные входы подключены к пятым входам узла памяти и к входам входного блока кодирования, выходы которого подключены к шестым входам узла памяти, вход синхронизации подключен к седьмому входу узла памяти, к первому входу блока элементов И и к первому входу первого элемента И, первые выходы узла памяти подключены к вторым входам блока элементов И и к входам выходного блока кодирования, выходы которого подключены к первым входам блока выявления ошибки, вторые входы блока выявления ошибки подключены к вторым выходам узла памяти, выходы блока выявления ошибки подключены к входам первого элемента ИЛИ, выход которого подключен ко второму входу первого элемента И, выходы блока элементов И являются информационными выходами устройства, отличающееся тем, что дополнительно содержит второй элемент ИЛИ, второй элемент И, первый триггер, второй триггер, элемент НЕ, элемент задержки, транспарант "Отказ устройства", выход "Повторное считывание", причем выход первого элемента И подключен к единичному входу первого триггера, к первому входу второго элемента И и через элемент НЕ к третьему входу блока элементов И, единичный выход первого триггера подключен ко второму входу второго элемента И, через элемент задержки подключен к первому входу второго элемента ИЛИ и является выходом "Повторное считывание", выход второго элемента И подключен к единичному входу второго триггера, вход установки устройства в нулевое состояние подключен к нулевому входу второго триггера и к второму входу второго элемента ИЛИ, выход которого подключен к нулевому входу первого триггера, единичный выход второго триггера является выходом "Отказ устройства" и подключен к транспаранту.

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2009 |

|

RU2403615C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| US 9052942 B1, 09.06.2015 | |||

| US 5048022 A, 10.09.1991. | |||

Авторы

Даты

2017-02-08—Публикация

2015-10-22—Подача