Резервированное запоминающее устройство с коррекцией ошибок в дублируемых каналах относится к вычислительной технике, цифровым системам передачи данных и может быть использовано для повышения их отказоустойчивости.

Известно устройство хранения и передачи информации с обнаружением двойных ошибок (Патент на изобретение №2403615 от 27.01. 2009 г.), содержащее узел памяти, входной блок кодирования, выходной блок кодирования, блок выявления ошибки, блок элементов И, элемент И, элемент ИЛИ, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала «ошибка», причем входной блок кодирования формирует значения контрольных разрядов r1 и r2 путем сложения по модулю 2 информационных символов x1, х2, х3 и y1, у2, у3, поступающих на входы входного блока кодирования, в соответствии с правилом: r1=x1 ⊕ х2 ⊕ у1, и ⊕y2; r2=х2 ⊕ х3 ⊕ у2 ⊕ у3, выходной блок кодирования формирует значения проверочных контрольных разрядов r1c и r2c путем сложения по модулю информационных символов x1c, х2с, х3с и у1с, у2с, y3c, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом: r1c=х1с ⊕ х2с ⊕ y1c, ⊕y2c; rc2=х2с ⊕ х3с ⊕ у2с ⊕ у3с, вход установки в нулевое состояние, вход записи, вход считывания, адресные входы подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, информационные символы поступают на пятые входы узла памяти совместно с контрольными символами, полученными из информационных символов с помощью входного блока кодирования, вход синхронизации подключен к шестому входу узла памяти и к первым входам блока элементов И и элемента И, информационные символы с информационных выходов узла памяти поступают на вторые входы блока элементов И и на входы выходного блока кодирования, выходные символы выходного блока кодирования поступают на первые входы блока выявления ошибки, на вторые входы которого поступают контрольные символы с информационных выходов узла памяти, выходы блока выявления ошибки подключены к входам элемента ИЛИ, выход элемента ИЛИ подключен к второму входу элемента И, выходы блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала «ошибка».

Недостатком устройства является недостаточная его отказоустойчивость, так как не корректируются возникающие ошибки.

Наиболее близким по техническому решению является резервированное запоминающее устройство (Авторское свидетельство СССР №1080217 от 15.03.1984 г.), содержащее основные блоки памяти, выходы которых подключены к одним из входов коммутаторов и одним из входов элементов И первой группы, выходы которых подключены к одним из входов сумматора по модулю два, другой вход которого соединен с выходом резервного блока памяти, а выход с другими входами коммутаторов и первым входом формирователя сигнала неисправности, второй вход которого и первые входы элементов И второй группы подключены к выходу генератора тактовых импульсов, причем выходы коммутаторов соединены с вторыми входами элементов И второй группы, выходы которых являются информационными выходами устройства, введены дополнительный блок памяти и первый дешифратор, вход которого подключен к выходу дополнительного блока памяти, а одни из выходов соединены с другими входами элементов И первой группы и управляющими входами коммутаторов, причем другой выход первого дешифратора подключен к третьему входу формирователя сигнала неисправности, выход которого является контрольным выходом устройства.

Недостатком устройства являются большие аппаратурные затраты на средства обнаружения ошибок, возникающих в основном и резервном блоках памяти.

Задачей изобретения является сокращение аппаратурных затрат на средства контроля, обнаруживающих одиночные и двойные ошибки, возникающие в основном и резервном блоках памяти, которые являются наиболее вероятными при эксплуатации данных устройств.

Сущность изобретения заключается в том, что устройство, содержащее основной блок памяти, резервный блок памяти, формирователь сигнала неисправности, блок сумматоров по модулю два, отличающееся тем, что он дополнительно содержит первый кодирующий блок, второй кодирующий блок, третий кодирующий блок, четвертый кодирующий блок, второй формирователь сигнала неисправности, первый корректор, второй корректор, первый элемент ИЛИ, второй элемент ИЛИ, первый блок элементов И, второй блок элементов И, третий блок элементов И, четвертый блок элементов И, пятый блок элементов И, первый блок обработки информации, второй блок обработки информации, причем вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, вход синхронизации, подключены соответственно к первым, вторым, третьим, четвертым, пятым входам основного и резервного блоков памяти, информационные входы подключены к шестым входам основного и резервного блоков памяти и к входам первого и второго кодирующих блоков, которые формируют, соответственно, значения проверочных разрядов r1 и r2 путем сложения по модулю 2 информационных символов x1, х2, х3 и у1, у2, у3, поступающих на их входы в соответствии с правилом: r1=x1 ⊕ х2 ⊕ y1, ⊕ у2; r2=х2 ⊕ х3 ⊕ у2 ⊕ у3, выходы первого и второго кодирующих блоков подключены соответственно к седьмым входам основного и резервного блоков памяти, информационные выходы которых подключены соответственно к первым входам первого и второго корректоров, а также к входам третьего и четвертого кодирующих блоков, третий и четвертый блоки кодирования формируют значения проверочных контрольных разрядов r1c и r2c путем сложения по модулю информационных символов х1с, х2с, х3с и y1c, y2c, y3c, поступающих на их входы при считывании информации с информационных выходов соответственно с основного и резервного блоков памяти в соответствии с правилом: r1c=х1с ⊕ х2с ⊕ y1c, ⊕ y2c; rc2=х2с ⊕ х3с ⊕ y2c ⊕ y3c, выходы третьего кодирующего блока подключены к первым входам первого формирователя сигнала неисправности, вторые входы которого подключены к выходам проверочных разрядов основного блока памяти, а выходы подключены к входам первого элемента ИЛИ, выходы которого подключены к первым входам первого и второго блоков элементов И, выходы четвертого кодирующего бока подключены к первым входам второго формирователя сигнала неисправности, вторые входы которого подключены к выходам проверочных разрядов резервного блока памяти, а выходы подключены к входам второго элемента ИЛИ, выходы которого подключены к вторым входам первого блока элементов И и к первым входам третьего блока элементов И, выходы блока сумматоров по модулю два подключены к вторым входам второго и третьего блоков элементов И, выходы которых подключены соответственно к вторым входам первого и второго корректоров, вход синхронизации подключен к третьему входу первого блока элементов И и к первым входам четвертого и пятого блоков элементов И, вторые входы которых подключены соответственно к выходам первого и второго корректоров, а выходы подключены к входам первого и второго блоков обработки информации.

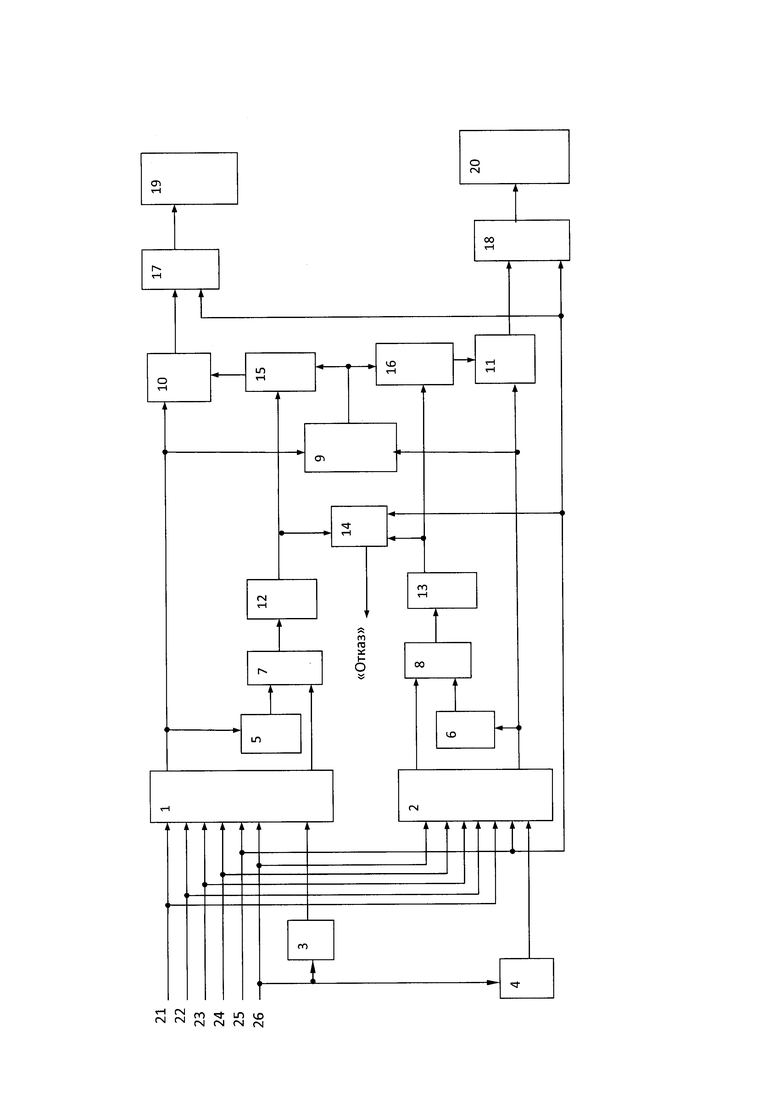

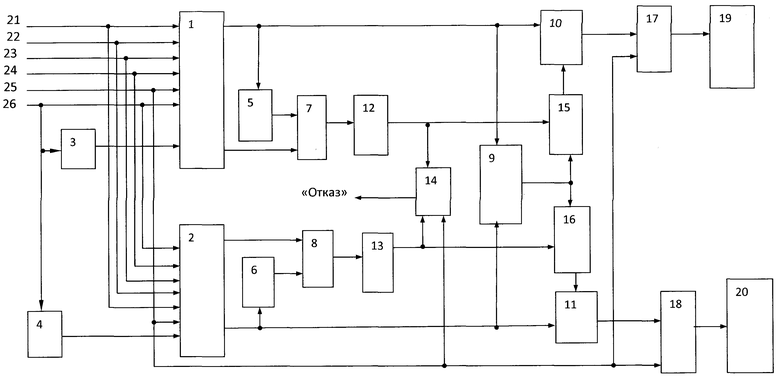

На фиг. представлена блок-схема резервированное запоминающее устройство с коррекцией ошибок в дублируемых каналах. Устройство содержит: основной блок 1 памяти, резервный блок 2 памяти, первый блок 3 кодирования, второй блок 4 кодирования, третий блок 5 кодирования, четвертый блок 6 кодирования, первый формирователь 7 сигнала неисправности, второй формирователь 8 сигнала неисправности, блок 9 сумматоров по модулю два, первый корректор 10, второй корректор 11, первый 12 элемент ИЛИ, второй 13 элемент ИЛИ, первый блок 14 элементов И, второй блок 15 элементов И, третий блок 16 элементов И, четвертый блок 17 элементов И, пятый блок 18 элементов И, первый блок 19 обработки информации, второй блок 20 обработки информации, вход 21 установки в нулевое состояние, вход 22 записи, вход 23 считывания, адресные входы 24, вход 25 синхронизации, информационные входы 26.

Вход 21 установки в нулевое состояние, вход 22 записи, вход 23 считывания, адресные входы 24, вход 25 синхронизации подключены соответственно к первым, вторым, третьим, четвертым, пятым входам основного 1 и резервного 2 блоков памяти, информационные входы 26 подключены к шестым входам основного 1 и резервного 2 блоков памяти и к входам первого 3 и второго 4 кодирующих блоков, которые формируют, соответственно, значения проверочных разрядов r1 и r2 путем сложения по модулю 2 информационных символов x1, х2, х3 и y1, у2, y3, поступающих на их входы в соответствии с правилом: r1=x1 ⊕ х2 ⊕ y1, ⊕ у2; r2=х2 ⊕ х3 ⊕ y2 ⊕ y3, выходы первого 3 и второго 4 кодирующих блоков подключены соответственно к седьмым входам основного 1 и резервного 2 блоков памяти, информационные выходы которых подключены соответственно к первым и вторым входам блока 9 сумматоров по модулю два, к первым входам первого 10 и второго 11 корректоров, а также к входам третьего 5 и четвертого 6 кодирующих блоков, третий 5 и четвертый 6 блоки кодирования формируют значения проверочных контрольных разрядов r1c и r2c путем сложения по модулю информационных символов х1с, х2с, х3с и у1с, у2с, y3c, поступающих на их входы при считывании информации с информационных выходов соответственно основного и резервного блоков памяти в соответствии с правилом: r1c=х1с ⊕ х2с ⊕ у1с, ⊕ у2с; rc2=х2с ⊕ х3с ⊕ у2с ⊕ у3с, выходы третьего кодирующего блока подключены к первым входам первого формирователя 7 сигнала неисправности, вторые входы которого подключены к выходам проверочных разрядов основного блока 1 памяти, а выходы подключены к входам первого 12 элемента ИЛИ, выходы которого подключены к первым входам первого 14 и второго 15 блоков элементов И, выходы четвертого кодирующего блока 6 подключены к первым входам второго формирователя 8 сигнала неисправности, вторые входы которого подключены к выходам проверочных разрядов резервного блока 2 памяти, а выходы подключены к входам второго 13 элемента ИЛИ, выходы которого подключены к вторым входам первого блока 14 элементов И и к первым входам третьего блока 16 элементов И, выходы блока 9 сумматоров по модулю два подключены к вторым входам второго 15 и третьего 16 блоков элементов И, выходы которых подключены соответственно к вторым входам первого 10 и второго 11 корректоров, вход 25 синхронизации подключен к третьему входу первого блока 14 элементов И и к первым входам четвертого 17 и пятого 18 блоков элементов И, вторые входы которых подключены соответственно к выходам первого 10 и второго 11 корректоров, а выходы подключены к входам первого 19 и второго 20 блоков обработки информации.

Основной 1 и резервный 2 блоки памяти, в данном случае, представляет собой статическое полупроводниковое устройство памяти и предназначен для хранения кодовых слов: УК=х1 х2 х3 у1 у2 у3 r1 r2, полученных при кодировании исходной информации.

Первый 3 и второй 4 блоки кодирования предназначен для формирования значений контрольных разрядов r1, r2 путем сложения по mod2 информационных символов в соответствии с правилом:

r1=x1 ⊕ х2 ⊕ у1, ⊕ у2;

r2=х2 ⊕ х3 ⊕ у2 ⊕ у3/

Третий 5 и четвертый 6 блоки кодирования предназначены для формирования значений контрольных разрядов r1c, r2c путем сложения по mod2 информационных символов в соответствии с правилом:

r1c=xlc ⊕ x2c ⊕ y1c, ® y2c;

r2c=x2c ⊕ x3c ⊕ y2c ⊕ y3c,

Первый 7 и второй формирователи сигнала неисправности предназначены для обнаружения ошибки в кодовом слове при считывании информации соответственно с основного 1 и резервного 2 блоков путем сложения по mod2 значений проверочных разрядов r1, r2, считываемых с выходов проверочных разрядов первого 1 и резервного 2 блоков памяти с значениями проверочных разрядов r1c, r2c, сформированных на выходах третьего 5 и четвертого 6 блоков кодирования:

λ1=r1 ⊕ r1c;

λ2=r2 ⊕ r2c..

Нулевой результат суммы свидетельствует об отсутствии ошибки, и ее наличии в противном случае.

Выходы λ1, λ2, первого 7 и второго 8 формирователей сигнала неисправностей объединены в один выход соответственно первым 12 и вторым 13 элементами ИЛИ,

Блок 9 сумматоров по модулю два предназначен для формирования вектора ошибки путем поразрядного сложения по mod 2 одноименных информационных разрядов основного 1 и резервного 2 блоков памяти:

Первый 10 и второй 11 корректоры предназначены для исправления ошибочных информационных разрядов неисправного блока памяти путем сложения по mod 2 значений информационных разрядов с значением вектора ошибки:

Устройство работает следующим образом. Перед началом работы устройства на вход 21 "установки в нулевое состояние" подается единичный сигнал, который переводит устройство в нулевое состояние.

При записи информации в основной 1 и резервный блоки памяти, подается единичный сигнал на вход 22 записи, адресные входы 24 и информационные входы 25.

Например, на информационные входы поступает кодовая комбинация: х1 x2 x3 y1 y2 y3 соответствующая значению -000 110

В этом случае первый 3 и второй 4 блоки кодирования формирует вектор:

r1=х1 ⊕ х2 ⊕ у1 ⊕ у2=0; r2=х2 ⊕ х3 ⊕ у2 ⊕ у3=1.

Соответственно в основной 1 и резервный 2 блоки памяти запишется информация:

000 110 01.

При считывании информации на вход 23 считывания и адресные входы 24 подаются сигналы, разрешающие считывание информации с основного 1 и резервного блоков памяти узла по указанному адресу.

Значения информационных разрядов поступают на входы первого 10 и второго 11 корректоров и на входы третьего 5 и четвертого 6 боков кодирования, которые формируют значения проверочных разрядов относительно считываемой информации.

В первом 7 и втором 8 формирователях сигнала неисправности осуществляется поразрядное сравнение значений проверочных разрядов считываемых с основного и резервного блоков памяти с с значениями проверочных разрядов, сформированными третьим 5 и четвертым 6 боками кодирования.

При отсутствии ошибки, на выходах первого 7 и второго 8 формирователей сигнала неисправности имеем значения: λ1=0, λ2=0.

Информация с основного 1 и резервного 2 блоков памяти, при поступлении сигнала синхронизации, поступает соответственно в первый 19 и второй 20 блоки информации без коррекции.

Допустим, произошла ошибка в первом информационном разряде: 1* 00 110 01 основного блока 1 памяти. В этом случае на выходах третьего блока 5 кодирования получим значения сигналов: r1c=1 и r2c=1. Так как значение r1=0 и r2=1, поступающее с выходов основного блока 1 памяти не совпадает с сформированными значениями r1c=1 и r2c=1, то на выходе первого формирователя 7 сигнала неисправности получим значения сигналов: λ1=1, λ2=0, соответственно на выходе первого 12 элемента ИЛИ появится единичное значение сигнала, которое подготавливает к открытию второй блок 15 элементов И, на вторые входы которого поступает значение вектора ошибки с выходов блока 9 сумматоров по модулю два.

При поступлении сигнала с входа 25 синхронизации, значение вектора ошибки поступит на вход первого корректора 10, в котором происходит исправление ошибочного разряда.

Аналогичным образом устройство работает при появлении других ошибок.

При одновременном возникновении ошибок в основном 1 и резервном 2 блоках памяти, первый 14 элемент И открывается и выдается сигнал «отказ устройства».

Предлагаемое устройство обеспечивает сокращение аппаратурных затрат, связанных с построением средства контроля для обнаружения одиночных и двойных ошибок в дублирующих каналах. Это достигается кодированием исходной двоичной информации на основе алгебраического линейного кода с использованием двух проверочных разрядов, что позволяет сократить аппаратурные затраты, связанные с хранением значений проверочных разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ОДИНОЧНЫХ И ДВОЙНЫХ ОШИБОК | 2011 |

|

RU2450332C1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2421786C1 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2579954C2 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2422923C1 |

| СБОЕУСТОЙЧИВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2610264C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ОШИБОК | 2016 |

|

RU2621284C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2009 |

|

RU2403615C2 |

| УСТРОЙСТВО ХРАНЕНИЯ И СЧИТЫВАНИЯ ИНФОРМАЦИИ С КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК | 2023 |

|

RU2816550C1 |

| КОНТРОЛИРУЕМОЕ УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ | 2015 |

|

RU2618388C1 |

Изобретение относится к резервированному запоминающему устройству с коррекцией ошибок в дублируемых каналах. Технический результат заключается в сокращении аппаратурных затрат, связанных с построением средства контроля для обнаружения одиночных и двойных ошибок в дублирующих каналах, и в повышении отказоустойчивости резервированного устройства за счет коррекции возникающих ошибок. Указанный результат достигается кодированием исходной двоичной информации на основе алгебраического линейного кода с использованием двух проверочных разрядов, что позволяет сократить аппаратурные затраты, связанные с хранением значений проверочных разрядов. Исправление возникающих ошибок, обеспечивается формированием вектора ошибки на основе поразрядного суммирования по модулю два значений информационных разрядов, поступающих с информационных выходов основного и резервного блоков памяти. 1 ил.

Резервированное запоминающее устройство с коррекцией ошибок в дублируемых каналах, содержащее основной блок памяти, резервный блок памяти, первый формирователь сигнала неисправности, блок сумматоров по модулю два, отличающееся тем, что оно дополнительно содержит первый кодирующий блок, второй кодирующий блок, третий кодирующий блок, четвертый кодирующий блок, второй формирователь сигнала неисправности, первый корректор, второй корректор, первый элемент ИЛИ, второй элемент ИЛИ, первый блок элементов И, второй блок элементов И, третий блок элементов И, четвертый блок элементов И, пятый блок элементов И, первый блок обработки информации, второй блок обработки информации, причем вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, вход синхронизации, подключены соответственно к первым, вторым, третьим, четвертым и пятым входам основного и резервного блоков памяти, информационные входы подключены к шестым входам основного и резервного блоков памяти и к входам первого и второго кодирующих блоков, которые формируют, соответственно, значения проверочных разрядов r1 и r2 путем сложения по модулю 2 информационных символов x1, х2, х3 и у1,у2, y3, поступающих на их входы в соответствии с правилом: r1=x1 ⊕ х2 ⊕ у1, и ⊕ y2, r2=х2 ⊕ х3 ⊕ у2 ⊕ у3, выходы первого и второго кодирующих блоков подключены соответственно к седьмым входам основного и резервного блоков памяти, информационные выходы которых подключены соответственно к входам блока сумматоров по модулю два, к первым входам первого и второго корректоров, а также к входам третьего и четвертого кодирующих блоков, третий и четвертый блоки кодирования формируют значения проверочных контрольных разрядов r1c и r2c путем сложения по модулю информационных символов х1с, х2с, х3с и у1с, y2c, y3c, поступающих на их входы при считывании информации с информационных выходов соответственно основного и резервного блоков памяти в соответствии с правилом: r1c=х1с ⊕ х2с ⊕ y1c, ⊕ y2c; rc2=х2с ⊕ x3c ⊕ y2c ⊕ y3c, выходы третьего кодирующего блока подключены к первым входам первого формирователя сигнала неисправности, вторые входы которого подключены к выходам проверочных разрядов основного блока памяти, а выходы подключены к входам первого элемента ИЛИ, выходы которого подключены к первым входам первого и второго блоков элементов И, выходы четвертого кодирующего бока подключены к первым входам второго формирователя сигнала неисправности, вторые входы которого подключены к выходам проверочных разрядов резервного блока памяти, а выходы подключены к входам второго элемента ИЛИ, выходы которого подключены к вторым входам первого блока элементов И и к первым входам третьего блока элементов И, выходы блока сумматоров по модулю два подключены к вторым входам второго и третьего блоков элементов И, выходы которых подключены соответственно к вторым входам первого и второго корректоров, вход синхронизации подключен к третьему входу первого блока элементов И и к первым входам четвертого и пятого блоков элементов И, вторые входы которых подключены соответственно к выходам первого и второго корректоров, а выходы подключены к входам первого и второго блоков обработки информации.

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2579954C2 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2211492C2 |

| Укупорочная машина и патрон для укупоривания бутылок корковыми пробками | 1956 |

|

SU109888A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149319A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| US 9959166 B2, 01.05.2018. | |||

Авторы

Даты

2024-09-19—Публикация

2022-07-18—Подача