Устройство хранения и передачи информации с обнаружением ошибок относится к вычислительной технике и может быть использовано для повышения достоверности функционирования работы, устройств хранения и передачи информации.

Известно устройство памяти с обнаружением двойных ошибок [1], содержащее узел памяти, входной блок кодирования, формирующий значения контрольных разрядов rl и r2 путем сложения по модулю 2 информационных символов х1,х2,х3,у1,у2,у3, поступающих на входы входного блока кодирования, в соответствии с правилом: r1=х1⊕х2⊕y1⊕у2; r2=х2⊕х3⊕у2⊕у3, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1П, r2П путем сложения по модулю 2 информационных символов x1C, х2С, х3С, у1С,у2С,у3С, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом: r1П=х1С⊕х2С⊕y1C⊕y2C; r2П=х2С⊕х3С⊕у2С⊕у3С, блок выявления ошибки, блок элементов И, элемент И, блок элементов ИЛИ, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки, вход установки в нулевое состояние, вход записи, вход считывании, адресные входы, информационные входы, вход синхронизации подключены соответственно к первому, второму, третьему и четвертому, пятому и шестому входам узла памяти, информационные выходы узла памяти подключены к входам выходного блока кодирования и к первым входам блока элементов И, выходы выходного блока кодирования подключены к первым входам блока выявления ошибки, вторые входы которого подключены к выходом контрольных разрядов узла памяти, а выходы подключены к входам блока элементов ИЛИ, выход которого подключен к первому входу элемента И, второй вход блока элементов И и второй вход элемента И подключены к входу синхронизации, выходы первого блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала "Ошибка".

Недостатком устройства является низкая обнаруживающая способность двойных ошибок.

Наиболее близким по техническому решению является контролируемое устройство хранения и передачи информации [2], содержащее узел памяти, входной блок кодирования, формирующий значения контрольных разрядов r1, r2 и r3, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1p, r2p, r3p блок выявления ошибки, блок элементов ИЛИ, блок элементов И, элемент И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки, вход установки в нулевое состояние, вход записи, вход считывании, адресные входы, вход синхронизации подключены соответственно к первому, второму, третьему и четвертому, пятому входам узла памяти, информационные входы подключены к шестым входам узла памяти и к входам входного кодирующего устройства, выходы которого подключены к седьмым входам узла памяти, информационные выходы узла памяти подключены к входам выходного блока кодирования и к первым входам блока элементов И, выходы выходного блока кодирования подключены к первым входам блока выявления ошибки, вторые входы которого подключены к выходам контрольных разрядов узла памяти, а выходы подключены к входам блока элементов ИЛИ, выход которого подключен к первому входу элемента И, второй вход блока элементов И и второй вход элемента И подключены к входу синхронизации, выходы первого блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала "Ошибка", входной блок кодирования формирует значение контрольного разряда r1 путем сложения по модулю 2 информационных символов у1,у2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r1=у3⊕у4⊕у5⊕y6⊕y9⊕у10⊕y11⊕y12, значение контрольного разряда r2 - путем сложения по модулю 2 информационных символов у1,у2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r2=y3⊕y6⊕y7⊕y8⊕у9⊕у10⊕y11⊕y12, значение контрольного разряда r3 - путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r3=y1⊕у2⊕у4⊕y5⊕y7⊕y8⊕у10⊕y11, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1p, r2p, r3p, путем сложения по модулю 2 информационных символов y1p,y2p,y3p, y4p,y5p,y6p, y7p,y8p,y9p, y10p,y11p,y12p, поступающих на его входы при считывании информации с информационных выходов узла памяти, в соответствии с правилом: r1p=y3p⊕y4p⊕y5p⊕y6p⊕y9p⊕y10p⊕y11p⊕y12p; r2p=y3p⊕y6p⊕y7p⊕y8p⊕y9p⊕y10p⊕y11p⊕y12p; r3p=y1p⊕у2р⊕y4p⊕y5p⊕y7p⊕y8p⊕y10p⊕y11p, блок выявления ошибки осуществляет поразрядное сложение по mod2 значений контрольных разрядов r1S, r2S и r3S, считываемых с вторых выходов узла 1 памяти, соответственно с значениями контрольных разрядов r1p, r2p, r3p, сформированных на выходах выходного блока 3 кодирования.

Недостатком устройства является недостаточная обнаруживающая способность двойных ошибок, так как обнаруживаются не все двойные ошибки.

Целью изобретения является повышение достоверности функционирования устройства за счет обнаружения 100% одиночных и максимального количества двойных ошибок при минимальной информационной избыточности.

Поставленная цель достигается тем, что устройство, содержащее узел памяти, входной блок кодирования, формирующий значения контрольных разрядов r1, r2 и r3, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1p, r2p, r3p, блок выявления ошибки, блок элементов ИЛИ, блок элементов И, элемент И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки, вход установки в нулевое состояние, вход записи, вход считывании, адресные входы, вход синхронизации подключены соответственно к первому, второму, третьему и четвертому, пятому входам узла памяти, информационные входы подключены к шестым входам узла памяти и к входам входного кодирующего устройства, выходы которого подключены к седьмым входам узла памяти, информационные выходы узла памяти подключены к входам выходного блока кодирования и к первым входам блока элементов И, выходы выходного блока кодирования подключены к первым входам блока выявления ошибки, вторые входы которого подключены к выходам контрольных разрядов узла памяти, а выходы подключены к входам блока элементов ИЛИ, выход которого подключен к первому входу элемента И, второй вход блока элементов И и второй вход элемента И подключены к входу синхронизации, выходы первого блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала "Ошибка", отличается тем, что дополнительно содержит четвертый выход r4 входного блока кодирования, четвертый выход r4p выходного блока кодирования и четвертый выход r4S контрольного разряда узла памяти, четвертый выход r4 входного блока кодирования подключен к восьмому входу узла памяти, четвертый выход r4p выходного блока кодирования подключен к третьему входу блока 4 выявления ошибки, четвертый вход которого подключен к четвертому выходу r4S узла памяти, причем входной блок кодирования формирует значение контрольного разряда r1 путем сложения по модулю 2 информационных символов y1,у2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r1=у3⊕у4⊕у5⊕у6⊕y9⊕у10⊕y11⊕у12, значение контрольного разряда r2 - путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r2=y3⊕у6⊕у7⊕у8⊕у9⊕у10⊕у11⊕у12, значение контрольного разряда r3 - путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r3=y1⊕у2⊕у4⊕у5⊕у7⊕у8⊕у10⊕у11, значение контрольного разряда r4 - путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r4=у2⊕у5⊕у6⊕у7⊕у9⊕у10, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1p, r2p, r3p, r4p, путем сложения по модулю 2 информационных символов y1p,y2p,y3p, y4p,y5p,y6p, y7p,y8p,y9p, y10p,y11p,y12p, поступающих на его входы при считывании информации с информационных выходов узла памяти, в соответствии с правилом: r1p=y3p⊕у4р⊕у5р⊕у6р⊕у9р⊕у10р⊕y11p⊕у12р; r2p=y3p⊕у6р⊕у7р⊕у8р⊕у9р⊕у10р⊕у11р⊕y12p; r3p=y1p⊕у2р⊕у4р⊕у5р⊕у7р⊕у8р⊕у10р⊕у11р, r4=y2⊕у5⊕у6⊕у7⊕y9⊕у10, блок выявления ошибки осуществляет поразрядное сложение по mod2 значений контрольных разрядов r1S, r2S и r3S, r4S, считываемых с вторых выходов узла 1 памяти, соответственно с значениями контрольных разрядов r1p, r2p, r3p, r4p, сформированных на выходах выходного блока 3 кодирования.

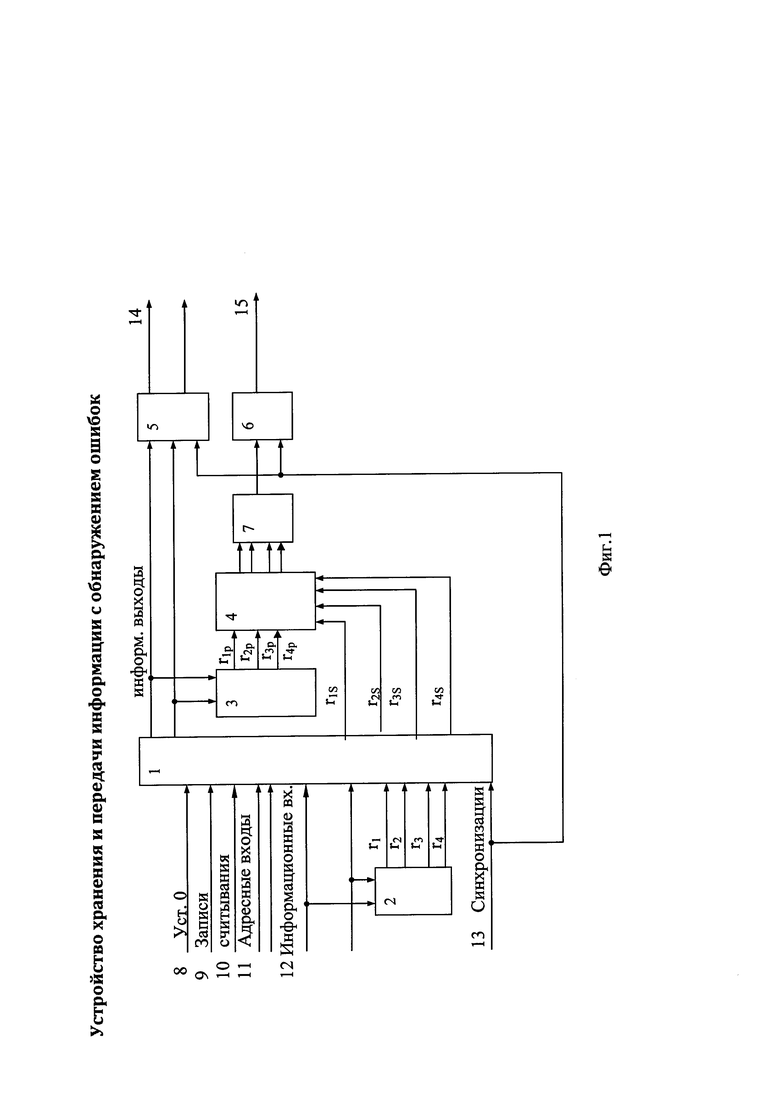

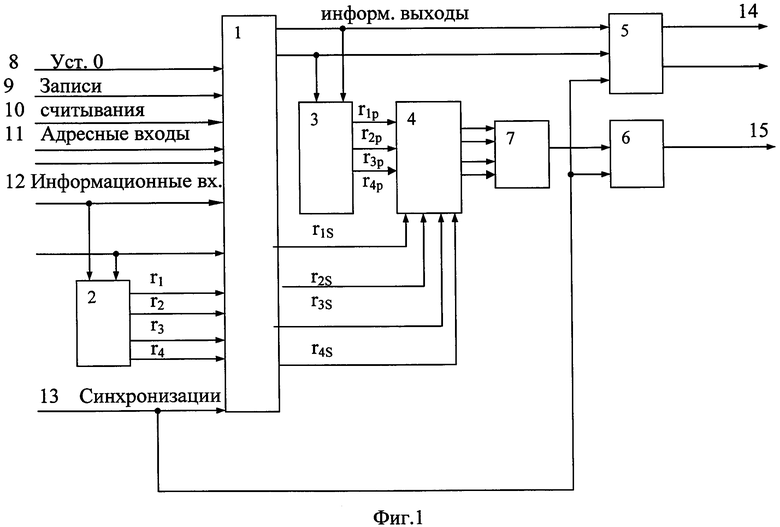

На фиг. 1 представлена блок-схема устройства. Устройство хранения и передачи информации с обнаружением ошибок содержит: узел 1 памяти, входной блок 2 кодирования, выходной блок 3 кодирования, блок 4 выявления ошибки, блок 5 элементов И, элемент 6 И, блок 7 элементов ИЛИ, вход 8 установки в нулевое состояние, вход 9 записи, вход 10 считывания, адресные входы 11, информационные входы 12, вход 13 синхронизации, информационные выходы 14, выход 15 "Ошибка".

Вход 8 установки в нулевое состояние, вход 9 записи, вход 10 считывании, адресные входы 11, вход 13 синхронизации подключены соответственно к первому, второму, третьему и четвертому, пятому входам узла 1 памяти, информационные входы 12 подключены к шестым входам узла 1 памяти и к входам входного кодирующего устройства 2, выходы которого подключены к седьмым входам узла 1 памяти, информационные выходы узла 1 памяти подключены к входам выходного блока 3 кодирования и к первым входам блока 5 элементов И, выходы выходного блока 3 кодирования подключены к первым входам блока 4 выявления ошибки, вторые входы которого подключены к выходам контрольных разрядов узла 1 памяти, а выходы подключены к входам блока 7 элементов ИЛИ, выход которого подключен к первому входу элемента 6 И, второй вход блока элементов 5 И и второй вход элемента 6 И подключены к входу 13 синхронизации, выходы блока 5 элементов И являются информационными выходами устройства, выход элемента 6 И является выходом сигнала "Ошибка", устройство отличается тем, что дополнительно содержит четвертый выход r4 входного блока 2 кодирования, четвертый выход r4p выходного блока 3 кодирования и четвертый выход r4S контрольного разряда узла 1 памяти, четвертый выход r4 входного блока 2 кодирования подключен к восьмому входу узла 1 памяти, четвертый выход r4p выходного блока 3 кодирования подключен к третьему входу блока 4 выявления ошибки, четвертый вход которого подключен к четвертый выходу r4S узла 1 памяти, причем входной блок 2 кодирования формирует значение контрольного разряда r1 путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r1=у3⊕y4⊕y5⊕y6⊕y9⊕y10⊕y11⊕y12, значение контрольного разряда r2 - путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r2=у3⊕y6⊕y7⊕y8⊕y9⊕y10⊕y11⊕y12, значение контрольного разряда r3 - путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r3=y1⊕y2⊕y4⊕y5⊕y7⊕y8⊕y10⊕y11, значение контрольного разряда r4 - путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r4=у2⊕y5⊕y6⊕y7⊕y9⊕y10, выходной блок 3 кодирования, формирующий значения проверочных контрольных разрядов r1p, r2p, r3p, r4p, путем сложения по модулю 2 информационных символов y1p,y2p,y3p, y4p,y5p,y6p, y7p,y8p,y9p, y10p,y11p,y12p, поступающих на его входы при считывании информации с информационных выходов узла памяти, в соответствии с правилом: r1p=y3p⊕у4р⊕у5р⊕у6р⊕у9р⊕у10р⊕y11p⊕у12р; r2p=y3p⊕у6р⊕у7р⊕у8р⊕у9р⊕у10р⊕у11р⊕y12p; r3p=y1p⊕у2р⊕у4р⊕у5р⊕у7р⊕у8р⊕у10р⊕у11р, r4=y2⊕у5⊕у6⊕у7⊕y9⊕у10, блок 4 выявления ошибки осуществляет поразрядное сложение по mod2 значений контрольных разрядов r1S, r2S и r3S, r4S, считываемых с вторых выходов узла 1 памяти, соответственно с значениями контрольных разрядов r1p, r2p, r3p, r4p, сформированных на выходах выходного блока 3 кодирования.

Узел 1 памяти в данном случае представляет собой статическое полупроводниковое оперативное устройство памяти и предназначен для хранения кодовых слов: УК=y1y2 y3 y4 у5 y6 y7 y8 у9, y10 y11 y12 r1 r2 r3 r4, полученных при кодировании исходной информации.

Входной блок 2 кодирования предназначен для формирования значений контрольных разрядов r1, r2, r3, r4 путем сложения по mod2 информационных символов в соответствии с правилом:

r1=y3⊕y4⊕y5⊕y6⊕y9⊕y10⊕y11⊕y12;

r2=y3⊕y6⊕y7⊕y8⊕y9⊕y10⊕y11⊕y12;

r3=y1⊕y2⊕y4⊕y5⊕y7⊕y8⊕y10⊕y11;

r4=y2⊕y5⊕y6⊕y7⊕y9⊕y10.

Выходной блок 3 кодирования предназначен для формирования значений проверочных контрольных разрядов r1p, r2p, r3p, r4p, путем сложения по mod2 информационных символов, полученных при считывании информации с узла 1 памяти в соответствии с правилом:

r1p=y3p⊕y4p⊕y5p⊕y6p⊕y9p⊕y10p⊕y11p⊕y12p;

r2p=y3p⊕y6p⊕y7p⊕y8p⊕y9p⊕y10p⊕y11p⊕y12p;

r3p=y1p⊕y2p⊕y4p⊕y5p⊕y7p⊕y8p⊕y10p⊕y11p.

r4p=y2p⊕y5p⊕y6p⊕y7p⊕y9p⊕y10p.

Блок 4 выявления ошибки предназначен для обнаружения ошибки в кодовом слове при считывании информации с узла 1 памяти путем сложения по mod2 значений контрольных разрядов r1S, r2S, r3S и r4S, считываемых с вторых выходов узла 1 памяти, соответственно с значениями контрольных разрядов r1p, r2p и r3p, сформированных на выходах выходного блока 3 кодирования:

λ1=r1S⊕r1p;

λ2=r2S⊕r2p;

λ3=r3S⊕r3p;

λ4=r4S⊕r4p.

Нулевой результат суммы свидетельствует об отсутствии ошибки и ее наличии в противном случае.

Выходы λ1, λ2, λ3 и λ4 блока 4 выявления ошибки объединены в один выход первым элементом 7 ИЛИ, значение сигнала на данном выходе поступает первый вход элемента 6 И.

Считывание выходной информации с выходов 14 устройства проводится при поступлении сигнала с входа 13 синхронизации на второй вход блока 5 элементов И и второй вход элемента 6 И.

Устройство работает следующим образом. Перед началом работы устройства на вход 8 "Установки в нулевое состояние" подается единичный сигнал, который переводит узел 1 памяти в нулевое состояние.

При записи информации в узел 1 памяти подается единичный сигнал на вход 9 записи, адресные входы 11 и информационные входы 12.

Например, на информационные входы поступает

двенадцатиразрядное слово, имеющие в своих разрядах следующие значения: 110 001 101 111.

Входной блок 2 кодирования сформирует значения контрольных разрядов:

r1=(у3⊕у9)⊕(у4⊕у5⊕y6)⊕(y10⊕y11⊕y12)=0⊕1⊕0⊕0⊕1⊕1⊕1⊕1=1;

r2==(y3⊕y6)⊕(y7⊕y8⊕y9)⊕(y10⊕y11⊕y12)=0⊕1⊕1⊕0⊕1⊕1⊕1⊕1=0;

r3=(y1⊕y2)⊕(y4⊕y5)⊕(y7⊕у8)⊕(у10⊕у11)=1⊕1⊕0⊕0⊕1⊕0⊕1⊕1=1;

r4=y2⊕y5⊕y6⊕y7⊕y9⊕y10=1⊕0⊕1⊕1⊕1⊕1=1

В результате имеем кодовое слово: Ук=110 001 101 111 1011 (последние четыре разряда являются контрольными разрядами), которое записывается в узле 1 памяти.

При считывании информации с узла 1 памяти второй блок 3 кодирования относительно принятой информации сформирует значения контрольных разрядов: Rp={r1p, r2p, r3p, r4p}={1011}

Если ошибок нет, то имеем результат: R=(1011), Rp=(1011), RS=(1011), λ=(0000).

Пусть произошла одиночная ошибка во первом информационном разряде: 0* 10 001 1 01 111 1011.

На выходе второго блока 3 кодирования имеем результат: Rp=(1001), а с вторых выходов узла 1 памяти считывается значения переданных контрольных разрядов RS=(1011),

В этом случае сигналы на выходе блока 4 выявления ошибки принимают значение: λ=(0010).

Соответственно на выходе блока 5 ИЛИ появится единичное значение сигнала, которое при поступлении сигнала с входа 13 синхронизации поступит на вход элемента 6 И, на выходе которого появится значение сигнала "Ошибка".

Аналогичным образом устройство работает при возникновении двойных ошибок.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Патент на изобретение №2403615 "Устройство хранения и передачи информации с обнаружением двойных ошибок" / Павлов А.А., Царьков А.Н. и др. от 27.01.2009.

2. Патент на полезную модель №161373 "Контролируемое устройство хранения и передачи информации "/ Бутранов А.С., Павлов А.А., Царьков А.Н. и др. от 29.03.2016.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНТРОЛИРУЕМОЕ УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ | 2015 |

|

RU2618388C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ ОШИБОК | 2016 |

|

RU2637426C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И СЧИТЫВАНИЯ ИНФОРМАЦИИ С КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК | 2023 |

|

RU2816550C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ ОДИНОЧНЫХ И ДВОЙНЫХ ОШИБОК | 2017 |

|

RU2659479C1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ С ПОВЫШЕННОЙ КОРРЕКТИРУЮЩЕЙ СПОСОБНОСТЬЮ | 2024 |

|

RU2829012C1 |

| ОТКАЗОУСТОЙЧИВАЯ ЭВМ | 2018 |

|

RU2704325C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ МАГИСТРАЛЕЙ | 1990 |

|

RU2017210C1 |

| УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ ПАМЯТИ | 1990 |

|

RU2020566C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении достоверности функционирования устройств хранения и передачи информации путем обнаружения одиночных и двойных ошибок при минимальной избыточности. Технический результат достигается за счет кодирования исходной двоичной информации на основе организации независимых проверок и за счет введения входного блока 2 кодирования, выходного блока 3 кодирования, блока 4 выявления ошибки, блока 5 элементов И, элемента 6 И, блока 7 элементов ИЛИ. 1 ил.

Устройство хранения и передачи информации с обнаружением ошибок, содержащее узел памяти, входной блок кодирования, формирующий значения контрольных разрядов r1, r2 и r3, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1p, r2p, r3p, блок выявления ошибки, блок элементов ИЛИ, блок элементов И, элемент И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки, вход установки в нулевое состояние, вход записи, вход считывании, адресные входы, вход синхронизации подключены соответственно к первому, второму, третьему и четвертому, пятому входам узла памяти, информационные входы подключены к шестым входам узла памяти и к входам входного кодирующего устройства, выходы которого подключены к седьмым входам узла памяти, информационные выходы узла памяти подключены к входам выходного блока кодирования и к первым входам блока элементов И, выходы выходного блока кодирования подключены к первым входам блока выявления ошибки, вторые входы которого подключены к выходам контрольных разрядов узла памяти, а выходы подключены к входам блока элементов ИЛИ, выход которого подключен к первому входу элемента И, второй вход блока элементов И и второй вход элемента И подключены к входу синхронизации, выходы первого блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала "Ошибка", отличающееся тем, что дополнительно содержит четвертый выход r4 входного блока кодирования, четвертый выход r4p выходного блока кодирования и четвертый выход r4S контрольного разряда узла памяти, четвертый выход r4 входного блока кодирования подключен к восьмому входу узла памяти, четвертый выход r4p выходного блока кодирования подключен к третьему входу блока 4 выявления ошибки, четвертый вход которого подключен к четвертому выходу r4S узла памяти, причем входной блок кодирования формирует значение контрольного разряда r1 путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r1 = y3 ⊕ y4 ⊕ у5 ⊕ y6 ⊕ y9 ⊕ y10 ⊕ y11 ⊕ y12, значение контрольного разряда r2 - путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r2 = y3 ⊕ y6 ⊕ y7 ⊕ y8 ⊕ y9 ⊕ y10 ⊕ y11 ⊕ y12, значение контрольного разряда r3 - путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r3 = y1 ⊕ y2 ⊕ y4 ⊕ y5 ⊕ y7 ⊕ y8 ⊕ y10 ⊕ y11, значение контрольного разряда r4 - путем сложения по модулю 2 информационных символов y1,y2,y3, y4,y5,y6, y7,y8,y9, y10,y11,y12, поступающих на его входы, в соответствии с правилом: r4 = y2 ⊕ y5 ⊕ y6 ⊕ у7 ⊕ y9 ⊕ y10, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1p, r2p, r3p, r4p, путем сложения по модулю 2 информационных символов y1p,y2p,y3p, y4p,y5p,y6p, y7p,y8p,y9p, y10p,y11p,y12p, поступающих на его входы при считывании информации с информационных выходов узла памяти, в соответствии с правилом: r1p = y3p ⊕ y4p ⊕ y5p ⊕ y6p ⊕ y9p ⊕ y10p ⊕ y11p ⊕ y12p; r2p = y3p ⊕ y6p ⊕ y7p ⊕ y8p ⊕ y9p ⊕ y10p ⊕ y11p ⊕ y12p; r3p = y1p ⊕ y2p ⊕ y4p ⊕ y5p ⊕ y7p ⊕ y8p ⊕ y10p ⊕ y11p, r4 = y2 ⊕ y5 ⊕ y6 ⊕ y7 ⊕ y9 ⊕ y10, блок выявления ошибки осуществляет поразрядное сложение по mod2 значений контрольных разрядов r1S, r2S и r3S, r4S, считываемых с вторых выходов узла 1 памяти, соответственно с значениями контрольных разрядов r1p, r2p, r3p, r4p, сформированных на выходах выходного блока 3 кодирования.

| 0 |

|

SU161373A1 | |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2421786C1 |

| Способ выплавки ферросилиция в электропечах с применением брикетов | 1956 |

|

SU107606A1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2014 |

|

RU2542665C1 |

| US 7764958 B2, 27.07.2010. | |||

Авторы

Даты

2017-06-01—Публикация

2016-05-23—Подача