Изобретение относится к области радиоизмерений, в частности к устройствам для измерения характеристик случайных процессов.

Известно устройство для определения параметра m случайного процесса с распределением Накагами (SU 481907, G06G 7/00, 1975 г.), содержащее нелинейный блок с логарифмической характеристикой, соединенный через блок определения дисперсии с нелинейным индикаторным прибором, отградуированным в единицах дзета-функции Римана. Выход источника случайного процесса, имеющего распределение плотностей Накагами, подключен к входу нелинейного блока с логарифмической амплитудной характеристикой, выход которого подключен к входу блока определения дисперсии случайного процесса, выход которого соединен с входом индикаторного прибора.

Недостатком известного устройства является относительно низкая точность определения параметра m случайного процесса с распределением Накагами вследствие визуального определения, исходя из информации, отображаемой на индикаторном приборе.

Известно устройство для определения характеристик случайных процессов (SU 1273947 А1, 4 G06F 15/36, 1986 г.), содержащее усреднитель, первый элемент И, блок сравнения, первый делитель, первый сумматор, квадратор, одновибратор, второй элемент И, масштабные блоки, логарифматор, блоки извлечения корня, второй сумматор, второй делитель, вход устройства соединен с входом квадратора и одновибратора, выход которого подключен к счетному входу счетчика, выход которого соединен с первыми входами первого и второго элементов И, выход квадратора подключен к входу первого масштабного блока и к входу усреднителя, выход которого соединен со вторым входом второго элемента И, выход которого подключен к входу делимого первого делителя, вход делителя первого делителя соединен с выходом первого блока извлечения корня, вход которого объединен с первым входом блока сравнения и подключен к выходу первого элемента И, второй вход которого соединен с выходом первого масштабного блока, выход первого делителя подключен к входу логарифматора, выход которого соединен с входами второго и третьего масштабных блоков, выход второго масштабного блока подключен к входу первого сумматора, выход которого соединен с входом второго блока извлечения корня, выход которого подключен к входу второго сумматора, выход которого соединен с входом делимого второго делителя, вход делителя второго делителя подключен к выходу третьего масштабного блока, выход второго делителя является выходом первого параметра распределения Накагами устройства, второй вход блока сравнения соединен с входом задания нуля устройства, выходы блока сравнения и первого делителя являются соответственно выходами "Стоп" и второго параметра распределения Накагами устройства.

Недостатком известного устройства является относительно низкая точность определения параметра m случайного процесса с распределением Накагами. Низкая точность обусловлена тем, что в устройстве для определения параметра m случайного процесса с распределением Накагами, реализован метод максимального правдоподобия.

Наиболее близким по технической сущности и выполняемым функциям к заявляемому устройству является устройство для измерения характеристик случайных процессов (Патент РФ №2336562, МПК 7 G06G 7/52, 19.05.2006 г.).

Устройство-прототип содержит первый дешифратор, индикатор, нормирующий усилитель, вход которого соединен с входной шиной, а выход через последовательно соединенные двойной квадратичный детектор и первый интегратор подключен к первому входу первого делителя, при этом выход нормирующего усилителя через последовательно соединенные первый детектор, второй интегратор и второй детектор подключен также ко второму входу первого делителя, при этом выход нормирующего усилителя последовательно соединен с первым умножителем, третьим интегратором и вторым делителем, выход которого подключен одновременно к первым входам первого и второго компараторов, вторые входы которых соединены соответственно с входными шинами, при этом первый вход второго умножителя непосредственно, а второй вход через первый блок извлечения квадратного корня подключены к выходу второго интегратора, выход второго умножителя подключен ко второму входу второго делителя, при этом первый вход первого умножителя непосредственно, а второй через третий детектор подключен к выходу нормирующего усилителя, при этом выход третьего делителя подключен к первому входу первого ключа, второй вход которого соединен со вторым входом второго ключа, при этом выходы первого, второго, третьего, четвертого, пятого, шестого и седьмого элементов И-НЕ соответственно подключены к первому, второму, третьему, четвертому, пятому, шестому и седьмому входам индикатора, восьмой, девятый, десятый и одиннадцатый входы которого соединены соответственно с первым, вторым, третьим и четвертым выходами коммутатора, пятый вход которого соединен с входной шиной, а первый, второй, третий и четвертый входы соединены соответственно с первым, вторым, третьим и четвертым выходами второго дешифратора, первый вход которого одновременно соединен с входной шиной и объединенными девятыми входами первого и второго мультиплексоров, при этом второй вход второго дешифратора одновременно соединен с входной шиной и объединенными десятыми входами первого и второго мультиплексоров, а объединенные девятые и объединенные десятые входы первого и второго регистров соединены соответственно с входными шинами, первый, второй, пятый и шестой входы первого мультиплексора соединены соответственно с первым, пятым, вторым и шестым выходами первого регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого и двенадцатого компараторов, первые входы которых объединены, при этом третий, седьмой, четвертый и восьмой выходы первого регистра подключены соответственно к первому, второму, пятому и шестому входам второго мультиплексора, третий, четвертый, седьмой и восьмой входы которого соединены соответственно с третьим, седьмым, четвертым и восьмым выходами второго регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами третьего, четвертого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восемнадцатого компараторов, первые входы которых объединены, а первый, пятый, второй и шестой выходы второго регистра подключены соответственно к третьему, четвертому, седьмому и восьмому входам первого мультиплексора, первый и второй выходы которого подключены соответственно к первому и второму входам первого дешифратора, третий и четвертый входы которого соединены соответственно с первым и вторым выходами второго мультиплексора, второй выход первого дешифратора одновременно подключен к первым входам первого и второго элементов И, вторые входы которых соответственно соединены с пятым и восьмым выходами первого дешифратора, десятый выход которого подключен ко второму входу четвертого элемента И-НЕ, первый вход которого одновременно соединен с первыми входами третьего и второго элементов И-НЕ и двенадцатым выходом первого дешифратора, одиннадцатый выход которого одновременно подключен к объединенным второму входу седьмого элемента И-НЕ, третьему входу третьего элемента И-НЕ и второму входу второго элемента И-НЕ, при этом первый выход первого дешифратора подключен к четвертому входу седьмого элемента И-НЕ, третий вход которого одновременно соединен с третьим входом первого элемента И-НЕ и пятнадцатым выходом первого дешифратора, четырнадцатый выход которого подключен к объединенным вторым входам четвертого элемента И и третьего элемента И-НЕ, четвертый вход которого одновременно соединен со вторым входом шестого элемента И-НЕ и третьим выходом первого дешифратора, тринадцатый выход которого одновременно подключен к первым входам четвертого элемента И и первого элемента И-НЕ, объединенные второй и четвертый входы которого одновременно соединены с выходом первого элемента И и первым входом третьего элемента И, выход которого одновременно подключен к четвертому входу четвертого элемента И-НЕ и первому входу пятого элемента И-НЕ, второй вход которого одновременно соединен с первым входом шестого элемента И-НЕ и четвертым выходом первого дешифратора, шестой выход которого одновременно подключен к объединенным четвертым входам пятого и второго элементов И-НЕ, при этом седьмой выход первого дешифратора подключен к третьему входу второго элемента И-НЕ, а девятый выход подключен к третьему входу пятого элемента И-НЕ, выход второго элемента И одновременно подключен ко второму входу третьего элемента И, первому входу седьмого элемента И-НЕ и к объединенным четвертому и третьему входам шестого элемента И-НЕ, а выход четвертого элемента И подключен к третьему входу четвертого элемента И-НЕ, при этом вход второго блока извлечения квадратного корня соединен с выходом первого делителя, а выход подключен к первому входу третьего делителя, второй вход которого соединен с входной шиной, первые входы первого и второго амплитудных селекторов одновременно соединены с выходом нормирующего усилителя, а вторые входы соединены соответственно с первым и вторым выходами генератора ступенчатого напряжения, вход которого соединен с входной шиной, при этом выходы первого и второго амплитудных селекторов подключены соответственно к первому и второму входам первого вычитающего устройства, выход которого подключен к входу четвертого интегратора, выход которого одновременно подключен к входу логарифмического усилителя и второму входу третьего умножителя, первый вход которого соединен с выходом логарифмического усилителя, а выход подключен к входу пятого интегратора, выход которого подключен к входу блока вычисления экспоненциальной функции, выход которого подключен к первому входу четвертого делителя, второй вход которого соединен с входной шиной, а выход подключен к первому входу пятого делителя, второй вход которого соединен с выходом первого блока извлечения квадратного корня, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый, семнадцатый, восемнадцатый, девятнадцатый, двадцатый, двадцать первый, двадцать второй, двадцать третий, двадцать четвертый, двадцать пятый, двадцать шестой, двадцать седьмой, двадцать восьмой, двадцать девятый, тридцатый, тридцать первый, тридцать второй, тридцать третий и тридцать четвертый коммутаторы, вторые и третьи входы которых соединены соответственно с входными шинами, а объединенные первые входы соединены с первым входом тридцать пятого коммутатора, вторыми входами первого и второго ключей, двадцать восьмым входом индикатора и выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго компараторов, объединенные первые входы которых соединены с первым входом второго ключа и вторым входом тридцать пятого коммутатора, третий вход которого соединен с выходом пятого делителя, а выход подключен к объединенным первым входам двадцать седьмого, двадцать восьмого, двадцать девятого, тридцатого, тридцать первого, тридцать второго, тридцать третьего и тридцать четвертого компараторов, вторые входы которых соединены соответственно с выходами двадцать седьмого, двадцать восьмого, двадцать девятого, тридцатого, тридцать первого, тридцать второго, тридцать третьего и тридцать четвертого коммутаторов, при этом вторые входы третьего, четвертого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восемнадцатого компараторов соединены соответственно с выходами третьего, четвертого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восемнадцатого коммутаторов, а объединенные первые входы соединены третьим входом тридцать пятого коммутатора, при этом вторые входы пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого, двенадцатого, девятнадцатого, двадцатого, двадцать первого, двадцать второго, двадцать третьего, двадцать четвертого, двадцать пятого и двадцать шестого компараторов соединены соответственно с выходами пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого, двенадцатого, девятнадцатого, двадцатого, двадцать первого, двадцать второго, двадцать третьего, двадцать четвертого, двадцать пятого и двадцать шестого коммутаторов, а объединенные первые входы соединены с выходом третьего делителя, при этом выходы восьмого, девятого, десятого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого элементов И-НЕ соответственно подключены к шестнадцатому, семнадцатому, восемнадцатому, девятнадцатому, двадцатому, двадцать первому и двадцать второму входам индикатора, двенадцатый, тринадцатый, четырнадцатый и пятнадцатый входы которого соединены соответственно с первым, вторым, третьим и четвертым выходами второго коммутатора, пятый вход которого соединен с пятым входом первого коммутатора, а первый, второй, третий и четвертый входы соединены соответственно с первым, вторым, третьим и четвертым выходами третьего дешифратора, первый вход которого одновременно соединен с объединенными девятыми входами первого, второго, третьего и четвертого мультиплексоров, при этом второй вход третьего дешифратора одновременно соединен с объединенными десятыми входами первого, второго, третьего и четвертого мультиплексоров, а объединенные девятые и объединенные десятые входы третьего и четвертого регистров соединены соответственно с объединенными девятыми и объединенными десятыми входами первого и второго регистров, первый, второй, пятый и шестой входы третьего мультиплексора соединены соответственно с первым, пятым, вторым и шестым выходами третьего регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами девятнадцатого, двадцатого, двадцать первого, двадцать второго, двадцать третьего, двадцать четвертого, двадцать пятого и двадцать шестого компараторов, при этом третий, седьмой, четвертый и восьмой выходы третьего регистра подключены соответственно к первому, второму, пятому и шестому входам четвертого мультиплексора, третий, четвертый, седьмой и восьмой входы которого соединены соответственно с третьим, седьмым, четвертым и восьмым выходами четвертого регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами двадцать седьмого, двадцать восьмого, двадцать девятого, тридцатого, тридцать первого, тридцать второго, тридцать третьего и тридцать четвертого компараторов, а первый, пятый, второй и шестой выходы четвертого регистра подключены соответственно к третьему, четвертому, седьмому и восьмому входам третьего мультиплексора, первый и второй выходы которого подключены соответственно к первому и второму входам четвертого дешифратора, третий и четвертый входы которого соединены соответственно с первым и вторым выходами четвертого мультиплексора, второй выход четвертого дешифратора одновременно подключен к первым входам пятого и шестого элементов И, вторые входы которых соответственно соединены с пятым и восьмым выходами четвертого дешифратора, десятый выход которого подключен ко второму входу одиннадцатого элемента И-НЕ, первый вход которого одновременно соединен с первыми входами десятого и девятого элементов И-НЕ и двенадцатым выходом четвертого дешифратора, одиннадцатый выход которого одновременно подключен к объединенным второму входу четырнадцатого элемента И-НЕ, третьему входу десятого элемента И-НЕ и второму входу девятого элемента И-НЕ, при этом первый выход четвертого дешифратора подключен к четвертому входу четырнадцатого элемента И-НЕ, третий вход которого одновременно соединен с третьим входом восьмого элемента И-НЕ и пятнадцатым выходом четвертого дешифратора, четырнадцатый выход которого подключен к объединенным вторым входам восьмого элемента И и десятого элемента И-НЕ, четвертый вход которого одновременно соединен со вторым входом тринадцатого элемента И-НЕ и третьим выходом четвертого дешифратора, тринадцатый выход которого одновременно подключен к первым входам восьмого элемента И и восьмого элемента И-НЕ, объединенные второй и четвертый входы которого одновременно соединены с выходом пятого элемента И и первым входом седьмого элемента И, выход которого одновременно подключен к четвертому входу одиннадцатого элемента И-НЕ и первому входу двенадцатого элемента И-НЕ, второй вход которого одновременно соединен с первым входом тринадцатого элемента И-НЕ и четвертым выходом четвертого дешифратора, шестой выход которого одновременно подключен к объединенным четвертым входам двенадцатого и девятого элементов И-НЕ, при этом седьмой выход четвертого дешифратора подключен к третьему входу девятого элемента И-НЕ, а девятый выход подключен к третьему входу двенадцатого элемента И-НЕ, выход шестого элемента И одновременно подключен ко второму входу седьмого элемента И, первому входу четырнадцатого элемента И-НЕ и объединенным четвертому и третьему входам тринадцатого элемента И-НЕ, а выход восьмого элемента И подключен к третьему входу одиннадцатого элемента И-НЕ, при этом выход второго ключа подключен к объединенным первым входам четвертого и пятого умножителей, вторые входы которых соединены соответственно с входными шинами, а выходы подключены соответственно к входу второго блока вычисления экспоненциальной функции и первому входу второго вычитающего устройства, второй вход которого соединен с входной шиной, а выход подключен к двадцать пятому входу индикатора, двадцать третий и двадцать четвертый входы которого соединены соответственно с выходами шестого и седьмого умножителей, вторые входы которых соединены соответственно с входными шинами, а первые входы соединены соответственно с выходами второго блока вычисления экспоненциальной функции и шестого делителя, первый вход которого соединен с входной шиной, а второй вход соединен с выходом второго блока вычисления экспоненциальной функции, при этом двадцать шестой и двадцать седьмой входы индикатора соединены соответственно с выходами сумматора и четвертого вычитающего устройства, первый вход которого соединен с входной шиной, а второй вход соединен с выходом девятого умножителя, второй вход которого соединен с входной шиной, а первый вход соединен с объединенными выходом первого ключа, входом четвертого детектора и первым входом восьмого умножителя, второй вход которого соединен с входной шиной, а выход подключен ко второму входу третьего вычитающего устройства, первый вход которого соединен с входной шиной, а выход подключен к первому входу сумматора, второй вход которого соединен с выходом десятого умножителя, первый вход которого соединен с входной шиной, а второй вход соединен с выходом четвертого детектора.

Недостатком устройства-прототипа является относительно низкая точность определения параметра m случайного процесса с распределением Накагами. Относительно низкая точность обусловлена тем, что реализованное в устройстве-прототипе выражение для определения параметр m случайного процесса с распределением Накагами справедливо не для всех значений коэффициента асимметрии закона распределения случайной величины [1].

Целью заявляемого технического решения является разработка устройства определения параметров случайных процессов, обеспечивающего повышение точности определения параметра m случайного процесса с распределением Накагами.

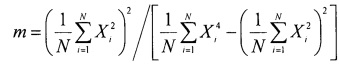

Поставленная цель достигается за счет использования для определения параметра m случайного процесса с распределением Накагами метода моментов амплитуд.

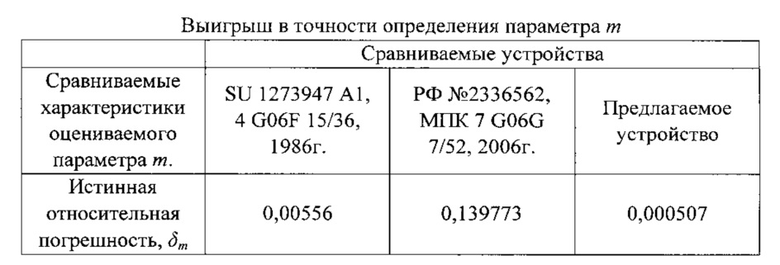

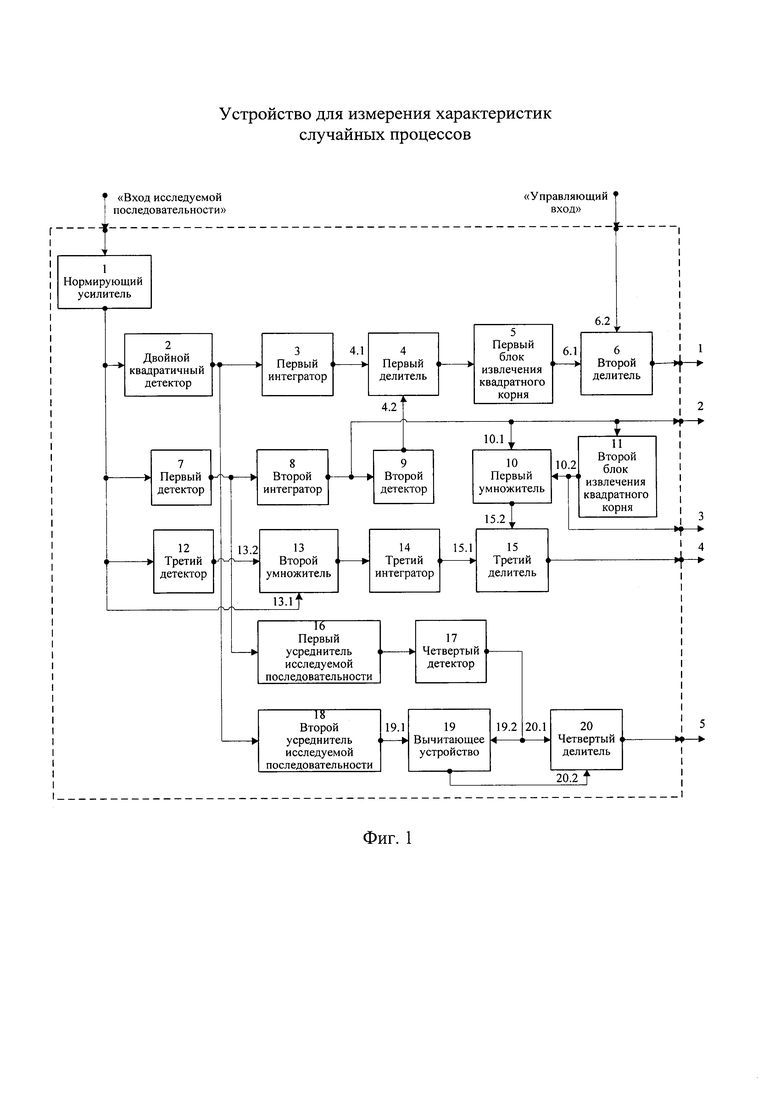

Сущность изобретения поясняется Фиг.1, на которой представлена структурная электрическая схема устройства.

Указанный технический результат достигается тем, что в известное устройство для измерения характеристик случайных процессов, содержащее нормирующий усилитель (1), вход которого является "входом исследуемой последовательности" устройства, а выход подключен к входам двойного квадратичного детектора (2), первого детектора (7), третьего детектора (12) и к первому входу второго умножителя (13). Выход двойного квадратичного детектора (2) подключен к входу первого интегратора (3), выход которого подключен к первому входу первого делителя (4), второй вход которого подключен к выходу второго детектора (9). Выход первого делителя (4) подключен к входу первого блока извлечения квадратного корня (5), выход которого подключен к первому входу второго делителя (6), второй вход которого является "управляющим входом" устройства. Выход первого детектора (7) подключен к входу второго интегратора (8), выход которого подключен к входам второго детектора (9), второго блока извлечения квадратного корня (11) и к первому входу первого умножителя (10). Выход третьего детектора (12) подключен ко второму входу второго умножителя (13), выход которого подключен к входу третьего интегратора (14), выход которого подключен к первому входу третьего делителя (15), второй вход которого подключен к выходу первого умножителя (10), второй вход которого подключен к выходу второго блока извлечения квадратного корня (11). Дополнительно введены первый усреднитель исследуемой последовательности (16), четвертый детектор (17), второй усреднитель исследуемой последовательности (18), вычитающее устройство (19) и четвертый делитель (20), выход которого является пятым выходом устройства. Вход первого усреднителя исследуемой последовательности (16) подключен к выходу первого детектора (7), а выход подключен к входу четвертого детектора (17). Вход второго усреднителя исследуемой последовательности (18) подключен к выходу двойного квадратичного детектора (2), а выход подключен к первому входу вычитающего устройства (19), второй вход которого подключен к входу четвертого делителя (20) и выходу четвертого детектора (17). выход вычитающего устройства (19) подключен ко второму входу четвертого делителя (20), причем выходы второго делителя (6), второго интегратора (8), второго блока извлечения квадратного корня (11) и третьего делителя (15) являются соответственно первым, вторым, третьим и четвертым выходами устройства.

Благодаря указанной новой совокупности существенных признаков в устройстве определяются начальные моменты второго и четвертого порядка, что и указывает на возможность достижения технического результата.

Заявленное устройство, структурная схема которого показана на рисунке состоит из нормирующего усилителя 1, двойного квадратичного детектора 2, первого интегратора 3, первого делителя 4, первого блока извлечения квадратного корня 5, второго делителя 6, первого детектора 7, второго интегратора 8, второго детектора 9, первого умножителя 10, второго блока извлечения квадратного корня 11, третьего детектора 12, второго умножителя 13, третьего интегратора 14, третьего делителя 15, первого усреднителя исследуемой последовательности 16, четвертого детектора 17, второго усреднителя исследуемой последовательности 18, вычитающего устройства 19, четвертого делителя 20.

Нормирующий усилитель 1 предназначен для усиления и ограничения исследуемой последовательности. Нормирующий усилитель 1 известен и описан в [2].

Двойной квадратичный детектор 2 предназначен для формирования сигнала, пропорционального четвертой степени исследуемой последовательности. Двойной квадратичный детектор 2 известен и описан в патенте SU №744655, G06J 3/00, 30.06.1980 г.

Первый и третий детекторы 7, 12 предназначены для формирования сигналов, пропорциональных квадрату исследуемой последовательности. Первый и третий детекторы 7, 12 известны и описаны патенте SU №460548, G06G 7/20, 15.02.1975 г.

Первый интегратор 3 предназначен для формирования сигналов, пропорциональных центральному моменту случайной величины четвертого порядка. Первый интегратор 3 известен и описан в патенте SU №1195362, G06G 7/186,30.11.1983 г.

Первый делитель 4 предназначен для формирования сигнала, пропорционального эксцессу. Первый делитель 4 известен и описан в патенте SU №1064279, G06F 7/52, 30.12.1983 г.

Первый блок извлечения квадратного корня 5 предназначен для формирования сигнала, пропорционального квадратному корню из эксцесса. Первый блок извлечения квадратного корня 5 известен и описан в патенте SU №1005083, G06G 7/20, 19.03.1983 г.

Второй делитель 6 предназначен для формирования сигнала пропорционального контрэксцессу. Второй делитель 6 известен и описан в патенте SU №1064279, G06F 7/52, 30.12.1983 г.

Второй интегратор 8 предназначен для формирования сигнала, пропорционального дисперсии случайной величины. Второй интегратор 8 известен и описан в патенте SU №1195362, G06G 7/186, 30.11.1983 г.

Второй детектор 9 предназначен для формирования сигнала, пропорционального квадрату дисперсии случайной величины. Второй детектор 9 известен и описан в патенте SU №460548, G06G 7/20, 15.02.1975 г.

Первый умножитель 10 предназначен для формирования сигнала, пропорционального кубу среднего квадратического отклонения случайной величины. Первый умножитель 10 известен и описан в патенте SU №918953, G06G 7/16, 07.04.1982 г.

Второй блок извлечения квадратного корня 11 предназначен для формирования сигнала, пропорционального среднему квадратическому отклонению случайной величины. Второй блок извлечения квадратного корня 11 известен и описан в патенте SU №1005083, G06G 7/20, 19.03.1983 г.

Второй умножитель 13 предназначен для формирования сигнала, пропорционального кубу исследуемой последовательности. Второй умножитель 13 известен и описан в патенте SU №918953, G06G 7/16, 07.04.1982 г.

Третий интегратор 14 предназначен для формирования сигнала, пропорционального центральному моменту случайной величины третьего порядка. Третий интегратор 14 известен и описан в патенте SU №1195362, G06G 7/186,30.11.1983 г.

Третий делитель 15 предназначен для формирования сигнала, пропорционального коэффициенту асимметрии. Третий делитель 15 известен и описан в патенте SU №1064279, G06F 7/52, 30.12.1983 г.

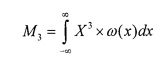

Первый усреднитель исследуемой последовательности 16 предназначен для формирования сигнала, пропорционального начальному моменту случайной величины второго порядка. Первый усреднитель исследуемой последовательности 16 известен и описан в патенте SU 1322313 А1, 4 G06F 15/36 07.07.1987 г., Бюл. №25.

Четвертый детектор 17 предназначен для формирования сигнала, пропорционального квадрату начального момента случайной величины второго порядка. Четвертый детектор 17 известен и описан в патенте SU №460548, G06G 7/20, 15.02.1975 г.

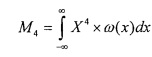

Второй усреднитель исследуемой последовательности 18 предназначен для формирования сигнала, пропорционального начальному моменту случайной величины четвертого порядка. Первый усреднитель исследуемой последовательности 18 известен и описан в патенте SU 1322313 А1, 4 G06F 15/36 07.07.1987 г., Бюл. №25.

Вычитающее устройство 19 предназначено для формирования сигнала, пропорционального разнице начального момента случайной величины четвертого порядка и квадрата начального момента случайной величины второго порядка. Вычитающее устройство 19 может быть выполнена по схеме, предложенной в патенте SU 1070568 A, G06G 7/14 30.01.1984 г., Бюл. №4.

Четвертый делитель 20 предназначен для формирования сигнала, пропорционального параметру m случайного процесса с распределение Накагами. Четвертый делитель 20 известен и описан в патенте SU №1064279, G06F 7/52,30.12.1983 г.

Заявляемое устройство для измерения случайных процессов работает следующим образом.

На "вход исследуемой последовательности" устройства, который является входом нормирующего усилителя 1, поступает исследуемая случайная последовательность X ,характеризующая случайный процесс, где усиливается, ограничивается и с выхода поступает на входы двойного квадратичного детектора 2, первого детектора 7, третьего детектора 12 и на первый вход второго умножителя 13. С выхода двойного квадратичного детектора 2 сигнал, описывающий исследуемую последовательность в четвертой степени X4, поступает на вход первого интегратора 3 и второго усреднителя исследуемой последовательности 18. На выходе первого интегратора 3 формируется сигнал, пропорциональный центральному моменту случайной величины четвертого порядка

,

,

где ω(х) - плотность распределения вероятностей исследуемого процесса. Сигнал, пропорциональный центральному моменту случайной величины четвертого порядка, поступает на первый вход первого делителя 4. С выхода первого детектора 7 сигнал, описывающий исследуемую последовательность во второй степени X2, поступает на входы второго интеграторы 8 и первого усреднителя исследуемой последовательности 16. На выходе второго интеграторы 8 формируется сигнал, пропорциональный дисперсии случайной величины

,

,

который поступает на вход второго детектора 9, первый вход первого умножителя 10, вход второго блока извлечения квадратного корня 11 и на второй выход устройства. На выходе второго детектора 9 формируется сигнал, пропорциональный квадрату дисперсии случайной величины, поступает на второй вход первого делителя 4, на выходе которого формируется сигнал, пропорциональный эксцессу

,

,

который поступает на вход первого блока извлечения квадратного корня 5. С выхода блока извлечения квадратного корня 5 сигнал, пропорциональный эксцессу, поступает на первый вход второго делителя 6. На "управляющий вход" устройства, который является вторым входом второго делителя 6, поступает сигнал, пропорциональный единице. На выходе второго делителя 6 формируется сигнал, пропорциональный контрэксцессу,

,

,

который поступает на первый выход устройства. С выхода второго блока извлечения квадратного корня 11 сигнал, пропорциональный среднему квадратическому отклонению случайной величины

,

,

поступает на второй вход первого умножителя 10 и на третий выход устройства. С выхода первого умножителя 10 сигнал, пропорциональный кубу среднего квадратического отклонения случайной величины, поступает на второй вход третьего делителя 15. С выхода третьего детектора 12 сигнал, описывающий исследуемую последовательность во второй степени X2, поступает на второй вход второго умножителя 13, с выхода которого сигнал, описывающий исследуемую последовательность в третей степени X3, поступает на вход третьего интегратора 14, на выходе которого формируется сигнал, пропорциональный центральному моменту случайной величины третьего порядка,

,

,

который подается на первый вход третьего делителя 15. На выходе третьего делителя 15 формируется сигнал, пропорциональный коэффициенту асимметрии,

,

,

который подается на четвертый выход устройства. На выходе первого усреднителя исследуемой последовательности 16 формируется сигнал, пропорциональный начальному моменту случайной величины второго порядка, который подается на вход четвертого детектора 17. С выхода четвертого детектора 17 сигнал, пропорциональный квадрату начального момента случайной величины второго порядка, поступает на второй вход вычитающего устройства 19 и на первый вход четвертого делителя 20. На выходе второго усреднителя исследуемой последовательности 18 формируется сигнал, пропорциональный начальному моменту случайной величины четвертого порядка, который поступает на первый вход вычитающего устройства 19. На выходе вычитающего устройства 19 формируется сигнал, пропорциональный разности начального момента случайной величины четвертого порядка и квадрата начального момента случайной величины второго порядка, который подается на второй вход четвертого делителя 20, на выходе которого формируется сигнал, пропорциональный параметру m случайного процесса с распределением Накагами,

,

,

где Xi - i-й член исследуемой последовательности, N - объем исследуемой последовательности. Сигнал, пропорциональный параметру m случайного процесса с распределением Накагами поступает на пятый выход устройства.

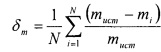

Предлагаемое устройство позволяет повысить точность определения параметра m случайного процесса с распределением Накагами за счет реализации метода моментов амплитуд. В качестве показателя, описывающего точность определения параметра m случайного процесса с распределением Накагами, используется истинная относительная погрешность оцениваемого параметра m [3], которая вычисляется в соответствии с выражением

,

,

где  - истинное значение параметра m случайного процесса с распределением Накагами, N - количество измерений, mi - оценочное значение параметра m случайного процесса с распределением Накагами, i=[1, 2, 3, …, N].

- истинное значение параметра m случайного процесса с распределением Накагами, N - количество измерений, mi - оценочное значение параметра m случайного процесса с распределением Накагами, i=[1, 2, 3, …, N].

Значения истинной относительной погрешности получены при анализе выборок из значений параметра m случайного процесса с распределением Накагами (объем выборки N=50, истинное значении параметра m=1,5) с использованием вычислительной среды MathCAD 15.

Источники информации

1. И.И. Сытько. Определение характеристик случайных процессов, распределенных по закону Накагами // Компоненты и технологии. - 2014. - №1. - С. 172-173.

2. А.Г. Алексенко. Е.А. Коломбет. Г.И. Стародуб. Применение прецизионных аналоговых микросхем. - М.: Радио и связь. 1985 г.

3. Справочник по математике для инженеров и учащихся втузов. Бронштейн И.Н., Семендяев К.А. - М: Наука. Главная редакция физико-математической литературы. 1981 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2004 |

|

RU2280278C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2006 |

|

RU2336562C2 |

| Устройство для контроля аппаратуры управления электростанций | 1983 |

|

SU1201799A1 |

| УСТРОЙСТВО ОЦЕНИВАНИЯ ПАРАМЕТРОВ АСИНХРОННОГО ДВИГАТЕЛЯ | 2010 |

|

RU2426219C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1999 |

|

RU2168763C2 |

| Комплексный измеритель дальности | 1986 |

|

SU1396103A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1995 |

|

RU2110806C1 |

| УСТРОЙСТВО ОЦЕНИВАНИЯ ПАРАМЕТРОВ ЭЛЕКТРОДВИГАТЕЛЯ | 2009 |

|

RU2392731C1 |

| Устройство для неразрушающего контроля материалов и изделий | 1989 |

|

SU1711046A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ НЕКОГЕРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ СВЕРХШИРОКОПОЛОСНЫХ КВАЗИРАДИОСИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 2020 |

|

RU2756974C1 |

Изобретение относится к области радиоизмерений и может использоваться для определения характеристик случайного процесса. Достигаемый технический результат - повышение точности определения параметра m случайного процесса с распределением Накагами. Такой результат достигается тем, что в устройство для измерения характеристик случайных процессов дополнительно введены первый усреднитель исследуемой последовательности (16), четвертый детектор (17), второй усреднитель исследуемой последовательности (18), вычитающее устройство (19) и четвертый делитель (20), выход которого является пятым выходом устройства. 1 ил.

Устройство для измерения характеристик случайных процессов, содержащее нормирующий усилитель, вход которого является "входом исследуемой последовательности" устройства, а выход подключен к входам двойного квадратичного детектора, первого детектора, третьего детектора и к первому входу второго умножителя, выход двойного квадратичного детектора подключен к входу первого интегратора, выход которого подключен к первому входу первого делителя, второй вход которого подключен к выходу второго детектора, выход первого делителя подключен к входу первого блока извлечения квадратного корня, выход которого подключен к первому входу второго делителя, второй вход которого является "управляющим входом" устройства, выход первого детектора подключен к входу второго интегратора, выход которого подключен к входам второго детектора, второго блока извлечения квадратного корня и к первому входу первого умножителя, выход третьего детектора подключен ко второму входу второго умножителя, выход которого подключен к входу третьего интегратора, выход которого подключен к первому входу третьего делителя, второй вход которого подключен к выходу первого умножителя, второй вход которого подключен к выходу второго блока извлечения квадратного корня, отличающееся тем, что дополнительно введены первый усреднитель исследуемой последовательности, четвертый детектор, второй усреднитель исследуемой последовательности, вычитающее устройство и четвертый делитель, выход которого является пятым выходом устройства, вход первого усреднителя исследуемой последовательности подключен к выходу первого детектора, а выход подключен к входу четвертого детектора, вход второго усреднителя исследуемой последовательности подключен к выходу двойного квадратичного детектора, а выход подключен к первому входу вычитающего устройства, второй вход которого подключен к входу четвертого делителя и выходу четвертого детектора, выход вычитающего устройства подключен ко второму входу четвертого делителя, причем выходы второго делителя, второго интегратора, второго блока извлечения квадратного корня и третьего делителя являются соответственно первым, вторым, третьим и четвертым выходами устройства.

| Устройство для оценки параметра " " случайного процесса распределением накагами | 1974 |

|

SU481907A1 |

| Устройство для определения характеристик случайных процессов | 1985 |

|

SU1273947A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1999 |

|

RU2168763C2 |

| CN 104052557 A, 17.09.2014 | |||

| US 7650261 B2, 19.01.2010. | |||

Авторы

Даты

2017-03-21—Публикация

2016-04-14—Подача