но с входами третьего, четвертого и пятого компараторов,выходы которых являются соответственно третьим четвертым и пятым выходами устройства, причем третий вычислитель содержит первый умножитель, вход и выход которого являются соответственно первыми входом и выходом данного вычислителя, включенные последовательно второй умножитель, вход которого является пятым в ходом третьего вьиислителя, первые сумматор и делитель, третий умножитель другой вход которого соединен с его первым входом, вторые делитель и сумматор, четвертый умножитель ипервый инвертор, выход которого является вторым выходом данного вычислителя, пятый умножитель, вход которого является четвертым входом данного вычислителя, а выход подключен к другому входу первого сумматора, включенные последовательно шестой умножитель, соединенньй входом с входом второго умножителя, третьи сумматор и делитель, другой вход которого является вторым входом третьего вычислителя, седьмой умножитель, четвертый сумматор и восьмой умножитель, выход которого является третьим выходом третьего вычислителя, девятый умножитель, вход и выход которого соединены соответственно с входом пятого умножителя и другим входом третьего сумматора, пятый сумматор, один вход которого подключен к выходу первого делителя другой вход соединен с другими входами первого и второго делителей и второго сумматора и является вторым входом третьего вычислителя, десятый умножитель, подключенный входом и выходом соответственно к выходу птого и другому входу четвертого сумматоров, включенные последовательно четвертый делитель, вход которого является третьим входом третьего вычислителя, одиннадцатый умножитель, первый вход которого соединен с другим входом седьмого умножителя, а второй вход - с вькодом пятого сумматора, шестой сумматор и двенадцатый умножитель, выход которого является четвертым выходом третьего вьмислителя, включенные последовательно пятый делитель, соединенный входом с входом четвертого делителя, тринадцатый умножитель, первый вход которого соединен

799

с другим входом десятого умножителя а второй вход - с выходом третьего делителя, и четырнадцатый умножител соединенный выходом с другим входом шестого сумматора, включенные последовательно пятнадцатый умножитель, другой вход которого соединен с его первым входом и входом четвертого делителя, шестнадцатый умножитель, соединенный другим входом с вторьм входом третьего делителя, и семнадцатый умножитель, выход которого является пятым выходом третьего вычислителя, включенные последовательно восемнадцатьй умножитель, другой вход которого соединен с его первьм входом и вторым входом третьего делителя, девятнадцатьй умножитель, соединенньй другим входом с входом четвертого делителя, и двадцатый умножитель, выход которого является шестым выходом третьего вычислителя включенные последовательно двадцать первый умножитель, подключенный входом к входу девятого умножителя, и второй инвертор, выход которого является седьмым выходом третьего вычислителя, и включенные последовательно двадцать второй умножитель, соединенный входом с входом шестого умножителя, и третий инвертор, выход которого является восьмым выходом третьего вычислителя, четвертьй вычМслитель содержит включенные последовательно двадцать третий умножитель, другой вход которого соединен с его первым входом и является четвертым входом четвертого вычислителя, двадцать четвертый умножитель, седьмой и восьмой сумматоры и девятый сумматор, выход которого является первым вькодом четвертого вычислителя, последовательно соединенные двадцать пятый умножитель, другой вход которого соединен с его первым входом и является третьим входом четвертого вычислителя, и двадцать шестой умножитель, выход которого соединен с другим входом седьмого сумматора, последовательно соединенные двадцать седьмой умножитель, другой вход которого соединен с его первым входом и является вторым входом четвертого вычислителя, и двадцать восьмой умножитель, выход которого соединен с другим входом восьмого сумматора, последовательно соединенные двадцать девятый умножитель, другой вход которого соединен с его первым входом и является первым входом четвертого вычислителя, и тридцатый умножитель, выход которого соединен с другим входом девятого сумматора, последовательно .соединенные тридцать первьй умножитель, другой вход которого соединен с его первымвходом и является восьмым входом четвертого iумножителя, тридцать второй умножитель, десятый и одиннадцатый сумматоры и двенадцатый сумматор, выход ;которого является третьим выходом четвертого; вычислителя, последова|тельно соединенные тридцать третий :умножитель, другой вход которого ; соединен с его первым входом и является седьмым . входом четвертого .вычислителя, и тридцать четвертый умножитель, выход .которого соединен с другим входом десятого сумматора, последовательно соединенные тридцать пятый умножитель, другой вход ; которого соединен с его первым входом и является шестым входом четвертого вычислителя, и тридцать шестой умножитель, выход которого соединен с другим входом одиннадцатого сумматора, последовательно с.оединенные тридцать седьмой умножитель, другой вход которого соединен с , его первым- входрм и является пятым входом .четвертого вычислителя, и тридцать восьмой умножитель, выход которого соединен с другим входом двенадцатого сумматораi последовательно соединеннью тридцать девятый умножитель, цервый и второй входь которого соединены соответственно с входами двадцать третьего и тридцать первого умножителей, сороковой умножитель, тринадцатый сумматор и четырнадцатый сумматор, выход которого, является вторым выходом четвертого вычислителя, последовательно соединенные сорок первый.умножитель, первый и второй входы которого соединены соответственно с входами двадцать пятого и тридцать третьего умножителей, и сорок второй умножитель, выход которого соединен с другим входом -тринадцатого сумматора, последовательно соединенные сорок третий умножитель, первьш и второй входы которого соединены соответственно с входами двадцать седьмого Iи тридцать седьмого умножителей, и сорок четвертый згмножитель, выход iкоторого соединен с другим входом четырнадцатого сумматора, пятый вычислитель содержит последовательно соединенные сорок пятый умножитель, другой вход которого соединен с его первым входом и является третьим входом пятого вычислителя, пятнадцатьй сумматор и шестой делитель, другой вход которого подключен к первому входу пятого вычислителя, а выход является вторым выходом пятого вычислителя, сорок шестой умножитель, первый и второй входы которого являются соответственно первым и вторым входами пятого вычислителя, а выход соединен с другим входо 1 пятнадцатого сумматора, седьмой Делит.ель, первый и второй входы которого соединены соответственно с вторым входом сорок шестого умножителя и выходом пятнадцатого сумматора, а выход .-является первым выходом пятого вычислителя, последова:тельно соединенные восьмой делитель, первый и второй входы которого соединены соответственно с входом сорок пятого умножителя и выходом пятнадцатого сумматора, и четвертый инвертор, выход которого является третьим выходом пятого вычи.слителя, шестой вычислитель- содержит последовательно соединенные сорок седьмой умножитель, первый и второй входы которого являются соответственно одиннадцатым и тринадцатым входами шестого вычислителя, шестнадцатьй сумматор, сорок восьмой умножитель, другой вход которого является первым входом шестого вычислителя и сорок девятьй умножитель, выход которого является первьш выходом шестого вычислителя, пятидесятый умножитель, первый и кторой входы которого являются.соответственно девять и двенадцатым входами шестого, вычислителя, а выход соединен с другим входом шестнадцатого сумматора, последовательно соединённые пятьдесят первый умножитель, первый и второй входы-которот го являются соответственно пятым и десятым входами шестого вычислителя, семнадцатый сумматор, пятьдесят второй умножитель, другой вход которого соединен с вторьм входом сорок седьмого умножителя, восемнадцатый сумматор и пятьдесят третий умрожитель, выход которого является вторым выходом шестого вычислителя, пятьдесят четвертый умножитель, первый

и второй входы которого подключены соответственно к второму и одиннадцатому входам шестого вычислителя, а выход соединен с другим входом . семнадцатого сумматора, последовательно Соединенные пятьдесят пятый умножитешь, первый и второй входы которого подключены соответственно к пятому и одиннадцатому входам шестого вычислителя, восемнадцатый сумматор и пятьдесят шестой умножитель, другой вход которого соединен с вторым входом пятидесятого умножителя, а выход - с другим входом восемнадцатого сумматора, пятьдесят седьмой умножитель, первь и второй входы которого подключены соответственно к второму и девятому входам шестого вьиислителя, а выход соединен с другим входом восемнадцатого сумматора, последовательно соединенные пятьдесят восьмой умножитель, первый и второй входы которого подключены соответственно к десятому и тринадцатому входам шестого вычислителя, девятнадцатый сумматор, пятьдесят девятый умножитель, другой вход которого подключен к шестомувходу шестого вычислителя, и шестидесятый умножитель, выход которого является третьим выходом шестого вычислителя, шестьдесят первый умножитель, первый и второй входы которого подключены соответственно к девятому и двенадцатому входам шестого умножителя, а выход соединен с другим входом девятнадцатого сумматора, последовательно соединенные шестьдесят второй умножитель, первый и второй входы которого подключены соответственно к седьмому и десятому входам шестого вычислителя, двадцатьй сумматор, шестьдесят третий умножитель, другой вход которого соединен с вторым входом сорок седьмого умножителя, двадцать первьй сумматор и шестьдесят четвертьм умножитель, выход которого является четвертым выходом шестого вычислителя, шестьдесят пятый умножитель, первый и второй входи которого подключены соответственно к третьему и одиннадцатому входам

01799

шестого вычислителя, а выход соединен с другим входом двадцатого сумматора, последовательно соединенные шестьдесят шесто умножитель, первый и второй входы которого под-, ключены соответственно к седьмому и одиннадцатому входам шестого вычислителя, двадцать второй сумматор, шестьдесят седьмой умножитель, другой вход которого соединен с вторьм входом пятидесятого умножителя, а выход - с другим входом двадцать первого сумматора, шестьдесят восьмой умножитель, первьй и второй входы которого подключены соответственно к третьему и девятому входам шестого вычислителя, а выход соединен с другим входом двадцать второго сумматора, последовательно соединенные шестьдесят девятьй умножитель, первый и второй входы которого подключены соответственно к восьмому и десятому входам шестого вычислителя, двадцать третий сумматор, семидесятый умножитель, другой вход которого соединен с вторым входом сорок седьмого умножителя, двадцать четвертый сумматор и семьдесят первый умножитель, выход которого является пятым выходом шестого вычислителя, семьдесят второй умножитель, первый и второй входы которого подключены соответственно к четвертому и одиннадцатому входам- шестого вычислителя, а выход соединен с другим входом двадцать третьего сумматора, последовательно соединенные семьдесят третий умножитель, первьй и второй входь1 которого подключены соответственно к восьмому и одиннадцатому входам шестого вычислителя, двадцать пятый сумматор и семьдесят четвертый умножитель, другой вход которого соединен с вторым входом пятидесятого умножителя, а выход - с другим входом двадцать четвертого сз мматора, и семьдесят пятьй умножитель, первьй и второй входы которого подключены соответственно к четвертому и девятому входам шестого вычислителя, а выход соединен с другим входом двадцать пятого сум матора.

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в АСУ ТП электростанций.

Цель изобретения - расширение .области применения устройства путем селекции источника параметрического отказа.

На фиг. I показана функциональная схема устройства; на фиг. 2-7 функциональные схемы .соответственно первого -. шестого вычислителей соответственно.

Устройство содержит первый 1 и. второй 2 вьиислители, генератор 3 татовых .импульсов (таймер), первый 4 ,и второй 5 интеграторы ;.со сбросом) первый 6 и второй 7 компараторы (синализаторы отклонений), блок 8 вычислителей, содержащий третий 9, четвертый 10, пятый 11 и шестой 12 вычислители, третий 13, четвертый 14 и пятый 15 интеграторы (со сбросом), а также третий 16, .четвертый 17 и пятый 18 компараторы (сигнализаторы отклонений).

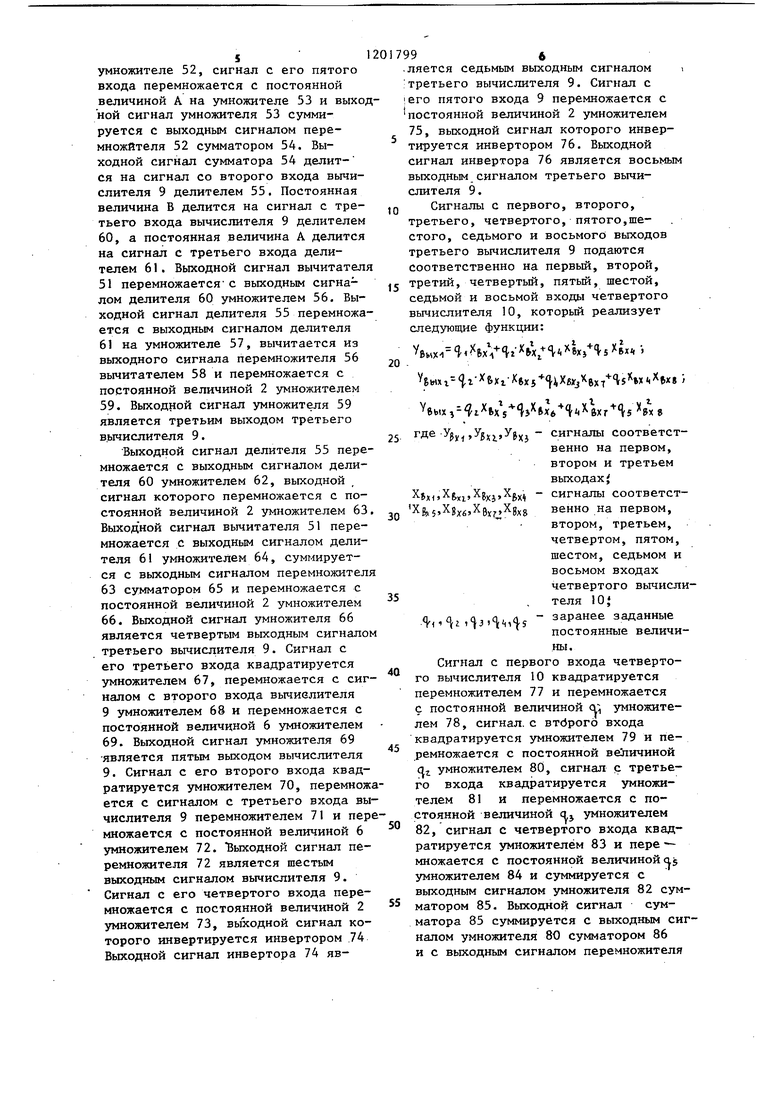

Первый вычислитель С фиг. 2). образуют умножители 19-21, - сумматор 22, делитель 23, сумматор (вычитатель) 24, умножители 25-21, .сумматор (вычитатель) 28, делитель 29, умножитель 30 и сумматор 31 и сумматор (вычитатель) 32. j

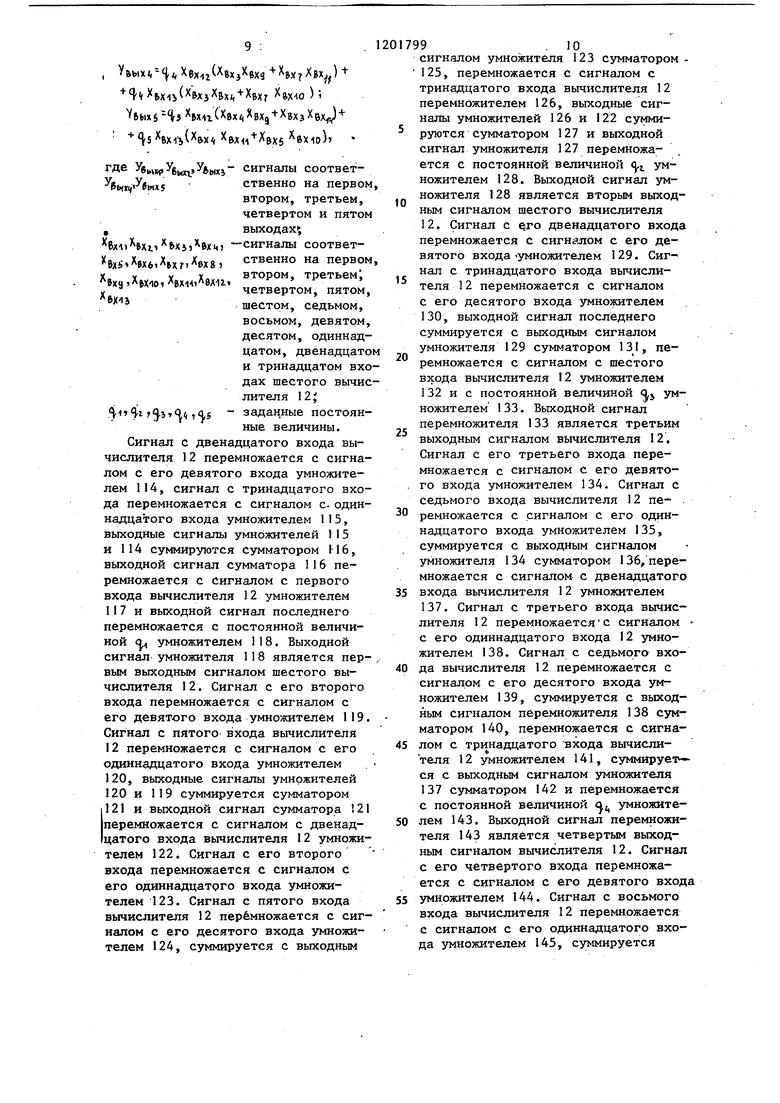

Второй вычислитель (фиг. 3) состоит из умножителей 33-38, сумматора 39 и сумматора (вычитателя) 40.

Третий вычислитель (фиг. 4) содержит умножители 41-43, сумматор 44, делитель 45, умножитель 46, делитель 47, сумматор (вычитатель) 48 умножитель 49, ин вертор 50, матор ( вычитатель) 51, умножители 52 и 53, сумматор 54, делитель 55, умножители 56 и 57, сумматор (вычитатель; 58, умножитель 59, делители 60 и 61, умножители , сумматор 65, умножители 66-73, инвертор 74, умножитель 75 и инвертор 76.

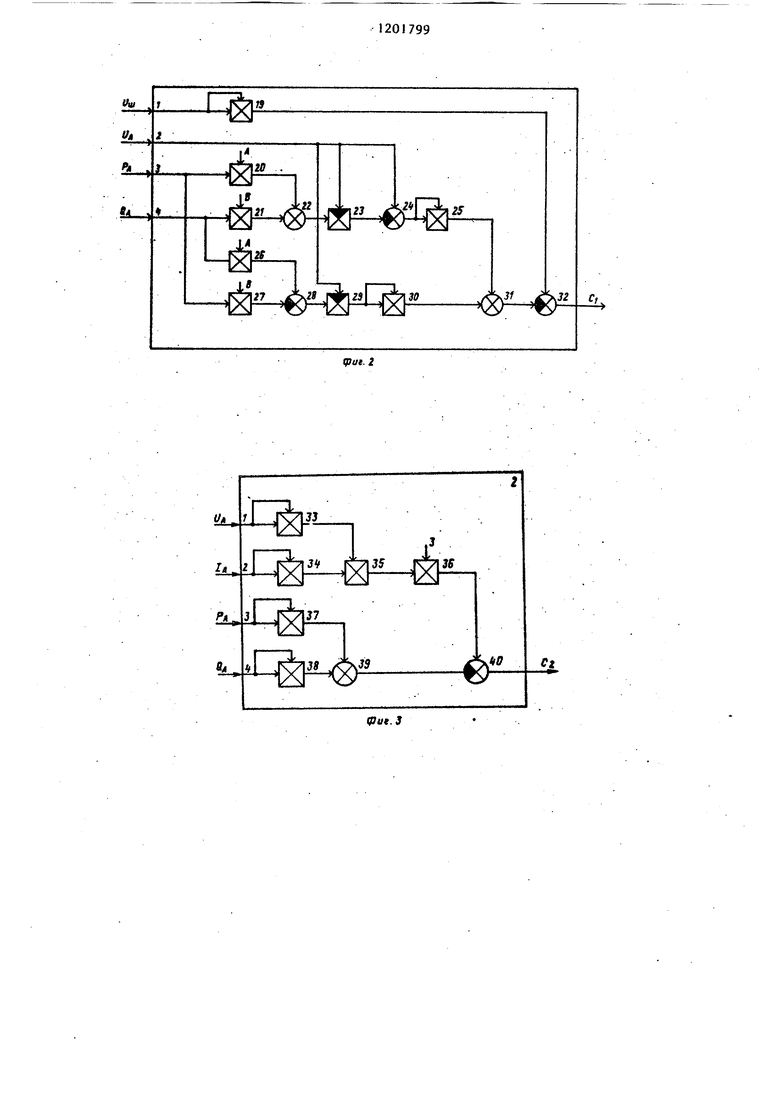

Четвертый вычислитель (фиг. 5) образуют умножители 77-84, сумматоры 85-87, умножителш 88-93, сумматоры 94 и 95, умножители,96-103 и

сумматоры 104-106.

I

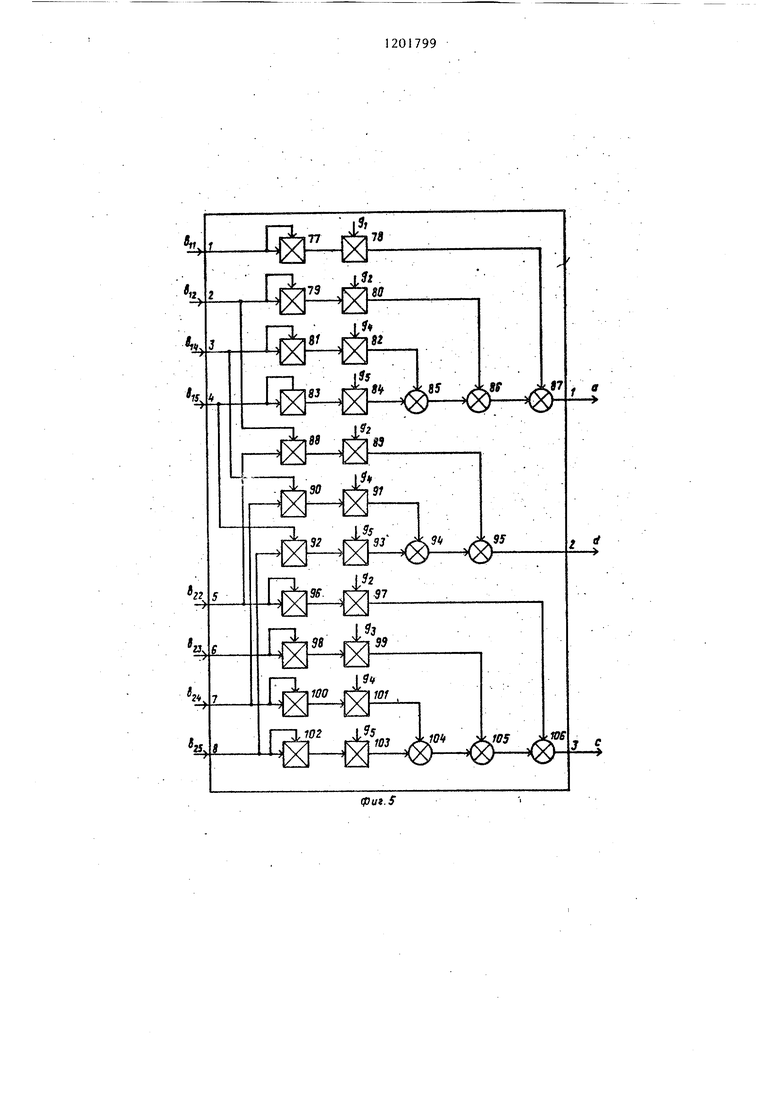

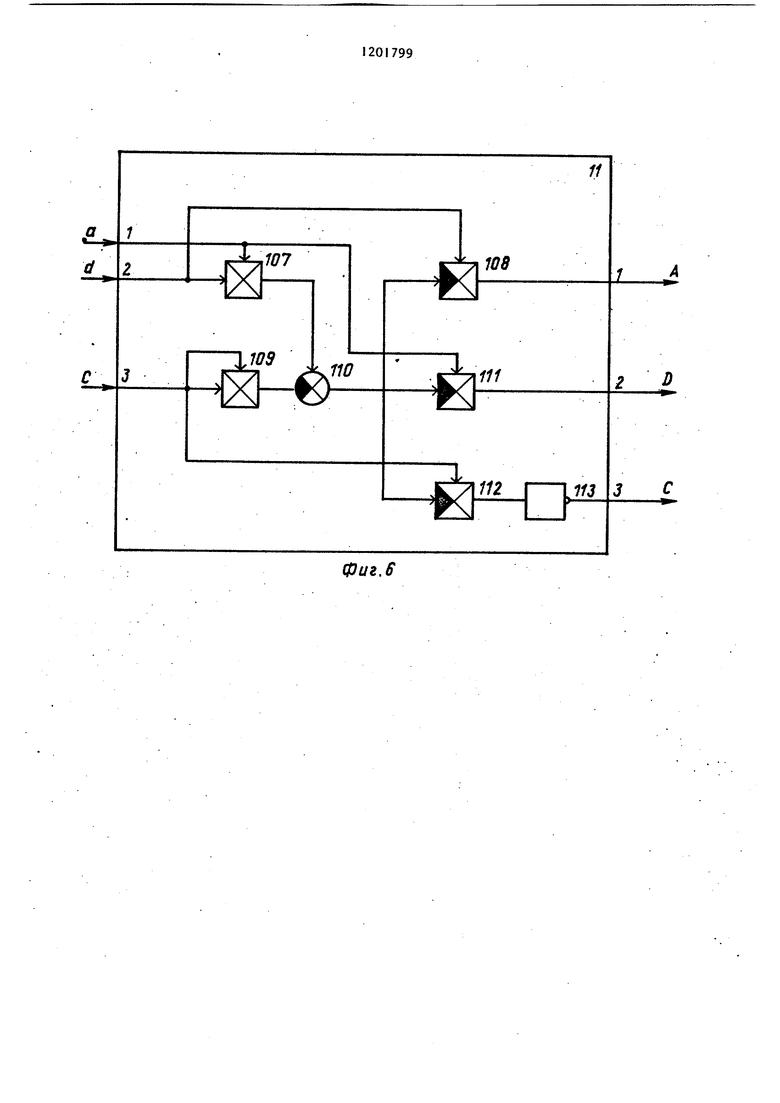

Лятый вь1числитель (фиг. Ь} .состоит из умножителя 107, делителя 108, умножителя 10, сумматора Свычитателя) ПО, делителей 111 и 112 и инвертора 113.

Шестой вычислитель (фиг. 7} содержит умножители 114 и 115, сумматор 116, умножители 117-120, сумматор 121, умножители 122-124, сумматор

125, умножитель 126, сумматор 127, умножители 128-130, сумматор 131, умножители 132-135, сумматор 136, умножители 137-139, сумматор 140, умножитель 141, сумматор 142, умножители 143-145, сумматор 146, умножители 147-149, сумматор 150, умножитель 151, сумматор 152 и умножитель 153.

Устройство работает следующим

образом.

/.

На первый, второй, третий, четвертый входы первого вычислителя 1 подаются измеренные аналоговые

сигналы .соответственно напряжения шин Uuj, напряжения U, активной . и реактивной Q мощностей агрегата. Первый вычислитель 1 реализует функцию:

V у (у jxiltxgx, g.7 / Хб,.-б-Хаж Л). Увыг 6x1-1бх - хГТ / I

г-де - сигнал на выходе;

- сигналы соответственно

Xexii ftxii

у на первом, втором, тре тьем и четвертом его входахА и В - заранее заданные постоянные величины.

Сигнал с первого входа первого вычислителя 1 квадратируется умножителем 19, сигнал с третьего входа первого вычислителя 1 перемножается с постоянной величиной А .на умножителе 20, сигнал с четвертого входа первого вычислителя 1 перемножается с постояннойвеличиной В на умножителе 21, сигнал с его выхода

суммируется с выходным сигналом умножителя сумматорами 22, 20. и 21 и делится на сигнал с второго входа первого вычислителя 1 делителем 23. Выходной сигнал делителя 23 вычитается из сигнала с второго входа пер.вого вычислителя Г вычитателем 24, выходной сигнал которого перемножается сам с собой на умножителе 25. Сигнал с четвертого входа первого

вычислителя 1 перемножается с постоянной величиной А на умножителе 26, а сигнал с третьего входа перемножается с постоянной величиной на ум

ножителе 27, выходной сигнал которого вычитается из выходного сигнала умножителя 26 вычитателем 28. Выходной сигнал вычитателя 28 делится на сигнал с второго входа первого вычислителя 1 делителем 29, перемножается с самим собой на умножителе 30, суммируется с выходным сигналом умножителя 25 сумматором 31 и вычитается из выходного сигнала умножителя 19 вычитателем 32, выходной сигнал которого является выходным сигналом первого вычислителя 1

На первый, второй, третий и четвертый входы второго вычислителя 2 подаются измеренные аналоговые сигналы соответственно напряжения И тока I(j, активной Рд и реактивной Q(j мощности агрегата.

Второй вычислитель 2 реализует функцию:

УЬЫК - 5 ftXl X JX 1 - X йл - X д; J

где УВ, - сигнал на выходе, . а)1(,,,хйхг сигналы соответственно Xexj,X6 на первом, втором, третьем и четвертом входах второго вычислителя 2. Сигнал с первого входа второго вычислителя 2 квадратируется умножителем 33, сигнал с второго входа квадратируется умножителем 34, их выходные сигналы перемножаются умножителем 35, выходной сигнал которого перемножается с постоянной величиной 3 умножителем 36. Сигнал с третьего входа второго вычислителя 2 квадратируется умножителем 37, а сигнал с четвертого входа квадратируется умножителем 38, выходной сигнал которого суммируется с вьпсодным сигналом умножителя 37 сумматором 39, выходной сигнал которого вычитается из выходного сигнала умножителя 36 вычитателем 40, выходной сигнал вычитателя 40 является выходным сигналом второго вычислителя 2. .На первый, второй, третий, четвертый, пятый, шестой и седьмой входы блока вычислителей 8 поступают соответственно измеренные аналоговые сигналы напряжения шин и,, напряжения Кд, тока lo,, активной и реактивной О.д мощностей агрегата, а также выходные сигналы с первого 1 и второго 2 вычислителей. Третий вычислитель реализует следующие фунции:

V. -)). V ,. 01|хИ « хг6)

Jnxi-tBXi;

exj

V -гл(1 « XHS-BI . /xtxyB-Xfai-A). YB,,,J-ZAH xext

V« --. 8xsR.../%,.

Чш,-гf( .k(xj;;

Увь.Х5--6Хвх, У8ь, Xftxji Vewx -iXbxv Yftbixe - Xexs

где У(„,Л«г вькь- сигналы соответстУйычч Ьы. венно на первом,

втором, третьем, четвертом, пятом, шестом, седьмом и восьмом выходахJ

Хб„,Хб„,Х4„, - сигналы соответст х1, венно на первом, втором, третьем, четвертом и пятом входах третьего вычислителя 9.

Сигнал с первого входа третьего вычислителя 9 перемножается с постоянной величиной 2 на умножителе 41. Сигнал с выхода перемножителя 41 является первым выходным сигналом третьего вычислителя 9. Сигнал с его четвертого входа перемножается с по- стоянной величиной А на умножителе

42, сигнал с пятого входа перемно- жается с постоянной величиной В на умножителе 43, их выходные сигналы суммируются,сумматором 44, выходной сигнал сумматора .44 делится на сигнал с второго входа этого вычислителя делителем 45. Сигнал с выхода делителя 45 вычитается из сигнала с второго входа вычислителя 9. Сигнал с выхода делителя 45 квадратируется на умножителе 46 и делится на сигнал с второго входа вычислителя 9 делителем 47. Выходной сигнал делителя 47 вычитается из сигнала с второго входа вычислителя 9

вычитателем 48, выходной сигнал которого перемножается с постоянной величиной 2 умножителем 49, выходной сигнал умножителя 49 инвертируется инвертором 50. Выходной сигнал

инвертора 50 является вторым выходом третьего вычислителя 9. Сигнал с его четвертого входа перемножается с постоянной величиной В на умножителе 52, сигнал с его пятого входа перемножается с постоянной величиной А на умножителе 53 и выхо ной сигнал умножителя 53 суммируется с выходным сигналом перемножйтеля 52 сумматором 54. Выходной сигнал сумматора 54 делится на сигнал со второго входа вычислителя 9 делителем 55. Постоянная величина В делится на сигнал с третьего входа вычислителя 9 делителем 60, а постоянная величина А делится на сигнал с третьего входа делителем 61. Выходной сигнал вычитател 51 перемножаетсяс выходным сигналом делителя 60 умножителем 56. Выходной сигнал делителя 55 перемножа ется с выходным сигналом делителя 61 на умножителе 57, вычитается из выходного сигнала перемножителя 56 вычитателем 58 и перемножается с постоянной величиной 2 умножителем 59. Выходной сигнал умножителя 59 является третьим выходом третьего в.ычислителя 9. Выходной сигнал делителя 55 пере множается с выходным сигналом делителя 60 умножителем 62, выходной сигнал которого перемножается с постоянной величиной 2 умножителем 63 Выходной сигнал вычитателя 51 перемножается с выходным сигналом делителя 61 умножителем 64, суммируется с выходным сигналом перемножител 63 сумматором 65 и перемножается с постоянной величиной 2 умножителем 66. Выходной сигнал умножителя 66 является четвертым выходным сигнало третьего вычислителя 9. Сигнал с его третьего входа квадратируется умножителем 67, перемножается с сиг налом с второго входа вычислителя 9 умножителем 68 и перемножается с постоянной величиной 6 умножителем 69. Выходной сигнал умножителя 69 -является пятым выходом вычислителя 9. Сигнал с его второго входа квадратируется умножителем 70, перемнож ется с сигналом с третьего входа вы числителя 9 перемножителем 71 и пер множается с постоянной величиной 6 умножителем 72. Выходной сигнал перемножителя 72 является шестым выходным сигналом вычислителя 9. Сигнал с его четвертого входа перемножается с постоянной величиной 2 умножителем 73, выходной сигнал которого инвертируется инвертором .74 Выходной сигнал инвертора 74 яв96ляется седьмым выходным сигналом i третьего вычислителя 9. Сигнал с его пятого входа 9 перемножается с постоянной величиной 2 умножителем 75, выходной сигнал которого инвертируется инвертором 76. Выходной сигнал инвертора 76 является восьмым выходным сигналом третьего вычислителя 9. Сигналы с первого, второго, третьего, четвертого, пятого,шестого, седьмого и восьмого выходов третьего вычислителя 9 подаются соответственно на первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы четвертого вычислителя 10, который реализует следующие функции: VBMX.bxVti frx.V. Sxjns Х, -, Ygwxr Jt- 6XiX6x5 } Xey,XRxTns4x, вых,-.ХбД,Х,(,)(5, где Yj ,yg;,j, - сигналы соответственно на первом, втором и третьем выходах J Х х1Дбх1ДВх} &х« сигналы соответст 6 5 Вхй 6к7 8х8 венно на первом, втором, третьем, четвертом, пятом, шестом, седьмом и восьмом входах четвертого вычислителя 10« заранее заданные .,}з. постоянные величины. Сигнал с первого входа четвертого вычислителя 10 квадратируется перемножителем 77 и перемножается с постоянной величиной Q, умножителем 78, сигнал, с втброго входа квадратируется умножителем 79 и перемножается с постоянной ве11ичиной cjj умножителем 80, сигнал р третьего входа квадратируется умножителем 81 и перемножается с постоянной величиной ij умножителем 82, сигнал с четвертого входа квадратируется умножителем 83 и пере - множается с постоянной величиной CLJ умножителем 84 и суммируется с выходным сигналом умножителя 82 сумматором 85. Выходной сигнал сумматора 85 суммируется с выходным сигналом умножителя 80 сумматором 86 и с выходным сигналом перемножителя 7 78 сумматором 87. Выходной сигнал сумматора 87 является сигналом с первого выхода вычислителя 10, сиг нал с второго входа которого перемножается с сигналом с его пятого входа умножителем 88 и с постоянно величиной С|, умножителем 89.; Сигнал с третьего входа вычислител 10 перемножается с сигналом с его седьмого входа перемножителем 90 и с постоянной величиной ( умножи телем 91, сигнал с четвертого вход вычислителя 10 перемножается с сиг налом с его восьмого входа умножит лем 92 и с постоянной величиной умножителем 93 и суммируется с вых ным сигналом умножителя 91 суммато ром 94 и с выходным сигналом умножителя 89 сумматором95. Выходной сигнал сумматора 95 является сигналом с второго выхода четвертого вычислителя 10. Сигнал с пятого входа последнего квадрати руется умножителем 96 и перемножается с постоянной величиной Ji умн жителем 97. Сигнал с шестого входа вычислителя 10 квадратируется умножителем 98 и перемножается с постоянной величиной (ij. умножителем 99, сигнал с седьмого входа квадратируется умножителем 100 и перемножается с постоянной величиной Л||. умножителем 101, сигнал с восьkoro входа квадратируется да1ножителем 102, перемножается с постоян ной величиной умножителем 103, суммируется с выходным сигналом сумматором 104, с выходным сигнало умножителя 99 - сумматором 105, а с выходным сигналом умножителя 97 - сумматором 106. Выходной сигн сумматора 106 является третьим выходным сигналом четвертого вычисли теля. На первый, второй и третий вход пятого вычислителя 11 подаются сигналы соответственно с первого, второго и третьего выходов четвертого вычислителя 10. Пятый вычислит ель 11 реализует следуюп ие функ ции: k«i 6xi X2 t j 6X1 «I ХЬлХвхг-Хм, 8 - JL где У м УкыкгДбых соответственно первый, второй и третий выходные сигналыХ|х,Х&х&Хб,з. - первьй, второй и третий соответственно входные сигналы вычислителя.. Сигнал с первого входа вычислителя 11 перемножается с сигналом с его второго входа умножителем 107, сигнал с третьего входа вычислителя 11 квадратируется умножителем 109 и вычитается из выходного сигнала умножителя I07 вычитателем 110, сигнал с второго входа вычислителя 11 делится на сигнал с выхода вычитателя 110 делителем 108. ВьСсодной сигнал делителя 108 является первым выходным сигналом вычислителя 1I. Сигнал с его первого входа делится на сигнал с выхода вычитателя 110 делителем 111. Выходной сигнал делителя 111 является вторым выходным сигналом вычислителя 11. Сигнал с его третьего входа делится на выходной сигнал вычитателя 110 делителем 112 и его выходной сигнал инвертируется инвертором 113. Выходной сигнал инвертора 113 является третьим выходом вычислителя 11. На первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый и тринадцатый входы шестого вычислителя 12оподатся сигналы соответственно с перого, второго, третьего, четвер-г того, пятого, шестого, седьмого, осьмого выходов третьего вычислителя 9, первого, второго и третьего выходов пятого вычислителя 11 и ыходов первого и второго вычислителей 1 и 2. Шестой вычислитель 12 еализует следующие функхщи: , (exrXp g+Xe jXB;,J; (Хг г вхД вХгЧхд х$ ВХ(,) 1гбхи{Хмг5 йх/, XBXIO) 1Х6 1} 6 вХ12 &Л9ЧхАз &Х1о)т

9 :.

, ybwx, i,(

9 ЬХ1ь(&ХзХйх, ХбХГ ftXIO ) i

S-IrS Vn ( BXj Xsx3 XBxJ ВЛ«ХбХ5 6X10)

где ,кг. Сигналы соответ ь(Х1, ственно на первом втором, третьем, четвертом и пятом ,выходах,

-сигналы соответбх« вХб1 Х7.ех8 ственно на первом

X Y Y X, втором, третьем , )Л Х101вх1Ч)ЛвХ1г1 f , f , четвертом, пятом,

. шестом, седьмом,

восьмом, девятом, десятом, одиннадцатом, двенадцато и тринадцатом входах шестого вычислителя 12J

. заданные постоянные величины.

Сигнал с двенадцатого входа вычислителя 12 перемножается с сигналом с его девятого входа умножителем 114, сигнал с тринадцатого входа перемножается с сигналом с- одиннадцатого входа умножителем 115, выходные сигналы умножителей 1I5 и 114 суммируются сумматором 116, выходной сигнал сумматора 116 перемножается с Сигналом с первого входа вычислителя 12 умножителем 117 и выходной сигнал последнего перемножается с постоянной величиной с умножителем 118. Выходной сигнал умножителя 118 является первым выходным сигналом шестого вычислителя 12. Сигнал с его второго входа перемножается с сигналом с его девятого входа умножителем 119. Сигнал с пятого входа вычислителя 12 перемножается с сигналом с его одиннадцатого входа умножителем . 120, выходные сигналы умножителей

120и 119 суммируется сумматором

121и выходной сигнал сумматора 21 перемножается с сигналом с двенадцатого входа вычислителя 12 умножителем 122. Сигнал с его второго входа перемножается с сигналом с его одиннадцатого входа умножителем 123. Сигнал с пятого входа вычислителя 12 перемножается с сигналом с его десятого входа умножителем 124, суммируется с выходным

01799. 10

сигналом умножителя 123 сумматором 125, перемножается с сигналом с тринадцатого входа вычислителя 12 перемножителем 126, выходные сигналы умножителей 126 и 122 суммируются сумматором 127 и выходной сигнал умножителя 127 перемножается с постоянной величиной (J. умножителем 128. Выходной сигнал умножителя 128 является вторым выходным сигналом шестого вычислителя 12. Сигнал с го двенадцатого входа перемножается с сигналом с его девятого входа -умножителем 129. Сигнал с тринадцатого входа вычислителя 12 перемножается с сигналом с его десятого входа умножителем 130, выходной сигнал последнего суммируется с выходным сигналом умножителя 129 сумматором 131, перемножается с сигналом с шестого входа вычислителя I2 умножителем 132 и с постоянной величиной lj умножителем 133. Выходной сигнал перенножителя 133 является третьим выходным сигналом вычислителя 12. Сигнал с его третьего входа перемножается с сигналом с его девято, го входа умножителем 134. Сигнал с седьмого входа вычислителя 12 пе- .

3 ремножается с сигналом с его одиннадцатого входа умножителем 135, суммируется с выходным сигналом умножителя 134 сумматором 136, перемножается с сигналом с двенадцатого

35 входа вычислителя 12 умножителем 137. Сигнал с третьего входа вычислителя 12 перемножаетсяс сигналом с его одиннадцатого входа 12 умножителем 138. Сигнал с седьмого входа вычислителя 12 перемножается с сигналом с его десятого входа умножителем 139, суммируется с выходным сигналом перемножителя 138 сумматором 140, перемножается с сигналом с тринадцатого входа вычислителя 12 умножителем 141, cyммиpyeI - ся с выходным сигналом умножителя 137 сумматором 142 и перемножается с постоянной величиной , умножителем 143. Выходной сигнал перемножителя 143 является четвертым выходным сигналом вычислителя 12. Сигнал с его четвертого входа перемножается с сигналом с его девятого входа

55 умножителем 144. Сигнал с восьмого входа вычислителя 12 перемножается с сигналом с его одиннадцатого входа умножителем 145, суммируется

с выходным сигналом умножителя 144 сумматором 146 и перемножается с сигналом с двенадцатого входа вычислителя 12 умножителем 147. Сигнал с четвертого входа вычислителя 12 перемножается с сигналом с его одиннадцатого входа умножителем 148. Сигнал с восьмого входа вычислителя 12 перемножается с сигналом с его десятого входа умножителем 149, суммируется с выходным сигналом умножителя 148 сумматором 150, перемножается с сигналом с тринадцатого входа вычислителя 12 умножителем 151, суммируется с выходным сигналом умножителя 147 сумматором 152 и 152 перемножается с постоянной величиной О 5 умножителем 153. Выходной сигнал умножителя 153 является пятым выходным сигналом вычислителя 12

Первый, второй, третий, четвертый и пятый выходные сигналы блока вычислителей 8 интегрируются первым 4, вторым 5, третьим 13, четвертым 14 и пятым 15 интеграторами (со сбро сом). Выходные сигналы интеграторов

контролируются соответственно первым 6, вторым 7,, третьим 16, четвертым 17 и пятым 18 сигнализаторами отклонений, каждый из которых настрен на определенную уставку. При выходе входного сигнала за границы диапазона, задаваемого уставкой, сигнализатор отклонений вьщает 1 на соответствующий выход устройства Таймер 3 периодически вьщает сигналы на сброс всех интеграторов.

В качестве сигнализатора отклонений может быть выбран любой двухпороговый компаратор. В качестве интеграторов могут быть использованы интеграторы,в которых сброс осуществляется внешним сигналом.

Предлагаемое устройство испытывали на математической модели измерительных каналов, реализованной на мини-ЭВМ СМ-2. Результаты расчетов показали, что ошибки при оценке параметров, возникающие за счет линеаризации исходной системы уравнений, не превьш1ают 0,005% от дисперсии ошибок измерений.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТОПЛИВОМЕР | 1991 |

|

RU2019794C1 |

| ПРИЕМНИК ДЛЯ РЕЛЬСОВОЙ ЦЕПИ | 1994 |

|

RU2083410C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| Устройство для приема цифровых сигналов с непрерывной фазовой модуляцией | 1989 |

|

SU1690211A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2004 |

|

RU2287909C2 |

| УСТРОЙСТВО ДЛЯ РАСЧЕТА РАЗМЕРОВ ОБЛАСТИ ВЕРОЯТНОГО НАХОЖДЕНИЯ ЦЕЛИ | 2014 |

|

RU2554534C1 |

| Система записи и воспроизведения видеосигнала | 1990 |

|

SU1783635A1 |

| Система оптимизации управления непосредственно и косвенно управляемыми объектами | 1982 |

|

SU1080117A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВЕРОЯТНОСТИ ОБНАРУЖЕНИЯ ВОЗДУШНЫХ ЦЕЛЕЙ | 2000 |

|

RU2176104C1 |

| УСТРОЙСТВО ДЛЯ ПОЛЕТНОГО КОНТРОЛЯ ВЕСА НАГРУЗКИ САМОЛЕТА | 2003 |

|

RU2260179C1 |

УСТРОЙСТВО ЦЛЯ КОНТРОЛЯ АППАРАТУРЫ УПРАВЛЕНИЯ ЭЛЕКТРОСТАНЦИИ, содержащее первый вычислитель, первый, второй, третий и четвертый входы которого являются соответственно первым, вторым, третьим и четвертым входами устройства, второй вычислитель, первый вход которого соединен с вторым входом первого вычислителя, второй вход является пятым входом устройства, а третий и четвертый входы соединены соответственно с третьим и четвертым входами первого вычислителя, первый и второй интеграторы, соединенные первыми входами с выходом генератора тактовых импульсов, а выходами соответственно с входами первого и второго компараторов, выходы которых являются соответственно первым и вторым выходами устройства, отличающееся тем, что, с целью расширения области применения устройства путем селекции источника параметрического отказа, оно содер-. жит третьи, четвертые и пятые интеграторы и компараторы, третий вычислитель, соединенный первым, вторым, третьим, четвертью и пятым входами соответственно с первым, вторым, пятым, третьим и четвертым входами устройства, четвертьй вычислитель, подключенный первым, вторым третьим, четвертым, пятым, шестым,седьмым и восьмым входами соответственно к первому, второму, третьему, четвертому, пятому, шестому, седьмому и восьмому выходам третьего вычислитеi ля , пятый вычислитель, соединенный первым, вторым и третьим входаin ми соответственно с первым, вторым и третьим выходами четвертого вычислителя, шестой вычислитель, подключенный первым, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым входами соответственно к первому, второму, третьему, четto вертому, пятому, шестому, седьмому и.восьмому входам третьего вычислителя, девятым, десятым и одиннад-. датым входами - соответственно к ;о со первому, второму и третьему выходам пятого вычислителя, двенадцатым и тринадцатым входами - к выходам соответственно первого и второго вычислителей, первым и вторым выхода ми соответственно к вторым входам первого и второго интеграторов, а третьим, четвертым и пятым выходами - к входам соответственно третьего, четвертого и пятого интеграторов, другие входы которых соединены с выходом генератора тактовых импульсов, а вькоды - соответствен

1л

31 К

37

ИЗ

Рл

ПЙШ

Ил

««

«rf

фиг.В

| Дисковый пакет программных модулей генерации задач сбора и обработки информации в АСУ ТП: Краткое описание и руководство по поль - | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Автоматизированная система управления технологическим процессом Саяно-Шушенской ГЭС | |||

| Техн | |||

| проект | |||

| Инн | |||

| Устройство для генерирования незатухающих электрических колебаний для беспроволочного телеграфирования и телефонирования | 1916 |

|

SU1609A1 |

| ВЭИ, 1978. | |||

Авторы

Даты

1985-12-30—Публикация

1983-11-05—Подача