Изобретение относится к области вычислительной техники и предназначено для использования в системах обработки информации, а также может быть применено в блоках сжатия и распаковки данных без потерь в системах для рационального использования устройств хранения и передачи данных, обработки данных физических экспериментов.

Известен способ сжатия данных (RU №2386210 С2, МПК Н03М 7/40, Н03М 7/46, заявлено 04.08.2006, опубликовано 10.04.2010, бюл. №10), в котором сжатие данных осуществляется с помощью кодера. В первом блоке памяти кодера хранятся предварительно записанные кодовые комбинации (КК1) с числом разрядов n, где n=2, 3, 4, …, представляющие собой полный набор возможных входных кодовых комбинаций (КК). Во втором блоке памяти кодера хранятся предварительно записанные кодовые комбинации КК2, однозначно соответствующие KK1, с числом разрядов, меньшим или таким же, как в КК1. Входной поток данных разделяют на КК с одинаковым числом разрядов n. КК последовательно вводят в кодер, идентифицируют путем сравнения с КК1, отображают соответствующий выходной кодовой комбинацией КК2. КК2 представляют собой последовательность групп с одинаковым числом разрядов n в каждой. Совокупное число кодовых комбинаций КК2-mn, где m=2, 3, 4, …, n=1, 2, 3, …. Число последовательных групп КК определяют как mn-1, mn-2, …. Разрядность КК2 в группе выравнивают за счет добавления незначащего нуля перед кодовой комбинацией.

Известен способ сжатия восстановления данных без потерь (RU №2403677 С1, МПК Н03М 7/30, заявлено 09.02.2009, опубликовано 10.11.2010, бюл. №31), в котором используется сжатие данных, ранее подвергнутых сжатию. В сжимаемом потоке данных считают количество нулей n0 и количество единиц n1, выбирают алгоритм присвоения неповторяющихся цифровых кодов всем возможным перестановкам с повторениями из по нулей и m единиц и нахождения соответствующей перестановки, которой присваивают цифровой код Nc, считают общее количество кодов nc, определяют значения d1=n0+n1-nc и d2=(n0+n1)/2, а для восстановления потока данных выполняют обратные операции.

Известно эффективное по использованию памяти адаптивное блочное кодирование (RU №2413360 С1, МПК Н03М 7/40, заявлено 14.11.2007, опубликовано 27.02.2011, бюл. №6), в котором используется кодирование переменной длины (VLC) с низкой сложностью данных. Структура кода определяет группы кодовых слов в кодовом дереве, причем каждая из групп включает в себя кодовые слова, представляющие значения, имеющие одинаковые весовые коэффициенты, и кодовые слова упорядочиваются лексикографически относительно значений, представленных посредством кодовых слов. Кроме того, структура кода определяет первую и вторую подгруппу кодовых слов в каждой из групп, при этом первая подгруппа включает в себя кодовые слова, имеющие первую длину, а вторая подгруппа - вторую длину, отличную от первой длины. Затем формируют результат кодирования переменной длины, по меньшей мере, для одного из сохранений в запоминающем устройстве, передачи в устройство или представлении пользователю.

Недостатком данных устройств является схемная сложность, что затрудняет их применение.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип кодирующее устройство (RU №153302 U1, МПК Н03М 7/30, заявлено 17.06.2014, опубликовано 10.07.2015, бюл. №19), содержащее входной регистр, анализатор разрядов, блок управления ключами, блок ключей, ПЗУ, блок мультиплексоров, выходной регистр, а также тактовый генератор, делитель частоты, счетчик и выходной регистр со следующими соединениями: выход входного регистра 1-n соединен с входами анализатора разрядов и с блоком управления ключами, выходы 1-n2 анализатора соединены с информационными входами блока ключей, а выходы 1-n2 - с управляющими входами этого блока, выходы которого 1-n2 соединены с входами ПЗУ, а выходы 1-2n ПЗУ соединены с информационными входами блока мультиплексора, выходы которого 1-n являются выходами маркера устройства; выходы 3-8 входного регистра соединены с выходным регистром, выходы которого являются выходами информационных разрядов устройства; выход тактового генератора через счетчик соединен с управляющими входами блока мультиплексоров, а через делитель частоты - с управляющими входами: через выход 1 входного регистра, через выход 2 с блоком управления ключами, а через выход 3 с выходным регистром.

Недостатком данного устройства является схемная сложность, что затрудняет его применение.

К причинам, препятствующим достижению указанного ниже технического результата, относятся большие аппаратные затраты и связи между ними, что приводит к уменьшению надежности и усложнению устройства.

Техническим результатом изобретения является простота реализации с одновременным уменьшением времени передачи данных, повышение информационной вместимости без потерь информации за счет сокращения необходимого объема памяти для хранения последовательности двоичных символов.

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для сжатия данных содержит

N входных символов D1, D2, …, DN по k разрядов соединенных с входным регистром данных 1, группу из L анализаторов символов 21, 22, …, 2L, каждый из которых содержит первую группу из w элементов ИЛИ 3, первую группу из w элементов И 4 и блок счета количества единиц 5 (L - количество групп по w символов из k разрядов, причем N=L*w), группу из (L-1) сумматоров 61, 62, …, 6L-1, группу из (L-1) схем сравнения 71, 72, …, 7L-1, группу из (L-1) D-триггеров 81, 82, …, 8L-1 с входом разрешения работы СЕ, асинхронным CLR и синхронным R входами установки в нулевое состояние, вторую группу из (L-1) элементов И 91, 92, …, 9L-1, третий элемент И 10, четвертый элемент И 11, второй элемент ИЛИ 12, многовыходной блок приоритета 13, блок коммутаторов данных 14, выходной буфер 15, внешние входы задания количества символов w в группе 16, внешний вход EN разрешения работы 17, внешний вход С синхронизации 18, внешний вход CLR установки в нулевое состояние 19, внешние выходы устройства Q 20, а также внутреннюю шину данных DD из N символов по k разрядов, внутреннюю N разрядную шину маски символов М, внутреннюю L разрядную шину указателей групп символов U,

причем внешний вход CLR установки в нулевое состояние 19 соединен с входами установки в нулевое состояние входного регистра 1 и выходного буфера 15, а также входами CLR асинхронной установки в нулевое состояние всех триггеров 81, 82, …, 8L-1,

внешний вход синхронизации 18 соединен с входами синхронизации С триггеров 81, 82, …, 8L-1, входного регистра 1 и выходного буфера 15,

внешний вход EN разрешения работы 17 соединен с входами разрешения работы СЕ триггеров 81, 82, …, 8L-1 и выходного буфера 15,

причем выходы входного регистра данных 1 соединены с внутренней шиной данных DD, из которой группами по w символов из k разрядов соединены с соответствующими входами первых групп из w элементов ИЛИ 3 анализаторов символов 21, 22, …, 2L, в каждом из которых выходы первых групп из w элементов ИЛИ 3 соединены со вторыми входами соответствующих первых групп из w элементов И 4, выходы которых являются внутренней шиной маски символов М и соединены с входами блока счета количества единиц 5, выходы которых являются выходами анализаторов символов 21, 22, …, 2L,

выход первого анализатора символов 21 соединен с первой группой входов первого сумматора 61, выходы анализаторов символов, начиная со второго 22 до последнего 2L анализатора, соединены со вторыми группами входов соответствующих сумматоров 61, 62, …, 6L-1, выходы сумматоров, начиная в первого 21 до предпоследнего 6L-2 сумматора, соединены с первой группой входов последующего сумматора, начиная со второго 22 до последнего 2L сумматора, а также выходы (L-1) сумматоров 61, 62, …, 6L-1 соединены со вторыми группами входов соответствующих (L-1) схем сравнения 71, 72, …, 7L-1, первые группы входов которых соединены между собой и подключены к внешним входам 16 задания количества символов w в группе,

выходы схем сравнения, начиная с первой 71 до предпоследней 7L-2 схемы сравнения, соединены с информационными входами D соответствующих триггеров, начиная со второго 82 до последнего 8L-1 триггера, и с первыми входами соответствующих элементов И второй группы, начиная со второго 92 до предпоследнего 9L-2 элемента И, а информационный вход D первого триггера 81 соединен с первым входом первого элемента 91 из второй группы элементов И и подключен к логической единице,

инверсные выходы NT1, NT2, …, NTL-1 триггеров 81, 82, …, 8L-1 соединены с первыми входами первых групп из w элементов И 4 соответствующих (L-1) первых анализаторов символов 21, 22, …, 2L-1 и вторыми входами соответствующих элементов И второй группы 91, 92, …, 9L-1, первые входы первой группы из w элементов И 4 последнего анализатора символов 2L соединены с выходом последней схемы сравнения 7L-1, который также соединен с первым входом третьего элемента И 10 и со вторым входом четвертого элемента И 11, выход которого соединен с входом разрешения работы СЕ входного регистра 1,

третьи входы всех элементов второй группы элементов И 91, 92, …, 9L-1 соединены между собой, соединены со вторым входом третьего элемента И 10 и подключены к выходу третьего элемента ИЛИ 12, входы которого соединены со всеми N разрядами внутренней шины маски символов М, которые также соединены со второй группой входов выходного буфера 15 и с входами многовыходного блока приоритета 13, у которого w групп выходов соединены с управляющими входами блока коммутаторов данных 14, информационные входы которого соединены с внутренней шиной данных DD, а выходы блока коммутаторов данных 14 соединены с третьей группой входов выходного буфера 15,

выходы второй группы элементов И 91, 92, …, 9L-1 и выход третьего элемента И 10 являются внутренней шиной указателей групп символов U и соединены с первой группой входов выходного буфера 15, выходы Q которого являются внешними выходами устройства 20.

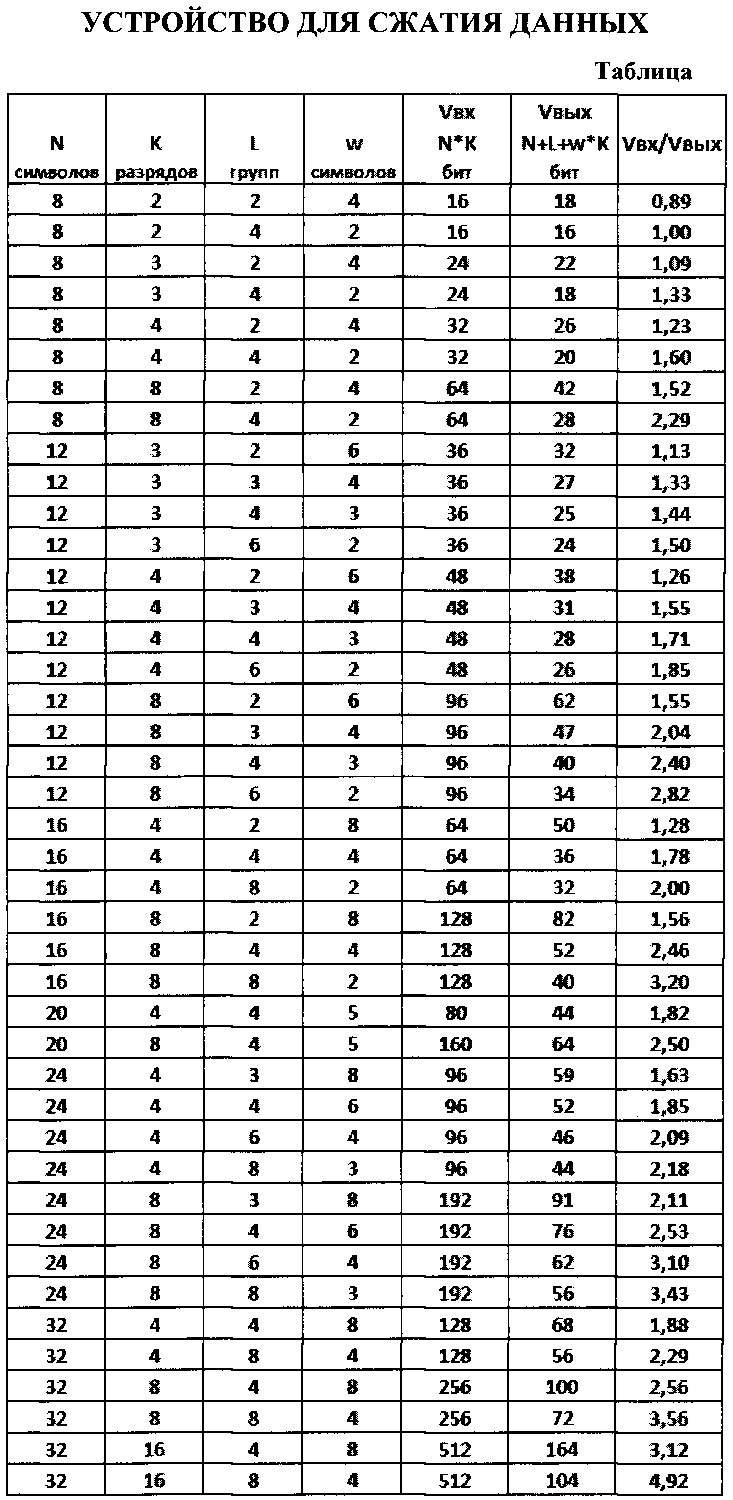

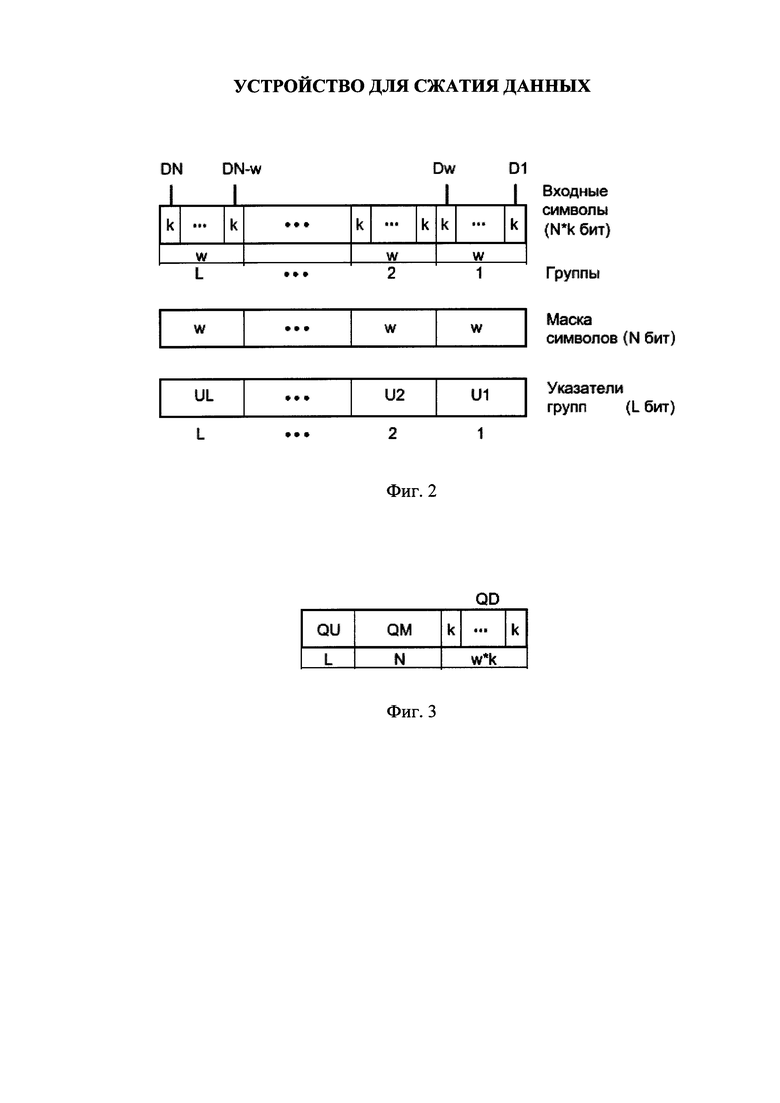

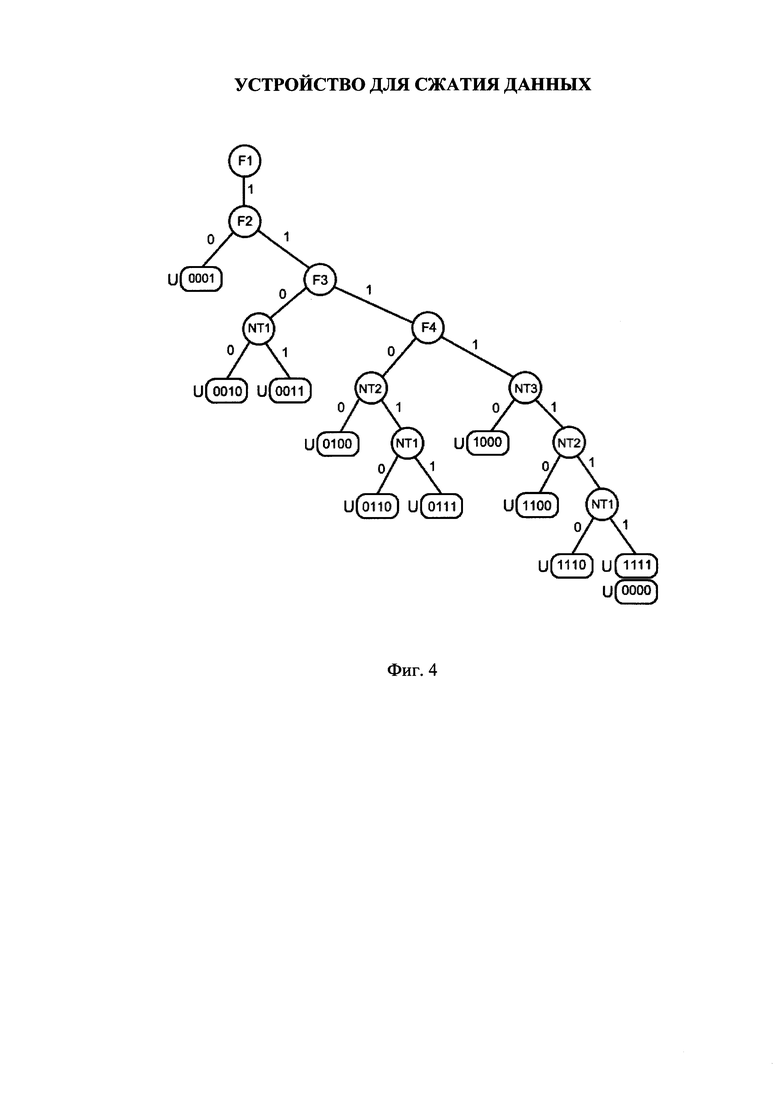

На фиг. 1 представлена схема предлагаемого устройства для сжатия данных. На фиг. 2 приведены форматы входных данных и внутренних шин. На фиг. 3 приведен формат выходных данных. На фиг. 4 приведено кодовое дерево для формирования указателей групп при L=4.

В устройстве приняты следующие обозначения:

D1, D2, …, DN - N входных символов по k разрядов,

k - разрядность символов,

L - количество групп, причем N=L*w,

w - количество символов в каждой группе,

DD - внутренняя шина данных из N символов по k разрядов,

М - внутренняя N разрядная шина маски символов,

U - внутренняя L разрядная шина указателей групп символов,

Q - выходная шина разрядностью L+N+w*k,

QD - выходные разряды данных w символов по k разрядов,

QM - выходные N разрядов маски символов,

QU - выходные L разрядов указателей групп символов,

EN - внешний вход разрешения работы,

CLR - внешний вход установки в нулевое состояние,

FZ - флаг нулевых символов,

D - информационный вход триггера,

R - вход синхронной установки триггера в нулевое состояние,

СЕ - вход разрешения работы триггера,

NT1, NT2, …, NL-1 - инверсные выходы триггеров,

F1, F2, …, FL - флаги значения суммы символов меньше w,

1 - входной регистр данных,

21, 22, …, 2L - группа из L анализаторов символов,

3 - первые группы из w элементов ИЛИ,

4 - первые группы из w элементов И,

5 - блок счета количества единиц,

61, 62, …, 6L-1 - группа из (L-1) сумматоров,

71, 72, …, 7L-1 - группа из (L-1) схем сравнения,

81, 82, …, 8L-1 - группа из (L-1) D-триггеров с входом разрешения работы СЕ и синхронным входом установки в нулевое состояние,

91, 92, …, 9L-1 - вторая группа из (L-1) элементов И,

10 - третий элемент И,

11 - четвертый элемент И,

12 - второй элемент ИЛИ,

13 - многовыходной блок приоритета,

14 - блок коммутаторов данных,

15 - выходной буфер,

16 - внешний вход задания w количества символов в группе,

17 - внешний вход EN разрешения работы,

18 - внешний вход С синхронизации,

19 - внешний вход CLR установки в нулевое состояние,

20 - внешние выходы Q.

Входной регистр данных 1 содержит N*k информационных разрядов и предназначен для хранения текущего массива N входных символов D1, D2, …, DN по k разрядов, а также содержит вход разрешения записи СЕ, вход синхронизации С и вход установки в нулевое состояние CLR. Выходы входного регистра данных 1 являются внутренней шиной данных DD.

В D-триггерах 81, 82, …, 8L-1 также содержатся вход синхронизации С, вход разрешения работы СЕ, асинхронный CLR и синхронный R входы установки в нулевое состояние.

Выходной буфер 15 содержит три группы информационных входов, вход разрешения работы СЕ, вход синхронизации С и вход установки в нулевое состояние CLR

Внешний вход CLR установки в нулевое состояние 19 соединен с входами установки в нулевое состояние входного регистра 1 и выходного буфера 15, а также входами CLR асинхронной установки в нулевое состояние всех триггеров 81, 82, …, 8L-1.

Внешний вход синхронизации 18 соединен с входами синхронизации С триггеров 81, 82, …, 8L-1, входного регистра 1 и выходного буфера 15.

Внешний вход EN разрешения работы 17 соединен с входами разрешения работы СЕ триггеров 81, 82, …, 8L-1 и выходного буфера 15.

Каждый из L анализаторов символов 21, 22, …, 2L содержит первую группу из w элементов ИЛИ 3, первую группу из элементов И 4 и блок счета количества единиц 5 (L - количество групп по w символов из k разрядов, причем N=L*w). При этом k входов каждого элемента ИЛИ 3 первых групп соединены с разрядами соответствующих символов внутренней шины данных DD. Выходы первых групп из w элементов ИЛИ 3 соединены со вторыми входами соответствующих первых групп из w элементов И 4, выходы которых являются соответствующими разрядами внутренней шины маски символов М и соединены с входами блока счета количества единиц 5, выходы которых являются выходами анализаторов символов 21, 22, …, 2L.

Выход первого анализатора символов 21 соединен с первой группой входов первого сумматора 61. Выходы анализаторов символов, начиная со второго 22 до последнего 2L анализатора, соединены со вторыми группами входов соответствующих сумматоров 61, 62, …, 6L-1. Выходы сумматоров, начиная в первого 21 до предпоследнего 6L-2 сумматора, соединены с первой группой входов последующего сумматора, начиная со второго 22 до последнего 2L сумматора. Также выходы (L-1) сумматоров 61, 62, …, 6L-1 соединены со вторыми группами входов соответствующих (L-1) схем сравнения 71, 72, …, 7L-1, первые группы входов которых соединены между собой и подключены к внешним входам 16 задания количества символов w в группе,

Выходы схем сравнения, начиная с первой 71 до предпоследней 7L-2 схемы сравнения, соединены с информационными входами D соответствующих триггеров, начиная со второго 82 до последнего 8L-1 триггера, и с первыми входами соответствующих элементов И второй группы, начиная со второго 92 до предпоследнего 9L-2 элемента И. Информационный вход D первого триггера 81 соединен с первым входом первого элемента 91 из второй группы элементов И и подключен к логической единице.

Инверсные выходы NT1, NT2, …, NTL-1 триггеров 81, 82, 8L-1 соединены с первыми входами первых групп из w элементов И 4 соответствующих (L-1) первых анализаторов символов 21, 22, …, 2L-1 и вторыми входами соответствующих элементов И второй группы 91, 92, …, 9L-1. Первые входы первой группы из w элементов И 4 последнего анализатора символов 2L соединены с выходом последней схемы сравнения 7L-1, который также соединен с первым входом третьего элемента И 10 и со вторым входом четвертого элемента И 11, выход которого соединен с входом разрешения работы СЕ входного регистра 1.

Третьи входы всех элементов второй группы элементов И 91, 92, …, 9L-1 соединены между собой, соединены со вторым входом третьего элемента И 10 и подключены к выходу третьего элемента ИЛИ 12, входы которого соединены со всеми N разрядами внутренней шины маски символов М, которые также соединены со второй группой входов выходного буфера 15 и с входами многовыходного блока приоритета 13, у которого w групп выходов соединены с управляющими входами блока коммутаторов данных 14, информационные входы которого соединены с внутренней шиной данных DD, а выходы блока коммутаторов данных 14 соединены с третьей группой входов выходного буфера 15.

Выходы второй группы элементов И 91, 92, …, 9L-1 и выход третьего элемента И 10 являются внутренней шиной указателей групп символов U и соединены с первой группой входов выходного буфера 15, выходы Q которого являются внешними выходами устройства 20.

Принцип работы устройства состоит в следующем.

Входной массив данных D1, D2, …, DN, содержащий N символов по к разрядов, разбивается на L групп по w символов в каждой группе (фиг. 2). Определяют ненулевые символы (в первых группах элементов ИЛИ 3) и формируют маску символов М из N разрядов. Каждый разряд маски символов М принимает единичное значение, если соответствующий символ ненулевой, или нулевое значение, если соответствующий символ нулевой.

В каждой группе символов проводится счет количества ненулевых символов (в блоках 5). Далее проводится последовательное суммирование ненулевых символов по группам (в группе из (L-1) сумматоров 61, 62, …, 6L-1) и сравнение этих сумм со значением w количества символов в группе (в группе из (L-1) схем сравнения 71, 72, …, 7L-1). На выходах схем сравнения 71, 72, …, 7L-1 формируются единичные значения флагов сумм F2, F3, …, FL, если значение соответствующей суммы меньше или равно w, или нулевые значения флагов сумм F2, F3, …, FL, если соответствующая сумма больше w. В соответствии со значениями флагов в соответствующее состояние устанавливаются триггера 81, 82, …, 8L-1.

При этом на L разрядах внутренней шины U указателей групп символов единичные значения будут установлены в разрядах тех групп, сумма которых меньше или равна w, в соответствии со значениями флагов сумм F2, F3, …, FL и инверсными значениями выходов NT1, NT2, …, NTL-1 триггеров 81, 82, …, 8L-1 (фиг. 4).

Далее по значениям указателей групп U на выходах многовыходного блока приоритета 13 формируется w групп приоритета (группа с меньшим номером имеет высший приоритет), по которым на выходы блока коммутаторов данных 14 передается не более w соответствующих символов входных данных D1, D2, …, DN. На входы выходного буфера 15 поступают значения указателей групп U, маски символов М и выделенные w символов входных данных D1, D2, …, DN (фиг. 3).

Далее в соответствии со значениями указателей групп U, блокируются выбранные и переданные символы - обнуляются соответствующие разряды в маске символов М (первые группы элементов И 4) и проводится выборка для передачи следующих w символов. При единичном значении флага суммы FL проводится синхронная установка в нулевое состояние триггеров 81, 82, …, 8L-1 и разрешается прием следующего массива входных данных D1, D2, …, DN во входной регистр 1. При всех нулевых символах входных данных D1, D2, …, DN в устройстве формируется флаг нуля FZ=0 на выходе третьего элемента ИЛИ 12, по которому на всех разрядах указателей групп U формируются нулевые значения.

Предлагаемое устройство работает следующим образом

При подаче единичного сигнала CLR на вход начальной установки устройства 19 в нулевое состояние устанавливаются входной регистр 1, группа из D-триггеров 81, 82, …, 8L-1 и выходной буфер 15. При этом на инверсных выходах NT1, NT2, …, NTL-1 триггеров 81, 82, 8L-1 будут установлены единичные значения, на выходах регистра 1 будут установлены нулевые значения, флаг нуля FZ=0, а на всех разрядах маски М и на всех разрядах указателя групп U будут сформированы также нулевые значения.

При подаче единичного сигнала EN на внешний вход разрешения работы 17 по тактовому сигналу С на внешнем входе 18 проводится запись первых входных данных D1, D2, …, DN в регистр 1, выходы которого образуют внутреннюю шину данных DD, к которой подключены входы первых групп элементов ИЛИ 3. Далее на выходах первых групп элементов ИЛИ 3 в анализаторах символов 21, 22, …, 2L будут установлены единичные значения для ненулевых символов, и так как инверсных выходах NT1, NT2, …, NTL-1 триггеров 81, 82, …, 8L-1 также установлены единичные значения, то на внутренней шине маски М сформируются единичные значения соответствующие ненулевым символам.

В блоках счета единиц 5 в анализаторах символов 21, 22, …, 2L проводится счет количества единиц в группах, соответствующих количеству ненулевых символов в группе. С выходов блоков 5 значения сумм групп поступают на входы группы сумматоров 62, 62, …, 6L-1 и далее с выходов сумматоров последовательно от младшего к последующему старшему сумматору. На выходах сумматоров 61, 62, …, 6L-1 будут получены значения соответствующие сумме всех ненулевых символов, начиная с первого младшего символа D1 входных данных D1, D2, …, DN до символов соответствующих групп.

С выходов сумматоров 61, 62, …, 6L-1 значения сумм поступают на вторые входы соответствующих схем сравнения 71, 72, …, 7L-1, а на первые входы задается значение w количества символов в группе. На выходах схем сравнения 71, 72, …, 7L-1 формируются единичные значения флагов сумм F2, F3, …, FL, если значение соответствующей суммы меньше или равно w, или формируются нулевые значения флагов сумм F2, F3, …, FL, если соответствующая сумма больше w. Флаг суммы F1 всегда равен единице F1=1, так как в группе содержится w символов и поэтому не может быть ненулевых символов более w.

В соответствии со значениями флагов сумм F1, F2, …, FL и состояниями инверсных выходов NT1, NT2, …, NTL-1 триггеров 81, 82, …, 8L-1 устанавливаются значения указателей групп U на выходах второй группы элементов И 9 и третьего элемента И 10, в соответствии с кодовым деревом (фиг. 4). Например, если сумма ненулевых символов в первой группе меньше или равна w (F1=1), сумма первой и второй групп больше w (F2=0), то на шине указателей групп будет установлено значение U=0001 (для случая, когда L=4). Если сумма первой и второй групп меньше или равна w (F1=1, F2=1), а сумма трех групп больше w (F3=0) и выход триггера NT1=1, то в соответствии с кодовым деревом на шине указателей групп будет установлено значение U=0011 (фиг. 4).

С внутренней шины указателей групп U сигналы поступают на входы многовыходного блока приоритета 13, на выходах которого формируется w групп приоритета, в которых указан номер приоритетной группы (при этом группа с меньшим номером имеет высший приоритет, наивысший приоритет присвоен группе 1, наименьший приоритет группе L). Номера w групп приоритета поступают на адресные входы блока коммутаторов данных 14.

В блоке коммутаторов данных 14 с внутренней шины данных DD, содержащей N символов по k разрядов, выбирается w ненулевых символов имеющих высший приоритет.

По следующему синхросигналу С значения флагов сумм F1, F2, …, FL-1 записываются в триггеры 81, 82, …, 8L-1, а значения указателей групп U, разряды маски символов М и w ненулевых символов имеющих высший приоритет с выходов блока коммутаторов данных 14 записываются в выходной буфер 15.

Далее нулевые сигналы с инверсных выходов NT тех триггеров 81, 82, …, 8L-1 которые установлены в единичное состояние, поступают на первые входы первых групп элементов И 4 в анализаторах символов 21, 22, …, 2L и устанавливают в нулевое состояние разряды маски символов М, соответствующие переданным символам.

Далее вновь проводится счет количества единиц, соответствующее количеству ненулевых символов в группах, их последовательное суммирование по группам, формирование значений флагов сумм F2, F3, …, FL, формирование указателей групп U, формирование w номеров групп приоритета на выходах блока приоритета 13 и выбор w ненулевых символов имеющих высший приоритет. Например, если F1=1, F2=1, F3=1, F4=1 и NT2=1, NT2=0, то в соответствии с кодовым деревом на шине указателей групп будет установлено значение U=0110 (фиг. 4).

Когда количество всех текущих ненулевых символов не превышает значение w, формируется единичное значение последнего флага сумм FL=1, который поступает на второй вход четвертого элемента И 11, первый вход которого соединен с внешним входом разрешения работы 17. Единичный сигнал с выхода четвертого элемента И 11 поступает на вход разрешения работы СЕ входного регистра 1, в который по следующему синхросигналу будет записан следующий массив входных данных D1, D2,..., DN. Единичный сигнал последнего флага сумм FL=1 также поступает на входы R синхронной установки в нулевое состояние триггеров 81, 82, …, 8L-1, которые устанавливаются в нулевое состояние по синхросигналу.

Далее проводится формирование групп символов в соответствии с рассмотренным выше алгоритмом работы для «нового» массива данных.

При всех нулевых символах входных данных D1, D2, …, DN в устройстве формируется флаг нуля FZ=0 на выходе третьего элемента ИЛИ 12, который соединен со вторыми входами второй группы элементов И 91, 92, …, 9L-1 и вторым входом третьего элемента И 10, выходы которых являются внутренней шиной U указателей групп. Поэтому на всех L разрядах указателей групп U формируются нулевые значения.

Таким образом, в канал передачи на внешние выходы устройства 20 поступают:

- L разрядов указателей групп QU,

- N разрядов маски символов QM,

- разряды данных выбранных приоритетных w символов по k разрядов QD.

Блок счета количества единиц 5 может быть реализован как древовидная структура сумматоров - на первом уровне одноразрядные полные сумматоры, на втором -двухразрядные сумматоры с выходом переноса, на третьем - трехразрядные сумматоры с выходом переноса и т.д. (Дж. Ф. Уэйкерли. Проектирование цифровых устройств. В 2-х томах. - М.: Постмаркет, 2002. - 1088 с, рис. 6.15, с. 606-609).

Многовыходной блок приоритета 13 может быть реализован на группе из приоритетных шифраторов, и группах из дешифраторов и элементов И-НЕ, с помощью которых исключают запросы высших приоритетов (Дж. Ф. Уэйкерли. Проектирование цифровых устройств. В 2-х томах. - М.: Постмаркет, 2002. - 1088 с, рис. 6.6, с. 561-562). На выходах блока приоритета формируются приоритеты по старшинству приоритетов.

Блок коммутаторов данных 14 может быть реализован на матрице мультиплексоров. Выходной буфер 15 может быть реализован как регистр или как буфер FIFO.

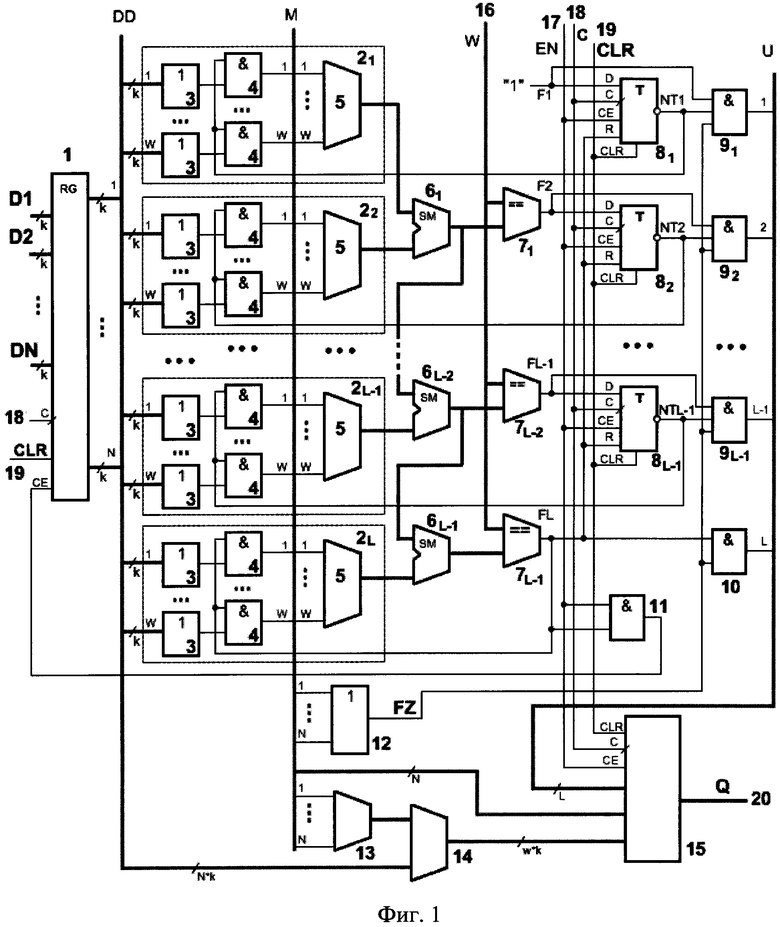

В таблице приведены коэффициенты сжатия, как отношение объема входных данных Vвх к объему выходных данных Vвых, в зависимости от количества N входных символов, разрядности символов k, количества групп символов L и символов w в группе, для случая, когда количество ненулевых символов не превышает значения w, равного количеству символов в одной группе данных. Из таблицы видно, что при заданном количестве N входных символов, заданной разрядности символов k коэффициент сжатия Vвх/Vвых увеличивается при увеличении количества групп L и уменьшении символов в группе. Например, при количестве входных данных N=12, количестве разрядов символов k=8 и изменение количества групп символов L=2, 3, 4, 6 и соответствующим им количествам символов группе w=6, 4, 3, 2 коэффициент сжатия увеличивается соответственно как Vвх/Vвых=1.55, 2.04, 2.40, 2.82.

При значениях отношения Vвх/Vвых больших единицы устройство сжатия эффективно для массивов входных данных содержащих не более w ненулевых символов. При значениях отношения Vвх/Vвых больших двух предложенное устройство сжатия будет эффективно при количестве ненулевых символов до 2*w и т.д. Эффективность предлагаемого устройства повышается, когда число нулевых символов превышает число ненулевых символов во входных данных, при произвольном расположении символов во входном массиве.

Приведенное сжатие данных может быть эффективно применено в системах регистрации, сбора и обработки данных без потери информации в режиме реального времени в физических экспериментах.

В результате предлагаемое устройство позволяет экономить объем памяти, повышать эффективность использования ресурсов с одновременным уменьшением времени передачи данных, за счет исключения из входных данных нулевых символов.

Таким образом, вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство обеспечивает сжатие входных данных без потерь, обладает регулярностью узлов и связей, при этом упрощается конструкция и, следовательно, устройство соответствует заявляемому техническому результату - простота реализации с одновременным уменьшением времени передачи данных, повышение информационной вместимости без потерь информации за счет сокращения необходимого объема памяти для хранения последовательности двоичных символов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОМПРЕССИИ ДАННЫХ | 2017 |

|

RU2672625C1 |

| УСТРОЙСТВО ДЛЯ КОМПРЕССИИ ДАННЫХ | 2019 |

|

RU2710987C1 |

| УСТРОЙСТВО ДЛЯ УПАКОВКИ ДАННЫХ | 2019 |

|

RU2701711C1 |

| УСТРОЙСТВО ДЛЯ РАСПАКОВКИ ДАННЫХ | 2017 |

|

RU2658147C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОМПРЕССИИ ДАННЫХ | 2018 |

|

RU2697618C1 |

| УСТРОЙСТВО ГРУППОВОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРАНИЦ ДИАПАЗОНА ЕДИНИЧНЫХ БИТ | 2021 |

|

RU2763903C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ | 2021 |

|

RU2780985C1 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРАНИЦ ДИАПАЗОНА ЕДИНИЧНЫХ БИТ | 2021 |

|

RU2759002C1 |

| УСТРОЙСТВО ГРУППОВОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ШАБЛОНОВ БИТ ПЕРЕМЕННОЙ РАЗРЯДНОСТИ | 2023 |

|

RU2809741C1 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ НЕПЕРЕКРЫВАЮЩИХСЯ ШАБЛОНОВ БИТ | 2023 |

|

RU2798197C1 |

Изобретение относится к области сжатия и распаковки данных без потерь. Технический результат - простота реализации с одновременным уменьшением времени передачи данных, повышение информационной вместимости без потерь информации за счет сокращения необходимого объема памяти для хранения последовательности двоичных символов. Устройство для сжатия данных содержит N входных символов D1, D2, …, DN по k разрядов, соединенных с входным регистром данных 1, группу из L анализаторов символов 21, 22, …, 2L, каждый из которых содержит первую группу из w элементов ИЛИ 3, первую группу из w элементов И 4 и блок счета количества единиц 5 (L - количество групп по w символов из k разрядов, причем N=L*w), группу из (L-1) сумматоров 61, 62, …, 6L-1, группу из (L-1) схем сравнения 71, 72, …, 7L-1, группу из (L-1) D-триггеров 81, 82, …, 8L-1 с входом разрешения работы СЕ, асинхронным CLR и синхронным R входами установки в нулевое состояние, вторую группу из (L-1) элементов И 91, 92, …, 9L-1, третий элемент И 10, четвертый элемент И 11, второй элемент ИЛИ 12, многовыходной блок приоритета 13, блок коммутаторов данных 14, выходной буфер 15, внешние входы задания количества символов w в группе 16, внешний вход EN разрешения работы 17, внешний вход С синхронизации 18, внешний вход CLR установки в нулевое состояние 19, внешние выходы устройства Q 20, а также внутреннюю шину данных DD из N символов по k разрядов, внутреннюю N разрядную шину маски символов М, внутреннюю L разрядную шину указателей групп символов U. 4 ил., 1 табл.

Устройство для сжатия данных содержит N входных символов D1, D2, …, DN по k разрядов, соединенных с входным регистром данных 1, группу из L анализаторов символов 21, 22, …, 2L, каждый из которых содержит первую группу из w элементов ИЛИ 3, первую группу из w элементов И 4 и блок счета количества единиц 5 (L - количество групп по w символов из k разрядов, причем N=L*w), группу из (L-1) сумматоров 61, 62, …, 6L-1, группу из (L-1) схем сравнения 71, 72, …, 7L-1, группу из (L-1) D-триггеров 81, 82, …, 8L-1 с входом разрешения работы СЕ, асинхронным CLR и синхронным R входами установки в нулевое состояние, вторую группу из (L-1) элементов И 91, 92, …, 9L-1, третий элемент И 10, четвертый элемент И 11, второй элемент ИЛИ 12, многовыходной блок приоритета 13, блок коммутаторов данных 14, выходной буфер 15, внешние входы задания количества символов w в группе 16, внешний вход EN разрешения работы 17, внешний вход С синхронизации 18, внешний вход CLR установки в нулевое состояние 19, внешние выходы устройства Q 20, а также внутреннюю шину данных DD из N символов по k разрядов, внутреннюю N разрядную шину маски символов М, внутреннюю L разрядную шину указателей групп символов U, причем внешний вход CLR установки в нулевое состояние 19 соединен с входами установки в нулевое состояние входного регистра 1 и выходного буфера 15, а также входами CLR асинхронной установки в нулевое состояние всех триггеров 81, 82, …, 8L-1, внешний вход синхронизации 18 соединен с входами синхронизации С триггеров 81, 82, …, 8L-1, входного регистра 1 и выходного буфера 15, внешний вход EN разрешения работы 17 соединен с входами разрешения работы СЕ триггеров 81, 82, …, 8L-1 и выходного буфера 15, причем выходы входного регистра данных 1 соединены с внутренней шиной данных DD, из которой группами по w символов из k разрядов соединены с соответствующими входами первых групп из w элементов ИЛИ 3 анализаторов символов 21, 22, …, 2L, в каждом из которых выходы первых групп из w элементов ИЛИ 3 соединены со вторыми входами соответствующих первых групп из w элементов И 4, выходы которых являются внутренней шиной маски символов М и соединены с входами блока счета количества единиц 5, выходы которых являются выходами анализаторов символов 21, 22, …, 2L, выход первого анализатора символов 21 соединен с первой группой входов первого сумматора 61, выходы анализаторов символов, начиная со второго 22 до последнего 2L анализатора, соединены со вторыми группами входов соответствующих сумматоров 61, 62, …, 6L-1, выходы сумматоров, начиная в первого 21 до предпоследнего 6L-2 сумматора, соединены с первой группой входов последующего сумматора, начиная со второго 22 до последнего 2L сумматора, а также выходы (L-1) сумматоров 61, 62, …, 6L-1 соединены со вторыми группами входов соответствующих (L-1) схем сравнения 71, 72, …, 7L-1, первые группы входов которых соединены между собой и подключены к внешним входам 16 задания количества символов w в группе, выходы схем сравнения, начиная с первой 71 до предпоследней 7L-2 схемы сравнения, соединены с информационными входами D соответствующих триггеров, начиная со второго 82 до последнего 8L-1 триггера, и с первыми входами соответствующих элементов И второй группы, начиная со второго 92 до предпоследнего 9L-2 элемента И, а информационный вход D первого триггера 81 соединен с первым входом первого элемента 91 из второй группы элементов И и подключен к логической единице, инверсные выходы NT1, NT2, …, NTL-1 триггеров 81, 82, …, 8L-1 соединены с первыми входами первых групп из w элементов И 4 соответствующих (L-1) первых анализаторов символов 21, 22, …, 2L-1 и вторыми входами соответствующих элементов И второй группы 91, 92, …, 9L-1, первые входы первой группы из w элементов И 4 последнего анализатора символов 2L соединены с выходом последней схемы сравнения 7L-1, который также соединен с первым входом третьего элемента И 10 и со вторым входом четвертого элемента И 11, выход которого соединен с входом разрешения работы СЕ входного регистра 1, третьи входы всех элементов второй группы элементов И 91, 92, …, 9L-1 соединены между собой, соединены со вторым входом третьего элемента И 10 и подключены к выходу третьего элемента ИЛИ 12, входы которого соединены со всеми N разрядами внутренней шины маски символов М, которые также соединены со второй группой входов выходного буфера 15 и с входами многовыходного блока приоритета 13, у которого w групп выходов соединены с управляющими входами блока коммутаторов данных 14, информационные входы которого соединены с внутренней шиной данных DD, а выходы блока коммутаторов данных 14 соединены с третьей группой входов выходного буфера 15, выходы второй группы элементов И 91, 92, …, 9L-1 и выход третьего элемента И 10 являются внутренней шиной указателей групп символов U и соединены с первой группой входов выходного буфера 15, выходы Q которого являются внешними выходами устройства 20.

| СПОСОБ СЖАТИЯ ДАННЫХ | 2006 |

|

RU2386210C2 |

| Способ автоматической стабилизации концентрации сернистого газа печей пылевидного обжига флотационного колчедана | 1959 |

|

SU135472A1 |

| 0 |

|

SU153302A1 | |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| КАПСУЛА, СИСТЕМА И СПОСОБ ПРИГОТОВЛЕНИЯ НАПИТКА | 2017 |

|

RU2757694C2 |

| US 8717203 B2, 06.05.2014. | |||

Авторы

Даты

2017-06-20—Публикация

2016-08-01—Подача