ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также для анализа свойств генераторов псевдослучайных последовательностей двоичных чисел и для обработки результатов физических экспериментов.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известно устройство для определения количества единиц в упорядоченном двоичном числе (RU №2522875, МПК Н03К 21/12, заявлено 24.05.2012, опубликовано 20.07.2014, Бюл. №20), содержащее буферы с тремя состояниями с прямым и инверсным входами разрешения, n разрядов входного двоичного числа, (k+1) разрядов выходного двоичного кода (k=[log2n] меньшее целое), причем буферы с тремя состояниями объединены в пирамидальную структуру, состоящую из (m-1) ступеней (m=]log2n[большее целое), и в выходной блок, содержащий k буферов с тремя состояниями с инверсным входом разрешения и к буферов с тремя состояниями с прямым входом разрешения, при этом каждая i-я ступень (i=1, …, (m-1)) содержит (2i-1) буферов с тремя состояниями с инверсным входом разрешения и 2i-1 буферов с тремя состояниями с прямым входом разрешения.

Недостатком данного устройства является определение количества единиц только в одной группе упорядоченного двоичного числа.

Известно устройство для определения количества единиц (нулей) в двоичном числе (RU №2446442, МПК G06F 7/50, Н03К 21/00, заявлено 11.04.2011, опубликовано 27.03.2012, Бюл. №9), содержащее блок управляемой инверсии, состоящий из n-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ» (n - количество разрядов входного числа), элементы ИЛИ и модули, состоящие из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, которые объединены в группы, состоящие из ярусов, и объединены в k-каскадов (k=]log2n[), так, что каждый i-й каскад содержит g(i)=n/2i групп (i=1, …, k), каждая группа i-го каскада разделена на j ярусов (j=1, …, i), при этом первый ярус каждой группы i-го каскада содержит i модулей, а каждый j-й ярус каждой группы i-го каскада (j=2, .., i,) содержит (i-j) модулей и элемент «ИЛИ».

Недостатком данного устройства является определение только общего количества единиц (нулей) в двоичном числе, а не по группам.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство параллельно-последовательной структуры для детектирования групп нулевых и единичных бит и определение их количества (RU №2711054, МПК G06F 7/74, заявлено 06.08.2019, опубликовано 14.01.2020, Бюл. №2), содержащее М разрядов D1, …, DM набора входных данных из N разрядного двоичного числа, состоящего из L наборов по М разрядов в наборе, где N=L*M, N внешних выходов групп бит QG1, …, QGN, группу внешних выходов общего количества групп QK, внешний выход левого (первого) бита QLB, группу внешних выходов количества единичных бит QU, группу внешних выходов количества нулевых бит QZ, модуль FK детектирования групп 1, первый триггер ТЕВ разрешения приема 2, триггер TLB левого (первого) бита 3, элемент «ИСКЛЮЧАЮЩЕЕ ИЛИ» 4, элемент И с одним инверсным входом 5, первый модуль SF_1 сдвига групп 6, первый сумматор SM_G бит в группе 7, вычитатель SB_8, второй модуль SF_2 сдвига групп 9, второй сумматор SM_К количества групп 10, третий сумматор SM_U количества единичных бит 11, триггер ТРО пуска-останова 12, регистр RG_G групп бит 13, регистр RG_К количества групп 14, регистр RG_U количества единичных бит 15, третий модуль SF_3 сдвига групп 16, четвертый сумматор SM_N дополнения 17, пятый сумматор SM_Z количества нулевых бит 18, второй триггер TEQ разрешения приема 19, первый выходной буферный регистр кодов групп 20, второй выходной буферный регистр общего количества групп 21, выходной триггер левого (первого) бита входных данных 22, третий выходной буферный регистр количества единичных бит 23, четвертый выходной буферный регистр количества нулевых бит 24, внешние входы С тактовых сигналов 25, R синхронной установки в нулевое состояние 26, начала работы START, остановки STOP и внутренний флаг декрементации FD.

Недостатком данного устройства является выявление отдельных групп нулевых и единичных бит произвольной размерности, а не заданных шаблонов из совокупности единичных и нулевых бит.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является разработка аппаратных средств для исследования свойств генераторов псевдослучайных последовательностей двоичных чисел, а также для обработки результатов физических экспериментов.

При анализе генераторов псевдослучайных последовательностей двоичных чисел устройство предназначено для выявления заданных шаблонов из совокупности групп (рядов) нулевых и единичных бит.

При обработке результатов физических экспериментов устройство предназначено для выявления непериодических событий (областей) - заданных длительностей событий и интервалов между ними, а также координат событий.

Техническим результатом изобретения является выявление шаблонов содержащих заданные группы (последовательность) из единичных и нулевых бит и их расположение во входных данных.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для детектирования групп бит содержит внешний m разрядный вход данных ID, внешний m разрядный вход заданного шаблона IG, группу внешних выходов данных QB, первый RS-триггер пуска-останова TSS 1, второй D-триггер TR2 задержки 2, счетчик CTG групп 3, выходной буфер ОВ 4, первый R1 регистр данных 5, второй R2 регистр данных 6, группу из m компараторов 71, 72, …, 7m, группу из (m-1) элементов И 82, 83, …, 8m, элемент ИЛИ 9 и элемент И 10,

а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внутренняя 2m-разрядная шина данных BD, внутренняя m-разрядная шина данных буфера IOB, внутренний флаг совпадения FE, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ,

причем внешний вход асинхронной установки в нулевое состояние CLR соединен с соответствующими входами асинхронной установки в нулевое состояние CLR первого RS-триггера пуска-останова TSS 1 и второго D-триггера TR2 задержки,

внешний тактовый вход устройства С соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, второго D-триггера TR2 задержки 2, счетчика CTG групп 3, выходного буфера ОВ 4, первого R1 регистра данных 5 и второго R2 регистра данных 6,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1 и с входами R синхронной установки в нулевое состояние счетчика CTG групп 3, выходного буфера ОВ 4, первого R1 регистр данных 5 и второго R2 регистр данных 6,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1,

причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен с D-входом второго триггера TR2 задержки 2, с входами СЕ разрешения работы первого R1 регистр данных 5 и второго R2 регистр данных 6 и вторыми входами всех элементов И группы 82, 83, …, 8m, выход второго D-триггера TR2 задержки соединен с входом СЕ разрешения работы счетчика CTG групп 3 и первым входом элемента И 10, выход которого соединен с входом СЕ разрешения записи в выходной буфер ОВ 4,

причем внешний m разрядный вход заданного шаблона IG соединен с первыми группами входов всех m компараторов группы 71, 72, …, 7m, выходы которых, начиная со второго компаратора 72 до последнего 7m, соединены с первыми входами соответствующих одноименных элементов И группы 82, 83, …, 8m, выходы которых являются соответствующими одноименными разрядами, начиная со второго до m-го разряда, внутренней шины данных буфера IOB,

внешний m разрядный вход данных ID соединен с группой информационных D-входов первого R1 регистра данных 5, выходы которого являются соответствующими разрядами, начиная с (m+1)-го до 2m-го разряда, внутренней шины данных BD, а также соединены с группой информационных D-входов второго R2 регистра данных 6, выходы которого являются соответствующими разрядами, начиная с первого до m-го разряда, внутренней шины данных BD,

причем разряды внутренней шины данных BD группами по m разрядов, каждая из которых начинается с i-го разряда (i=1, …, m), соединены со вторыми группами соответствующих одноименных i-x компараторов группы 71, 72, …, 7m, а выход первого компаратора 71 является первым разрядом внутренней шины данных буфера IOB, которая соединена с соответствующими входами элемента ИЛИ 9, выход которого является внутренним флагом совпадения FE и соединен со вторым входом элемента И 10,

кроме того, все m разрядов внутренней шины данных буфера IOB соединены со второй группой информационных D-входов выходного буфера ОВ 4, у которого первая группа информационных D-входов соединена с выходами счетчика CTG групп 3,

причем выходной буфер ОВ 4 также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 16 являются группой внешних выходов данных QB и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

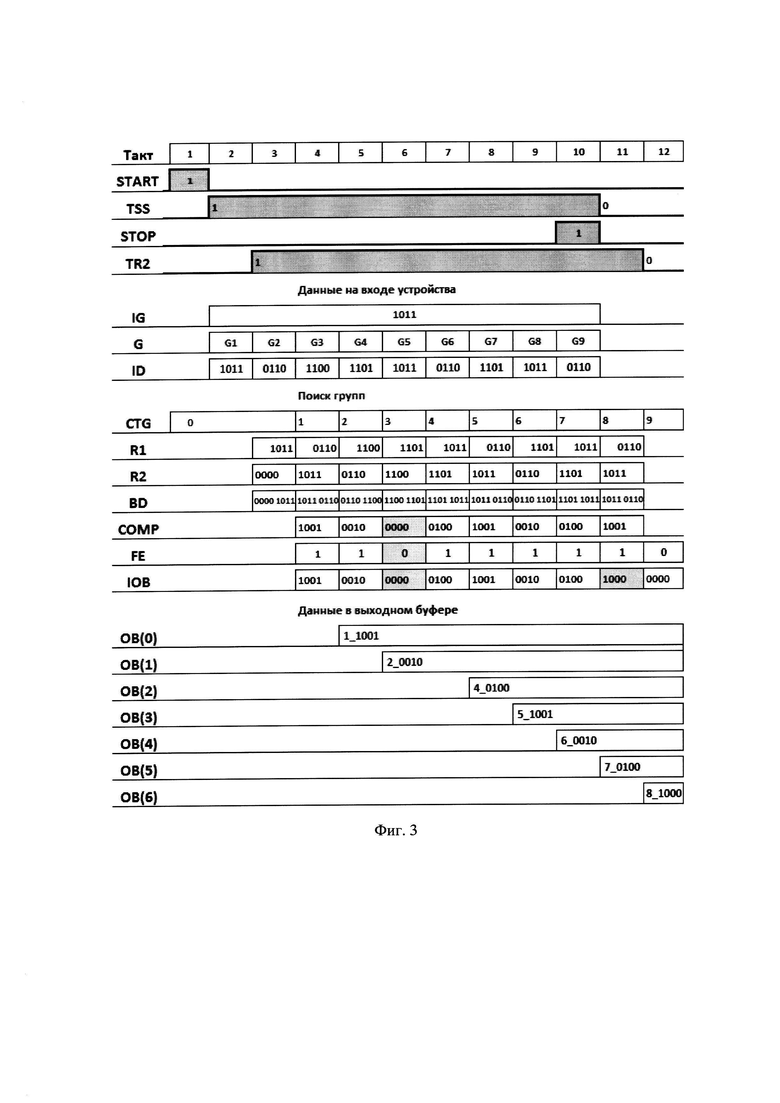

На фиг. 1 представлена схема предлагаемого устройства. На фиг. 2 приведена схема поиска шаблонов. На фиг. 3 приведена временная диаграмма работы устройства.

На фиг. 1-3 и в тексте приняты следующие обозначения:

BUF - буфер с дисциплиной обслуживания FIFO,

BD - внутренняя 2m разрядная шина данных,

С - тактовый вход,

СЕ - вход разрешения работы,

CLR - вход асинхронной установки в нулевое состояние,

CTG - счетчик групп,

D - информационные входы,

FE - внутренний флаг совпадения,

FF - внешний флаг «Буфер заполнен»,

FZ - внешний флаг «Буфер пуст»,

G1, G2, …, GL - входные группы,

ID - внешний m разрядный вход данных,

IG - внешний m разрядный вход заданного шаблона,

IOB - внутренняя m разрядная шина данных буфера,

L - количество входных групп L=N/m,

N - размерность (длина) входной последовательности данных,

m - разрядность входных данных,

OB - выходной буфер,

QB - группа внешних выходов данных,

RG - регистр,

R - вход синхронной установки в нулевое состояние,

S - вход синхронной установки в единичное состояние,

START - внешний вход пуска,

STOP - внешний вход останова,

Т - триггер,

TR2 - триггер задержки,

TSS - триггер пуска-останова,

1 - первый RS-триггер пуска-останова TSS,

2 - второй D-триггер задержки TR2,

3 - счетчик групп CTG,

4 - выходной буфер ОВ,.

5 - первый регистр данных R1,

6 - второй регистр данных R2,

71, 72, …, 7m - группа из m компараторов (СОМР),

82, 83, …, 8m - группа из (m-1) элементов И (AND),

9 - элемент ИЛИ (OR);

10 - элемент И (AND).

Предлагаемое устройство содержит внешний m разрядный вход данных ID, внешний m разрядный вход заданного шаблона IG, группу внешних выходов данных QB, первый RS-триггер пуска-останова TSS 1, второй D-триггер TR2 задержки 2, счетчик CTG групп 3, выходной буфер ОВ 4, первый R1 регистр данных 5, второй R2 регистр данных 6, группу из m компараторов 71, 72, …, 7m, группу из (m-1) элементов И 82, 83, …, 8m, элемент ИЛИ 9 и элемент И 10.

В предлагаемое устройство также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внутренняя 2m-разрядная шина данных BD, внутренняя m-разрядная шина данных буфера IOB, внутренний флаг совпадения FE, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

Внешний вход асинхронной установки в нулевое состояние CLR соединен с соответствующими входами асинхронной установки в нулевое состояние CLR первого RS-триггера пуска-останова TSS 1 и второго D-триггера TR2 задержки.

Внешний тактовый вход устройства С соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, второго D-триггера TR2 задержки 2, счетчика CTG групп 3, выходного буфера ОВ 4, первого R1 регистра данных 5 и второго R2 регистра данных 6.

Внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1 и с входами R синхронной установки в нулевое состояние счетчика CTG групп 3, выходного буфера ОВ 4, первого R1 регистр данных 5 и второго R2 регистр данных 6.

Внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1.

Первый RS-триггер пуска-останова TSS 1 предназначен для выделения цикла работы предлагаемого устройства, между сигналами START и STOP, для входной последовательности данных DI размерности N, содержащей L групп размерности m. Причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен с D-входом второго триггера TR2 задержки 2, с входами СЕ разрешения работы первого R1 регистр данных 5 и второго R2 регистр данных 6 и вторыми входами всех элементов И группы 82, 83, …, 8m, выход второго D-триггера TR2 задержки соединен с входом СЕ разрешения работы счетчика CTG групп 3 и первым входом элемента И 10, выход которого соединен с входом СЕ разрешения записи в выходной буфер ОВ 4.

Счетчик CTG групп 3 предназначен для счета и хранения номера текущей группы входных данных. Второй D-триггер TR2 задержки 2 задерживает на один такт разрешение счета текущих групп в счетчике CTG групп 3 и записи в выходной буфер ОВ 4.

Внешний m разрядный вход заданного шаблона IG соединен с первыми группами входов всех m компараторов группы 71, 72, …, 7m, выходы которых, начиная со второго компаратора 72 до последнего 7m соединены с первыми входами соответствующих одноименных элементов И группы 82, 83, …, 8m, выходы которых являются соответствующими одноименными разрядами, начиная со второго до m-го разряда, внутренней шины данных буфера IOB. На внутренней шине IOB формируются номера разрядов начала групп совпадающих с заданным шаблоном IG.

Внешний m разрядный вход данных ID соединен с группой информационных D-входов первого R1 регистра данных 5, выходы которого являются соответствующими разрядами, начиная с (m+1)-го до 2m-го разряда, внутренней шины данных BD, а также соединены с группой информационных D-входов второго R2 регистра данных 6, выходы которого являются соответствующими разрядами, начиная с первого до m-го разряда, внутренней шины данных BD.

На внутренней шине данных BD формируется 2m-разрядный двоичный код двух соседних групп входных данных с выходов первого R1 регистра данных 5 и второго R2 регистра данных 6. Причем разряды внутренней шины данных BD группами по m разрядов, каждая из которых начинается с i-го разряда (i=1, …, m), соединены со вторыми группами соответствующих одноименных i-x компараторов группы 71, 72, …, 7m. Выход первого компаратора 71 является первым разрядом внутренней шины данных буфера IOB, которая соединена с соответствующими входами элемента ИЛИ 9, выход которого является внутренним флагом совпадения FE и соединен со вторым входом элемента И 10.

Кроме того все m разрядов внутренней шины данных буфера IOB соединены со второй группой информационных D-входов выходного буфера ОВ 4, у которого первая группа информационных D-входов соединена с выходами счетчика CTG групп 3.

Выходной буфер ОВ 4 предназначен для накопления номеров входных групп и кода расположения разрядов начала выявленных групп соответствующих коду шаблона IG. Причем выходной буфер ОВ 4 также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 16 являются группой внешних выходов данных QB и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем.

Предлагаемое устройство позволяет детектировать m-разрядные группы во входном N-разрядном двоичном числе, соответствующие m-разрядному заданному шаблону групп IG, который содержит заданную последовательность единичных и нулевых бит, формировать и записывать в выходной буфер ОВ 4 номера входных групп и кода расположения разрядов начала выявленных групп соответствующих коду шаблона. При этом разряды соседних входных групп, совпадающих с заданным шаблоном IG, могут перекрываться.

Входное N разрядное двоичное число без знака разбивается на L=N/m групп по m разрядов в каждой группе. Группы входных данных G1, G2, …, GL последовательно поступают на входы устройства. При этом m двоичных разрядов каждой из L групп параллельно поступают на соответствующие входы данных ID. В течении работы устройства на внешних входах шаблона IG должна быть установлена заданная m-разрядная последовательность единичных и нулевых бит.

Работа устройства начинается по единичному сигналу START=1 и завершается по единичному сигналу остановки STOP=l, который поступает на следующем такте после кода последней L-ой группы. Группы входных данных поступают в каждом такте.

Поиск (выявление, детектирование, анализ) осуществляется для каждых двух последовательных входных групп общей разрядностью 2m. При этом каждая входная группа G1, G2, …, GL сначала поступает на первый R1 регистр данных 5, а затем на следующем такте переписывается во второй R2 регистр данных 6 с одновременной загрузкой следующей соседней группы в первый R1 регистр данных 5. Второй TR2 триггер 2 осуществляет задержку начала анализа на один такт для загрузки второй группы и удержание на один такт для возможности записи результата в выходной буфер ОВ 4 после сигнала остановки STOP=1.

На каждом такте для двух соседних групп осуществляется поиск заданного шаблона групп IG на группе из m компараторов 71, 72, …, 7m, на первые группы входов которых поступает m-разрядный код заданного шаблона IG, а на вторые группы входов которых поступают сдвинутые на один разряд соответствующие m-разрядные коды с внутренней 2m-разрядной шины данных BD, разрядами которой являются выходы первого R1 регистра данных 5 и второго R2 регистра данных 6. Одновременно осуществляется счет входных групп G1, G2, …, GL на счетчике CTG групп 3.

На выходах группы компараторов 71, 72, …, 7m формируются единичные значения при совпадении соответствующих m-разрядных групп с внутренней 2m-разрядной шины данных BD с кодом заданного шаблона групп IG и формируется m-разрядный код расположения разрядов начала выявленных шаблонов в текущей входной группе, номер которой устанавливается в счетчике CTG групп 3. При наличии хотя бы одного совпадения на выходе элемента ИЛИ 9 формируется единичное значение флага совпадений FE=1, которое передается на элемент И 10 и по которому далее разрешается запись в выходной буфер ОВ 4 номера группы во входном N-разрядном двоичном числе и кода расположения начала выявленных шаблонов в текущей входной группе.

Группа из (m-1)-го элементов И 82, 83, …, 8m осуществляет запрет передачи результатов сравнения с (m-1) компараторов 72, 73, …, 7m, кроме первого компаратора 71, на последнем такте работы после сигнала STOP. Элемент И 10 разрешает передачу значения флага совпадений FE на вход СЕ разрешения записи в выходной буфер ОВ 4.

Предлагаемое устройство работает следующим образом.

При подаче сигнала на вход CLR асинхронной установки в нулевое состояние устанавливается первый RS-триггер пуска-останова TSS=01 и второй D-триггер задержки TR2=0. Тактовые сигналы с входа С постоянно поступают на входы синхронизации первого и второго триггеров, первого и второго регистров, счетчика групп и выходного буфера, режимы работы которых задаются сигналами на соответствующих входах управления, а исполняются по фронтам тактовых сигналов С.

На фиг. 2 приведена схема поиска заданного m=4 - разрядного шаблона IG=1011 в N=16 разрядном двоичном числе, содержащем L=8 четырехразрядных групп G1, G2, …, G8. При этом девятая группа G9 устройством не анализируется, так как она поступает одновременно с сигналом STOP. На фиг. 3 приведена временная диаграмма работы предлагаемого устройства для входных данных, приведенных на фиг. 2.

Устройство начинает работать после подачи единичного сигнала START=1 (такт 1 на фиг. 3). При этом синхронно по фронту следующего тактового сигнала С (такт 2) в единичное состояние устанавливается первый RS триггер 1 пуска-останова TSS и в нулевое состояние устанавливаются счетчик CTG групп 3, первый R1 регистр данных 5, второй R2 регистр данных 6 и устанавливается начальный нулевой адрес в выходном буфере ОВ 4.

Единичное значение с выхода первого RS-триггера 1 пуска-останова TSS=1 поступает на информационный D-вход второго триггера задержки TR2 и разрешает на следующих тактах осуществлять прием групп входных данных в первый R1 регистр данных 5 с внешнего входа данных ID и запись данных с первого R1 регистра данных 5 во второй R2 регистр данных. При этом на фиг. 2 и фиг. 3 младшие разряды в группах ID, в шаблоне IG, в первом R1 и втором R2 регистрах, на компараторах СОМР и внутренних шинах показаны слева.

В такте 2 на входе шаблона IG устанавливается код 1011, который удерживается во время работы устройства, и на вход данных ID также поступает код 1011 первой группы G1, который записывается в такте 3 в первый R1 регистр данных 5. Одновременно в такте 3 в единичное состояние переключается второй триггер задержки TR2, который разрешает на следующих тактах работать в счетном режиме счетчику CTG групп 3, на котором устанавливается код номера текущей группы, и разрешает передачу значения флага совпадений FE через элемент И 10 на вход СЕ разрешения записи в выходной буфер ОВ 4.

В такте 3 на вход данных ID поступает код ОНО второй группы G2, который записывается в такте 4 в первый R1 регистр данных 5, и одновременно код 1011 с выходов первого R1 регистра данных 5 записывается во второй R2 регистр данных 6. Также в такте 3 увеличивается на единицу значение в счетчике 3 групп CTG=1. При этом на внутренней 2m-разрядной шине данных BD устанавливается 8-разрядный код 1011 ОНО. Далее группами по m разрядов, начиная с первого разряда (левого младшего) и сдвигом начала групп на один разряд в сторону старших разрядов, коды поступают на вторые группы входов соответствующих компараторов 71, 72, …, 7m, а на первые группы входов которых поступает m-разрядный код заданной шаблона IG=1011. При этом единичные значения формируются на выходах двух компараторов СОМР 71, 74 и устанавливается код 1001, что означает совпадение с шаблоном в двух группах (см. фиг. 2 и фиг. 3), начинающихся с младшего первого и старшего четвертого разрядов первой входной группы G1. Далее этот код 1001, при единичном значении первого RS-триггера 1 пуска-останова TSS=1, через группу элементов И 82, 83, …, 8m передается на внутреннюю шину данных буфера IOB и на входы элемента ИЛИ 9. Поэтому формируется единичное значение флага совпадений FE=1. Далее единичное значение устанавливается на выходе элемента И 10, так как установлен в единичное состояние второй D-триггер задержки TR2=1, и далее разрешается запись в выходной буфер ОВ 4, в который в такте 5 по нулевому адресу записывается код ОВ(0)=1_1001, соответствующий номеру первой группы G1 со счетчика CTG групп 3, и коду первого и четвертого разрядов расположения начала выявленных шаблонов в текущей первой группе G1, который поступает с внутренней шины данных буфера IOB.

При этом одновременно в такте 4 на вход данных ID поступает код 1100 третьей группы G3, который записывается в такте 5 в первый R1 регистр данных 5, и одновременно код 0110 с выходов первого R1 регистра данных 5 записывается во второй R2 регистр данных 6. Одновременно в такте 5 увеличивается на единицу значение в счетчике 3 групп CTG=2. Поэтому на внутренней 2m-разрядной шине данных BD устанавливается код 0110 1100. При этом совпадение с шаблоном IG=1011 будет выявлено только в одной группе на третьем компараторе СОМР 73. Поэтому далее при единичном значении первого RS-триггера 1 пуска-останова TSS=1 на внутренней шине данных буфера IOB будет установлен код 0010, а также формируется единичное значение флага совпадений FE=1, по которому далее в такте 6 в выходной буфер ОВ 4 по первому адресу записывается код ОВ(1)=2_0010, соответствующий входной второй группе G2 и третьему разряду начала группы соответствующей заданному шаблону IG=1011.

Одновременно в такте 5 на вход данных ID поступает код 1101 четвертой группы G4, который записывается в такте 6 в первый R1 регистр данных 5, и одновременно код 1100 с выходов первого R1 регистра данных 5 записывается во второй R2 регистр данных 6, а также увеличивается на единицу значение в счетчике 3 групп CTG=3. Поэтому далее на внутренней 2m-разрядной шине данных BD устанавливается код 1100 1101. При этом на компараторах устанавливаются нулевые значения, код 0000, так как не обнаружено совпадений с шаблоном IG=1011. Поэтому формируется также нулевое значение флага совпадений FE=0 и в такте 7 отсутствует запись в выходной буфер ОВ 4.

В такте 6 на вход данных ID поступает код 1011 пятой группы G5, который записывается в такте 7 в первый R1 регистр данных 5, и одновременно код 1101 с выходов первого R1 регистра данных 5 записывается во второй R2 регистр данных 6, а также увеличивается на единицу значение в счетчике 3 групп CTG=4 и далее на внутренней 2m-разрядной шине данных BD устанавливается код 1011 1011. При этом в группе компараторов совпадение с шаблоном IG=1011 будет выявлено только в одной группе на втором компараторе СОМР 72, Далее формируются код 0100 на внутренней шине данных буфера IOB и единичное значение флага совпадений FE=1, по которому в такте 8 в выходной буфер ОВ 4 по второму адресу записывается код ОВ(2)=4_0100, соответствующий входной четвертой группе G4 и второму разряду начала расположения группы соответствующей заданному шаблону IG=1011.

Далее в тактах 9 и 10 аналогично рассмотренному алгоритму при единичных значениях флага совпадений FE=1 осуществляется запись для выявленных входных пятой G5 и шестой G6 группах соответствующих кодов по третьему ОВ(3)=5_1001 и четвертому ОВ(4)=6_0010 адресам в выходной буфер ОВ 4.

Одновременно в такте 9 на вход данных ID поступает код 1011 восьмой группы G8, который записывается в такте 10 в первый R1 регистр данных 5, и одновременно код 1101 с выходов первого R1 регистра данных 5 записывается во второй R2 регистр данных 6, а также увеличивается на единицу значение в счетчике 3 групп CTG=7. Далее на внутренней 2m-разрядной шине данных BD устанавливается код 1101 1011 для которого в группе компараторов совпадение с шаблоном IG=1011 будет выявлено только в одной группе на втором компараторе СОМР 72 и далее формируются код 0100 на внутренней шине данных буфера IOB и единичное значение флага совпадений FE=1, по которому в такте 11 в выходной буфер ОВ 4 по пятому адресу записывается код ОВ(5)=7_0100, соответствующий входной седьмой группе G7 и второму разряду начала расположения группы соответствующей заданному шаблону IG=1011.

Одновременно в такте 10 поступает единичный сигнал STOP=1, по которому по фронту тактового сигнала С в такте 11 в нулевое состояние устанавливается первый RS-триггер 1 пуска-останова TSS=0. При этом код ОНО с входа данных ID для девятой группы G9 записывается в такте 11 в первый R1 регистр данных 5, и одновременно код 1011 для восьмой группы G8 с выходов первого R1 регистра данных 5 записывается во второй R2 регистр данных 6, а также увеличивается на единицу значение в счетчике 3 групп CTG=8. При этом в группе компараторов совпадение с шаблоном IG=1011 будет выявлено в двух группах на первом и четвертом компараторах СОМР 71 и 74 и на выходах компараторов формируется код 1001. Но так как в такте 11 нулевое состояние установлено в первом RS-триггер 1 пуска-останова TSS=0, то запрещается передача значений в группе из (m-1)-го элементов И 82, 83, …, 8m, т.е. разрешается детектирование только в первом компараторе СОМР 71. Поэтому на внутренней шине данных буфера IOB устанавливается код 1000, который в такте 12 записывается вместе с номером восьмой группы G8 в шестой адрес ОВ(6)=8_1000 в выходной буфер ОВ 4.

Таким образом, для входного N=16 разрядного двоичного числа приведенного на фиг. 2 в выходной буфер ОВ 4 записаны по семи адресам ОВ(0), …, ОВ(6) номера входных групп и разряды соответствующие расположению начала групп в них соответствующих заданному шаблону IG=1011.

Считывание результатов на группу внешних выходов данных QB из выходного буфера ВО 4 выполняется под управлением по внешней шине управления ЕО. При реализации выходного буфера ВО 11 в виде двухпортовой памяти FIFO, обмен можно выполнять в процессе детектирования групп с учетом значений флагов «Буфер пуст» FZ и «Буфер заполнен» FF.

Обработка следующего входного N разрядного двоичного числа начинается после подачи единичного сигнала START=1.

Предлагаемое устройство может быть применено для аппаратной реализации статистических тестов разработанных лабораторией информационных технологий Национального института стандартов и технологий (NIST, США), целью которых является определение меры случайности двоичных последовательностей порожденных генераторами случайных чисел. В частности предлагаемое устройство реализует тест на совпадение перекрывающихся заданных шаблонов размерностью m бит с группами из входных данных также размерностью m бит. При этом независимо от совпадения или несовпадения шаблону соседние группы из входных данных сдвигаются на один бит вперед. Цель - выявить генераторы случайных или псевдослучайных чисел, формирующие слишком часто заданные непериодические шаблоны.

При обработке результатов физических экспериментов предлагаемое устройство обеспечивает выявление непериодических событий (шаблонов - заданной группы из последовательностей единичных бит (длительности событий) и нулевых бит (интервалов между ними)) и координат событий.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу и соответствует заявляемому техническому результату - выявление шаблонов содержащих заданные группы (последовательности) из единичных и нулевых бит и их расположение во входных данных.

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных. Техническим результатом изобретения является обеспечение возможности выявления m-разрядных групп бит в N-разрядной последовательности данных. Технический результат достигается за счет того, что устройство для детектирования групп бит содержит внешний m разрядный вход данных ID, внешний m разрядный вход заданного шаблона IG, группу внешних выходов данных QB, первый RS-триггер пуска-останова TSS 1, второй D-триггер TR2 задержки 2, счетчик CTG групп 3, выходной буфер ОВ 4, первый R1 регистр данных 5, второй R2 регистр данных 6, группу из m компараторов 71, 72, …, 7m, группу из (m-1) элементов И 82, 83, …, 8m, элемент ИЛИ 9 и элемент И 10, а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внутренняя 2m-разрядная шина данных BD, внутренняя m-разрядная шина данных буфера IOB, внутренний флаг совпадения FE, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ. 3 ил.

Устройство для детектирования групп бит содержит внешний m разрядный вход данных ID, внешний m разрядный вход заданного шаблона IG, группу внешних выходов данных QB, первый RS-триггер пуска-останова TSS 1, второй D-триггер TR2 задержки 2, счетчик CTG групп 3, выходной буфер ОВ 4, первый R1 регистр данных 5, второй R2 регистр данных 6, группу из m компараторов 71, 72, …, 7m, группу из (m-1) элементов И 82, 83, …, 8m, элемент ИЛИ 9 и элемент И 10,

а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внутренняя 2m-разрядная шина данных BD, внутренняя m-разрядная шина данных буфера IOB, внутренний флаг совпадения FE, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ,

причем внешний вход асинхронной установки в нулевое состояние CLR соединен с соответствующими входами асинхронной установки в нулевое состояние CLR первого RS-триггера пуска-останова TSS 1 и второго D-триггера TR2 задержки,

внешний тактовый вход устройства С соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, второго D-триггера TR2 задержки 2, счетчика CTG групп 3, выходного буфера ОВ 4, первого R1 регистра данных 5 и второго R2 регистра данных 6,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1 и с входами R синхронной установки в нулевое состояние счетчика CTG групп 3, выходного буфера ОВ 4, первого R1 регистр данных 5 и второго R2 регистр данных 6,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1,

причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен с D-входом второго триггера TR2 задержки 2, с входами СЕ разрешения работы первого R1 регистр данных 5 и второго R2 регистр данных 6 и вторыми входами всех элементов И группы 82, 83, …, 8m, выход второго D-триггера TR2 задержки соединен с входом СЕ разрешения работы счетчика CTG групп 3 и первым входом элемента И 10, выход которого соединен с входом СЕ разрешения записи в выходной буфер ОВ 4,

причем внешний m разрядный вход заданного шаблона IG соединен с первыми группами входов всех m компараторов группы 71, 72, …, 7m, выходы которых, начиная со второго компаратора 72 до последнего 7m, соединены с первыми входами соответствующих одноименных элементов И группы 82, 83, …, 8m, выходы которых являются соответствующими одноименными разрядами, начиная со второго до m-го разряда, внутренней шины данных буфера IOB,

внешний m разрядный вход данных ID соединен с группой информационных D-входов первого R1 регистра данных 5, выходы которого являются соответствующими разрядами, начиная с (m+1)-го до 2m-го разряда, внутренней шины данных BD, а также соединены с группой информационных D-входов второго R2 регистра данных 6, выходы которого являются соответствующими разрядами, начиная с первого до m-го разряда, внутренней шины данных BD,

причем разряды внутренней шины данных BD группами по m разрядов, каждая из которых начинается с i-го разряда (i=1, …, m), соединены со вторыми группами соответствующих одноименных i-x компараторов группы 71, 72, …, 7m, а выход первого компаратора 71 является первым разрядом внутренней шины данных буфера IOB, которая соединена с соответствующими входами элемента ИЛИ 9, выход которого является внутренним флагом совпадения FE и соединен со вторым входом элемента И 10,

кроме того, все m разрядов внутренней шины данных буфера IOB соединены со второй группой информационных D-входов выходного буфера ОВ 4, у которого первая группа информационных D-входов соединена с выходами счетчика CTG групп 3,

причем выходной буфер ОВ 4 также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 16 являются группой внешних выходов данных ОВ и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2728957C1 |

| УСТРОЙСТВО ПЕРЕСТАНОВОК И СДВИГОВ БИТОВ ДАННЫХ В МИКРОПРОЦЕССОРАХ | 2011 |

|

RU2488161C1 |

| FR 2997772 A1, 09.05.2014 | |||

| US 6904114 B2, 07.06.2005 | |||

| УСТРОЙСТВО ПОСЛЕДОВАТЕЛЬНОГО ТИПА ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2018 |

|

RU2680759C1 |

Авторы

Даты

2022-10-04—Публикация

2021-12-01—Подача