ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также для обработки результатов физических экспериментов.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известно устройство для определения количества единиц в упорядоченном двоичном числе (RU №2522875, МПК Н03К 21/12, заявлено 24.05.2012, опубликовано 20.07.2014, Бюл. №20), содержащее буферы с тремя состояниями с прямым и инверсным входами разрешения, n разрядов входного двоичного числа, (k+1) разрядов выходного двоичного кода (k=[log2n] меньшее целое), причем буферы с тремя состояниями объединены в пирамидальную структуру, состоящую из (m-1) ступеней (m=]log2n[большее целое), и в выходной блок, содержащий к буферов с тремя состояниями с инверсным входом разрешения и к буферов с тремя состояниями с прямым входом разрешения, при этом каждая i-я ступень (i=1, …, (m-1)) содержит (2i-1) буферов с тремя состояниями с инверсным входом разрешения и 2i-1 буферов с тремя состояниями с прямым входом разрешения.

Недостатком данного устройства является определение количества единиц в упорядоченном двоичном числе, а не выявление диапазона единичных бит.

Известно устройство для определения количества единиц (нулей) в двоичном числе (RU №2446442, МПК G06 F7/50, Н03К 21/00, заявлено 11.04.2011, опубликовано 27.03.2012, Бюл. №9), содержащее блок управляемой инверсии, состоящий из n-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ» (n - количество разрядов входного числа), элементы ИЛИ и модули, состоящие из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, которые объединены в группы, состоящие из ярусов, и объединены в k-каскадов (k=]log2n[), так, что каждый i-й каскад содержит g(i)=n/2i групп (i=1, …, k), каждая группа i-го каскада разделена на j ярусов (j=1, …, i), при этом первый ярус каждой группы i-го каскада содержит i модулей, а каждый j-й ярус каждой группы i-го каскада (j=2, …, i,) содержит (i-j) модулей и элемент «ИЛИ».

Недостатком данного устройства является определение только общего количества единиц (нулей) в двоичном числе, а не выявление диапазона единичных бит.

Известен указатель старшей единицы (Угрюмов Е.П. Цифровая схемотехника. -СПб.: БХВ-Петербург, 2000. - 528 с, рис. 2.8 с. 50-54), содержащий группу элементов И и группу элементов запрета И с одним инверсным входом. В данном устройстве реализована цепочечная схема передачи сигнала опроса путем последовательного опроса, начиная со старшего разряда, и прекращения дальнейшего опроса при выявлении первой же единицы.

Недостатком данного устройства является выявление только одного старшего единичного бита.

Известно устройство для детектирования диапазона единичных бит (RU №2717631 С1, МПК G06F7/74, заявлено 07.11.2019, опубликовано 24.03.2020, Бюл. №9), содержащее N разрядов входной шины D - D1, D2, …, DN, N разрядов выходной шины Q - Q1, Q2, …, QN, первую группу из (N-2) элементов ИЛИ 11, 12, …, 1(N-2), вторую группу из (N-2) элементов ИЛИ 21, 22, …, 2(N-2) и группу из (N-2) элементов И 31, 32, …, 3(N-2). Причем первая группа элементов ИЛИ 11, 12, …, 1(N-2), объединенных в цепочку, формирует упорядоченную группу подряд идущих единиц в младших разрядах, вторая группа элементов ИЛИ 21, 22, …, 2(N-2) формирует упорядоченную группу единиц в старших разрядах, а в группе элементов И 31, 32, …, 3(N-2) осуществляется проверка единичных значений в одноименных разрядах упорядоченных групп единиц.

Недостатком данного устройства является только выявление младшего и старшего бит диапазона единичных бит для параллельно поступающего N разрядного входного двоичного числа и заполнение диапазона единичными битами, без вычисления номеров бит.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство для детектирования границ диапазона единичных бит (RU №2717934 С1, МПК G06F 7/74, Н03К 21/00 заявлено 19.12.2019, опубликовано 27.03.2020, Бюл. №9), содержащее N разрядную входную шину D, выходную шину QR номера младшего разряда и выходную шину QL номера старшего разряда содержащие по М разрядов, где M=]log2(N+1)[(большее целое), группу из (N-1) элементов ИЛИ 11, 12, …, 1(N-1), группу из (N-1) элементов ИЛИ-НЕ 21, 22, …, 2(N-1), первый 31 и второй 32 блоки счета младших упорядоченных единиц, а также внутреннюю шину SR сдвига вправо и внутреннюю шину SL сдвига влево, которые содержат по N разрядов.

Недостатком данного устройства является определение границ только для параллельно поступающего N разрядного входного двоичного числа.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является выявление номера левого (старшего) единичного бита и номера правого (младшего) единичного бита во входных данных и оценка ширины диапазона.

При обработке результатов физических экспериментов устройство предназначено для выявления диапазона событий.

Техническим результатом изобретения является расширение арсенала средств того же назначения, в части возможности выявления границ диапазона единичных бит и оценки ширины диапазона, а также фиксация номера левого (старшего) единичного бита и номера правого (младшего) единичного бита во входных данных и кода ширины диапазона.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что устройство параллельно-последовательной структуры для детектирования границ диапазона единичных бит содержит М разрядов D1, …, DM группы входных данных из N разрядного двоичного числа, состоящего из L наборов по М разрядов в группе, где N=L*M, n разрядную выходную шину 23 номера старшего единичного разряда QM, где n=]log2(N+1)[(большее целое), n разрядную выходную шину 24 ширины диапазона QD, n разрядную выходную шину 25 номера младшего единичного разряда QL, группу из (М-1) элементов ИЛИ 11, 12, …, 1(M-1), группу из (М-1) элементов ИЛИ-НЕ 21, 22, …, 2(M-1), первый 31 и второй 32 блоки счета младших упорядоченных единиц, а также внутреннюю шину SR сдвига вправо и внутреннюю шину SL сдвига влево, которые содержат по М разрядов, внутреннюю m разрядную шину номера младшего единичного бита UL в М-разрядной группе, где m=]log2(M+1)[(большее целое), внутреннюю m разрядную шину номера старшего единичного бита UM в М-разрядной группе, внутреннюю n разрядную шину текущей разрядности числа BD,

элемент ИЛИ 4, первый регистр 5 текущей разрядности числа, первый триггер 6 пуска-останова TSS, второй триггер 7 единичных бит TU, первый 8 и второй 9 элементы И, первый 10 сумматор групп SMG, второй 11 сумматор старших номеров SMM, третий 12 сумматор младших номеров SML, инкрементор 13 увеличения старшего номера INC, четвертый 14 сумматор разрядности диапазона SMD, мультиплексор MX 15, выходные второй 16, третий 17 и четвертый 18 регистры, а также внешний вход 19 остановки STOP, внешний вход 20 начала работы START, внешний вход 21 тактовых сигналов С, внешний вход 22 асинхронной установки в нулевое состояние CLR, причем внешний вход С тактовых сигналов 21 и внешний вход CLR асинхронной установки в нулевое состояние 22 соединены с соответствующими входами С тактовых сигналов и входами CLR асинхронной установки в нулевое состояние первого триггера 6 пуска-останова TSS, второго триггера 7 единичных бит TU, первого регистра 5 текущей разрядности числа, выходных второго 16, третьего 17 и четвертого 18 регистров,

внешний вход 20 начала работы START соединен с входом S синхронной установки в единичное состояние первого триггера TSS пуска-останова 6,

внешний вход 19 остановки STOP соединен с входом R синхронной установки в нулевое состояние триггера TSS пуска-останова 6, выход которого соединен с входом разрешения работы СЕ первого регистра 5 текущей разрядности числа и с первым входом первого элемента И 8, выход которого соединен с входами разрешения работы СЕ выходных второго 16 и третьего 17 регистров,

причем первые (М-1) разрядов D1, D2, …, D(M-1) входной шины D, начиная с первого до (M-1)-го разрядов, соединены со вторыми входами соответствующих (М-1) элементов ИЛИ, начиная с первого до (M-1)-го элементов 11, 12, …, 1(M-1), а также соединены с первыми прямыми входами соответствующих (М-1) элементов ИЛИ-НЕ, начиная с первого до (M-1)-го элементов 21, 22, …, 2(М-1), а также все М разрядов D1, D2, …, DM входной шины D соединены с одноименными входами элемента ИЛИ 4,

при этом первые входы первых (М-2) элементов ИЛИ, начиная с первого до (М-2)-го элементов 11, 12, …, 1(М-2), соединены с выходами соответствующих последующих (М-2) элементов ИЛИ, начиная со второго до (M-1)-го элементов 12, 13, …, 1(M-1), а первый вход (M-1)-го элемента ИЛИ 1(M-1) соединен с М-ым разрядом DM входной шины D,

кроме того выходы всех (М-1) элементов ИЛИ 11, 12, …, 1(M-1) являются соответствующими одноименными (М-1) разрядами внутренней шины SR сдвига вправо, у которой старший М-ый разряд соединен с М-ым разрядом DM входной шины D, а все М разрядов шины SR сдвига вправо подключены к входам первого 31 блока счета младших упорядоченных единиц,

причем третьи инверсные входы (М-2) элементов ИЛИ-НЕ, начиная со второго до (M-1)-го элементов 22, 23, …, 2(M-1), соединены с инверсными выходами соответствующих предыдущих (М-2) элементов ИЛИ-НЕ, начиная с первого до (М-2)-го элементов 21, 22, …, 2(M-2), кроме того вторые инверсные входы всех (M-1)-го элементов ИЛИ-НЕ 21, 22, …, 2(M-1) соединены между собой, а также подключены к выходу первого элемента ИЛИ 11 из группы элементов ИЛИ 11, 12, …, 1(M-1),

кроме того инверсные выходы всех (М-1) элементов ИЛИ-НЕ 21, 22, …, 2(M-1) являются соответствующими (М-1) разрядами внутренней шины SL сдвига влево, начиная со второго до М-го разряда, а младший первый разряд шины SL сдвига влево соединен с выходом первого элемента ИЛИ 11 из группы элементов ИЛИ 11, 12, …, 1(M-1), а все М разрядов шины SL сдвига влево подключены к входам второго 32 блока счета младших упорядоченных единиц,

причем выходы первого 31 и второго 32 блоков счета младших упорядоченных единиц являются соответствующими m разрядами соответственно внутренней шины UM номера разряда старшего единичного бита и внутренней шины UL номера разряда младшего единичного бита в М-разрядной группе,

причем значение кода числа «М» подано на группу входов второго слагаемого первого 10 сумматора групп SMG, выход которого соединен с группой D-входов первого регистра 5 текущей разрядности числа, выходы которого являются соответствующими n разрядами внутренней шины текущей разрядности числа BD и соединены с группой входов первого слагаемого первого 10 сумматора групп SMG, с группой входов второго слагаемого второго 11 сумматора старших номеров SMM и с группой входов второго слагаемого третьего12 сумматора младших номеров SML,

кроме того выход элемента ИЛИ 4 является флагом единичных бит FU и соединен со вторыми входами первого 8 и второго 9 элементов И и соединен с входом S синхронной установки в единичное состояние второго триггера 7 единичных бит TU, инверсный выход которого соединен с первым входом второго элемента И 9, выход которого соединен с адресным А входом мультиплексора MX 15 и с входом разрешения работы СЕ четвертого выходного регистра 18,

причем разряды внутренней шины UM номера разряда старшего единичного бита и внутренней шины UL номера разряда младшего единичного бита в М-разрядной группе соединены с соответствующими разрядами групп входов первых слагаемых соответственно второго 11 сумматора старших номеров SMM и третьего 12 сумматора младших номеров SML,

кроме того выход второго 11 сумматора старших номеров SMM соединен с группой D-входов второго выходного регистра 16 и с первой группой информационных входов инкрементора 13 увеличения старшего номера INC, у которого на второй вход увеличения подано значение логической единицы «1», а выход инкрементора 13 увеличения старшего номера INC соединен с группой прямых входов первого слагаемого четвертого 14 сумматора разрядности диапазона SMD,

причем выход третьего 12 сумматора младших номеров SML соединен с первой группой информационных входов мультиплексора MX 15 и с группой D-входов четвертого выходного регистра 18, выход которого соединен с нулевой группой информационных входов мультиплексора MX 15, выход которого соединен с группой инверсных входов второго слагаемого четвертого 14 сумматора разрядности диапазона SMD, у которого на вход переноса CI подано значение логической единицы «1», а выход четвертого 14 сумматора разрядности диапазона SMD соединен с группой D-входов третьего выходного регистра 17,

причем разряды выходов второго выходного регистра 16 являются n разрядами выходной шины 23 номера старшего единичного разряда QM, разряды выходов третьего выходного регистра 17 являются n разрядами выходной шины 24 ширины диапазона QD, разряды выходов четвертого выходного регистра 18 являются n разрядами выходной шины 25 номера младшего единичного разряда QL.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

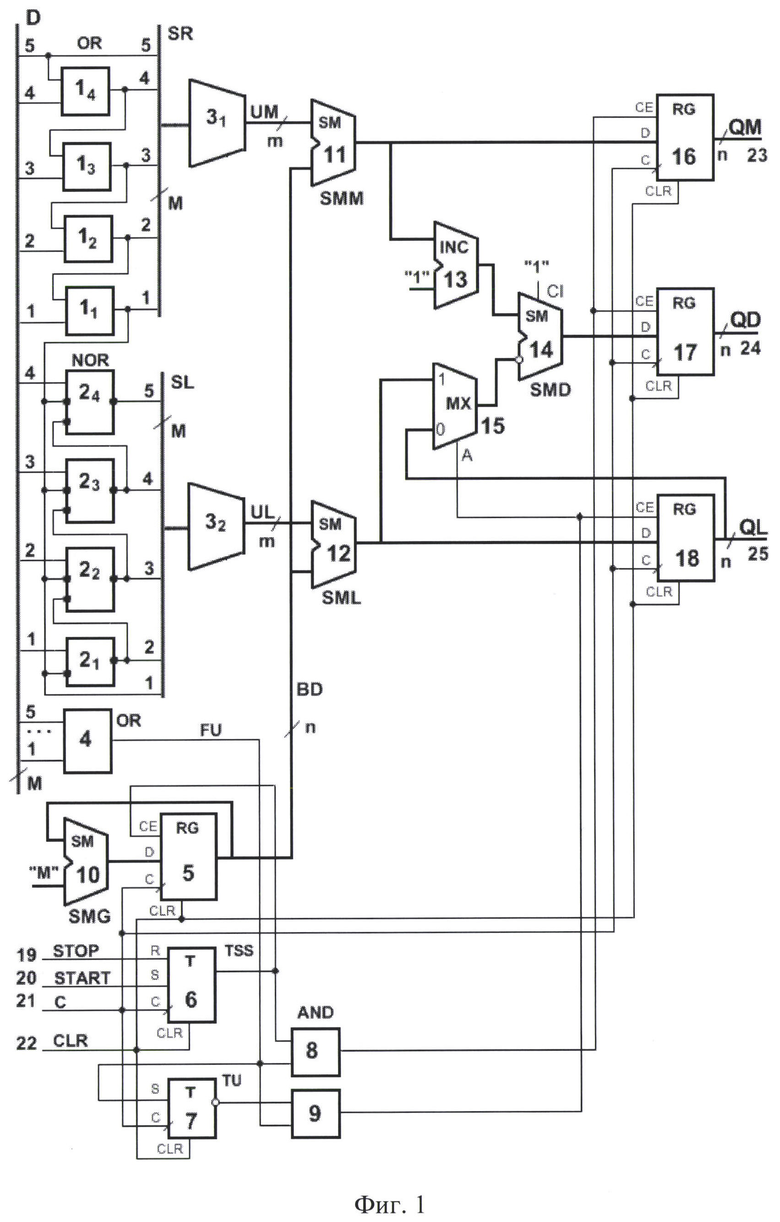

На фиг. 1 представлена функциональная схема предлагаемого устройства параллельно-последовательной структуры для детектирования границ диапазона единичных бит при количестве разрядов М=5 входной шины D - D1, D2, …, D5(M). На фиг. 2 приведена потактовая временная диаграмма работы для тестовых примеров при количестве разрядов входного двоичного числа N=20, количестве разрядов в группе входных данных М=5 и количестве групп L=4.

На фиг. 1, фиг. 2 и в тексте введены следующие обозначения:

N - количество разрядов входного двоичного числа,

М - количество разрядов в группе входных данных,

L- количество групп во входном двоичном числе, где N=M*L,

D - N разрядная входная шина;

D1, D2, …, D5 (DM) - двоичные разряды М-разрядной группы входной шины;

QL - n разрядная выходная шина номера младшего единичного разряда N разрядного двоичного числа, где n=]log2(N+1)[(большее целое);

QD - n разрядная выходная шина ширины диапазона N разрядного двоичного числа;

QM - n разрядная выходная шина номера старшего единичного разряда N разрядного двоичного числа;

SR - М разрядная внутренняя шина сдвига вправо в сторону младших разрядов;

SL - М разрядная внутренняя шина сдвига влево в сторону старших разрядов;

UL - внутренняя m разрядная шина номера младшего единичного бита в М-разрядной группе, где m=]log2(M+1)[(большее целое);

UM - внутренняя m разрядная шина номера старшего единичного бита в М-разрядной группе;

BD - внутренняя n разрядная шина текущей разрядности числа;

С - тактовый вход;

СЕ - вход разрешения работы;

CLR - вход асинхронной установки в нулевое состояние;

R - вход синхронной установки в нулевое состояние;

S - вход синхронной установки в единичное состояние;

START - внешний вход начала работы;

STOP - внешний вход остановки;

FU - флаг единичных бит;

Т - триггер;

RG -регистр;

MX - мультиплексор;

SM - сумматор;

А - адресный вход мультиплексора MX;

CI - входной перенос сумматора;

SMG - сумматор групп;

SML- сумматор младших номеров;

SMM - сумматор старших номеров;

SMD - сумматор разрядности диапазона;

INC - инкрементор увеличения старшего номера;

OR - элемент ИЛИ;

NOR - элемент ИЛИ-НЕ;

AND - элемент И;

TSS - триггер пуска-останова;

TU - триггер единичных бит;

i - правый (младший) разряд, имеющий единичное значение, где1≤i≤М;

j - левый (старший) разряд, имеющий единичное значение, где i≤j, 1≤j≤M;

11, 12, …, 1(M-1) - группа из (М-1) элементов ИЛИ (OR);

21, 22, …, 2(M-1) - группа из (М-1) элементов ИЛИ-НЕ (NOR);

31, 32 - первый и второй блоки счета младших упорядоченных единиц;.

4 - элемент ИЛИ (OR);

5 - первый регистр текущей разрядности числа;

6 - первый триггер пуска-останова TSS;

7 - второй триггер единичных бит TU;

8 - первый элемент И (AND);

9 - второй элемент И (AND);

10 - первый сумматор групп SMG;

11 - второй сумматор старших номеров SMM;

12 - третий сумматор младших номеров SML;

13 - инкрементор увеличения старшего номера INC;

14 - четвертый сумматор разрядности диапазона SMD;

15 - мультиплексор MX;

16 - второй выходной регистр номера старшего единичного бита;

17 - третий выходной регистр ширины диапазона;

18 - четвертый выходной регистр номера младшего единичного бита;

19 - внешний вход остановки STOP;

20 - внешний вход начала работы START;

21 - внешний вход тактовых сигналов С;

22 - внешний вход асинхронной установки в нулевое состояние CLR;

23 - n разрядная выходная шина номера старшего единичного разряда QM;

24 - n разрядная выходная шина ширины диапазона QD;

25 - n разрядная выходная шина номера младшего единичного разряда QL. Предлагаемое устройство параллельно-последовательной структуры для детектирования границ диапазона единичных бит содержит М разрядов D1, DM группы входных данных из N разрядного двоичного числа, состоящего из L наборов по М разрядов в группе, где N=L*M, n разрядную выходную шину 23 номера старшего единичного разряда QM, где n=]log2(N+1)[(большее целое), n разрядную выходную шину 24 ширины диапазона QD, n разрядную выходную шину 25 номера младшего единичного разряда QL, группу из (М-1) элементов ИЛИ 11, 12, …, 1(M-1), группу из (М-1) элементов ИЛИ-НЕ 21, 22, …, 2(M-1), первый 31 и второй 32 блоки счета младших упорядоченных единиц, а также внутреннюю шину SR сдвига вправо и внутреннюю шину SL сдвига влево, которые содержат по М разрядов, внутреннюю m разрядную шину номера младшего единичного бита UL, где m=]log2(M+1)[(большее целое), внутреннюю m разрядную шину номера старшего единичного бита UM в М-разрядной группе, внутреннюю n разрядную шину текущей разрядности числа BD, элемент ИЛИ 4, первый регистр 5 текущей разрядности числа, первый триггер 6 пуска-останова TSS, второй триггер 7 единичных бит TU, первый 8 и второй 9 элементы И, первый 10 сумматор групп SMG, второй 11 сумматор старших номеров SMM, третий 12 сумматор младших номеров SML, инкрементор 13 увеличения старшего номера INC, четвертый 14 сумматор разрядности диапазона SMD, мультиплексор MX 15, выходные второй 16, третий 17 и четвертый 18 регистры, а также внешний вход 19 остановки STOP, внешний вход 20 начала работы START, внешний вход 21 тактовых сигналов С, внешний вход 22 асинхронной установки в нулевое состояние CLR.

Группа элементов ИЛИ 11, 12, …, 1(M-1) предназначена для формирования упорядоченной группы единиц (подряд идущих) в младших разрядах, начиная с первого разряда до j-го левого (старшего) единичного разряда. Группа элементов ИЛИ-НЕ 21, 22, 2(м-1) предназначена для формирования упорядоченной группы единиц в младших разрядах, начиная со второго разряда до i-го разряда (где i-й правый (младший) единичный разряд). Подсчет младших упорядоченных единиц в первом 31 и втором 32 блоках счета осуществляется соответственно с шины SR сдвига вправо и с шины SL сдвига влево.

Первый триггер пуска-останова TSS 6 принимает единичное значение по фронту синхросигнала С между сигналами внешними сигналами начала работы START и остановки STOP. Флаг единичных бит FU принимает единичное значение при наличии единичных бит в М-разрядной группе входной шины D1, D2, …, DM. Первый 10 сумматор групп SMG и первый регистр текущей разрядности числа 5 образуют накапливающий сумматор и осуществляют подсчет по М разрядов групп. На четвертом 14 сумматоре разрядности диапазона SMD осуществляется вычитание номера младшего единичного разряда из текущего номера старшего единичного разряда N разрядного двоичного числа. Выходные второй 16, четвертый 18 и третий 17 регистры предназначены для фиксации номера левого (старшего) единичного бита и номера правого (младшего) единичного бита во входных данных и кода ширины диапазона.

Причем внешний вход С тактовых сигналов 21 и внешний вход CLR асинхронной установки в нулевое состояние 22 соединены с соответствующими входами С тактовых сигналов и входами CLR асинхронной установки в нулевое состояние первого триггера 6 пуска-останова TSS, второго триггера 7 единичных бит TU, первого регистра 5 текущей разрядности числа, выходных второго 16, третьего 17 и четвертого 18 регистров.

Внешний вход 20 начала работы START соединен с входом S синхронной установки в единичное состояние первого триггера TSS пуска-останова 6.

Внешний вход 19 остановки STOP соединен с входом R синхронной установки в нулевое состояние триггера TSS пуска-останова 6, выход которого соединен с входом разрешения работы СЕ первого регистра 5 текущей разрядности числа и с первым входом первого элемента И 8, выход которого соединен с входами разрешения работы СЕ выходных второго 16 и третьего 17 регистров.

Причем первые (М-1) разрядов D1, D2, …, D(M-1) входной шины D, начиная с первого до (M-1)-го разрядов, соединены со вторыми входами соответствующих (М-1) элементов ИЛИ, начиная с первого до (M-1)-го элементов 11, 12, …, 1(M-1), а также соединены с первыми прямыми входами соответствующих (М-1) элементов ИЛИ-НЕ, начиная с первого до (M-1)-го элементов 21, 22, …, 2(M-1). Все М разрядов D1, D2, …, DM входной шины D соединены с одноименными входами элемента ИЛИ 4.

При этом первые входы первых (М-2) элементов ИЛИ, начиная с первого до (М-2)-го элементов 11, 12, …, 1(M-2), соединены с выходами соответствующих последующих (М-2) элементов ИЛИ, начиная со второго до (M-1)-го элементов 12, 13, …, 1(M-1), а первый вход (M-1)-го элемента ИЛИ 1(M-1) соединен с М-ым разрядом DM входной шины D.

Кроме того выходы всех (М-1) элементов ИЛИ 11, 12, …, 1(M-1) являются соответствующими одноименными (М-1) разрядами внутренней шины SR сдвига вправо, у которой старший М-ый разряд соединен с М-ым разрядом DM входной шины D. Все М разрядов шины SR сдвига вправо подключены к входам первого 31 блока счета младших упорядоченных единиц.

Причем третьи инверсные входы (М-2) элементов ИЛИ-НЕ, начиная со второго до (M-1)-го элементов 22, 23, …, 2(M-1), соединены с инверсными выходами соответствующих предыдущих (М-2) элементов ИЛИ-НЕ, начиная с первого до (М-2)-го элементов 21, 22, …, 2(M-2). Кроме того вторые инверсные входы всех (M-1)-го элементов ИЛИ-НЕ 21, 22, …, 2(M-1) соединены между собой, а также подключены к выходу первого элемента ИЛИ 11 из группы элементов ИЛИ 11, 12, …, 1(M-1).

Кроме того инверсные выходы всех (М-1) элементов ИЛИ-НЕ 21, 22, …, 2(M-1) являются соответствующими (М-1) разрядами внутренней шины SL сдвига влево, начиная со второго до М-го разряда. Младший первый разряд шины SL сдвига влево соединен с выходом первого элемента ИЛИ 11 из группы элементов ИЛИ 11, 12, …, 1(M-1). Все М разрядов шины SL сдвига влево подключены к входам второго 32 блока счета младших упорядоченных единиц.

Причем выходы первого 31 и второго 32 блоков счета младших упорядоченных единиц являются соответствующими m разрядами соответственно внутренней шины UM номера разряда старшего единичного бита и внутренней шины UL номера разряда младшего единичного бита в М-разрядной группе.

Причем значение кода числа «М» подано на группу входов второго слагаемого первого 10 сумматора групп SMG, выход которого соединен с группой D-входов первого регистра 5 текущей разрядности числа, выходы которого являются соответствующими n разрядами внутренней шины текущей разрядности числа BD и соединены с группой входов первого слагаемого первого 10 сумматора групп SMG, с группой входов второго слагаемого второго 11 сумматора старших номеров SMM и с группой входов второго слагаемого третьего 12 сумматора младших номеров SML.

Кроме того выход элемента ИЛИ 4 является флагом единичных бит FU и соединен со вторыми входами первого 8 и второго 9 элементов И и соединен с входом S синхронной установки в единичное состояние второго триггера 7 единичных бит TU, инверсный выход которого соединен с первым входом второго элемента И 9, выход которого соединен с адресным А входом мультиплексора MX 15 и с входом разрешения работы СЕ четвертого выходного регистра 18.

Причем разряды внутренней шины UM номера разряда старшего единичного бита и внутренней шины UL номера разряда младшего единичного бита в М-разрядной группе соединены с соответствующими разрядами групп входов первых слагаемых соответственно второго 11 сумматора старших номеров SMM и третьего 12 сумматора младших номеров SML.

Кроме того выход второго 11 сумматора старших номеров SMM соединен с группой D-входов второго выходного регистра 16 и с первой группой информационных входов инкрементора 13 увеличения старшего номера INC, у которого на второй вход увеличения подано значение логической единицы «1». Выход инкрементора 13 увеличения старшего номера INC соединен с группой прямых входов первого слагаемого четвертого 14 сумматора разрядности диапазона SMD.

Причем выход третьего 12 сумматора младших номеров SML соединен с первой группой информационных входов мультиплексора MX 15 и с группой D-входов четвертого выходного регистра 18, выход которого соединен с нулевой группой информационных входов мультиплексора MX 15, выход которого соединен с группой инверсных входов второго слагаемого четвертого 14 сумматора разрядности диапазона SMD, у которого на вход переноса CI подано значение логической единицы «1». Выход четвертого 14 сумматора разрядности диапазона SMD соединен с группой D-входов третьего выходного регистра 17.

Причем разряды выходов второго выходного регистра 16 являются n разрядами выходной шины 23 номера старшего единичного разряда QM, разряды выходов третьего выходного регистра 17 являются n разрядами выходной шины 24 ширины диапазона QD, разряды выходов четвертого выходного регистра 18 являются n разрядами выходной шины 25 номера младшего единичного разряда QL.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ Принцип работы предлагаемого устройства состоит в следующем.

Предлагаемое устройство позволяет детектировать правый (младший) разряд и левый (старший) разряд входного N-разрядного двоичного числа, которые имеют единичное значение, и сформировать на выходах устройства номера младшего QL и старшего QM единичных разрядов и ширину диапазона единичных бит QD. При отсутствии единичных значений в разрядах входного N-разрядного двоичного числа на выходах номеров QL и QM границ диапазона и ширины диапазона QD устанавливаются нулевые значения.

Входное N разрядное двоичное число без знака разбивается на L=N/M групп по М разрядов в каждой группе. Группы входных данных последовательно поступают на входы устройства, при этом М двоичных разрядов каждой из L групп параллельно поступают на соответствующие входы D1, DM устройства.

Работа устройства начинается по единичному сигналу START=1 и завершается по единичному сигналу остановки STOP=1, который поступает одновременно с кодом последней L-ой группы.

При выявлении единичных значений в j-м (старшем) и i-м (младшем) разрядах в М-разрядной группе (где i≤j, 1≤i≤M, 1≤j≤M), в группе элементов ИЛИ 11, 12, …, 1(M-1) единичные значения последовательно передаются в сторону младших разрядов по цепочке элементов ИЛИ, начиная от левого (старшего) единичного j-го разряда до первого разряда, и соответствующие единичные значения устанавливаются на выходах элементов ИЛИ 11, …, 1j, которые далее поступают на внутреннюю шину SR сдвига вправо с первого разряда до j-го разряда.

Одновременно при выявлении единичного значения в правом (младшем) i-м разряде в группе элементов ИЛИ-НЕ 21, 22, …, 2(M-1) нулевые значения в разрядах меньше выявленного правого (младшего) единичного i-го разряда преобразуются в единичные значения на выходах элементов в группе элементов ИЛИ-НЕ, начиная с первого элемента до (i-1)-го элемента ИЛИ-НЕ 21, …, 2i-1. Нулевые значения устанавливаются на выходах элементов ИЛИ-НЕ 2i, …, 2(M-1), так как единичное значение i-го разряда на элементе ИЛИ-НЕ 2i преобразуется в нулевое значение, которое далее последовательно передается в сторону старших разрядов по цепочке элементов ИЛИ-НЕ, начиная от правого (младшего) единичного i-го разряда до последнего старшего (М-1) разряда. Далее значения с выходов группы элементов ИЛИ-НЕ 21, 22, …, 2(м-1) поступают на внутреннюю шину SL сдвига влево. Также на первый разряд шины SL сдвига влево поступает значение с выхода первого элемента ИЛИ 11, которое принимает единичное значение при наличии хотя бы одного единичного бита на входной шине D группы.

Таким образом, на шине SR сдвига вправо формируются единичные значения с первого разряда до j-го разряда, сумма которых равна j, что соответствует номеру левого (старшего) единичного бита в группе. Одновременно на шине SL сдвига влево также формируются единичные значения с первого разряда до i-го разряда, сумма которых равна i, что соответствует номеру правого (младшего) единичного бита во входных данных группы.

Далее значения с выходов внутренней шины SR сдвига вправо поступают на входы первого блока 31 счета младших упорядоченных единиц, а с выходов внутренней шины SL сдвига влево поступают на входы второго блока 32 счета младших упорядоченных единиц, на которых соответственно формируются номера j-го и i-го разрядов, которые далее передаются соответственно на внутренние m разрядные шины номера старшего единичного бита UM и номера младшего единичного бита UL в М-разрядной группе (где m=]log2(M+1)[(большее целое)).

При выявлении только одного единичного значения в i-м разряде (где 1≤i≤М, при этом j=i) входной шины D группы на выходах элементов ИЛИ, начиная с первого до i-го элементов, группы элементов ИЛИ 11, …, 1i устанавливаются единичные значения, которые поступают на внутреннюю шину SR сдвига вправо. Одновременно на выходах элементов ИЛИ-НЕ, начиная с первого до (i-1)-го элементов, группы элементов ИЛИ-НЕ 21, …, 2(i-1) также устанавливаются единичные значения, которые поступают на внутреннюю шину SL сдвига влево, на первый разряд которой передается единичное значение с первого элемента ИЛИ 11. Далее значения с выходов внутренней шины SR сдвига вправо и с выходов внутренней шины SL сдвига влево поступают соответственно на первый 31 и второй 32 блоки счета младших упорядоченных единиц.

Далее в первом 31 и втором 32 блоках счета младших упорядоченных единиц формируется номер i-го разряда (при этом j=i) и передается на выходные шины QL и QR.

При отсутствии единичных значений на входной шине D группы нулевые значения устанавливаются во всех разрядах шины SR сдвига вправо. При этом нулевое значение с первого элемента ИЛИ 11, передается на инверсные входы всех элементов ИЛИ-НЕ 21, 22, …, 2(M-1), на инверсных выходах которых также устанавливаются нулевые значения и далее нулевые значения устанавливаются во всех разрядах шины SL сдвига влево.

Одновременно на каждом такте на первом 10 сумматоре групп SMG и первом регистре текущей разрядности числа 5, которые образуют накаливающий сумматор, осуществляется подсчет по М разрядов групп.

Значения номера старшего единичного разряда с шины UM и номера младшего единичного бита UL в группе суммируются с кодом текущей разрядности числа на внутренней шине BD, с первого регистра 5 соответственно, на втором 11 сумматоре старших номеров SMM и третьем сумматоре младших номеров SML, на выходах которых формируются коды текущих номеров старшего и младшего единичных разрядов от 1-го разряда до текущей группы входного N-разрядного двоичного числа, которые по соответствующим единичным сигналам с выходов первого 8 и второго 9 элементов И записываются во второй 16 и четвертый 18 выходные регистры, выходы которых являются соответственно n разрядами выходной шины номера старшего единичного разряда QM и выходной шины номера младшего единичного разряда QL для N разрядного двоичного числа (где n=]log2(N+1)[(большее целое)).

Одновременно значение текущего номера старшего единичного разряда со второго 11 сумматора старших номеров SMM увеличивается на единицу в инкременторе INC 13 и передается на группу прямых входов первого слагаемого четвертого 14 сумматора разрядности диапазона SMD. Увеличение на единицу номера старшего единичного разряда осуществляется для учета в разности разрядов границ диапазона. При выявлении младшего единичного разряда значение его номера с третьего 12 сумматора младших номеров SML поступает на первую группу мультиплексора MX 15 и при единичном значении с выхода второго элемента И 9 передается на инверсную группу входов второго слагаемого четвертого 14 сумматора разрядности диапазона SMD, на выходах которого формируется значение кода ширины диапазона единичных бит, соответствующее разности между инкрементированным значением INC номера старшего единичного разряда и значением номера младшего единичного разряда. Значение кода ширины диапазона единичных бит с выхода четвертого 14 сумматора разрядности диапазона SMD, при единичном сигнале на выходе первого элемента И 8, записывается в третий выходной регистр ширины диапазона 17, разряды выхода которого являются соответственно n разрядами выходной шины ширины диапазона QD N разрядного двоичного числа.

Кроме того при выявлении единичного разряда в М-разрядной группе формируется единичное значение флага единичных бит FU=1, по которому на следующем такте второй триггер единичных бит TU устанавливается в единичное состояние TU=1. При этом на инверсном выходе второго триггера единичных бит TU устанавливается нулевое значение, по которому далее устанавливается нулевое значение на выходе второго элемента И 9. Поэтому далее на следующих тактах на выход мультиплексора MX 15 с нулевой группы входов передается значение номера младшего единичного разряда, зафиксированное на четвертом выходном регистре 18 при выявлении младшего единичного разряда в N разрядном двоичном числе.

Таким образом, в предлагаемом устройстве на выходных шинах в каждом такте устанавливаются текущие значения номера старшего единичного разряда QM, номера младшего единичного разряда QL и ширины диапазона QD. По единичному сигналу остановки STOP на выходных шинах QM, QL и QD будут зафиксированы итоговые значения для входного N разрядного двоичного числа.

Предлагаемое устройство работает следующим образом.

Перед началом работы подается сигнал на внешнем входе 22 асинхронной установки в нулевое состояние CLR, по которому в нулевые состояния устанавливаются первый триггер 6 пуска-останова TSS, второй триггер 7 единичных бит TU, первый регистр 5 текущей разрядности числа, выходные второй 16, третий 17 и четвертый 18 регистры.

Далее при единичном значении сигнала начала работы на внешнем 20 входе START=1 (такты 1 на фиг.2 при N=20, М=5, L=4) на такте 2 по фронту тактового сигнала С на внешнем входе 21 в единичное состояние устанавливается первый 6 триггер пуска-останова TSS=1.

Далее в каждом такте 2-5, начиная с такта 2, на внешние входы устройства D1, D5(DM) параллельно поступают по М=5 разрядов последовательных L=N/M=4 групп входного N=20 разрядного двоичного числа без знака. При этом младший разряд D1 является первым (правым) разрядом каждой входной группы (на фиг. 2 показан слева). Значения с входной шины D поступают на соответствующие входы группы элементов ИЛИ 11, 12, …, 1(M-1) и группы элементов ИЛИ-НЕ 21, 22, …, 2(м-1).

При выявлении единичных значений в правом (младшем) i-м разряде и в левом (старшем) j-м разряде входной группы (где i≤j, 1≤i≤M, 1≤j≤M)„ единичные значение последовательно по цепочке передаются на выходы элементов ИЛИ в сторону младших разрядов, начиная с j-го до первого элементов ИЛИ 1j, …, 11, а также последовательно по цепочке передаются на выходы элементов ИЛИ-НЕ, начиная с первого до (i-1)-го элементов ИЛИ 21, …, 2(i-1).

На фиг. 2 приведены два тестовых примера. На фиг. 2 в скобках указано представление значений в двоичном коде (2) или десятичном коде (10), а выходы триггеров TSS и TU, флага единичных бит FU и логических элементов 4, 8 и 9 приведены в виде временной диаграммы.

В тесте №1 в такте 2 на входы D1, D5 поступает первая группа 00110, для которой соответствующие единичные значения последовательно устанавливаются на выходах группы элементов ИЛИ 11, …, 14 и группы элементов ИЛИ-НЕ 21, …, 24, которые далее поступают на разряды шин соответственно сдвига вправо SR и сдвига влево SL. При этом в младших разрядах (на фиг. 2 слева - направо) будет установлено на шине сдвига вправо SR четыре единичных разряда SR=11110 и на шине сдвига влево SL три единичных разряда SL=11100. Подсчет единиц осуществляется соответственно в первом 31 и втором 32 блоках счета младших упорядоченных единиц, и формируются коды номеров границ единичных бит, которые передаются на соответствующие внутренние шины номеров разрядов - соответственно старший разряд UM=4 (j=4) и младший разряд UL=3 (i=3), которые поступают на входы первых слагаемых соответственно второго 11 сумматора старших номеров SMM и третьего 12 сумматора младших номеров SML. Так как на первом регистре текущей разрядности числа 5 установлено нулевое значение BD=0, то значения номеров с внутренних шин UM=4 и UL=3 передаются без изменений на выходы второго 11 сумматора старших номеров SMM=4 и третьего 12 сумматора младших номеров SML=3.

Далее код номера старшего разряда SMM=4 в инкременторе 13 увеличивается INC=5 и передается на группу прямых входов первого слагаемого четвертого 14 сумматора разрядности диапазона SMD. Кроме того единичное значение установлено на выходе элемента ИЛИ 4 (флаг FU=1) и далее на выходе первого элемента И 8, так как в единичное состояние также установлен первый триггер 6 пуска-останова TSS=1. На выходе второго элемента И 9 также установлено единичное значение, так как в нулевое состояние установлен второй триггер 7 единичных бит TU=0 и в единичное состояние его инверсный выход. Поэтому через первую группу входов мультиплексора MX 15 код номера младшего разряда с выхода третьего сумматора SML=3 передается на группу инверсных входов второго слагаемого четвертого 14 сумматора разрядности диапазона SMD, у которого код логической единицы «1» установлен на входе переноса CI=1. Поэтому на выходе четвертого 14 сумматора разрядности диапазона SMD формируется код разности SMD=2 соответствующий ширине единичного диапазона в первой группе.

В такте 3 по фронту синхросигнала С, при единичных значениях на выходах первого элемента И 8 и второго элемента И 9 установленных в такте 2, осуществляется запись соответствующих значений номеров старшего SMM=4 и младшего SML=3 единичных разрядов и ширины диапазона SMD=2 в выходные второй 16, четвертый 18 и третий 17 регистры соответственно, и передача этих значений на выходные шины: QM=4, QL=3, QD=2. Также в такте 3 по фронту синхросигнала в единичное состояние переключается второй триггер 7 единичных бит TU=1 и формируется нулевое значение на инверсном выходе. Кроме того осуществляется суммирование кода «М=5» на первом сумматоре 10 и запись суммарного кода «М=5» в первый регистр текущей разрядности числа 5. Поэтому на внутренней шине BD текущей разрядности числа формируется код BD=5.

Одновременно в такте 3 теста №1 на фиг. 2 на входы D1, D5 поступает код второй группы 01000, в которой содержится только одно единичное значение во втором разряде (D2=1). При этом детектируются младший i=2 и старший j=2 единичные разряды, для которых формируются соответствующие значения по единичных на шинах сдвига вправо SR=11000 и сдвига влево SL=11000, по которым соответственно в первом 31 и втором 32 блоках счета младших упорядоченных единиц формируются коды номеров границ единичных бит UM=2 (j=2) и младший разряд UL=2 (i=2), которые далее суммируются во втором 11 и третьем 12 сумматорах с кодом на внутренней шине BD=5 и формируются коды SMM=7 и SML=7. Но так как на выходе второго элемента И 9 установлено нулевое значение, то мультиплексор MX 15 передает на выход значение кода QL=3 младшего разряда с выхода четвертого выходного регистра, установленного при детектировании первой группы, который вычитается из инкрементированного номера старшего разряда INC=8. Поэтому на выходе четвертого 14 сумматора разрядности диапазона SMD формируется код SMD=5 - разность между старшим единичным разрядом во второй группе и младшим единичным разрядом в первой группе.

В такте 4 по фронту синхросигнала С, при единичном значении на выходе первого элемента И 8 установленного в такте 3, осуществляется запись соответствующих текущих значений номера старшего единичного разряда SMM=7 и ширины диапазона SMD=5 в выходные второй 16 и третий 17 регистры соответственно, и передача этих значений на выходные шины: QM=7, QD=5. Значение кода QL=3 номера младшего разряда в четвертом выходном регистре 18 сохраняется, так как нулевое значение установлено на входе разрешения работы СЕ с выхода второго элемента И 9. Кроме того осуществляется суммирование кода «М=5» на первом сумматоре 10 и запись суммарного кода «М=10» в первый регистр текущей разрядности числа 5. Поэтому на внутренней шине BD текущей разрядности числа формируется код BD=10.

Одновременно в такте 4 теста №1 на фиг. 2 на входы D1, D5 поступает код третьей группы 01100, в которой содержатся единичные значения во втором и третьем разрядах (D2=1, D3=1). Далее на шинах сдвига формируются коды сдвига вправо SR=111000 и сдвига влево SL=11000, для которых формируются коды границ единичных бит старшего UM=3 (j=3) и младшего UL=2 (i=2) разрядов, которые далее суммируются во втором 11 и третьем 12 сумматорах с кодом BD=10 и формируются коды SMM=13 и SML=12. Но так как на выходе второго элемента И 9 установлено нулевое значение, то мультиплексор MX 15 передает на выход значение кода QL=3 младшего разряда с выхода четвертого выходного регистра, который вычитается из инкрементированного номера старшего разряда INC=14. Поэтому на выходе четвертого 14 сумматора разрядности диапазона SMD формируется код SMD=11 - разность между старшим единичным разрядом в третьей группе и младшим единичным разрядом в первой группе.

В такте 5 по фронту синхросигнала С, при единичном значении на выходе первого элемента И 8 установленном в такте 4, осуществляется запись соответствующих значений номера старшего единичного разряда SMM=13 и ширины диапазона SMD=11 в выходные второй 16 и третий 17 регистры соответственно, и передача значений на выходные шины: QM=13, QD=11. Кроме того осуществляется суммирование кода «М=5» на первом сумматоре 10 и на внутренней шине BD текущей разрядности числа формируется код BD=15.

Одновременно в такте 5 теста №1 на фиг. 2 на входы D1, D5 поступает код четвертой группы 00010, в которой содержится только одно единичное значение в четвертом разряде (D4=1). Далее аналогично на шинах сдвига формируются коды сдвига вправо SR=11110 и сдвига влево SL=11110, для которых формируются коды границ единичных бит старшего UM=4 (j=4) и младшего UL=4 (i=4), разрядов, которые далее суммируются во втором 11 и третьем 12 сумматорах с кодом BD=15 и формируются коды SMM=19 и SML=19. Но значение кода SML=19 с выхода третьего сумматора младших номеров SML не передается через мультиплексор MX 15, так как на выходе второго элемента И 9 установлено нулевое значение, а передается код QL=3 с выхода четвертого выходного регистра 18. Поэтому на выходе четвертого 14 сумматора разрядности диапазона SMD формируется код SMD=17.

Кроме того в такте 5 также поступает единичное значение сигнала по внешнему 19 входу остановки STOP=1.

В такте 6 по фронту синхросигнала С, при единичном значении на выходе первого элемента И 8 установленному в такте 5, осуществляется запись соответствующих значений номера старшего единичного разряда SMM=19 и ширины диапазона SMD=17 в выходные второй 16 и третий 17 регистры соответственно, и передача значений на выходные шины: QM=19, QD=17. Кроме того осуществляется суммирование кода «М=5» на первом сумматоре 10 и на внутренней шине BD текущей разрядности числа формируется код BD=20. Одновременно по сигналу STOP=1 в нулевое состояние переключается первый 6 триггер пуска-останова TSS=0.

Таким образом, для теста №1 на выходных шинах устройства будут установлены коды границ единичных разрядов и ширины диапазона: QM=19, QD=17, QL=3.

Для теста №2, аналогично как в тесте №1, в такте 1 перед началом работы подают сигналы CLR и START=1.

В тесте №2 в такте 2 на входы D1, D5 поступает первая группа 00000, в которой отсутствуют единичные значения, при этом i=0 и j=0. Поэтому нулевые значения устанавливаются на выходах всех элементов ИЛИ 11, …, 14 и всех элементов ИЛИ-НЕ 21, …, 24. Далее нулевые значения устанавливаются во всех разрядах шины сдвига вправо SR=00000 и шины сдвига влево SL=00000, при этом на шине SL сдвига влево нулевой код устанавливается за счет двойной инверсии нулевого значения с выхода первого элемента ИЛИ 11. Поэтому в первом 31 и втором 32 блоках счета младших упорядоченных единиц формируются нулевые коды - соответственно UM=0 (j=0) и яд UL=0 (i=0). Далее нулевые коды формируются на выходах второго 11 сумматора SMM=0 и третьего 12 сумматора SML=0. На выходе инкрементора 13 формируется код INC=1 и на выходе четвертого 14 сумматора разрядности диапазона код SMD=1. Кроме того нулевое значение FU=0 установлено на выходе элемента ИЛИ 4, так как нет единичных бит во входной группе, и поэтому далее нулевые значения формируются на выходе первого элемента И 8 и на выходе второго элемента И 9. Поэтому в такте 3 по фронту синхросигнала С не выполняется запись в выходные второй 16, четвертый 18 и третий 17 регистры. Поэтому на выходных шинах сохраняются нулевые значения - QM=0, QL=0, QD=0.

В такте 3 теста №2 на фиг. 2 на входы D1, D5 поступает код второй группы 01101, в которой содержится три единичных бита (D2=1, D3=1, D5=1). При этом детектируются единичные разряды i=2 и j=5 для которых формируются соответствующие значения на шинах сдвига вправо SR=11111 и сдвига влево SL=11000, для которых соответственно в первом 31 и втором 32 блоках счета младших упорядоченных единиц и формируются коды номеров границ единичных бит - старшего UM=5 (j=5) и младшего UL=2 (i=2) разрядов, которые далее суммируются во втором 11 и третьем 12 сумматорах с кодом BD=5 и формируются коды SMM=10 и SML=7. Кроме того единичное значение FU=1 установлено на выходе элемента ИЛИ 4 и далее на выходе элемента И 8, поэтому через мультиплексор MX 15 код номера младшего разряда с выхода третьего сумматора SML=7 передается на группу инверсных входов второго слагаемого четвертого 14 сумматора разрядности диапазона SMD, а на группу прямых входов первого слагаемого код INC=11 и на выходе четвертого 14 сумматора формируется код SMD=4 соответствующий разности - ширине единичного диапазона во второй группе.

В такте 4 теста №2 по фронту синхросигнала С, при единичных значениях на выходах первого элемента И 8 и второго элемента И 9 установленных в такте 3, осуществляется запись соответствующих значений номеров старшего SMM=10 и младшего SML=7 единичных разрядов и ширины диапазона SMD=4 в выходные второй 16, четвертый 18 и третий 17 регистры соответственно, и передача значений на выходные шины: QM=10, QL=7, QD=4. Также по фронту синхросигнала при FU=1 в единичное состояние переключается второй триггер 7 единичных бит TU=1 и нулевое значение устанавливается на инверсном выходе. Кроме того осуществляется суммирование кода «М=5» на первом сумматоре 10 и запись суммарного кода «М=10» в первый регистр текущей разрядности числа 5. Поэтому на внутренней шине BD текущей разрядности числа формируется код BD=10.

Одновременно в такте 4 теста №2 на фиг. 2 на входы D1, D5 поступает код третьей группы 11010, в которой содержится три единичных бита (D1=1, D2=1, D4=1). При этом детектируются младший i=1 и старший j=4 единичные разряды, для которых формируются соответствующие значения на шинах сдвига вправо SR=11110 и сдвига влево SL=10000, для которых соответственно в первом 3i и втором Зг блоках счета младших упорядоченных единиц и формируются коды номеров границ единичных бит старшего UM=4 (j=4) и младшего UL=1 (i=1) разрядов, которые далее суммируются во втором 11 и третьем 12 сумматорах с кодом BD=10 и формируются коды SMM=14 и SML=11. Но так как на выходе второго элемента И 9 установлено нулевое значение, то мультиплексор MX 15 передает на выход значение кода QL=7 младшего единичного разряда с выхода четвертого 18 выходного регистра, установленного при детектировании второй группы, который вычитается из инкрементированного номера старшего разряда INC=15. Поэтому на выходе четвертого 14 сумматора разрядности диапазона SMD формируется код SMD=8 - разность между старшим единичным разрядом в третьей группе и младшим единичным разрядом во второй группе.

В такте 5 по фронту синхросигнала С, при единичном значении на выходе первого элемента И 8 установленному в такте 3, осуществляется запись соответствующих значений номера старшего единичного разряда SMM=14 и ширины диапазона SMD=8 во второй 16 и третий 17 выходные регистры соответственно, и передача значений на выходные шины: QM=14, QD=8. Значение кода QL=7 номера младшего разряда в четвертом выходном регистре 18 сохраняется, так как нулевое значение установлено на входе разрешения работы СЕ с выхода второго элемента И 9.

Одновременно в такте 5 теста №2 на фиг. 2 на входы D1, D5 поступает код четвертой группы 00000, в которой отсутствуют единичные значения, при этом i=0 и j=0. Поэтому формируются нулевые коды - соответственно UM=0 (j=0) и яд UL=0 (i=0). Далее так как на внутренней шине BD=10, то формируются соответствующие коды на выходах второго 11 сумматора SMM=15 и третьего 12 сумматора SML=15, а на выходе инкрементора 15 INC=16 и далее на выходе четвертого 14 сумматора разрядности диапазона SMD формируется код SMD=8. Кроме того нулевое значение флага FU=0 установлено на выходе элемента ИЛИ 4, так как нет единичных бит во входной группе, и далее нулевые значения формируются на выходе первого элемента И 8 и на выходе второго элемента И 9. Поэтому в такте 6 по фронту синхросигнала С не выполняется запись в выходные второй 16, четвертый 18 и третий 17 регистры. Поэтому на выходных шинах сохраняются предыдущие значения - QM=14, QL=7, QD=8.

Таким образом, для теста №2 на выходных шинах устройства будут установлены коды границ единичных разрядов и ширины диапазона: QM=14, QL=7, QD=8.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу выявления границ диапазона единичных бит и оценки ширины диапазона, а также фиксации номера левого (старшего) единичного бита и номера правого (младшего) единичного бита во входных данных и кода ширины диапазона.

Изобретение относится к области вычислительной техники. Технический результат заключается в расширении арсенала технических средств за счет того, что устройство позволяет детектировать правый (младший) разряд и левый (старший) разряд входного N-разрядного двоичного числа, которые имеют единичное значение, и сформировать на выходах устройства номера младшего QL и старшего QM единичных разрядов и ширину диапазона единичных бит QD, при отсутствии единичных значений в разрядах входного N-разрядного двоичного числа на выходах номеров QL и QM границ диапазона и ширины диапазона QD устанавливаются нулевые значения. 2 ил.

Устройство параллельно-последовательной структуры для детектирования границ диапазона единичных бит содержит М разрядов D1, …, DM группы входных данных из N-разрядного двоичного числа, состоящего из L наборов по М разрядов в группе, где N=L*M, n-разрядную выходную шину 23 номера старшего единичного разряда QM, где n=]log2(N+1)[(большее целое), n-разрядную выходную шину 24 ширины диапазона QD, n-разрядную выходную шину 25 номера младшего единичного разряда QL, группу из (М-1) элементов ИЛИ 11, 12, …., 1(M-1), группу из (М-1) элементов ИЛИ-НЕ 21 22, …, 2(M-1), первый 31 и второй 32 блоки счета младших упорядоченных единиц, а также внутреннюю шину SR сдвига вправо и внутреннюю шину SL сдвига влево, которые содержат по М разрядов, внутреннюю m-разрядную шину номера младшего единичного бита UL в М-разрядной группе, где m=]log2(M+1)[(большее целое), внутреннюю m-разрядную шину номера старшего единичного бита UM в М-разрядной группе, внутреннюю n-разрядную шину текущей разрядности числа BD,

элемент ИЛИ 4, первый регистр 5 текущей разрядности числа, первый триггер 6 пуска-останова TSS, второй триггер 7 единичных бит TU, первый 8 и второй 9 элементы И, первый 10 сумматор групп SMG, второй 11 сумматор старших номеров SMM, третий 12 сумматор младших номеров SML, инкрементор 13 увеличения старшего номера INC, четвертый 14 сумматор разрядности диапазона SMD, мультиплексор MX 15, выходные второй 16, третий 17 и четвертый 18 регистры, а также внешний вход 19 остановки STOP, внешний вход 20 начала работы START, внешний вход 21 тактовых сигналов С, внешний вход 22 асинхронной установки в нулевое состояние CLR,

причем внешний вход С тактовых сигналов 21 и внешний вход CLR асинхронной установки в нулевое состояние 22 соединены с соответствующими входами С тактовых сигналов и входами CLR асинхронной установки в нулевое состояние первого триггера 6 пуска-останова TSS, второго триггера 7 единичных бит TU, первого регистра 5 текущей разрядности числа, выходных второго 16, третьего 17 и четвертого 18 регистров,

внешний вход 20 начала работы START соединен с входом S синхронной установки в единичное состояние первого триггера TSS пуска-останова 6,

внешний вход 19 остановки STOP соединен с входом R синхронной установки в нулевое состояние триггера TSS пуска-останова 6, выход которого соединен с входом разрешения работы СЕ первого регистра 5 текущей разрядности числа и с первым входом первого элемента И 8, выход которого соединен с входами разрешения работы СЕ выходных второго 16 и третьего 17 регистров,

причем первые (М-1) разрядов D1, D2, D(M-1) входной шины D, начиная с первого до (M-1)-го разрядов, соединены со вторыми входами соответствующих (М-1) элементов ИЛИ, начиная с первого до (M-1)-го элементов 11, 12, …, 1(M-1), а также соединены с первыми прямыми входами соответствующих (М-1) элементов ИЛИ-НЕ, начиная с первого до (M-1)-го элементов 21, 22, …, 2(M-1), а также все М разрядов D1, D2, …, DM входной шины D соединены с одноименными входами элемента ИЛИ 4,

при этом первые входы первых (М-2) элементов ИЛИ, начиная с первого до (М-2)-го элементов 11, 12, …, 1(M-2), соединены с выходами соответствующих последующих (М-2) элементов ИЛИ, начиная со второго до (M-1)-го элементов 12, 13 …., 1(M-1), а первый вход (M-1)-го элемента ИЛИ 1(M-1) соединен с М-м разрядом DM входной шины D,

кроме того, выходы всех (М-1) элементов ИЛИ 11, 12, …, 1(M-1) являются соответствующими одноименными (М-1) разрядами внутренней шины SR сдвига вправо, у которой старший М-й разряд соединен с М-м разрядом DM входной шины D, а все М разрядов шины SR сдвига вправо подключены к входам первого 31 блока счета младших упорядоченных единиц,

причем третьи инверсные входы (М-2) элементов ИЛИ-НЕ, начиная со второго до (M-1)-го элементов 22, 23, …, 2(M-1), соединены с инверсными выходами соответствующих предыдущих (М-2) элементов ИЛИ-НЕ, начиная с первого до (М-2)-го элементов 21, 22, …, 2(M-2), кроме того, вторые инверсные входы всех (M-1)-го элементов ИЛИ-НЕ 21, 22, …, 2(M-1) соединены между собой, а также подключены к выходу первого элемента ИЛИ 11 из группы элементов ИЛИ 11, 12, …, 1(M-1),

кроме того, инверсные выходы всех (М-1) элементов ИЛИ-НЕ 21, 22, …, 2(M-1) являются соответствующими (М-1) разрядами внутренней шины SL сдвига влево, начиная со второго до М-го разряда, а младший первый разряд шины SL сдвига влево соединен с выходом первого элемента ИЛИ 11 из группы элементов ИЛИ 11, 12, …, 1(M-1), а все М разрядов шины SL сдвига влево подключены к входам второго 32 блока счета младших упорядоченных единиц,

причем выходы первого 31 и второго 32 блоков счета младших упорядоченных единиц являются соответствующими m разрядами соответственно внутренней шины UM номера разряда старшего единичного бита и внутренней шины UL номера разряда младшего единичного бита в М-разрядной группе,

причем значение кода числа «М» подано на группу входов второго слагаемого первого 10 сумматора групп SMG, выход которого соединен с группой D-входов первого регистра 5 текущей разрядности числа, выходы которого являются соответствующими n разрядами внутренней шины текущей разрядности числа BD и соединены с группой входов первого слагаемого первого 10 сумматора групп SMG, с группой входов второго слагаемого второго 11 сумматора старших номеров SMM и с группой входов второго слагаемого третьего 12 сумматора младших номеров SML,

кроме того, выход элемента ИЛИ 4 является флагом единичных бит FU и соединен со вторыми входами первого 8 и второго 9 элементов И и соединен с входом S синхронной установки в единичное состояние второго триггера 7 единичных бит TU, инверсный выход которого соединен с первым входом второго элемента И 9, выход которого соединен с адресным А входом мультиплексора MX 15 и с входом разрешения работы СЕ четвертого выходного регистра 18,

причем разряды внутренней шины UM номера разряда старшего единичного бита и внутренней шины UL номера разряда младшего единичного бита в М-разрядной группе соединены с соответствующими разрядами групп входов первых слагаемых соответственно второго 11 сумматора старших номеров SMM и третьего 12 сумматора младших номеров SML,

кроме того, выход второго 11 сумматора старших номеров SMM соединен с группой D-входов второго выходного регистра 16 и с первой группой информационных входов инкрементора 13 увеличения старшего номера INC, у которого на второй вход увеличения подано значение логической единицы «1», а выход инкрементора 13 увеличения старшего номера INC соединен с группой прямых входов первого слагаемого четвертого 14 сумматора разрядности диапазона SMD,

причем выход третьего 12 сумматора младших номеров SML соединен с первой группой информационных входов мультиплексора MX 15 и с группой D-входов четвертого выходного регистра 18, выход которого соединен с нулевой группой информационных входов мультиплексора MX 15, выход которого соединен с группой инверсных входов второго слагаемого четвертого 14 сумматора разрядности диапазона SMD, у которого на вход переноса CI подано значение логической единицы «1», а выход четвертого 14 сумматора разрядности диапазона SMD соединен с группой D-входов третьего выходного регистра 17,

причем разряды выходов второго выходного регистра 16 являются n разрядами выходной шины 23 номера старшего единичного разряда QM, разряды выходов третьего выходного регистра 17 являются n разрядами выходной шины 24 ширины диапазона QD, разряды выходов четвертого выходного регистра 18 являются n разрядами выходной шины 25 номера младшего единичного разряда QL.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ В УПОРЯДОЧЕННОМ ДВОИЧНОМ ЧИСЛЕ | 2012 |

|

RU2522875C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ (НУЛЕЙ) В ДВОИЧНОМ ЧИСЛЕ | 2011 |

|

RU2446442C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ДИАПАЗОНА ЕДИНИЧНЫХ БИТ | 2019 |

|

RU2717631C1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2019 |

|

RU2711054C1 |

Авторы

Даты

2021-11-08—Публикация

2021-03-11—Подача