Данная заявка притязает на приоритет Предварительной заявки (США) серийный номер 60/756100, озаглавленной "METHOD AND APPARATUS FOR LOW POWER DESIGN UTILIZING POWER GATING'", поданной 4 января 2006 года, и Предварительной заявки (США) серийный номер 60/756856, озаглавленной "LOW-POWER WORD-LINE LOGIC", поданной 6 января 2006 года, каждая из которых передана правопреемнику настоящей заявки и полностью содержится в данном документе в качестве ссылки.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение, в общем, относится к системам и способам снижения энергопотребления в памяти, а более конкретно, к системам и способам ограничения энергопотребления числовых шин в банке памяти.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Технологические усовершенствования привели к более компактным и обладающим большей вычислительной мощностью персональным вычислительным устройствам. Например, множество портативных персональных вычислительных устройств, в том числе беспроводные вычислительные устройства, такие как портативные беспроводные телефоны, «карманные» компьютеры (PDA) и пейджинговые устройства, являются небольшими, легкими и удобно носятся пользователями. Более конкретно, портативные беспроводные телефоны, такие как сотовые (аналоговые и цифровые) телефоны и телефоны, работающие по Интернет-протоколу (IP), могут передавать речевые пакеты и пакеты данных по беспроводным сетям. Дополнительно, многие такие беспроводные телефоны включают в себя другие типы устройств, которые содержатся в них. Например, беспроводной телефон также может включать в себя цифровой фотоаппарат, цифровую видеокамеру, цифровое записывающее устройство и проигрыватель аудиофайлов. Кроме того, такие беспроводные телефоны могут включать в себя веб-интерфейс, который может быть использован для того, чтобы осуществлять доступ в Интернет. По сути, эти беспроводные телефоны включают в себя значительные вычислительные возможности.

В типичном варианте, портативные вычислительные устройства питаются от аккумуляторов. Как следствие, для портативных устройств зачастую требуются электронные схемы для того, чтобы удовлетворять строгим требованиям по электроэнергии. Поскольку число транзисторов на микросхеме продолжает возрастать, тогда как пороговые напряжения этих транзисторов продолжают снижаться, энергия утечки через транзисторы становится все более важной.

Современные микропроцессоры, в общем, включают в себя плотную кэш-память, которая включает в себя множество транзисторов. Выяснено, что на долю энергии утечки приходится 30 процентов энергии кэша уровня 1 (L1), потребляемой 65 нм-частью в активном режиме работы, и 80 процентов энергии кэша уровня 2 (L2) для полупроводникового устройства, изготовленного по технологическому процессу 0,13 микрон.

По мере того как разрыв между частотами обработки и временем обращения к динамическому оперативному запоминающему устройству (DRAM) продолжает увеличиваться, производители полупроводниковых устройств все в большей степени применяют внутрипроцессорное статическое оперативное запоминающее устройство (SRAM), чтобы удовлетворять требованиям по производительности. Как результат, во многих микросхемах матрицы SRAM могут занимать практически 60 процентов площади кристалла. Поскольку большая часть элементов SRAM-схем бездействует в любой данный момент времени, SRAM-матрицы являются существенными источниками утечки тока.

Предложено стробировать источник питания на логику числовой шины по адресному модулю памяти, когда процессор находится в специальном режиме энергосбережения, таком как режим ожидания (когда состояние SRAM восстанавливается при пробуждении) или режим остановки (когда содержимое SRAM становится недостоверным). Эти режимы в типичном варианте управляются посредством программного обеспечения и добавляют в устройство сложность и непроизводительные издержки.

Следовательно, будет полезным предоставить усовершенствованный механизм управления мощностью для снижения утечки тока в запоминающих устройствах.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В конкретном варианте осуществления способ уменьшения энергопотребления памяти включает в себя прием запроса на то, чтобы выполнить обращение к запоминающему устройству. Запоминающее устройство включает в себя декодер, множество формирователей числовых шин и множество числовых шин, при этом каждая числовая шина ассоциативно связана с формирователем числовой шины из множества формирователей числовой шины. Запрос декодируется в декодере так, чтобы определить адрес, ассоциативно связанный с запросом. Формирователь числовой шины из множества формирователей числовых шин выборочно запитываются, чтобы выполнить обращение к адресу запоминающего устройства, но без запитывания других числовых шин из множества числовых шин. Формирователь числовой шины ассоциативно связан с конкретной числовой шиной, которая связана с адресом, ассоциативно связанным с запросом.

В конкретном варианте осуществления выборочное запитывание формирователя числовой шины включает в себя выборочную активацию, по меньшей мере, одного из верхнего ключа и нижнего ключа конкретной числовой шины, чтобы подключить формирователь числовой шины к источнику питания. Верхний ключ может включать в себя p-канальный транзистор, а нижний ключ может включать в себя n-канальный транзистор. В еще одном другом конкретном варианте осуществления способ включает в себя отключение питания каждого из множества формирователей числовых шин запоминающего устройства. В другом варианте осуществления формирователь числовой шины выборочно снабжается электроэнергией посредством выборочной активации p-канального транзистора инвертора формирователя числовой шины, чтобы зарядить локальную емкость с помощью диффузионной емкости, ассоциативно связанной с множеством формирователей числовых шин. В другом варианте осуществления формирователь числовой шины выборочно запитываются посредством заряда верхнего ключа и нижнего ключа от питающей емкости и локальной виртуальной земли, соответственно. В одном конкретном иллюстративном варианте осуществления запоминающее устройство - это статическое оперативное запоминающее устройство (SRAM). В другом варианте осуществления запоминающее устройство - это кэш-память, например, кэш-память первого уровня или второго уровня.

В еще одном другом конкретном варианте осуществления раскрыто электронное устройство, которое включает в себя память, множество формирователей числовых шин и декодер. Память включает в себя множество числовых шин. Множество формирователей числовых шин подключено к памяти, при этом каждый формирователь числовой шины ассоциативно связан с числовой шиной из множества числовых шин памяти. Питание каждого из множества формирователей числовых шин отключено в течение состояния по умолчанию и выборочно подается в течение периода обращения к числовой шине. Декодер подключен к множеству формирователей числовых шин, чтобы принимать запрос на обращение к памяти и декодировать запрос на обращение к памяти, чтобы определять адрес, ассоциативно связанный с запросом на обращение к памяти. Декодер выполнен с возможностью запитывать выбранный формирователь числовой шины, но не другие формирователи числовой шины из множества формирователей числовых шин, в ответ на запрос.

В конкретном варианте осуществления электронное устройство включает в себя менеджер питания, чтобы выборочно активировать выбранный формирователь числовой шины в ответ на определение адреса, ассоциативно связанного с запросом на обращение к памяти. В другом варианте осуществления память включает в себя множество банков памяти, при этом каждый из множества банков памяти включает в себя пару под-банков, причем пара под-банков совместно использует предварительно декодированные данные. В еще одном другом варианте осуществления каждый формирователь числовой шины включает в себя транзистор с высоким порогом напряжения (VT).

В еще одном другом конкретном варианте осуществления предусмотрен процессорночитаемый носитель, заключающий в себе процессорночитаемые команды, чтобы уменьшать энергопотребление процессора. Процессорночитаемые команды включают в себя команды, чтобы декодировать запрос на обращение к памяти, чтобы определять адрес памяти, соответствующий выбранной числовой шине памяти, и команды, чтобы выборочно запитать формирователь числовой шины, ассоциативно связанный с выбранной числовой шиной, без приложения питания к другим числовым шинам, в ответ на определение адреса памяти.

В еще одном другом конкретном варианте осуществления запоминающее устройство включает в себя средство хранения, включающее в себя множество числовых шин, средство декодирования ввода адреса, чтобы определять адрес памяти, соответствующий выбранной одной из множества числовых шин, и средство запитывания выбранной одной из множества числовых шин, но не других числовых шин из множества числовых шин, в ответ на определение адреса памяти. В еще одном другом конкретном варианте осуществления запоминающее устройство включает в себя средство переключения, чтобы выборочно подключать средство декодирования к выводу источника питания.

В одном конкретном варианте осуществления портативное устройство включает в себя контроллер дисплея, интерфейс ввода, чтобы принимать пользовательский ввод, приемопередатчик, чтобы принимать цифровые сигналы, и процессор цифровых сигналов. Процессор цифровых сигналов подключен к приемопередатчику, интерфейсу ввода и контроллеру дисплея. Процессор цифровых сигналов включает в себя оперативное запоминающее устройство, включающее в себя множество числовых шин, и декодер, чтобы декодировать запрос на обращение к памяти, чтобы определять числовую шину, ассоциативно связанную с запросом на обращение к памяти. Процессор цифровых сигналов включает в себя менеджер питания, чтобы выборочно питать числовую шину, без приложения питания к другим числовым шинам из множества числовых шин.

Одно конкретное преимущество конкретного иллюстративного варианта осуществления заключается в том, что введение верхнего ключа и нижнего ключа позволяет уменьшить ток утечки через формирователь шины примерно в 20 раз в сравнении с традиционным формирователем числовой шины в ходе активного и неактивного режимов работы.

Другое конкретное преимущество заключается в том, что общее энергопотребление памятью снижается без увеличения непроизводительных издержек. Данное снижение энергопотребления предоставляет дополнительное преимущество в том, что энергия экономится для использования в других процессах и/или продлевается срок службы источника питания, такого как аккумулятор.

В еще одном другом аспекте, конкретное преимущество иллюстративного варианта осуществления заключается в том, что диффузионная емкость p-канальных транзисторов формирователя числовой шины больше емкости числовой шины, позволяющая распределять локальную емкость в транзисторе за счет совместного использования заряда. Это снижает влияние верхнего ключа на задержку в числовой шине, давая возможность использовать небольшие верхние/нижние ключи.

Другие аспекты, преимущества и признаки настоящего изобретения должны стать очевидными из прочтения всей заявки, включающей в себя следующие разделы: "Краткое описание чертежей", "Подробное описание изобретения" и "Формула изобретения".

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Аспекты и сопутствующие преимущества описанных в данном документе вариантов осуществления должны стать более понятными посредством ссылки на последующее подробное описание, рассматриваемое вместе с прилагаемыми чертежами, на которых:

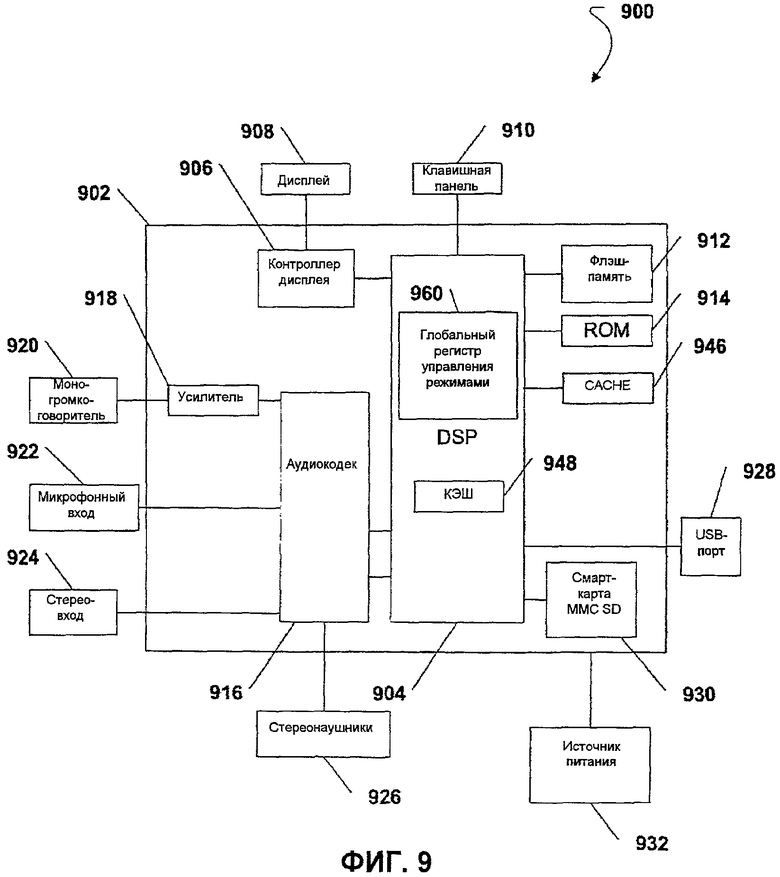

Фиг.1 - это блок-схема, иллюстрирующая конкретный вариант осуществления структуры с менеджером питания, чтобы выборочно снабжать электроэнергией одну числовую шину, но не другие числовые шины памяти;

Фиг.2 - это логическая схема, иллюстрирующая конкретный вариант осуществления логики числовой шины на уровне логических элементов, включающей в себя верхний ключ и нижний ключ, реагирующие на менеджер питания, такой как менеджер питания на фиг.1;

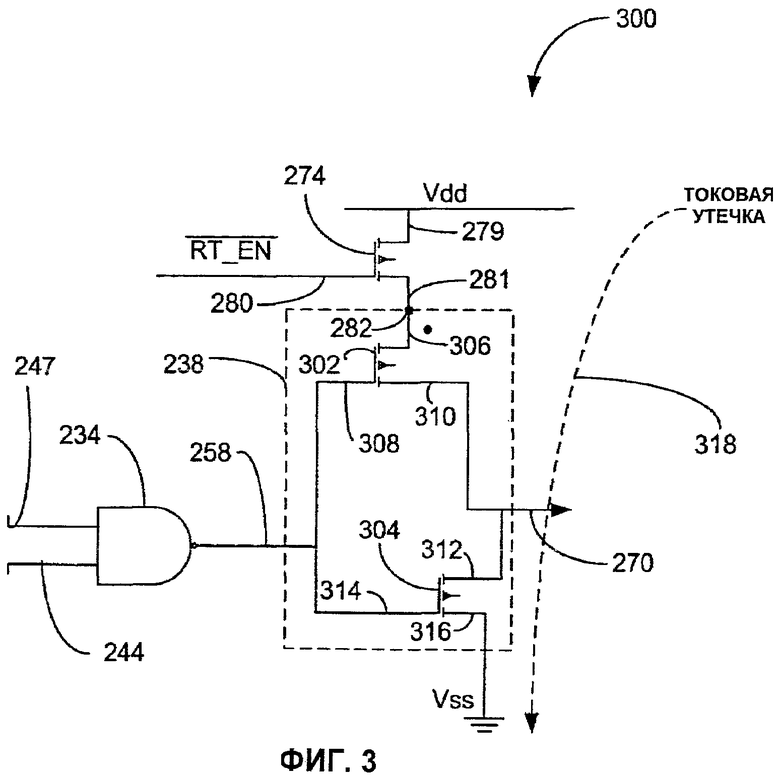

Фиг.3 - это расширенное представление части логической схемы по фиг.2;

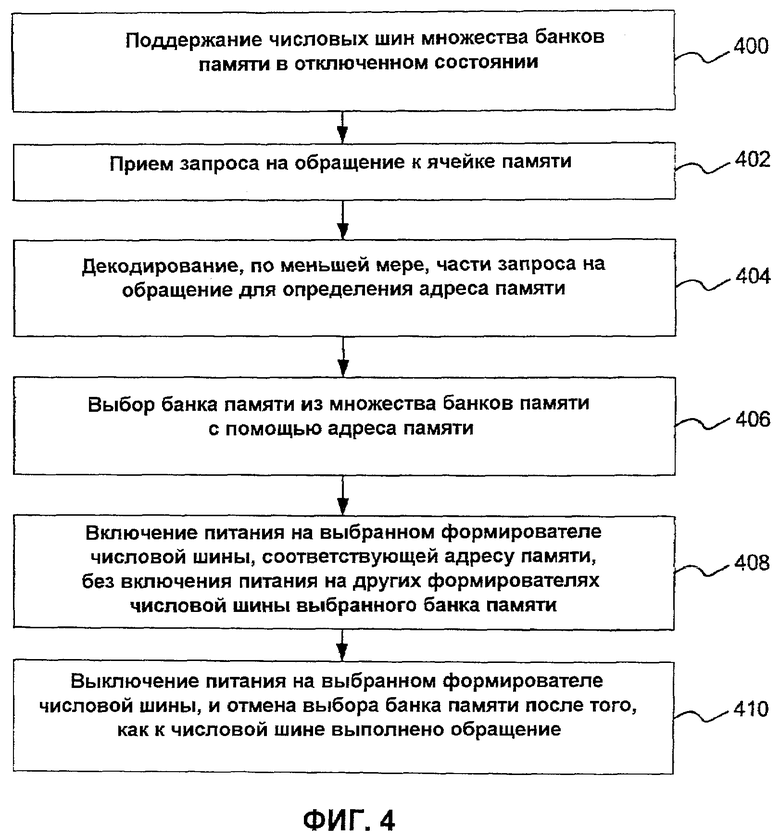

Фиг.4 - это блок-схема последовательности операций, иллюстрирующая конкретный вариант осуществления способа снижения потребления тока утечки посредством выборочного запитывания отдельных числовых шин;

Фиг.5 - это общая схема портативного устройства связи, содержащего память, в которой могут быть использованы система и способ пониженного энергопотребления, согласно фиг.1-4;

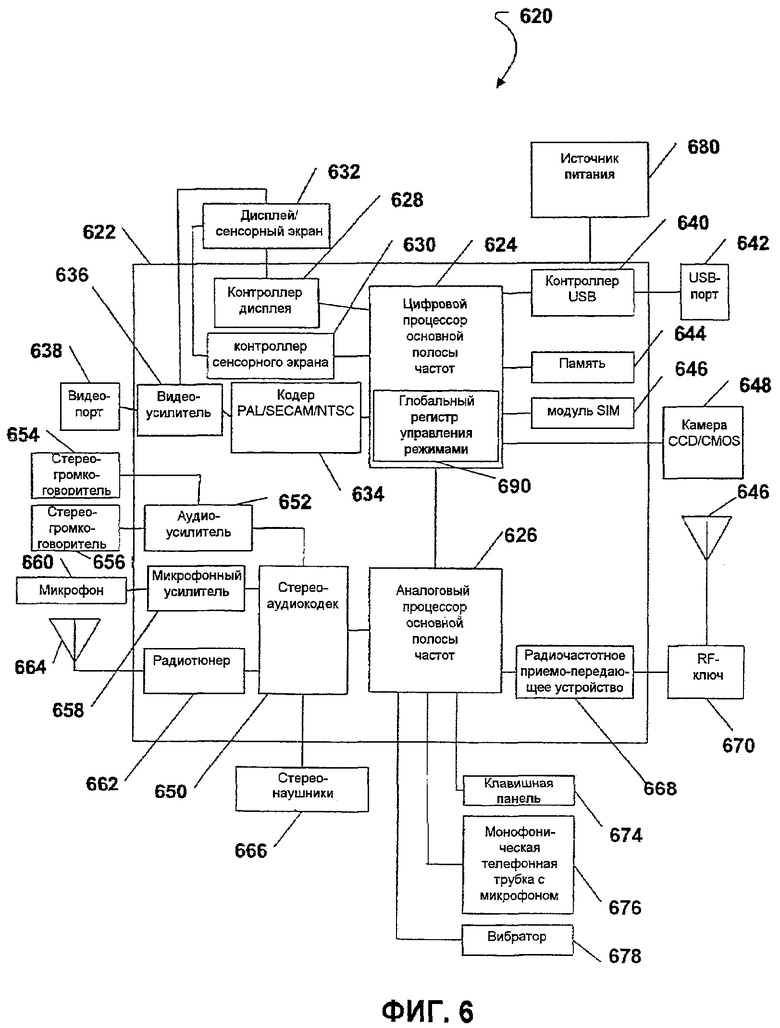

Фиг.6 - это общая схема примерного сотового телефона, содержащего процессор и память, в которых могут быть использованы система и способ пониженного энергопотребления, согласно фиг.1-4;

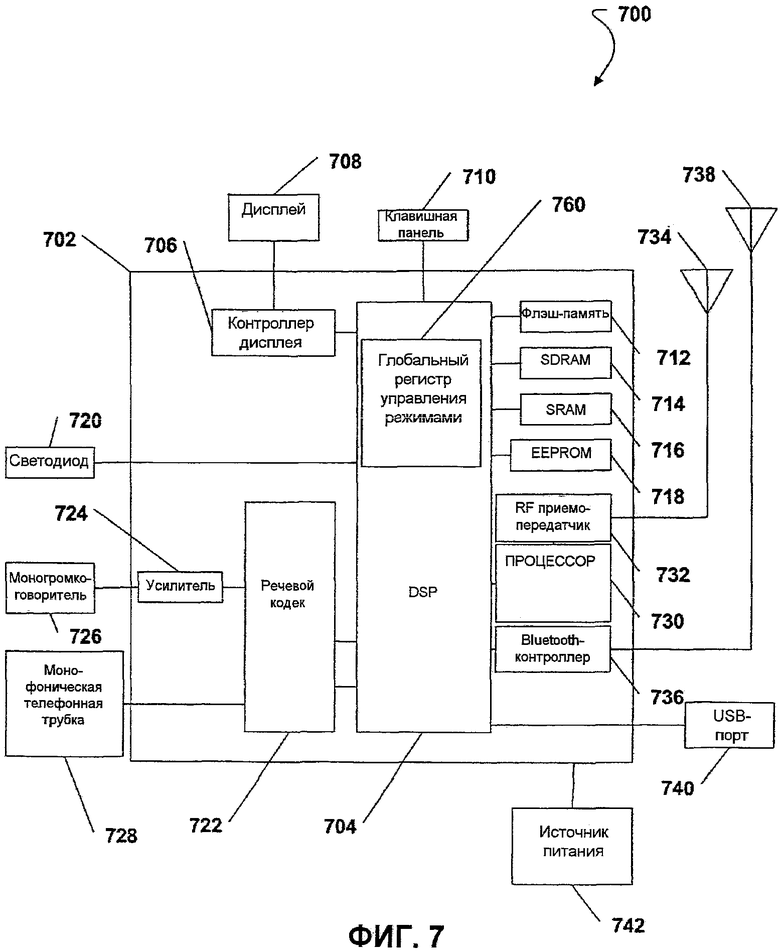

Фиг.7 - это общая схема примерного беспроводного телефона, работающего по Интернет-протоколу, содержащего процессор и память, в которых могут быть использованы система и способ пониженного энергопотребления, согласно фиг.1-4;

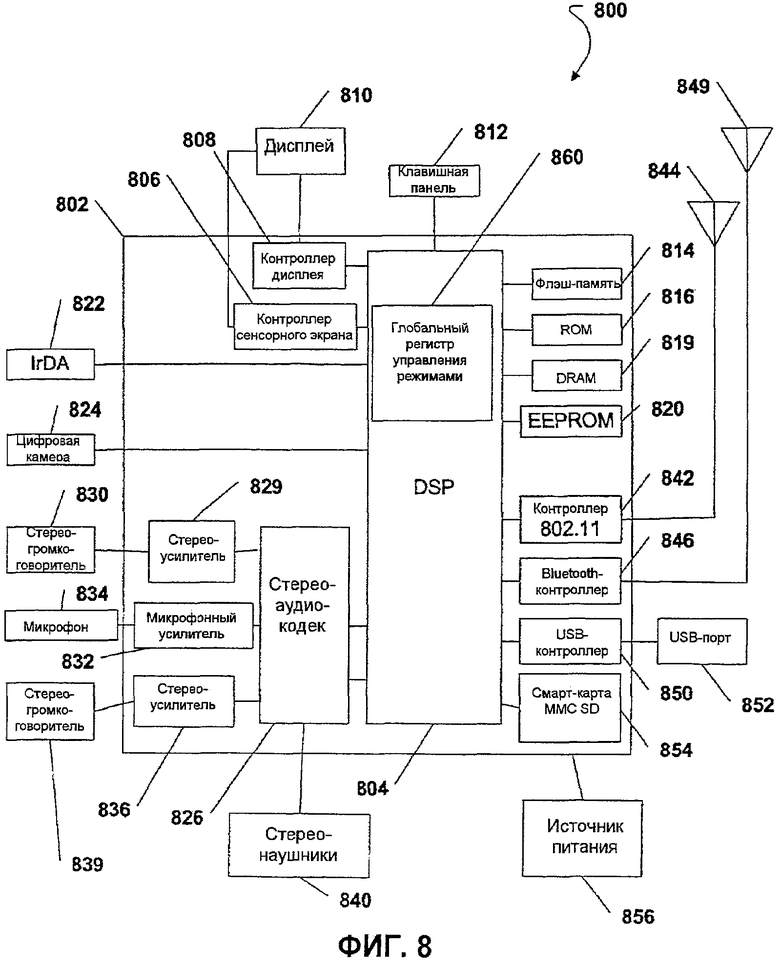

Фиг.8 - это общая схема примерного портативного цифрового устройства, содержащего процессор и память, в которых могут быть использованы система и способ пониженного энергопотребления, согласно фиг.1-4; и

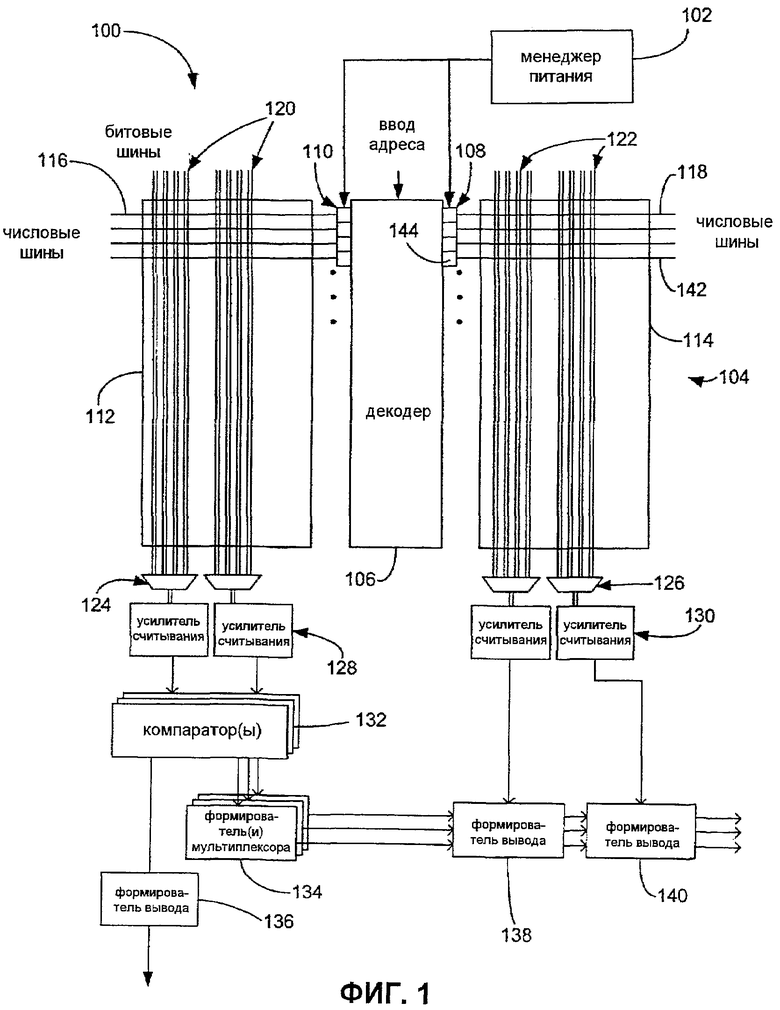

Фиг.9 - это общая схема примерного проигрывателя аудиофайлов, содержащего процессор и память, в которых могут быть использованы система и способ пониженного энергопотребления, согласно фиг.1-4.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Фиг.1 - это блок-схема, иллюстрирующая конкретный вариант осуществления структуры 100 с менеджером питания, чтобы выборочно запитывать одну числовую шину, но не другие числовые шины памяти, такой как кэш-память. Структура 100 включает в себя менеджер 102 питания, матрицу 104 кэш-памяти, декодер 106 и формирователи 108 и 110 числовой шины. Матрица 104 кэш-памяти подразделяется на два репрезентативных банка 112 и 114 памяти. Каждый банк 112 и 114 включает в себя множество числовых шин 116 и 118, соответственно. Каждый банк 112 и 114 также включает в себя множество разрядных шин 120 и 122, соответственно. Структура 100 также включает в себя мультиплексоры 124 и 126, усилители 128 и 130 считывания, компараторы 132, формирователи 134 мультиплексора (MUX), формирователь 136 вывода и формирователи 138 и 140 вывода.

Менеджер 102 питания включает в себя логику, чтобы выборочно активировать и деактивировать стробирование питания на формирователи 108 и 110 числовых шин. Декодер 106 включает в себя ввод и множество выводов числовых шин. Каждый формирователь 108 и 110 числовой шины включает в себя вход, подключенный к менеджеру 102 питания, вход, подключенный к одному из множества выходов числовых шин декодера 106, и выход, подключенный к числовой шине одного из банков 112 или 114. Каждый формирователь 108 и 110 числовой шины также включает в себя синхровход (показан на фиг.2), чтобы принимать синхронизирующий сигнал. Следует понимать, что формирователи 108 и 110 числовых шин также могут быть включены в декодер 106.

Мультиплексоры 124 и 126 включают в себя входы, подключенные к разрядным шинам 120 и 122, соответственно. Мультиплексоры 124 и 126 также включают в себя выходы. Усилители 128 и 130 считывания подключены к выходам мультиплексоров 124 и 126. Схема 132 компаратора включает в себя вход, подключенный к выходу усилителя 128 считывания, и включает в себя множество выходов. Схема 132 компаратора может включать в себя множество компараторов. Формирователь 134 мультиплексора (MUX) включает в себя входы, подключенные, по меньшей мере, к одному из множества выходов схемы 132 компаратора, и включает в себя множество выходов. Формирователь 136 вывода включает в себя вход, подключенный, по меньшей мере, к одному из множества выходов схемы 132 компаратора, и включает в себя выход. Формирователь 138 вывода включает в себя множество входов, подключенных к множеству выходов MUX-формирователя 134, вход, подключенный к выходу одного из усилителей 130 считывания, и множество выходов. Формирователь 140 вывода включает в себя множество входов, подключенных к множеству выходов формирователя 138 вывода, вход, подключенный к выходу одного из усилителей 130 считывания, и множество выходов.

При работе декодер 106 принимает запрос на обращение к памяти, такой как ввод адреса памяти для считывания из памяти или записи в память. Декодер 106 декодирует запрос на обращение к памяти, чтобы определить адрес памяти 104, соответствующий вводу адреса памяти. Когда совпадающий адрес найден, декодер 106 подтверждает числовую шину 108 или 110, соответствующую адресу памяти. Менеджер 102 питания, в ответ на вывод декодера, выборочно активирует запитывание выбранной числовой шины на основе адреса памяти.

Например, если числовая шина 142 банка 114 памяти подтверждается, менеджер 102 питания выборочно активирует запитывание конкретного формирователя 144 числовой шины, ассоциативно связанного с числовой шиной 142. Биты данных числовой шины 142 принимаются посредством мультиплексоров 126. Мультиплексоры 126 формируют выводы, которые принимаются посредством усилителей 130 считывания. Выводы усилителей считывания предоставляются в ассоциативно связанные формирователи 138 и 140 вывода, чтобы сформировать выходной сигнал, связанный с данными, предоставляемыми посредством числовой шины 142.

Поскольку только одна числовая шина из набора числовых шин 116 и 118 является активной в любом данном такте, запитывание формирователей 108 и 110 числовой шины отключается, за исключением запитывания конкретного формирователя 144 числовой шины, который ассоциативно связан с числовой шиной 142, к которой требуется выполнить обращение. Эта функция управления питанием может быть выполнена при обычном режиме работы на аппаратном уровне, без перехода в специальные режимы энергосбережения процессора.

Следует понимать, что фиг.1 предоставляется только в иллюстративных целях и не предназначена для того, чтобы быть ограничивающей. Более того, хотя структура памяти указана как архитектура кэша, варианты осуществления настоящего изобретения применимы к другим структурам памяти, в том числе статическому оперативному запоминающему устройству (SRAM), динамическому RAM и т.п. Дополнительно, хотя набор формирователей 108 и 110 числовых шин показан как отдельные блоки, подключенные к одному банку памяти, каждый формирователь числовой шины из формирователей 108 и 110 числовой шины может быть подключен к паре банков памяти, и менеджер 102 питания может быть выполнен с возможностью выборочной активации выбранного отдельного формирователя числовой шины, чтобы запитывать электроэнергией одну числовую шину одного из банков памяти в любое данное время.

Фиг.2 - это логическая схема, иллюстрирующая конкретный вариант осуществления логики 200 числовой шины на уровне логических элементов, включающей в себя верхний ключ 202 и нижний ключ 204, реагирующие на менеджер питания, такой как менеджер питания 102 на фиг.1. Дополнительно, логика 200 числовой шины включает в себя блок 144 формирователей числовых шин, логические элементы 206 и 208 И и конденсаторы 210 и 212. Логический элемент 206 И включает в себя синхронизирующий вход 214, вход 216 активации левой линии и выход 218. Логический элемент 208 И включает в себя синхронизирующий вход 214, вход 220 активации правой линии и выход 222. Блок 144 формирователей числовых шин включает в себя вход 246 левой числовой шины, подключенный к выходу 218 логического элемента 206 И, вход 249 правой числовой шины, подключенный к выходу 222 логического элемента 208 И, и пару входов 228, подключенных к детектору так, чтобы принимать предварительно декодированные данные.

Блок 144 формирователей числовых шин включает в себя логический элемент 230 И, логические элементы 232 и 234 И-НЕ и инверторы 236 и 238. Логический элемент 230 И включает в себя пару входов 240, подключенные к паре входов 228, и выход 242. Логический элемент 232 И-НЕ включает в себя вход 244, подключенный к выходу 218 логического элемента 206 И через узел 246, вход 247, подключенный к выходу 242 логического элемента 230 И, силовой вход 248 и выход 250. Логический элемент 234 И-НЕ включает в себя вход 252, подключенный к выходу 242 логического элемента 230 И, вход 254, подключенный к выходу 222 логического элемента 208 И через узел 249, силовой вход 250 и выход. 258. Инвертор 236 включает в себя вход 260, подключенный к выходу 250 логического элемента 232 И-НЕ, силовой вход 262 и выход 264, подключенный к числовой шине левого банка памяти. Инвертор 238 включает в себя вход 266, подключенный к выходу 258 логического элемента 234 И-НЕ, силовой вход 268 и выход 270, подключенный к числовой шине правого банка памяти. Следует понимать, что термины "левый" и "правый" используются только в пояснительных целях, и блок формирователей числовых шин может быть выполнен с возможностью обращаться к любой числовой шине.

Верхний ключ 202 включает в себя p-канальный транзистор 272 и p-канальный транзистор 274. P-канальные транзисторы 272 и 274 могут быть транзисторами с высоким порогом напряжения (VT). P-канальный транзистор 272 включает в себя первый вывод 275, подключенный к выводу напряжения питания (Vdd), управляющий вывод 276 и второй вывод 277, подключенный к силовому входу 262 инвертора 236 через виртуальный питающий узел 278. P-канальный транзистор 274 включает в себя первый вывод 279, подключенный к выводу напряжения питания (Vdd), управляющий вывод 280 и второй вывод 281, подключенный к силовому входу 268 инвертора 238 через виртуальный питающий узел 282. Нижний ключ 204 включает в себя n-канальный транзистор 284 и n-канальный транзистор 286. N-канальные транзисторы 284 и 286 могут быть транзисторами с высоким порогом напряжения (VT). N-канальный транзистор 284 включает в себя первый вывод 287, подключенный к силовому входу 248 логического элемента 232 И-НЕ через узел 288 виртуальной земли, управляющий вывод 289, подключенный к входу 216 активации левой линии, и второй вывод 290, подключенный к выводу напряжения питания (Vss). N-канальный транзистор 286 включает в себя первый вывод 292, подключенный к силовому входу 250 логического элемента 234 И-НЕ через узел 293 виртуальной земли, управляющий вывод 294, подключенный к входу 220 активации правой линии, и второй вывод 295, подключенный к выводу напряжения питания (Vss). Конденсатор 210 включает в себя первый вывод 296, подключенный к выводу напряжения питания (Vss), и второй вывод 297, подключенный ко второму выводу 281 p-канального транзистора 274. Конденсатор 212 включает в себя первый вывод 298, подключенный к выводу напряжения питания (Vss), и второй вывод 299, подключенный к выходу 270 инвертора 238.

При работе менеджер питания (такой как менеджер 102 питания на фиг.1) выдает сигнал активации линии, такой как сигнал активации левой линии посредством входа 216 активации левой линии или сигнал активации правой линии посредством входа 218 активации правой линии. Если сигнал активации линии - это, например, сигнал активации левой линии, n-канальный транзистор 284 принимает сигнал активации левой линии от входа 216 активации левой линии посредством управляющего вывода 289, который активирует n-канальный транзистор 284, чтобы выдавать ток, чтобы снабжать электроэнергией логический элемент 232 И-НЕ. Инверсия сигнала 216 активации левой линии выдается в управляющий вывод 276 p-канального транзистора 272, тем самым разрешая протекание тока через транзистор 272 в инвертор 236. Логический элемент 206 И выполняет логическую операцию И для сигнала активации левой линии и синхронизирующего сигнала из входа 216 активации левой линии и синхронизирующего входа 214, соответственно. Предварительно кодированные данные передаются в логический элемент 230 И посредством входов 228. Предварительно кодированные данные и сигнал активации левой линии предоставляются в логический элемент 232 И-НЕ, чтобы запитывать левую числовую шину посредством инвертора 236.

В общем, конденсаторы, такие как конденсатор 210, могут быть подключены ко второму выводу 281 p-канального транзистора 274, чтобы стабилизировать входное напряжение питания на инверторе 238 посредством силового входа 268, когда p-канальный транзистор 274 активирован. Аналогично, конденсатор (не показан) может быть добавлен ко второму выводу 277 p-канального транзистора 272, чтобы стабилизировать напряжение питания на инверторе 236 посредством силового входа 262, когда p-канальный транзистор 272 активирован. Дополнительно, конденсатор, такой как конденсатор 212, может быть предусмотрен на выходе 270 инвертора 238 (или на выходе 264 инвертора 236), чтобы стабилизировать выходное напряжение, чтобы запитывать числовую шину памяти.

В общем, каждая числовая шина банка памяти может включать в себя логику 200 числовой шины. Когда к матрице памяти банка памяти не осуществляется обращение, снабжение электроэнергией всех числовых шин отключено. При операции обращения на считывание или запись банк памяти выбирается посредством декодирования индексных битов, которые являются частью адресных битов запроса, ассоциативно связанного с операцией обращения. На основе запроса к памяти одна из числовых шин подтверждается.

Верхний ключ 202 и нижний ключ 204 включают в себя транзисторы с высоким порогом напряжения, чтобы уменьшить утечку тока. В общем, управляющие сигналы, активация левой линии (lft_en) и активация правой линии (lrt_en) являются текущими сигналами, используемыми для выбора под-банков. Поскольку только одна числовая шина активируется на банк, величина активного тока на питающих выводах Vdd и Vss, чтобы приводить в действие формирователь 200 числовой шины, небольшая.

Дополнительно, виртуальная земля и питающие узлы имеют относительно высокую емкость в сравнении с числовой шиной. Следовательно, величина заряда, требуемого верхним/нижним ключами 202 и 204 в ходе короткого периода переключения числовой шины, небольшая. Это ограничивает снижение скорости благодаря соответствующему последовательному транзистору, поскольку заряд исходит из локальной виртуальной земли или питающей емкости.

Благодаря высокому отношению диффузионной к вентильной емкости в передовых процессах, виртуальные питающие узлы (Vdd и Vss) (узлы между верхними ключами и p-канальным транзистором числовой шины) являются диффузионной емкостью всех p-канальных транзисторов формирователя числовой шины. Диффузионная емкость p-канальных транзисторов формирователя числовой шины следующая:

Уравнение 1

Подставляя C diff = 0,8 фФ/мкм, локальная емкость составляет примерно 512 фФ. Локальная емкость значительно больше емкости числовой шины в 62 фФ, описанной выше относительно уравнения 1. В ходе переключения числовой шины p-канальный транзистор инвертора включается, и отношение 8 к 1 емкости позволяет распределить заряд в C local посредством совместного использования зарядов. Это имеет преимущество уменьшения влияния на скорость числовой шины задержки числовой шины, тем самым, давая возможность использовать небольшие верхние ключи 202 и нижние ключи 204.

Посредством использования транзисторов с высоким VT в верхнем ключе 202 и нижнем ключе 204 на последней стадии логики числовой шины ток утечки ограничивается. Следовательно, другие логические устройства, в том числе логические элементы 232, 234 И-НЕ и инверторы 236 и 238, могут использовать транзисторы с низким VT, чтобы корректировать потерю скорости. Моделирования показали, что в типичном процессе 65 нм логика числовой шины на фиг.2 может быть реализована без введения значительных дополнительных вентильных задержек. Тем не менее, транзисторы с высоким VT верхнего ключа 202 и нижнего ключа 204 значительно снижают ток утечки, примерно в 20 раз, в сравнении с током утечки традиционных схем формирователей числовых шин.

Фиг.3 - это расширенное представление узла 300 логической схемы на фиг.2. Узел 300 включает в себя p-канальный транзистор 274, инвертор 238 и логический элемент 234 И-НЕ. P-канальный транзистор 274 имеет первый вывод 279, подключенный к выводу напряжения источника питания (Vdd), управляющий вывод 280, чтобы принимать сигнал активации правой числовой шины, и второй вывод 281. Инвертор 238 включает в себя транзистор 302 с низким VT и транзистор 304 с низким VT. Транзистор 302 с низким VT включает в себя первый вывод 306, подключенный ко второму выводу 281 транзистора 274 с высоким VT, управляющий вывод 308 и второй вывод 310. Логический элемент 234 И-НЕ включает в себя первый вход 244, второй вход 247 и выход 258, подключенный к управляющему выводу 308 транзистора 302. Транзистор 304 с низким VT включает в себя первый вывод 312, подключенный ко второму выводу 310 транзистора 302 с низким VT, управляющий вывод 314, подключенный к выходу 258 логического элемента 234 И-НЕ, и второй вывод 316, подключенный к выводу напряжения питания (Vss).

При работе ток, как правило, утекает через транзисторы с низким VT, указанные посредством стрелки 318. Тем не менее, p-канальный транзистор 274 сдерживает электрический ток, когда питание отключено. Поскольку менеджер питания отключает запитывания формирователя числовой шины посредством транзистора 274, к примеру, общее энергопотребление снижается за счет снижения утечки тока через неактивные транзисторы.

В общем, каждый раз когда конкретный формирователь числовой шины из набора формирователей 108 или 110 числовых шин принимает питание, ток может утекать через формирователь числовой шины вследствие низкого порога напряжения транзисторов в формирователе. Понятие порогового напряжения означает пороговый уровень напряжения включения, при котором транзистор переходит из неактивного состояния в активное состояние. В частности, электрический ток через транзистор возрастает с уровня тока в рабочей точке (измеряемого в наноамперах) до уровня активного тока, который может быть гораздо более высокого уровня. Следовательно, упрощенное уравнение подпорогового тока может читаться следующим образом:

где переменная I ds0 представляет ток утечки при пороге напряжения следующим образом:

где µ - это действительная подвижность носителей, - это соотношение ширины к длине устройства,

- это соотношение ширины к длине устройства, - это зависимая от процесса константа, и

- это зависимая от процесса константа, и  - это тепловое напряжение (примерно 26 мВ при 300° по Кельвину).

- это тепловое напряжение (примерно 26 мВ при 300° по Кельвину).

В общем, верхний ключ 202 и нижний ключ 204 могут использовать транзисторы с высоким порогом напряжения (VT). Транзистор с высоким VT относится к устройству, которое имеет высокий порог затвора, так чтобы транзистор представлял высокий импеданс по отношению к источнику напряжения. В транзисторах ток утечки возрастает экспоненциально с понижением порогового напряжения (V t). Дополнительно, ток утечки масштабируется линейно шириной транзистора (W) и обратно длиной канала (L). Посредством выборочного запитывания отдельных числовых шин в течение короткого периода времени, когда выполняется обращение к числовой шине, ток утечки значительно снижается.

Например, конкретным вариантом осуществления памяти может быть однопортовое 32 килобайтное (КБ) статическое оперативное запоминающее устройство (SRAM). SRAM может быть разделено на 16 банков, и каждый банк может быть разделен на два вложенных под-банка, с помощью логики числовой шины, такой как показанная на фиг.3. Логика 200 числовой шины совместно использует предварительно декодированные данные и отличается от традиционной логики на последней стадии. С учетом емкости (C nfet) затвора одного n-канального транзистора в SRAM следует понимать, что устройства обращения для каждой ячейки памяти добавляют емкостную нагрузку в C nfet*2 к числовой шине. Проводная емкость на ячейку примерно равна емкости одного транзистора, на основе оценки для широких ячеек 6T SRAM, сконструированных так, чтобы быть меньше 90 нм, и где соотношение сторон ячейки близко к двум, при этом направление разрядной шины является более короткой стороной. Соответственно, каждая ячейка вносит вклад в общую емкость 3C nfet числовой шины.

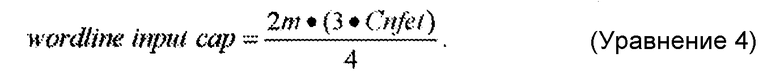

В общем, логика числовой шины может иметь такой размер, чтобы уменьшать задержки, с помощью теории логических усилий, которая предполагает, что для уменьшенной задержки для любого данного пути устройства должны иметь такой размер, чтобы каждая стадия видела усилие стадии в 4. Для блока памяти с 2n числовых шин и 2m разрядных шин конечный инвертор в логике числовой шины, такой как инвертор 236, должен иметь следующую входную емкость:

В одном варианте осуществления для n=6 и m=7 каждый вложенный под-банк SRAM составляет примерно 1 КБ, а входная емкость числовой шины составляет примерно 62 фФ. Для этой реализации общая ширина инвертора числовой шины может быть вычислена с помощью уравнения 4, так чтобы равняться 96C nfet. Пропускной элемент имеет меньший размер с длинным каналом для повышенной стабильности считывания, и C nfet составляет примерно 0,15 фемтофарад (фФ). Входная емкость в инверторе, который фактически приводит в действие числовую шину (к примеру, инверторе 236 для левой числовой шины), равна 96•0,15 фФ≈0,15 фФ. Емкость затвора в технологиях 65 нм имеет порядок примерно 1 фФ/мкм, так что общий размер формирователя 200 числовой шины может составлять примерно 15 мкм. При условии, что дырки имеют примерно половину мобильности электронов, и при условии, что требуется равное время нарастания и время спада, верхний ключ может быть сконструирован с помощью p-канального транзистора, имеющего ширину 10 мкм и ширину примерно 5 мкм, как например, p-канальный транзистор 304 на фиг.3.

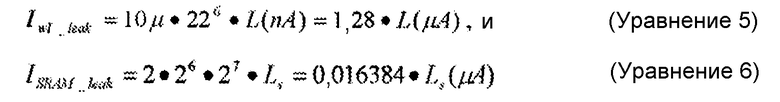

Используя характерное устройство с транзисторами с низким, обычным и высоким порогом напряжения, утечка на мкм длительности стробирующего импульса для p-канального транзистора может упоминаться как L nА/мкм, где значение L зависит от технологического процесса и от точек обработки, напряжения и температуры. Ячейка с транзисторами 6-T может быть сконструирована так, чтобы устройства в ячейке были устройствами минимальной ширины для данного технологического процесса. Устройства могут иметь большую длину канала и более высокий пороговый имплантат, что делает утечку очень небольшой. Утечка может упоминаться как L pA/на ячейку. Для банка в 2 КБ общий ток утечки всех формирователей числовых шин и ячеек матрицы должен быть следующим:

В общем, утечка формирователей числовых шин для различных значений L представлена в таблице 1.

Таблица 2 иллюстрирует утечку матрицы SRAM для различных значений L.

Таблицы 1 и 2 иллюстрируют ток утечки формирователя числовой шины в матрицу, а значения L и Ls соответствуют трем рабочим точкам по мощности, напряжению и температуре. Мощность утечки вычисляется при условии источника питания в 1,2 В, который является стандартным для процессов в 65 нм. В каждом случае ток утечки логики числовой шины больше тока утечки для всех ячеек 6-T в матрице памяти.

Это уменьшение может учитываться, поскольку транзисторы с высоким VT уменьшают утечку экспоненциально, как продемонстрировано посредством уравнения 2 выше. Ток утечки ограничен шириной верхнего ключа 202. Более того, наличие многоярусных транзисторов также снижает утечку.

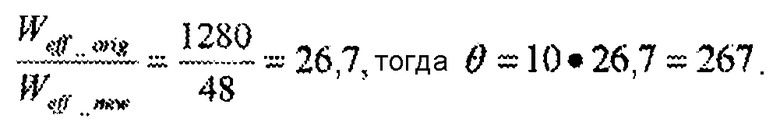

В общем, мощность утечки, сэкономленная из конечного инвертора, может быть определена посредством вычисления общей ширины верхнего ключа, которая составляет только 48 мкм. При условии, что утечка транзисторов с высоким VT составляет примерно в 10x меньше, чем для транзисторов с обычным VT, то экономия утечки (I reduce ) без учета эффекта многоярусности транзисторов может быть вычислена посредством использования отношения тока утечки на микрометр и фактической ширины конечного формирователя в обеих конструкциях следующим образом:

При подстановке в уравнение 7 отношения тока утечки в 10 отношение фактической ширины составляет

Ток утечки из конечного инвертора логики числовой шины может быть существенно снижен. При моделировании для блока 2 КБ с помощью традиционной логики числовой шины в сравнении с логикой числовой шины на фиг.2, маломощная логика числовой шины показывает общее снижение тока утечки примерно в 20 раз. Точная величина экономии утечки зависит от утечки транзистора с высоким VT, шаблона обращения к памяти и процесса выбора банков. В активном режиме, даже для шаблонов обращения к SRAM в наихудшем случае экономия мощности утечки более чем компенсирует увеличение энергопотребления от добавления верхних и нижних ключей для SRAM в 32 КБ.

Таблица 3 ниже иллюстрирует пример активной мощности наихудшего случая, добавляемой вследствие активности верхнего/нижнего ключа одного банка.

Сравнение значений таблицы 3 со значением утечки числовой шины из таблицы 1 с другими 15 неактивными банками памяти из 16 банков иллюстрирует, что экономия мощности более чем компенсирует увеличение активной мощности вследствие дополнительных устройств. Когда часть активна, температура перехода возрастает, и утечка числовой шины стремится к утечке наихудшего случая в 614,4 мкА в таблице 1.

Фиг.4 - это блок-схема последовательности операций, иллюстрирующая конкретный вариант осуществления способа снижения потребления тока утечки посредством выборочного запитывания отдельных числовых шин. Числовые шины множества банков памяти поддерживаются в отключенном состоянии (этап 400). Принимается запрос на обращение к ячейке памяти (этап 402). По меньшей мере, часть запроса на обращение к памяти декодируется, чтобы определить адрес памяти (этап 404). Банк памяти из множества банков памяти выбирается с помощью адреса памяти (этап 406). Питание включается на выбранном формирователе числовой шины, соответствующей адресу памяти, без включения питания на других формирователях числовой шины выбранного банка памяти (этап 408). Питание выключается на выбранном формирователе числовой шины, и выбор банка памяти отменяется после того, как к числовой шине выполнено обращение (этап 410).

Фиг.5 иллюстрирует примерный неограничивающий вариант осуществления портативного устройства связи, который, в общем, обозначен 520. Как проиллюстрировано на фиг.5, портативное устройство связи включает в себя внутрипроцессорную систему 522, которая включает в себя процессор 524 цифровых сигналов. Фиг.5 также иллюстрирует контроллер 526 дисплея, который подключен к процессору 524 цифровых сигналов и дисплею 528. Более того, устройство 530 ввода подключено к процессору 524 цифровых сигналов. Как показано, память 532 и кэш 546 подключены к процессору 524 цифровых сигналов. Дополнительно, процессор 524 цифровых сигналов может включать в себя кэш 548. Дополнительно, кодер/декодер (кодек) 534 может быть подключен к процессору 524 цифровых сигналов. Громкоговоритель 536 и микрофон 538 могут быть подключены к кодеку 530.

В общем, память 532, кэш 546 и кэш 548 могут включать в себя логику числовой шины согласно фиг.1-3 и могут использовать способ экономии энергии согласно фиг.4. Кэш 546 и 548 могут быть кэшем первого уровня, кэшем второго уровня и т.п. В одном конкретном варианте осуществления кэш 546 - это кэш второго уровня, а кэш 548 - это кэш первого уровня.

Фиг.5 также указывает то, что беспроводной контроллер 540 может быть подключен к процессору 524 цифровых сигналов и беспроводной антенне 542. В конкретном варианте осуществления источник 544 питания подключен к внутрипроцессорной системе 502. Более того, в конкретном варианте осуществления, как проиллюстрировано на фиг.5, дисплей 526, устройство 530 ввода, громкоговоритель 536, микрофон 538, беспроводная антенна 542 и источник 544 питания являются внешними для внутрипроцессорной системы 522. Тем не менее, каждый из них подключен к компоненту внутрипроцессорной системы 522.

В конкретном варианте осуществления процессор 524 цифровых сигналов использует перемежающуюся многопоточную обработку, чтобы обрабатывать команды, ассоциативно связанные с программными потоками, необходимыми для того, чтобы осуществлять функциональность, и операции, требуемые различными компонентами портативного устройства 520 связи. Например, когда сеанс беспроводной связи устанавливается посредством беспроводной антенны, пользователь может говорить в микрофон 538. Электронные сигналы, представляющие голос пользователя, могут отправляться в кодек 534 для кодирования. Процессор 524 цифровых сигналов может выполнять обработку данных для кодека 534, чтобы кодировать электронные сигналы от микрофона. Дополнительно, поступающие сигналы, принимаемые посредством беспроводной антенны 542, могут отправляться в кодек 534 посредством беспроводного контроллера 540 для декодирования и отправки в громкоговоритель 536. Процессор 524 цифровых сигналов также может выполнять обработку данных для кодека 534 при декодировании сигнала, принимаемого посредством беспроводной антенны 542.

Дополнительно, до, в ходе или после сеанса беспроводной связи процессор 524 цифровых сигналов может обрабатывать входные сигналы, которые принимаются от устройства 530 ввода. Например, в ходе сеанса беспроводной связи пользователь может использовать устройство 530 ввода и дисплей 528 для того, чтобы переходить с одного сайта на другой в Интернете посредством Интернет-проводника (Web browser), который встроен в память 532 портативного устройства 520 связи. Процессор 524 цифровых сигналов может перемежать различные программные потоки, которые используются устройством 530 ввода, контроллером 526 дисплея, дисплеем 528, кодеком 534 и беспроводным контроллером 540, как описано в данном документе, чтобы эффективно управлять работой портативного устройства 520 связи и его различных компонентов. Многие команды, ассоциативно связанные с различными программными потоками, исполняются одновременно в течение одного или более тактов. По сути, мощность и энергопотребление вследствие потерянных тактов могут быть существенно снижены.

DSP 524 дополнительно включает в себя глобальный регистр 560 управления режимом. Глобальный регистр 560 управления режимом может быть использован для того, чтобы управлять режимом исполнения перемежающихся потоков. Режимом исполнения для каждого потока может быть режим ожидания, активный режим, режим отключения, режим отладки или другой надлежащий режим.

Ссылаясь на фиг.6, показан примерный неограничивающий вариант осуществления сотового телефона, который в целом, обозначается 620. Как показано, сотовый телефон 620 включает в себя внутрипроцессорную систему 622, которая включает в себя цифровой процессор 624 основной полосы частот передачи и аналоговый процессор 626 основной полосы частот передачи, которые соединены между собой. В конкретном варианте осуществления цифровым процессором 624 основной полосы частот передачи является процессор цифровых сигналов. Процессор цифровых сигналов включает в себя глобальный регистр 680 управления режимами исполнения, чтобы управлять потоками процессора цифровых сигналов. Как проиллюстрировано на фиг.6, контроллер 628 дисплея и контроллер 630 сенсорного экрана подключены к цифровому процессору 624 основной полосы частот передачи. В свою очередь, сенсорный дисплей 632, внешний для внутрипроцессорной системы 622, подключен к контроллеру 628 дисплея и контроллеру 630 сенсорного экрана.

Фиг.6 дополнительно указывает то, что видеокодер 634, к примеру, кодер построчного изменения фазы (PAL), кодер Sequential Couleur abec Memoire (SECAM) или кодер National Television System Committee (NTSC), подключен к цифровому процессору 624 основной полосы частот передачи. Дополнительно, видеоусилитель 636 подключен к видеокодеру 634 и дисплею 632 сенсорного экрана. Кроме того, видеопорт 638 подключен к видеоусилителю 636. Как проиллюстрировано на фиг.6, контроллер 640 универсальной последовательной шина (USB) подключен к цифровому процессору 624 основной полосы частот передачи. Так же, USB-порт 642 подключен к USB-контроллеру 640. Память 644 и карта 646 модуля идентификации абонента (SIM) также могут быть подключены к цифровому процессору 624 основной полосы частот передачи. Память 644 может включать в себя логику числовой шины согласно фиг.1-3 и может использовать способ экономии энергии согласно фиг.4.

Дополнительно, как показано на фиг.6, цифровая камера 648 может быть подключена к цифровому процессору 624 основной полосы частот передачи. В примерном варианте осуществления цифровая камера 648 - это камера на устройстве с зарядовой связью (CCD) или камера на комплементарных (сопряженных) метало-оксидных полупроводниках (CMOS).

Как дополнительно проиллюстрировано на фиг.6, стереоаудиокодек 650 может быть подключен к аналоговому процессору 626 основной полосы частот передачи. Более того, аудиоусилитель 652 может быть подключен к стереоаудиокодеку 650. В примерном варианте осуществления первый стереогромкоговоритель 654 и второй стереогромкоговоритель 656 подключены к аудиоусилителю 652. Фиг.6 показывает, что микрофонный усилитель 658 также может быть подключен к стереоаудиокодеку 650. Помимо этого, микрофон 660 может быть подключен к микрофонному усилителю 658. В конкретном варианте осуществления радиотюнер 662 с частотной модуляцией (FM) может быть подключен к стереоаудиокодеку 650. Кроме того, FM-антенна 664 подключена к FM-радиотюнеру 662. Дополнительно, стереонаушники 666 могут быть подключены к стереоаудиокодеку 650.

Фиг.6 дополнительно иллюстрирует то, что радиочастотное (RF) приемо-передающее устройство 668 может быть подключено к аналоговому процессору 626 основной полосы частот передачи, RF-ключ 670 может быть подключен к RF приемо-передающему устройству 668 и RF-антенне 672. Как показано на фиг.6, клавишная панель 674 может быть подключена к аналоговому процессору 626 основной полосы частот передачи. Кроме того, монофоническая телефонная трубка с микрофоном 676 может быть подключена к аналоговому процессору 626 основной полосы частот передачи. Дополнительно, устройство 678 вибратора может быть подключено к аналоговому процессору 626 основной полосы частот передачи. Фиг.6 также иллюстрирует то, что источник 680 питания может быть подключен к внутрипроцессорной системе 622. В конкретном варианте осуществления источник 680 питания - это источник питания постоянного тока (DC), который снабжает питанием различные компоненты сотового телефона 620, которые требуют питания. Кроме того, в конкретном варианте осуществления источник питания - это перезаряжаемый аккумулятор DC или источник питания DC, на основе преобразователя переменного тока (AC) в DC, который подключен к источнику питания AC.

В конкретном варианте осуществления, как проиллюстрировано на фиг.6, сенсорный дисплей 632, видеопорт 638, USB-порт 642, камера 648, первый стереогромкоговоритель 654, второй стереогромкоговоритель 656, микрофон, FM-антенна 664, стереонаушники 666, RF-ключ 670, RF-антенна 672, клавишная панель 674, монофоническая телефонная трубка 676, вибратор 678 и источник 680 питания являются внешними к внутрипроцессорной системе 622. Более того, в конкретном варианте осуществления цифровой процессор 624 основной полосы частот передачи может использовать перемежающуюся многопоточную обработку, описанную в данном документе, чтобы обрабатывать различные программные потоки, ассоциативно связанные с одним или более различными компонентами, ассоциативно связанными с сотовым телефоном 620.

Ссылаясь на фиг.7, примерный неограничивающий вариант осуществления беспроводного телефона, работающего по Интернет-протоколу (IP), показан, и, в общем, обозначается 700. Как показано, беспроводной IP-телефон 700 включает в себя внутрипроцессорную систему 702, которая включает в себя процессор цифровых сигналов (DSP) 704. Процессор 704 цифровых сигналов включает в себя глобальный регистр 760 управления режимами, чтобы управлять программными потоками процессора. Как проиллюстрировано на фиг.7, контроллер 706 дисплея подключен к DSP 704, и дисплей 708 подключен к контроллеру 706 дисплея. В примерном варианте осуществления дисплеем 708 является жидкокристаллический дисплей (LCD). Фиг.7 дополнительно иллюстрирует то, что клавишная панель 710 может быть подключена к DSP 704.

Как дополнительно проиллюстрировано на фиг.7, флэш-память 712 может быть подключена к DSP 704. Синхронное динамическое оперативное запоминающее устройство (SDRAM) 714, статическое оперативное запоминающее устройство (SRAM) 716 и электрически стираемое программируемое постоянное запоминающее устройство (EEPROM) 718 также могут быть подключены к DSP 704. SDRAM 714 и SRAM 716 могут включать в себя логику числовой шины согласно фиг.1-3 и могут использовать способ экономии энергии согласно фиг.4.

Фиг.7 также иллюстрирует, что светодиод (LED) 720 может быть подключен к DSP 704. Дополнительно, в конкретном варианте осуществления речевой кодек 722 может быть подключен к DSP 704. Усилитель 724 может быть подключен к речевому кодеку 722, а моногромкоговоритель 726 может быть подключен к усилителю 724. Фиг.7 дополнительно указывает, что монофоническая телефонная трубка 728 также может быть подключена к речевому кодеку 722. В конкретном варианте осуществления монофоническая телефонная трубка 728 включает в себя микрофон.

Фиг.7 также иллюстрирует, что процессор 730 основной полосы частот передачи беспроводной локальной сети (WLAN) может быть подключен к DSP 704. RF приемопередатчик 732 может быть подключен к процессору 730 основной полосы частот передачи WLAN, а RF-антенна 734 может быть подключена к RF приемопередающему устройству 732. В конкретном варианте осуществления Bluetooth-контроллер 736 также может быть подключен к DSP 704, а Bluetooth-антенна 738 может быть подключена к контроллеру 736. Фиг.7 также иллюстрирует, что USB-порт 740 также может быть подключен к DSP 704. Более того, источник 742 питания подключен к внутрипроцессорной системе 702 и обеспечивает питанием различные компоненты беспроводного IР-телефона 700 посредством внутрипроцессорной системы 702.

В конкретном варианте осуществления, как указано на фиг.7, дисплей 708, клавишная панель 710, LED 720, моногромкоговоритель 726, монофоническая телефонная трубка 728, RF-антенна 734, Bluetooth-антенна 738, USB-порт 740 и источник 742 питания являются внешними для внутрипроцессорной системы 702. Тем не менее, каждый из этих компонентов подключен к одному или более компонентов внутрипроцессорной системы. Дополнительно, в конкретном варианте осуществления процессор 704 цифровых сигналов может использовать перемежающуюся многопоточную обработку, описанную в данном документе, чтобы обрабатывать различные программные потоки, включая связанные с исполнением потоки, ассоциативно связанные с одним или более различными компонентами, ассоциативно связанными с IP-телефоном 700.

Фиг.8 иллюстрирует примерный неограничивающий вариант осуществления портативного цифрового устройства (PDA), который, в общем, обозначен 800. Как показано, PDA 800 включает в себя внутрипроцессорную систему 802, которая включает в себя процессор цифровых сигналов (DSP) 804. Процессор цифровых сигналов 804 включает в себя глобальный регистр 860 режимов управления, чтобы управлять программными потоками процессора. Как проиллюстрировано на фиг.8, контроллер 806 сенсорного экрана и контроллер 808 дисплея подключены к DSP 804. Более того, сенсорный дисплей подключен к контроллеру 806 сенсорного экрана и контроллеру 808 дисплея. Фиг.8 также указывает то, что клавишная панель 812 может быть подключена к DSP 804.

Как дополнительно проиллюстрировано на фиг.8, флэш-память 814 может быть подключена к DSP 804. Также, постоянное запоминающее устройство (ROM) 816, динамическое оперативное запоминающее устройство (DRAM) 819 и электрически стираемое программируемое постоянное запоминающее устройство (EEPROM) 820 может быть подключено к DSP 804. DRAM 819, флэш-память 814 и другая память PDA 800 может включать в себя логику числовой шины согласно фиг.1-3 и может использовать способ экономии энергии согласно фиг.4.

Фиг.8 также показывает, что порт 822 Ассоциации по средствам передачи данных в инфракрасном диапазоне (IrDA) может быть подключен к DSP 804. Дополнительно, в конкретном варианте осуществления цифровая камера 824 может быть подключена к DSP 804.

Как показано на фиг.8, в конкретном варианте осуществления стереоаудиокодек 826 может быть подключен к DSP 804. Первый стереоусилитель 828 может быть подключен к стереоаудиокодеку 826, и первый стереогромкоговоритель 830 может быть подключен к первому стереоусилителю 828. Дополнительно, микрофонный усилитель 832 может быть подключен к стереоаудиокодеку 826, и микрофон 834 может быть подключен к микрофонному усилителю 832. Фиг.8 дополнительно показывает, что второй стереоусилитель 836 может быть подключен к стереоаудиокодеку 826, а второй стереогромкоговоритель 838 может быть подключен ко второму стереоусилителю 836. В конкретном варианте осуществления стереонаушники 840 также могут быть подключены к стереоаудиокодеку 826.

Фиг.8 также иллюстрирует, что контроллер 842 802.11 может быть подключен к DSP 804, и антенна 844 802.11 может быть подключена к контроллеру 842 802.11. Более того, Bluetooth-контроллер 846 может быть подключен к DSP 804, и Bluetooth-антенна 848 может быть подключена к Bluetooth-контролеру 846. Как проиллюстрировано на фиг.8, USB-контроллер 850 может быть подключен к DSP 804, и USB-порт 852 может быть подключен к USB-контроллеру 850. Дополнительно, смарт-карта 854, к примеру, мультимедийная карта (MMC) или защищенная цифровая карта (SD) может быть подключена к DSP 804. Более того, как показано на фиг.8, источник 856 питания может быть подключен к внутрипроцессорной системе 802 и может обеспечивать питанием различные компоненты PDA 800 посредством внутрипроцессорной системы 802.

В конкретном варианте осуществления, как указано на фиг.8, дисплей 810, клавишная панель 812, IrDA-порт 822, цифровая камера 824, первый стереогромкоговоритель 830, микрофон 834, второй стереогромкоговоритель 838, стереонаушники 840, антенна 844 802.11, Bluetooth-антенна 848, USB-порт 852 и источник 850 питания являются внешними для внутрипроцессорной системы 802. Тем не менее, каждый из этих компонентов подключен к одному или более компонентам внутрипроцессорной системы. Дополнительно, в конкретном варианте осуществления процессор 804 цифровых сигналов может использовать перемежающуюся многопоточную обработку, описанную в данном документе, чтобы обрабатывать различные программные потоки, включая связанные с исполнением потоки, ассоциативно связанные с одним или более различными компонентами, ассоциативно связанными с «карманным» компьютером 800.

Ссылаясь на фиг.9, показан примерный неограничивающий вариант осуществления проигрывателя аудиофайлов, такого как проигрыватель по стандарту Экспертной группы по киноизображению для аудио уровня-3 (MP3), который, в общем, обозначается 900. Как показано, проигрыватель 900 аудиофайлов включает в себя внутрипроцессорную систему 902, которая включает в себя процессор цифровых сигналов (DSP) 904. DSP 904 включает в себя глобальный регистр 960 управления режимами, чтобы управлять программными потоками процессора. Как проиллюстрировано на фиг, 9, контроллер 906 дисплея подключен к DSP 904, и дисплей 908 подключен к контроллеру 906 дисплея, В примерном варианте осуществления дисплеем 908 является жидкокристаллический дисплей (LCD). Фиг.9 дополнительно иллюстрирует то, что клавишная панель 904 может быть подключена к DSP 704.

Как дополнительно проиллюстрировано на фиг.9, флэш-память 912 и постоянное запоминающее устройство (ROM) 914 могут быть подключены к DSP 904. Дополнительно, MP3-проигрыватель 900 может включать в себя кэш 946, подключенную к DSP 904, и кэш 948 в DSP 904. Кэшем 946 может быть кэш второго уровня, тогда как кэшем 948 может быть кэш первого уровня. Более того, кэш 946 и 948 и другая память в аудиопроигрывателе могут включать в себя логику числовой шины согласно фиг.1-3 и могут использовать способ экономии энергии согласно фиг.4.

Дополнительно, в конкретном варианте осуществления аудиокодек 916 может быть подключен к DSP 904. Усилитель 918 может быть подключен к аудиокодеку 916, и моногромкоговоритель 920 может быть подключен к усилителю 918. Фиг.9 дополнительно указывает, что микрофонный вход 922 и стереовход 924 также могут быть подключены к аудиокодеку 916. В конкретном варианте осуществления стереонаушники 926 также могут быть подключены к аудиокодеку 916.

Фиг.9 также указывает, что USB-порт 928 и смарт-карта 930 могут быть подключены к DSP 904. Дополнительно, источник 932 питания может быть подключен к внутрипроцессорной системе 902 и может обеспечивать питанием различные компоненты проигрывателя 900 аудиофайлов посредством внутрипроцессорной системы 902.

В конкретном варианте осуществления, как указано на фиг.9, дисплей 908, клавишная панель 910, LED 920, моногромкоговоритель 920, микрофонный вход 922, стереовход 924, стереонаушники 926, USB-порт 928 и источник 932 питания являются внешними для внутрипроцессорной системы 902. Тем не менее, каждый из этих компонентов подключен к одному или более компонентам внутрипроцессорной системы. Кроме того, в конкретном варианте осуществления процессор 904 цифровых сигналов может использовать перемежающуюся многопоточную обработку, описанную в данном документе, чтобы обрабатывать различные программные потоки, включая связанные с исполнением потоки, ассоциативно связанные с одним или более различными компонентами, ассоциативно связанными с проигрывателем 900 аудиофайлов.

С помощью конфигурации структуры, раскрытой в данном документе, система и способ управления несколькими потоками в многопотоковом процессоре обеспечивают способ для того, чтобы переводить различные программные потоки в различные состояния. Кроме того, система и способ могут позволять одному потоку определять состояние другого потока. Система и способ могут быть использованы для того, чтобы управлять любым числом программных потоков способом, описанным в данном документе.

Специалисты в данной области техники дополнительно должны принимать во внимание, что различные иллюстративные логические блоки, конфигурации, модули, схемы и этапы алгоритма, описанные в связи с раскрытыми в данном документе вариантами осуществления, могут быть реализованы как электронные аппаратные средства, компьютерное программное обеспечение либо их сочетания. Чтобы понятно проиллюстрировать эту взаимозаменяемость аппаратных средств и программного обеспечения, различные иллюстративные компоненты, блоки, конфигурации, модули, схемы и этапы описаны выше, в общем, на основе их функциональности. Реализована эта функциональность в качестве аппаратных средств или программного обеспечения, зависит от конкретного варианта применения и конструктивных ограничений, накладываемых на систему в целом. Высококвалифицированные специалисты могут реализовать описанную функциональность различными способами для каждого конкретного варианта применения, но такие решения по реализации не должны быть интерпретированы как являющиеся отступлением от объема настоящего изобретения.

Этапы способа или алгоритма, описанные в связи с раскрытыми в данном документе вариантами осуществления, могут быть реализованы непосредственно в аппаратных средствах, в программном модуле, исполняемом процессором, или в их сочетании. Программный модуль может размещаться в памяти типа RAM, флэш-памяти, памяти типа ROM, память типа PROM, памяти типа EPROM, памяти типа EEPROM, в регистрах, на жестком диске, сменном диске, компакт-диске CD ROM или любой другой форме носителя данных, известной в данной области техники. Типичный носитель данных подключен к процессору, причем процессор может считывать информацию и записывать информацию на носитель данных. В альтернативном варианте носитель данных может быть встроен в процессор. Процессор и носитель данных могут постоянно размещаться в ASIC. ASIC может постоянно размещаться в вычислительном устройстве или пользовательском терминале. В альтернативном варианте процессор и носитель данных могут постоянно размещаться как дискретные компоненты в вычислительном устройстве или пользовательском терминале.

Предшествующее описание раскрытых вариантов осуществления предоставлено для того, чтобы дать возможность любому специалисту в данной области техники создавать или использовать настоящее изобретение. Различные модификации в этих вариантах осуществления должны быть очевидными для специалистов в данной области техники, а определенные в данном документе общие принципы могут быть применены к другим вариантам осуществления без отступления от сущности и объема изобретения. Таким образом, настоящее изобретение не ограничивается показанными в данном документе вариантами осуществления, а должно удовлетворять самой широкой области применения, согласующейся с принципами и новыми признаками, определенными прилагаемой формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| АССОЦИАТИВНАЯ ПАМЯТЬ СО СМЕШАННЫМ ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫМ ПОИСКОМ | 2006 |

|

RU2406167C2 |

| АССОЦИАТИВНАЯ ПАМЯТЬ | 2007 |

|

RU2452047C2 |

| УСТРОЙСТВО МАГНИТОРЕЗИСТИВНОЙ ОПЕРАТИВНОЙ ПАМЯТИ С СОВМЕСТНО ИСПОЛЬЗУЕМОЙ ЛИНИЕЙ ИСТОКА | 2008 |

|

RU2455711C2 |

| УПРАВЛЕНИЕ ВРЕМЕНЕМ ОБРАЩЕНИЯ К ПАМЯТИ | 2014 |

|

RU2618938C2 |

| СХЕМА ДВОЙНОГО ПИТАНИЯ В СХЕМЕ ПАМЯТИ | 2009 |

|

RU2480850C2 |

| УСТРОЙСТВО И СПОСОБ УСТАНОВЛЕНИЯ ТАКТОВОЙ ЧАСТОТЫ/НАПРЯЖЕНИЯ КЭШ-ПАМЯТИ НА ОСНОВАНИИ ИНФОРМАЦИИ ЗАПРОСА ПАМЯТИ | 2017 |

|

RU2717969C1 |

| ФИЗИЧЕСКИЙ УРОВЕНЬ ВЫСОКОПРОИЗВОДИТЕЛЬНОГО МЕЖСОЕДИНЕНИЯ | 2013 |

|

RU2599971C2 |

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

| ИСПОЛЬЗОВАНИЕ АУТЕНТИФИЦИРОВАННЫХ МАНИФЕСТОВ ДЛЯ ОБЕСПЕЧЕНИЯ ВНЕШНЕЙ СЕРТИФИКАЦИИ МНОГОПРОЦЕССОРНЫХ ПЛАТФОРМ | 2014 |

|

RU2599340C2 |

| СПОСОБ, УСТРОЙСТВО И СИСТЕМА УМЕНЬШЕНИЯ ВРЕМЕНИ ВОЗОБНОВЛЕНИЯ РАБОТЫ ДЛЯ КОРНЕВЫХ ПОРТОВ И КОНЕЧНЫХ ТОЧЕК, ИНТЕГРИРОВАННЫХ В КОРНЕВЫЕ ПОРТЫ | 2014 |

|

RU2645596C1 |

Изобретение относится к системам и способам снижения энергопотребления в памяти, а более конкретно к ограничению энергопотребления числовых шин в банке памяти. Техническим результатом является снижение утечки тока в запоминающих устройствах. Для достижения технического результата электронное устройство для снижения энергопотребления в запоминающем устройстве содержит память, включающую в себя множество числовых шин. Причем память включает в себя множество банков памяти, причем каждый из множества банков памяти включает в себя пару под-банков, причем пара под-банков совместно использует предварительно декодированные данные. Электронное устройство также включает множество формирователей числовых шин, подключенных к памяти, причем каждый формирователь числовой шины ассоциативно связан с числовой шиной из множества числовых шин памяти. При этом питание в каждом из множества формирователей числовых шин отключено в состоянии по умолчанию, за исключением периода обращения к числовой шине. Кроме того, электронное устройство включает декодер, подключенный к множеству формирователей числовых шин, чтобы принимать запрос на обращение к памяти и чтобы декодировать запрос на обращение к памяти для определения адреса, ассоциативно связанного с запросом на обращение к памяти. При этом декодер запитывает выбранный формирователь числовой шины, но не другие формирователи числовой шины из множества формирователей числовых шин, в ответ на запрос на обращение к памяти. 4 н. и 7 з.п. ф-лы, 9 ил., 3 табл.

1. Электронное устройство для снижения энергопотребления в запоминающем устройстве, содержащее

память, включающую в себя множество числовых шин, причем память включает в себя множество банков памяти, причем каждый из множества банков памяти включает в себя пару под-банков, причем пара под-банков совместно использует предварительно декодированные данные;

множество формирователей числовых шин, подключенных к памяти, причем каждый формирователь числовой шины ассоциативно связан с числовой шиной из множества числовых шин памяти, при этом питание в каждом из множества формирователей числовых шин отключено в состоянии по умолчанию, за исключением периода обращения к числовой шине;

декодер, подключенный к множеству формирователей числовых шин, чтобы принимать запрос на обращение к памяти, и чтобы декодировать запрос на обращение к памяти для определения адреса, ассоциативно связанного с запросом на обращение к памяти, при этом декодер запитывает выбранный формирователь числовой шины, но не другие формирователи числовой шины из множества формирователей числовых шин, в ответ на запрос на обращение к памяти.

2. Электронное устройство по п.1, в котором память содержит кэш-память.

3. Электронное устройство по п.1, дополнительно содержащее менеджер питания, чтобы выборочно активировать выбранный формирователь числовой шины в ответ на определение адреса, ассоциативно связанного с запросом на обращение к памяти.

4. Электронное устройство по п.1, в котором каждый из множества формирователей числовой шины включает в себя транзистор с высоким порогом напряжения (VT).

5. Электронное устройство для снижения энергопотребления в запоминающем устройстве, содержащее

память, включающую в себя множество числовых шин;

множество формирователей числовых шин, подключенных к памяти,

причем каждый формирователь числовой шины ассоциативно связан с числовой шиной из множества числовых шин памяти, при этом питание в каждом из множества формирователей числовых шин отключено в состоянии по умолчанию, за исключением периода обращения к числовой шине;

причем каждый из множества формирователей числовой шины содержит первый элемент И, включающий в себя первый вход, чтобы принимать сигнал активации, второй вход, чтобы принимать синхронизирующий сигнал, и выход;

второй элемент И, включающий в себя первый вход и второй вход, чтобы принимать предварительно кодированные данные, и выход;

элемент И-НЕ, включающий в себя силовой вывод, первый вход, подключенный к выходу первого элемента И, второй вход, подключенный к выходу второго элемента И, и выход;

инвертор, включающий в себя силовой вывод, вход, подключенный к выходу элемента И-НЕ, и выход, подключенный к выбранной числовой шине;

верхний ключ, включающий в себя первый вывод, подключенный к выводу напряжения питания, управляющий вывод и второй вывод, подключенный к силовому выводу инвертора; и

нижний ключ, включающий в себя первый вывод, подключенный к выводу напряжения питания, управляющий вывод и второй вывод, подключенный к силовому выводу элемента И-НЕ;

декодер, подключенный к множеству формирователей числовых шин, чтобы принимать запрос на обращение к памяти, и чтобы декодировать запрос на обращение к памяти для определения адреса, ассоциативно связанного с запросом на обращение к памяти, при этом декодер запитывает выбранный формирователь числовой шины, но не другие формирователи числовой шины из множества формирователей числовых шин;

при этом декодер формирует сигнал активации числовой шины, подаваемый на управляющие выводы верхнего ключа и нижнего ключа, чтобы выборочно запитывать формирователь числовой шины.

6. Процессорно-читаемый носитель, заключающий в себе процессорно-читаемые команды, при этом процессорно-читаемые команды содержат

команды, чтобы декодировать запрос на обращение к памяти, для определения адреса памяти, соответствующего выбранной числовой шине памяти, включающей в себя множество числовых шин, причем память включает в себя множество банков памяти, причем каждый из множества банков памяти включает в себя пару под-банков, причем пара под-банков совместно использует предварительно декодированные данные; и

команды, чтобы выборочно запитывать формирователь числовой шины, ассоциативно связанный с выбранной числовой шиной, без приложения питания к другим числовым шинам из множества числовых шин, в ответ на определение адреса памяти.

7. Процессорно-читаемый носитель по п.6, причем память содержит кэш-память второго уровня.

8. Процессорно-читаемый носитель по п.6, в котором процессорно-читаемые команды включают в себя команды, чтобы выполнить операцию чтения по выбранной числовой шине.

9. Процессорно-читаемый носитель по п.6, в котором процессорно-читаемые команды включают в себя команды, чтобы выполнить операцию записи по выбранной числовой шине.

10. Запоминающее устройство, содержащее

средство хранения, включающее в себя множество числовых шин, причем средство хранения включает в себя множество банков памяти, причем каждый из множества банков памяти включает в себя пару под-банков, причем пара под-банков совместно использует предварительно декодированные данные;

средство декодирования ввода адреса, чтобы определять адрес памяти, соответствующий выбранной одной из множества числовых шин; и средство запитывания выбранной одной из множества числовых шин, но не других числовых шин из множества числовых шин, в ответ на определение адреса памяти.

11. Запоминающее устройство по п.10, дополнительно содержащее средство переключения, чтобы выборочно подключать средство декодирования к выводу источника питания.

| СЕТЬ, ОБЕСПЕЧИВАЮЩАЯ ВОЗМОЖНОСТИ ИСПОЛЬЗОВАНИЯ МНОЖЕСТВА ВИДОВ СРЕДСТВ ПЕРЕДАЧИ ИНФОРМАЦИИ | 1994 |

|

RU2127960C1 |

| Устройство для обработки данных | 1979 |

|

SU809191A1 |

| Устройство для управления оперативной памятью | 1978 |

|

SU752338A1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Способ приработки конических зубчатых колес | 1978 |

|

SU1090512A1 |

Авторы

Даты

2011-07-20—Публикация

2007-01-04—Подача