Область техники, к которой относится изобретение

Данное раскрытие относится к компьютерным системам, и, в частности, (но не исключительно) к администрированию питанием канальных интерфейсов в таких системах.

Краткое описание чертежей

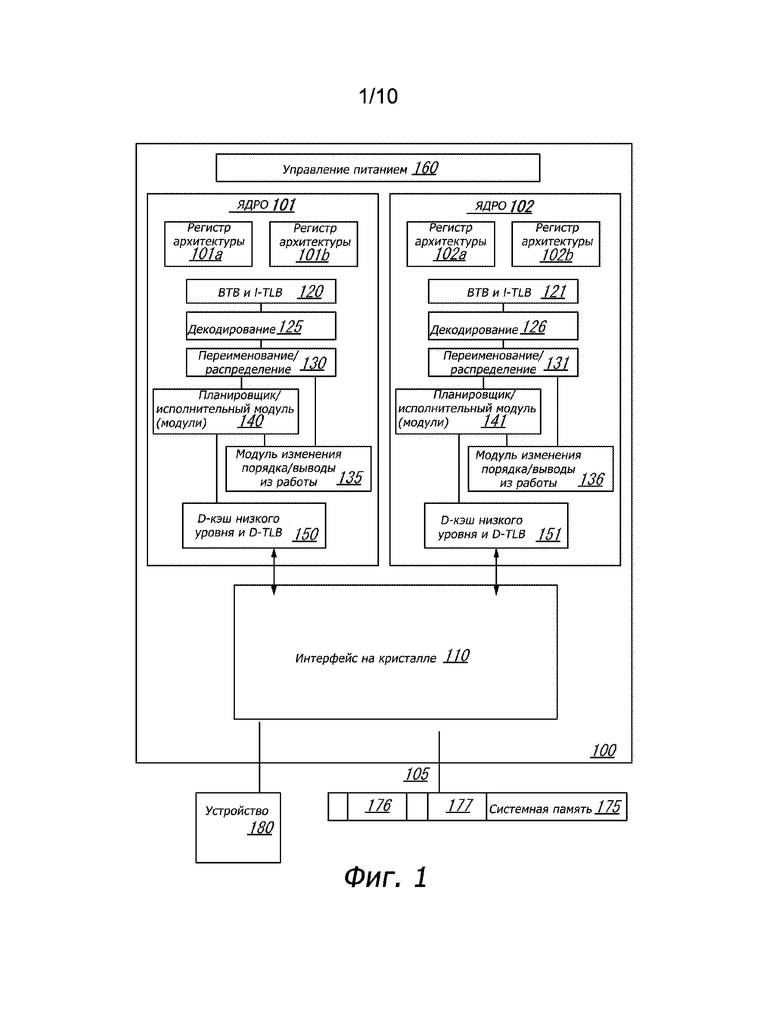

На фиг. 1 представлен вариант осуществления блок-схемы для вычислительной системы, включающей в себя многоядерный процессор.

На фиг. 2 представлен вариант осуществления структуры, состоящей из соединений из точки-в-точку, которые взаимно соединяют наборы компонентов.

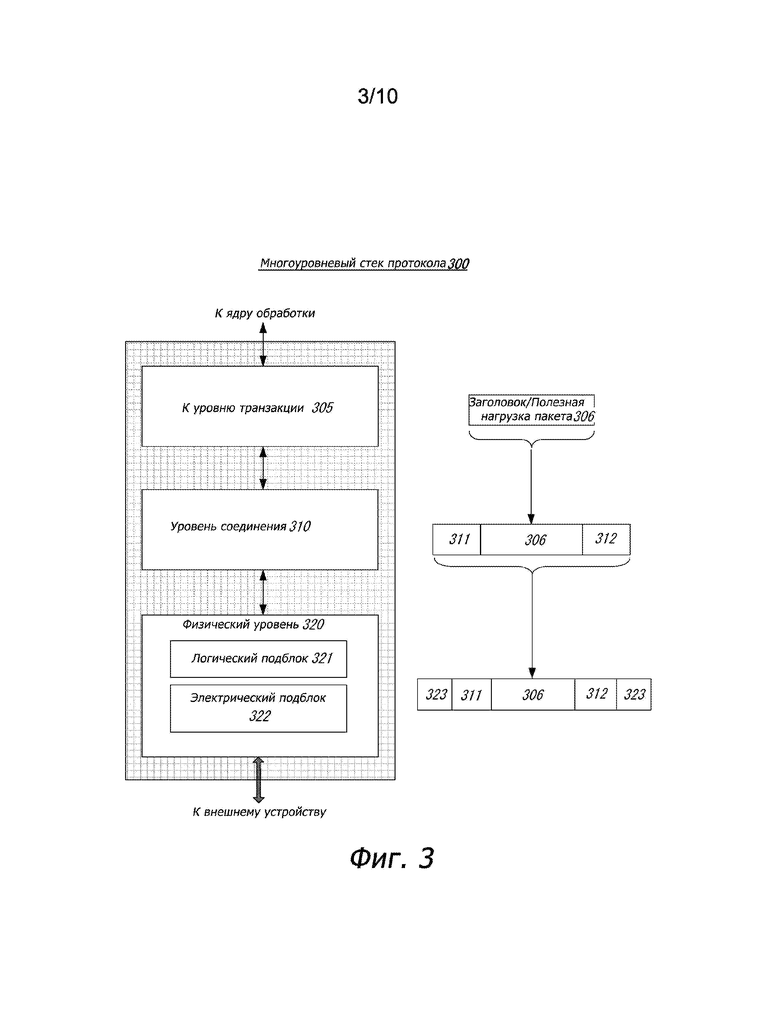

На фиг. 3 представлен вариант осуществления стека многоуровневого протокола.

На фиг. 4 представлен вариант осуществления дескриптора транзакции PCIe.

На фиг. 5 представлен вариант осуществления последовательной структуры соединений из точки-в-точку PCIe.

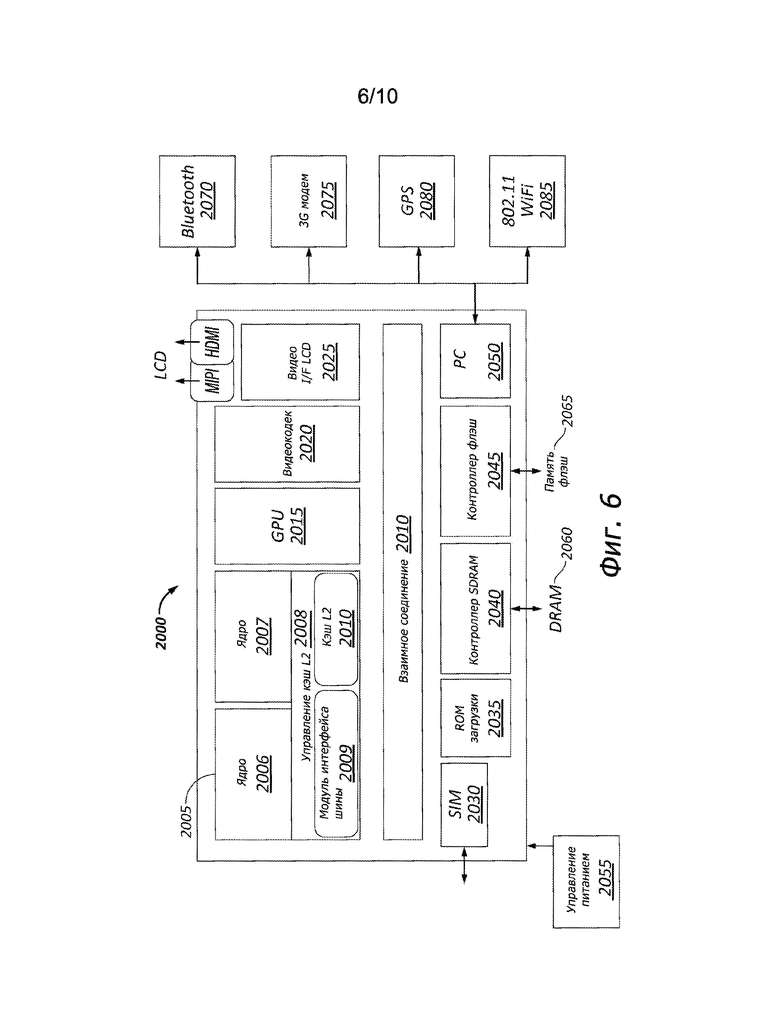

На фиг. 6 показана блок-схема конструкции SoC в соответствии с вариантом осуществления.

На фиг. 7 показана блок-схема системы в соответствии с вариантом осуществления настоящего изобретения.

На фиг. 8 показана блок-схема последовательности операций способа конфигурации в соответствии с вариантом осуществления настоящего изобретения.

На фиг. 9A показана блок-схема накопителя конфигурации в соответствии с вариантом осуществления.

На фиг. 9B показана блок-схема части схемы регулирования напряжения в соответствии с вариантом осуществления.

На фиг. 10 показана блок-схема части системы в соответствии с вариантом осуществления.

Подробное описание изобретения

В следующем описании представлено множество конкретных деталей, таких как примеры конкретных типов конфигураций процессоров и конфигураций систем, конкретных структур аппаратных средств, конкретных деталей архитектуры и микроархитектуры, конкретных конфигураций регистров, конкретных типов инструкций, конкретных компонентов системы, конкретных результатов измерений/значений высоты, конкретных этапов конвейерной обработки процессора и операций, и т.д., для того, чтобы обеспечить полное понимание настоящего изобретения. Однако для специалиста в данной области техники должно быть понятно, что данные конкретные детали не обязательно используются на практике настоящего изобретения. В других случаях хорошо известные компоненты или способы, такие как конкретная и альтернативная архитектура процессора, конкретные логические схемы/коды для описанных алгоритмов, конкретный код встроенного программного обеспечения, конкретная операция взаимного соединения, конкретные логические конфигурации, конкретные технологии изготовления и материалы, конкретные варианты воплощения компилятора, конкретное выражение алгоритмов в коде, конкретная технология/логика отключения питания и управление отпиранием, и другие конкретные детали операций компьютерной системы не были подробно описаны для того, чтобы исключить излишнее загромождение настоящего изобретения.

Хотя следующие варианты осуществления могут быть описаны со ссылкой на энергосбережение и эффективность использования энергии в конкретных интегральных схемах, таких как компьютерные платформы или микропроцессоры, другие варианты осуществления применимы для других типов интегральных схем и логических устройств. Аналогичные представленные здесь технологии и описания вариантов осуществления могут применяться для других типов схем или полупроводниковых устройств, которые также могут получать пользу, благодаря лучшей эффективности использования энергии и энергосбережения. Например, раскрытые варианты осуществления не ограничены настольными компьютерными системами или компьютерами Ультрабук™. И могут также использоваться в других устройствах, таких как переносные устройства, планшетные устройства, другие тонкие ноутбуки, устройства типа системы на кристалле (SOC) и во встроенном программном обеспечении. Некоторые примеры переносных устройств включают в себя сотовые телефоны, устройства протокола Интернет, цифровые камеры, карманные персональные компьютеры (PDA) и переносные PC. Встраиваемые приложения обычно включают в себя микроконтроллер, цифровой сигнальный процессор (DSP), систему на кристалле, сетевые компьютеры (NetPC), телевизионные приставки, сетевые концентраторы, коммутаторы глобальной вычислительной сети (WAN) или любую другую систему, которая может выполнять функции и операции, описанные ниже. Кроме того, устройство, способы и системы, описанные здесь, не ограничены физическими вычислительными устройствами, но также могут относиться к оптимизации программного обеспечения для энергосбережения и обеспечения эффективности использования энергии. Как будет понятно из представленного выше описания, варианты осуществления способов, устройств и систем, описанные здесь (либо со ссылкой на аппаратные средства, встроенное программное обеспечение, программное обеспечение или их комбинации), представляют собой основу будущей "зеленой технологии", сбалансированной с рабочими характеристиками.

По мере развития компьютерных систем, их компоненты становятся более сложными. В результате, также увеличивается сложность архитектуры взаимного соединения, предназначенной для соединения и обмена данными между компонентами, для обеспечения требуемой полосы пропускания для оптимальной работы компонента. Кроме того, различные сегменты рынка требуют разных аспектов архитектуры взаимного соединения, чтобы соответствовать потребностям рынка. Например, для сервера требуются более высокие рабочие характеристики, в то время как в мобильной экосистеме иногда могут пожертвовать общими рабочими характеристиками для экономии энергии. Также, исключительное назначение большинства структур состоит в том, чтобы обеспечить наиболее высокие рабочие характеристики при максимальной экономии энергии. Ниже описано множество взаимных соединений, которые потенциально могли бы быть улучшены на основе аспектов описанного здесь изобретения.

На фиг. 1 представлен вариант осуществления в виде блок-схемы компьютерной системы, включающей в себя многоядерный процессор. Процессор 100 включает в себя любой процессор или устройство обработки, такое как микропроцессор, встроенный процессор, цифровой сигнальный процессор (DSP), сетевой процессор, переносной процессор, процессор приложения, сопроцессор, система на кристалле (SOC) или другое устройство для выполнения кода. Процессор 100, в одном варианте осуществления, включает в себя, по меньшей мере, два ядра - ядра 101 и 102, которые могут включать в себя асимметричные ядра или симметричные ядра (в представленном варианте осуществления). Однако процессор 100 может включать в себя любое количество элементов обработки, которые могут быть симметричными или асимметричными.

В одном варианте осуществления элемент обработки относится к аппаратным средствам или логике для поддержания программного потока. Примеры аппаратных элементов обработки включают в себя: модуль потока, интервал потока, поток, модуль обработки, контекст, модуль контекста, логический процессор, аппаратный поток, ядро и/или любой другой элемент, который может поддерживать состояния процессора, такое как состояние исполнения или архитектурное состояние. Другими словами, элемент обработки, в одном варианте осуществления, относится к любому аппаратному средству, позволяющему его независимо ассоциировать с кодом, таким как программный поток, операционная система, приложение или другой код. Физический процессор (или разъем процессора) обычно относится к интегральной схеме, которая потенциально включает в себя любое количество других элементов обработки, таких как ядра или аппаратные потоки.

Ядро часто относится к логике, расположенной в интегральной схеме, позволяющей поддерживать независимое архитектурное состояние, в котором каждое независимо поддерживаемое архитектурное состояние ассоциировано, по меньшей мере, с некоторыми выделенными исполнительными ресурсами. В отличие от ядер, аппаратный поток обычно относится к любой логике, расположенной на интегральной схеме, позволяющей поддерживать независимое архитектурное состояние, в которой независимо поддерживаемые архитектурные состояния обращаются к исполнительным ресурсам. Как можно видеть, когда совместно используются определенные ресурсы, и другие специально выделяют для архитектурного состояния, происходит наложение линий между спецификацией аппаратного потока и ядром. Достаточно часто ядро и аппаратный поток рассматриваются операционной системой, как индивидуальные логические процессоры, где операционная система выполнена с возможностью индивидуального планирования операций каждого логического процессора.

Физический процессор 100, как представлено на фиг. 1, включает в себя два ядра - ядра 101 и 102. Здесь ядро 101 и 102 считаются симметричными ядрами, то есть, ядрами с одинаковыми конфигурациями, функциональными модулями и/или логикой. В другом варианте осуществления ядро 101 включает в себя ядро процессора, работающее по порядку, в то время как ядро 102 включает в себя ядро процессора, работающее по порядку. Однако ядра 101 и 102 могут быть индивидуально выбраны из любого типа ядра, такого как собственное ядро, ядро, администрируемое программными средствами, ядро, адаптированное для выполнения собственной архитектуры набора инструкций (ISA), ядро, адаптированное для выполнения транслируемой архитектуры набора инструкций (ISA), совместно разработанное ядро или другое известное ядро. В гетерогенной среде ядер (то есть, при асимметричных ядрах), некоторая форма трансляции, такая как бинарная трансляция, может использоваться для планирования или исполнения кода для одного или обоих ядер. В дальнейшем описании функциональные модули, представленные в ядре 101, описаны более подробно ниже, поскольку модули в ядре 102 работают аналогичным образом в представленном варианте осуществления.

Как представлено, ядро 101 включает в себя два аппаратных потока 101a и 101b, которые также могут называться интервалами 101a и 101b аппаратных потоков. Поэтому, программные объекты, такие как операционная система, в одном варианте осуществления потенциально рассматривают процессор 100, как четыре отдельных процессора, то есть, четыре логических процессора или элемента обработки, выполненных с возможностью исполнения четырех программных потоков одновременно. Как упомянуто выше, первый поток ассоциирован с регистрами 101a состояния архитектуры, второй поток ассоциирован с регистрами 101b состояния архитектуры, третий поток может быть ассоциирован с регистрами 102a состояния архитектуры, и четвертый поток может быть ассоциирован с регистрами 102b состояния архитектуры. Здесь каждый из регистров (101a, 101b, 102a, и 102b) состояния архитектуры может называться элементами обработки, интервалами потока или модулями потока, как описано выше. Как представлено, регистры 101a состояния архитектуры повторены в регистрах 101b состояния архитектуры, таким образом, что отдельные состояния/контексты архитектуры выполнены с возможностью их сохранения для логического процессора 101a и логического процессора 101b. В ядре 101 другие меньшие ресурсы, такие как указатели инструкций и логика переименования в блоке 130 распределения и переименования, также могут быть повторены для потоков 101a и 101b. Некоторые ресурсы, такие как буферы изменения порядка, в модуле 135 изменения порядка/вывода из работы, ILTB 120, буферы загрузки и сохранения, и очереди, могут совместно использоваться путем разделения на части. Другие ресурсы, такие как внутренние регистры общего назначения, регистр (регистры) на основе страничной таблицы, кэш данных низкого уровня и данные-TLB 115, исполнительный модуль (модули) 140, и части модуля 135, работающего не по порядку, потенциально совместно используются полностью.

Процессор 100 часто включает в себя другие ресурсы, которые могут полностью совместно использоваться, могут распределяться путем разделения на части, или могут быть специально выделены элементами обработки или для элементов обработки. На фиг. 1 представлен вариант осуществления исключительно примерного процессора с иллюстративными логическими модулями/ресурсами процессора. Следует отметить, что процессор может включать в себя или может исключать любой из этих функциональных модулей, а также может включать в себя любые другие известные функциональные модули, логику или встроенное программное обеспечение, которое не представлено. Как показано, ядро 101 включает в себя упрощенное, репрезентативное ядро процессора, работающее не по порядку (OOO). Но процессор, работающий по порядку, может использоваться в других вариантах осуществления. Ядро OOO включает в себя целевой буфер 120 ответвления для прогнозирования ответвлений, которые должны исполняться/которые требуется принимать, и буфер 120 инструкции-трансляции (I-TLB), для сохранения входов трансляции адресов для инструкций.

Ядро 101 дополнительно включает в себя модуль 125 декодирования, соединенный с модулем 120 выборки, для декодирования выбранных элементов. Логика выборки, в одном варианте осуществления, включает в себя индивидуальные секвенсоры, ассоциированные с интервалами 101a, 101b потока, соответственно. Обычно ядро 101 ассоциировано с первой ISA, которая определяет/устанавливает инструкции, исполняемые в процессоре 100. Часто инструкции машинного кода, которые представляют собой часть первой ISA, включают в себя часть инструкции (называется opp-кодом), которая ссылается на/устанавливает инструкцию или операцию для выполнения. Логика 125 декодирования включает в себя схему, которая распознает эти инструкции по их opp-кодам и передает декодированные инструкции в конвейер для обработки, как определено первой ISA. Например, как более подробно описано ниже, декодеры 125, в одном варианте осуществления, включают в себя логику, разработанную или адаптированную для распознавания конкретных инструкций, таких как инструкции транзакций. В результате распознавания декодерами 125, архитектура или ядро 101 предпринимает определенные, заданные действия для выполнения задач, ассоциированных с соответствующей инструкцией. Важно отметить, что любая из задач, блоков, операций и способов, описанных здесь, могут быть выполнены в ответ на одну или множество инструкций, некоторые из которых могут быть новыми или старыми инструкциями. Следует отметить, что декодеры 126, в одном варианте осуществления, распознают ту же ISA (или ее поднабор). В качестве альтернативы, в среде с гетерогенными ядрами, декодеры 126 распознают вторую ISA (либо поднабор из первой ISA, или отдельную ISA).

В одном примере блок 130 распределителя и переименования включает в себя распределитель для резервирования ресурсов, таких как файлы регистров, для сохранения результатов обработки инструкций. Однако потоки 101a и 101b потенциально могут выполняться не по порядку, при этом блок 130 распределителя и переименования также резервирует другие ресурсы, такие как буферы изменения порядка, для отслеживания результатов инструкций. Модуль 130 также может включать в себя блок переименования регистра для переименования регистров ссылки на программы/инструкции на другие регистры, внутренние для процессора 100. Модуль 135 изменения порядка/вывода из работы включает в себя компоненты, такие как упомянутые выше буферы изменения порядка, буферы загрузки и буферы сохранения, для поддержки исполнения не по порядку с последующим выводом из работы по порядку инструкций, выполненных не по порядку.

Блок 140 планировщика и исполнительного модуля (модулей), в одном варианте осуществления, включают в себя модуль планировщика для планирования инструкции/операции для исполнительных модулей. Например, инструкцию с плавающей точкой планируют по порту исполнительного модуля, который имеет доступный исполнительный модуль для операций с плавающей точкой. Файлы регистров, ассоциированные с исполнительными модулями, также включены для сохранения информации с результатами обработки инструкции. Примерные исполнительные модули включают в себя исполнительный модуль для операций с плавающей точкой, исполнительный модуль, работающий с целыми числами, исполнительный модуль перехода, исполнительный модуль загрузки, исполнительный модуль сохранения и другие известные исполнительные модули.

Кэш данных более низкого уровня и буфер 150 трансляции данных (D-TLB) соединены с исполнительным модулем (модулями) 140. Кэш данных предназначен для сохранения используемых/оперируемых в последнее время элементов, таких как операнды данных, которые потенциально содержаться в состояниях когерентности памяти. D-TLB предназначен для сохранения последних виртуальных/линейных трансляций в физический адрес.

В качестве конкретного примера, процессор может включать в себя структуру страничной таблицы, для разбивки физической памяти на множество виртуальных страниц.

Здесь ядра 101 и 102 совместно используют доступ к более высокому уровню или еще более дальний кэш, такой, как кэш второго уровня, ассоциированный с интерфейсом 110 на кристалле. Следует отметить, что более высокий уровень или более дальний относятся к уровням кэш, увеличивающимся или отдаляющимся дальше относительно исполнительного модуля (модулей). В одном варианте осуществления кэш более высокого уровня представляет собой кэш данных последнего уровня (последний кэш в иерархии памяти в процессоре 100), такой как кэш данных второго или третьего уровня. Однако кэш более высокого уровня не ограничен этим, и может быть ассоциирован с или может включать в себя кэш инструкции. Кэш трассы (тип кэш-инструкции) вместо этого, может быть включен после декодера 125 для сохранения последних декодированных трасс. Здесь инструкция потенциально относится к макроинструкции (то есть, общей инструкции, распознаваемой декодерами), которую можно декодировать на множество микроинструкций (микроопераций).

В представленной конфигурации процессор 100 также включает в себя модуль 110 интерфейса на кристалле. Исторически, контроллер памяти, который более подробно описан ниже, был включен в компьютерную систему, снаружи от процессора 100. В этом сценарии интерфейс 11 на кристалле должен связываться с устройствами, расположенными снаружи от процессора 100, такими как системная память 175, набор микросхем (часто включающий в себя концентратор контроллера памяти для соединения с памятью 175, и концентратор контроллера I/O для соединения с периферийными устройствами), концентратор контроллера памяти, северный мост или другую интегральную схему. И в этом сценарии, шина 105 может включать в себя любое известное взаимное соединение, такое как многоточечная шина, взаимное соединение из точки-в-точку, последовательное взаимное соединение, параллельную шину, когерентную (например, когерентную для кэш) шину, многоуровневую архитектуру протокола, дифференциальную шину и шину GTL.

Запоминающее устройство 175 может быть специально выделено для процессора 100 или может совместно использоваться с другими устройствами в системе. Общие примеры типов запоминающего устройства 175 включают в себя DRAM, SRAM, энергонезависимое запоминающее устройство (запоминающее устройство NV), и другие известные устройства сохранения. Следует отметить, что устройство 180 может включать в себя графический ускоритель, процессор или карту, соединенную с концентратором контроллера памяти, накопитель данных, соединенный с концентратором контроллера I/O, беспроводный приемопередатчик, устройство флэш-памяти, аудиоконтроллер, сетевой контроллер или другое известное устройство.

Однако, в последнее время, по мере того, как все чаще логику и устройства интегрируют на одном кристалле, таком как SOC, каждое из этих устройств может быть встроено в процессор 100. Например, в одном варианте осуществления, концентратор контроллера памяти находится в том же пакете и/или на том же кристалле с процессором 100. Здесь, часть ядра (участок на ядре) 110 включает в себя один или больше контроллер (контроллеров) для взаимодействия с другими устройствами, такими как запоминающее устройство 175 или графическое устройство 180. Конфигурация, включающая в себя взаимное соединение и контроллеры для взаимодействия с такими устройствами, часто называется конфигурацией на ядре (или вспомогательной частью процессора). В качестве примера, интерфейс 110 на кристалле включает в себя кольцевое взаимное соединение для передачи данных на кристалле, и высокоскоростное соединение 105 из точки-в-точку для обмена данными за пределами кристалла. Также, в среде SOC, даже большее количество устройств, таких как сетевой интерфейс, сопроцессоры, запоминающее устройство 175, графический процессор 180 и любые другие известные компьютерные устройства/интерфейсы могут быть интегрированы на одном кристалле или в интегральной схеме для обеспечения малых размеров при высокой функциональности и низком потреблении энергии.

В одном варианте осуществления процессор 100 выполнен с возможностью выполнения кода 177 компилятора, оптимизации и/или транслятора для компиляции, трансляции и/или оптимизации кода 176 приложения, для поддержки устройства и способов, описанных здесь для формирования интерфейса с ними. Компилятор часто включает в себя программу или набор программ для трансляции текста/кода источника в целевой текст/код. Обычно компиляция кода программы/приложения с помощью компилятора выполняется за множество фаз, и переходит к преобразованию кода языка высокого уровня программирования в код машинного языка или языка ассемблера низкого уровня. Хотя, компиляторы одним переходом все еще могут использоваться для простой компиляции. В компиляторе могут использоваться любые известные технологии компиляции, и он может выполнять любые известные операции компилятора, такие как лексический анализ, предварительная обработка, синтаксический анализ, семантический анализ, генерирование кода, преобразование кода и оптимизация кода.

Крупные компиляторы часто включают в себя множество фаз, но чаще всего эти фазы включены в две общие фазы: (1) предварительная обработка, то есть, в общем, когда происходит синтаксическая обработка, семантическая обработка, и некоторое преобразование/оптимизация, и (2) завершающая обработка, то есть, в общем, когда происходит анализ, преобразование, оптимизация и генерирование кода. Некоторые компиляторы относятся к средним, в которых представлено размывание границ или устранение границ между предварительной обработкой и завершающей обработкой компилятора. В результате, может происходить ссылка на вставку, ассоциацию, генерирование или другую операцию компилятора на любой из упомянутых выше фазах или переходах, также, как и на любых других известных фазах или проходах компилятора. В качестве иллюстративного примера, компилятор частично вставляет операции, вызовы, функции и т.д. в одну или больше фаз компиляции, таких как вставка вызовов/операций на фазе предварительной обработки компиляции и с последующим преобразованием вызовов/операций в код более низкого уровня во время фазы преобразования. Следует отметить, что во время динамической компиляции код компилятора или код динамической оптимизации может вставлять такие операции/вызовы, а также оптимизировать код для исполнения во время работы. В качестве конкретного иллюстративного примера, двоичный код (уже компилированный код) может быть динамически оптимизирован во время выполнения. Здесь программный код может включать в себя код динамической оптимизации, двоичный код или их комбинацию.

Аналогично компилятору, транслятор, такой как двоичный транслятор, транслирует код либо статически, или динамически для оптимизации и/или трансляции кода. Поэтому, ссылка на исполнение кода, кода приложения, программного кода или другой программной среды может относиться к следующим: (1) исполнение программы (программ) компилятора, оптимизатора кода оптимизации или транслятора либо динамически, или статически для компиляции программного кода, для поддержания программных структур, для выполнения других операций, для оптимизации кода или для трансляции кода; (2) исполнение основного программного кода, включая в себя операции/вызовы, такие как программный код, который был оптимизирован/компилирован; (3) исполнение другого программного кода, такого как библиотеки, ассоциированные с основным программным кодом, для поддержания программных структур, для выполнения других операций, относящихся к программному обеспечению, или для оптимизации кода; или (4) их комбинации.

Одна архитектура структуры взаимного соединения включает в себя архитектуру PCIe. Основная цель PCIe состоит в том, чтобы обеспечить возможность взаимодействия компонентов и устройств разных производителей в открытой архитектуре, охвата множества сегментов рынка; клиентов (настольных и мобильных), серверов (стандартных и промышленных) и встроенных устройств, и устройств передачи данных. PCI Express представляет собой взаимные соединения I/O высокой эффективности общего назначения, пригодные для большого разнообразия будущих вычислительных платформ и платформ передачи данных. Некоторые атрибуты PCI, такие как его модель использования, архитектура нагрузки и сохранения, и программные интерфейсы, поддерживались в течение его повторных изданий, тогда как предыдущие варианты воплощения параллельной шины были заменены высокомасштабируемым, полностью последовательным интерфейсом. В более поздних версиях PCI Express используются преимущества взаимных соединений из точки-в-точку, технологии на основе переключения и пакетированного протокола, для предоставления новых уровней рабочих характеристик и свойств. Администрирование питанием, качество услуги (QoS), поддержка установки во время работы/замена во время работы, целостности данных, и обработки ошибок находятся среди некоторых из усовершенствованных свойств, поддерживаемых PCI Express.

На фиг. 2 представлен вариант осуществления структуры, состоящей из соединений из точки-в-точку, которые соединяют наборы компонентов. Система 200 включает в себя процессор 205 и системную память 210, соединенную с концентратором 215 контроллера. Процессор 205 включает в себя любой элемент обработки, такой как микропроцессор, хост-процессор, встроенный процессор, сопроцессор или другой процессор. Процессор 205 соединен с концентратором 215 контроллера через системную шину (FSB) 206. В одном варианте осуществления FSB 206 представляет собой последовательное взаимное соединение из точки-в-точку, как описано ниже. В другом варианте осуществления, соединение 206 включает в себя последовательную архитектуру для дифференциального взаимного соединения, которая соответствует стандарту дифференциального взаимного соединения.

Системная память 210 включает в себя любое запоминающее устройство, такое как оперативное запоминающее устройство (RAM), энергонезависимое (NV) запоминающее устройство или другое запоминающее устройство, доступ к которому может осуществляться устройствами в системе 200. Системная память 210 соединена с концентратором 215 контроллера через интерфейс 216 памяти. Примеры интерфейса памяти включают в себя интерфейс памяти с двойной скоростью передачи данных (DDR), интерфейс памяти DDR с двойным каналом, и интерфейс памяти динамической RAM (DRAM).

В одном варианте осуществления концентратор 215 контроллера представляет собой корневой концентратор, корневой комплекс или корневой контроллер в иерархии взаимного соединения в последовательной шине периферийных компонентов PCI Express (PCIe или PCIE). Примеры концентратора 215 контроллера включают в себя набор микросхем, концентратор контроллера памяти (MCH), северный мост, взаимно соединенный концентратор контроллера (ICH), южный мост и корневой контроллер/концентратор. Часто термин набор микросхем относится к двум физически отдельным концентраторам контроллера, то есть, концентратору контроллера памяти (MCH), который соединен с концентратором контроллера взаимного соединения (ICH). Следует отметить, что современные системы часто включают в себя MCH, интегрированные с процессором 205, в то время как контроллер 215 предназначен для связи с устройствами I/O, аналогичным образом, как описано ниже. В некоторых вариантах осуществления, в случае необходимости, поддерживается "одноранговая" маршрутизация через корневой комплекс 215.

Здесь, концентратор 215 контроллера соединен с переключателем/мостом 220 через последовательное соединение 219. Модули 217 и 221 ввода/вывода, которые также могут называться интерфейсами/портами 217 и 221, включают в себя/воплощают многоуровневый стек протокола для обеспечения возможности обмена данными между концентратором 215 контроллера и переключателем 220. В одном варианте осуществления множество устройств выполнены с возможностью их соединения с переключателем 220.

Переключатель/мост 220 направляет пакеты/сообщения из устройства 225 вверх по потоку, то есть, вверх по иерархии в направлении корневого комплекса, в концентратор 215 контроллера, и вниз по потоку, то есть, вниз по иерархии от корневого контроллера из процессора 205 или системной памяти 210 в устройство 225. Переключатель 220, в одном варианте осуществления, называется логической сборкой множества виртуальных устройств моста PCI-в-PCI. Устройство 225 включает в себя любое внутреннее или внешнее устройство или компонент, который может соединяться с электронной системой, такой как устройство I/O, контроллер сетевого интерфейса (NIC), добавляемая карта, аудиопроцессор, сетевой процессор, привод жесткого диска, устройство накопитель, CD/DVD ROM, монитор, принтер, мышь, клавиатура, маршрутизатор, портативное устройство накопитель, устройство Firewire, устройство универсальной последовательной шины (USB), сканер и другие устройства ввода-вывода. Часто характерное для PCIe устройство называется конечной точкой. Хотя это специально не показано, устройство 225 может включать в себя мост из PCIe в PCI/PCI-X, для поддержки традиционной или другой версии устройства PCI. Конечные устройства в PCIe часто классифицируются, как традиционные PCIe или конечные точки, интегрированные с корневым комплексом.

Графический ускоритель 230 также соединен с концентратором 215 контроллера через последовательное соединение 232. В одном варианте осуществления графический ускоритель 230 соединен с MCH, который соединен с ICH. Переключатель 220 и, соответственно, устройство 225 I/O затем соединены с ICH. I/O модули 231 и 218 также должны воплощать многоуровневый стек протокола для обмена данными между графическим ускорителем 230 и концентратором 215 контроллера. Аналогично, представленное выше описание MCH, графический контроллер или графический ускоритель 230 сами по себе могут быть интегрированы в процессоре 205.

Возвращаясь к фиг. 3, здесь представлен вариант осуществления многоуровневого стека протокола. Многоуровневый стек 300 протокола включает в себя любую форму многоуровневого стека передачи данных, такого как стек быстрого пути взаимного соединения (QPI), стек PCIe, стек взаимного соединения для следующего поколения вычислительной техники с высокими рабочими характеристиками или другой многоуровневый стек. Хотя представленное ниже описание со ссылкой на фиг. 2-5, относится к стеку PCIe, те же концепции могут применяться в других стеках взаимного соединения. В одном варианте осуществления стек 300 протокола представляет собой стек протокола PCIe, включающий в себя уровень 305 транзакции, уровень 310 соединения и физический уровень 320. Интерфейс может быть представлен, как стек протокола 300 передачи данных. Представление в виде стека протокола передачи данных также может относиться к модулю или интерфейсу, воплощающему/включающему в себя стек протокола.

В PCI Express используются пакеты, для обмена информацией между компонентами. Пакеты формируют на уровне 305 транзакции и на уровне 310 соединения данных, для переноса информации из компонента передачи в компонент приема. По мере того, как передаваемые пакеты протекают через другие уровни, они расширяются дополнительной информацией, необходимой для обработки пакетов на этих уровнях. На стороне приема выполняется обратная обработка, и пакеты преобразуют из их представления физического уровня 320 в представление уровня 310 соединения данных и, в конечном итоге (для пакетов уровня транзакции) в форму, которая может обрабатываться уровнем 305 транзакции приемного устройства.

В одном варианте осуществления уровень 305 транзакции предназначен для обеспечения интерфейса между ядром обработки устройства и архитектурой взаимного соединения, такой как уровень 310 соединения данных и физический уровень 320. В этом отношении, основная ответственность уровня 305 транзакции состоит в сборке и разборке пакетов (то есть, пакетов уровня транзакции, или TLP). Уровень 305 трансляции обычно администрирует управлением потока на основе кредита для TLP. PCIe воплощает разделенные транзакции, то есть транзакции с запросом и ответом, разделенными по времени, что позволяют передавать по соединению другой трафик, в то время как целевое устройство собирает данные для ответа.

Кроме того, PCIe использует управление потоком на основе кредита. В этой схеме устройство объявляет исходную величину кредита для каждого из приемных буферов на уровне 305 транзакции. Внешнее устройство на противоположном конце соединения, такое как концентратор контроллера, подсчитывает величину кредита, расходуемую каждым TLP. Транзакция может быть передана, если транзакция не превышает предел кредита. При приеме отклика величину кредита восстанавливается. Преимущество кредитной схемы состоит в том, что задержка с возвратом кредита не влияет на рабочие характеристики, при условии, что предел кредита не будет превышен.

В одном варианте осуществления четыре области адреса транзакции включают в себя область адреса конфигурации, область адреса памяти, область адреса ввода/вывода и область адреса сообщения. Транзакции области памяти включают в себя один или больше запросов считывания и запросов записи для передачи данных в/из местоположения, отображенного в памяти. В одном варианте осуществления транзакции области памяти позволяют использовать два разных формата адреса, например, короткий формат адреса, такой как 32-битный адрес, или длинный формат адреса, такой как 64-битный адрес. Транзакции области конфигураций используются для области конфигураций доступа устройств PCIe. Транзакции для области конфигураций включают в себя запросы считывания и запросы записи. Транзакции области сообщения (или, просто сообщения) определены для поддержки передачи в полосе между агентами PCIe.

Поэтому, в одном варианте осуществления, уровень 805 транзакции собирает заголовок/полезную нагрузку 806 пакета. Формат для современных заголовков/полезных нагрузок пакета можно найти в спецификации PCIe на веб-сайте спецификации PCIe.

Вкратце, на фиг. 4 представлен вариант осуществления дескриптора транзакции PCIe. В одном варианте осуществления дескриптор 400 транзакции представляет собой механизм для переноса информации о транзакции. В этом отношении, дескриптор 400 транзакции поддерживает идентификацию транзакций в системе. Другое потенциальное использование включает в себя модификации отслеживания принятого по умолчанию упорядочивания транзакции и ассоциацию транзакции с каналами.

Дескриптор 400 транзакции включает в себя поле 402 глобального идентификатора, поле 404 атрибутов и поле 406 идентификатора канала. В представленном примере, поле 402 глобального идентификатора показано, как содержащее поле 408 локального идентификатора транзакции и поле 410 идентификатора источника. В одном варианте осуществления идентификатор 402 глобальной транзакции является уникальным для всех неотправленных запросов.

В соответствии с одним вариантом осуществления, поле 408 локального идентификатора транзакции представляет собой поле, генерируемое запрашивающим агентом, и оно является уникальным для всех неотправленных запросов, которые требуют завершения для этого запрашивающего агента. Кроме того, в этом примере, идентификатор 410 источника уникально идентифицирует агента запрашивающего устройства в пределах иерархии PCIe. В соответствии с этим, вместе с ID 410 источника, поле 408 локального идентификатора транзакции обеспечивает глобальную идентификацию транзакции в пределах области иерархии.

Поле 404 атрибутов устанавливает характеристики и взаимосвязи транзакции. В этом отношении, поле 404 атрибутов потенциально используется для предоставления дополнительной информации, которая позволяет выполнить модификацию принятой по умолчанию обработки транзакций. В одном варианте осуществления поле 404 атрибутов включает в себя поле 412 приоритета, зарезервированное поле 414, поле 416 упорядочения и поле 418 без отслеживания информации. Здесь вспомогательное поле 412 приоритета может быть модифицировано инициатором для назначения приоритета транзакции. Поле 414 зарезервированного атрибута остается зарезервированным для будущего использования или определенного использования поставщиком. Возможные модели использования с применением атрибута приоритета или безопасности могут быть воплощены, используя поле зарезервированного атрибута. В этом примере поле 416 атрибута упорядочения используется для предоставления дополнительной информации, переносящей тип упорядочивания, который может модифицировать принятые по умолчанию правила порядка. В соответствии с одним примерным вариантом осуществления, атрибут упорядочения, равный "0", обозначает принятые по умолчанию правила упорядочения, которые должны применяться, в которых атрибут упорядочения, равный "1", обозначает ослабленное упорядочение, в котором записи могут представлять собой записи передачи в том же направлении, и выполнение считывания может передавать записи в том же направлении. Поле 418 атрибута отслеживания используется для определения, выполняется ли отслеживание транзакции. Как показано, поле 406 ID канала идентифицирует канал, с которым ассоциирована транзакция.

Уровень 310 соединения, также называемый уровнем 310 соединения данных, действует, как промежуточный этап между уровнем 305 транзакции и физическим уровнем 320. В одном варианте осуществления ответственность уровня 310 соединения данных состоит в предоставлении надежного механизма для обмена пакетами уровня транзакции (TLP) между двумя компонентами соединения. Одна сторона уровня 310 соединения данных принимает TLP, собранные уровнем 305 транзакции, применяет идентификатор 311 последовательности пакета, то есть, идентификационный номер или номер пакета, рассчитывает и применяет код детектирования ошибок, то есть, CRC 312, и передает модифицированные TLP в физический уровень 320 для передачи через физический уровень во внешнее устройство.

В одном варианте осуществления физический уровень 320 включает в себя логический подблок 321 и электрический подблок 322 для физической передачи пакета во внешнее устройство. Здесь логический подблок 321 отвечает за "цифровые" функции физического уровня 321.

В этом отношении, логический подблок включает в себя блок передачи для подготовки исходящей информации для передачи физическим подблоком 322 и блок приемника, для идентификации и подготовки принятой информации перед передачей ее на уровень 310 соединения.

Физический блок 322 включает в себя передатчик и приемник. Логический подблок 321 подает в передатчик символы, которые передатчик преобразует в последовательную форму и передает по внешнее устройство. В приемник поступают преобразованные в последовательную форму символы из внешнего устройства и преобразуют принятые сигналы в поток битов. Поток битов преобразуют в параллельную форму и подают в логический подблок 321. В одном варианте осуществления используется код передачи 8b/10b, где передают/принимают десятибитные символы. Здесь используются специальные символы для формирования пакета в виде фреймов 323. Кроме того, в одном примере, приемник также предоставляет тактовую частоту символов, восстановленную из входящего последовательного потока.

Как упомянуто выше, хотя уровень 305 транзакции, уровень 310 соединения и физический уровень 320 описаны со ссылкой на конкретный вариант осуществления стека протокола PCIe, многоуровневый стек протокола не ограничен этим. Фактически, может быть включен/воплощен любой многоуровневый протокол. Например, порт/интерфейс, который представлен, как многоуровневый протокол, включает в себя: (1) первый уровень для сборки пакетов, то есть, уровень транзакций; второй уровень для упорядочивания последовательности пакетов, то есть, уровень соединения; и третий уровень для передачи пакетов, то есть, физический уровень. В качестве конкретного примера, используется многоуровневый протокол QPI.

Далее, на фиг. 5, представлен вариант осуществления последовательной структуры из точки-в-точку PCIe. Хотя представлен вариант осуществления последовательного соединения из точки-в-точку PCIe, последовательное соединение из точки-в-точку не ограничено этим, поскольку оно включает в себя любое количество путей передачи для передачи последовательных данных. В представленном варианте осуществления основное соединение PCIe включает в себя две низковольтные, дифференциально возбуждаемые сигнальные пары: пару 506/511 передачи и пару 512/507 приема. В соответствии с этим, устройство 505 включает в себя логику 506 передачи для передачи данных в устройство 510 и логику 507 приема для приема данных из устройства 510. Другими словами, два пути передачи, то есть, пути 516 и 517, и два пути приема, то есть, пути 518 и 515, включены в соединение PCIe.

Путь передачи относится к любому пути для данных передачи, таких как линия передачи, медная линия, оптическая линия, канал беспроводной передачи данных, канал инфракрасной передачи данных или другой путь передачи данных. Соединение между двумя устройствами, такими как устройство 505 и устройство 510, называется соединением, таким как соединение 415. Соединение может поддерживать одну трассу - каждая трасса представляет набор дифференциальных сигнальных пар (одна пара на передачу, одна пара на прием). Для масштабирования полосы пропускания, соединение может объединять множество трасс, обозначенных xN, где N представляет собой любую поддерживаемую ширину соединения, такую как 1, 2, 4, 8, 12, 16, 32, 64 или шире.

Дифференциальной парой называются два пути передачи, такие как линии 516 и 517 для передачи дифференциальных сигналов. Например, когда линии 516 переключаются с уровня низкого напряжения на уровень высокого напряжения, то есть, передний фронт, линия 517 возбуждается с высокого логического уровня на низкий логический уровень, то есть, отрицательный перепад. Дифференциальные сигналы потенциально демонстрируют лучшие электрические характеристики, такие как лучшая целостность сигнала, то есть, перекрестная взаимосвязь, выброс напряжения/недостаточное напряжение, затухающие колебания и т.д. Это позволяет обеспечить лучшее окно синхронизации, которое обеспечивает более высокие частоты передачи.

Возвращаясь к фиг. 6, здесь представлен вариант осуществления конструкции SoC, в соответствии с вариантом осуществления. В качестве конкретного иллюстративного примера, SoC 2000 включен в оборудование пользователя (UE). В одном варианте осуществления UE называется любое устройство, предназначенное для использования конечным пользователем для обмена данными, такое как портативный телефон, смартфон, планшетный компьютер, ультратонкий ноутбук, ноутбук с широкополосным адаптером или любое другое аналогичное устройство передачи данных. Часто UE соединяется с базовой станцией или узлом, который потенциально соответствует по своей сути мобильной станции (MS) в сети GSM.

Здесь SoC 2000 включает в себя 2 ядра - 2006 и 2007. Аналогично представленному выше описанию, ядра 2006 и 2007 могут соответствовать архитектуре набора инструкций, такой как процессор на основе Intel® ™ Architecture Core™, процессор Advanced Micro Devices, Inc. (AMD), процессор на основе MIPS, конструкция процессора на основе ARM, или их заказчика, а также их лицензиаты или последователи. Ядра 2006 и 2007 соединены с управлением 2008 кэш, которое ассоциировано с модулем 2009 интерфейса шины и кэш 2010 L2 для обмена данными с другими частями системы 2000. Взаимное соединение 2010 включает в себя взаимное соединение на кристалле, такое как IOSF, AMBA или другое взаимное соединение, описанное выше, которое потенциально воплощает один или больше описанных здесь аспектов.

Взаимное соединение 2010 обеспечивает каналы передачи данных с другими компонентами, такими как модуль 2030 идентичности абонента (SIM) для формирования интерфейса с SIM-картой, ROM 2035 начальной загрузки, для содержания) загрузочного кода для исполнения ядрами 2006 и 2007, для инициализации и загрузки SOC 2000, контроллер 2040 SDRAM для формирования интерфейса с внешним запоминающим устройством (например, DRAM 2060), контроллер 2045 флэш-памяти для формирования интерфейса с энергонезависимым запоминающим устройством (например, Flash 2065), периферийный контроллер 2050 (например, последовательного периферийного интерфейса) для формирования интерфейса с периферийными устройствами, видеокодеки 2020 и видеоинтерфейс 2025 для отображения и приема вводимых данных (например, вводимых через прикосновение), GPU 2015 предназначенное для выполнения расчетов, связанных с графикой, и т.д. В любой из этих интерфейсов могут быть встроены аспекты, описанные здесь.

Кроме того, в системе представлены периферийные устройства для передачи данных, такие как модуль 2070 Bluetooth, 3G модем 2075, GPS 2080 и WiFi 2085. Также в систему включен контроллер 2055 питания. Следует отметить, как упомянуто выше, UE включает в себя радиомодуль для передачи данных. В результате, требуются не все из этих периферийных модулей передачи данных. Однако в UE должна быть включена некоторая форма радиомодуля для внешней передачи данных.

В различных вариантах осуществления в, по меньшей мере, части схем одного или больше устройств, соединенных через заданное взаимное соединение, может выполняться управление питанием, (например, управление подачей питания), когда конфигурацией такого устройства определяется, что такая схема не используется. В качестве примера описанных здесь вариантов осуществления, схема, ассоциированная с одним или больше виртуальными каналами, которые обеспечивают передачу данных через взаимное соединение, может быть установлена в состоянии отключенного питания (например, без подачи рабочего напряжения в эту схему), когда определяют по конфигурации системы, что такие виртуальные каналы не будут использоваться для передачи данных. Конечно, варианты осуществления не ограничены этим примером, и описанные здесь технологии в равной степени применяются для управления питанием другой схемы.

На фиг. 7 показана блок-схема системы в соответствии с вариантом осуществления настоящего изобретения. Как показано на фиг. 7, система 700 представляет собой воплощение системы PCIe™, в которой различные устройства соединены с переключателем 720. Каждое из устройств соединено с переключателем 720 с помощью соответствующего соединения (соответственно, соединения 1 - 4). Следует отметить, что каждое из соединений, в варианте осуществления, может иметь разные характеристики и рабочие параметры.

В качестве примеров, устройства 730, 740 и 750 могут представлять собой разные типы периферийных устройств. В качестве одного такого примера, устройство 730 может представлять собой устройство графического ускорителя, устройство 740 может представлять собой устройство накопитель, и устройство 750 может представлять собой другой тип портативного устройства, например, устройства захвата. Переключатель 720 дополнительно соединяется с корневым комплексом 710 с помощью другого соединения (соединение 4). В качестве одного пример, корневые комплексы 710 могут представлять собой основным процессор обработки данных системы, такой как многоядерный процессор. Конечно, возможны другие примеры комплексов.

В частности, обращаясь к соединению между переключателем 720 и устройством 730, следует отметить, что различные количества виртуальных каналов предусмотрены в разных устройствах.

Как можно видеть, переключатель 720 включает в себя 8 виртуальных каналов в этот примере, каждый из которых соответствует аппаратному буферу в интерфейсе 725 соединения. Вместо этого, устройство 730 включает в себя только 4 виртуальных канала и, таким образом, имеет интерфейс 735 соединения, включающий в себя только 4 аппаратных буфера. Поскольку эти устройства имеют разные количества виртуальных каналов и буферов, по меньшей мере, некоторые из буферов в пределах интерфейса 725 соединения переключателя 720 не будут использоваться. В соответствии с этим, используя вариант осуществления настоящего изобретения, эти буферы могут быть отключены в аппаратных средствах таким образом, что исключается потребление энергии для этих буферов. Хотя данные конкретные варианты воплощения в варианте осуществления показаны на фиг. 7, следует понимать, что возможно много вариаций.

Далее, на фиг. 8, показана блок-схема последовательности операций способа конфигурации, в соответствии с вариантом осуществления настоящего изобретения. В конкретном варианте осуществления способ 800 может быть выполнен во время инициализации устройства логикой конфигурации устройств, соединенных вместе через соединение. Кроме того, способ может также быть выполнен динамически всякий раз, когда происходит какое-либо изменение в устройстве или в аппаратных средствах, соединенных с устройством через соединение. Например, если новое устройство соединено с конечной точкой, то соединение будет переобучено, и логика конфигурации будет повторно назначать некоторые определенные значения, соответственно. Со ссылкой на фиг. 8, способ 800 начинается путем считывания расширенного поля подсчета VC накопителя конфигурации, как для локального устройства или конечной точки, так и для удаленного устройства или конечной точки, расположенных на дальнем конце соединения, которое соединяет эти 2 устройства (блок 810 и блок 820). В одном варианте осуществления такое поле расширенного подсчета VC может быть сохранено в накопителе соответствующего устройства, например, в пределах пространство конфигураций PCIe™. Предположим, что с целью описания, локальное устройство (конечная точка 1) соответствует переключателю 720 на фиг. 7, и что удаленное устройство (конечная точка 2) соответствует устройству 730 на фиг. 7.

В указанном выше представлении (с 8 виртуальными каналами и буферами, присутствующими в переключателе 720, и 4 виртуальными каналами и буферами, присутствующими в устройстве 730) значение, возвращаемое для расширенного поля подсчета VC из устройства 720 переключателя, будет равно 8, и значение, возвращаемое из устройства 730, будет равно 4. Более конкретно, в варианте осуществления, в котором это поле подсчета представляет собой 3-битное поле, значение ноль соответствует одному поддерживаемому виртуальному каналу (например, VC0), и значения 1 - 7 этого 3-битного двоичного значения соответствуют дополнительному количеству поддерживаемых VC. Таким образом, в этом варианте осуществления, расширенное поле подсчета VC для переключателя 720 имеет значение 111b, и расширенное поле подсчета VC для устройства 730 имеет значение подсчета 011b. Конечно, возможны другие представления.

Также, со ссылкой на фиг. 8, дальнейшее управление переходит к ромбу 830, где может быть определено, превышает ли величина подсчета VC для локального устройства величину подсчета VC для удаленного устройства. Если это так, управление переходит в блок 835, где максимальное значение VC соединения может быть установлено, как расширенное поле подсчета VC из удаленного устройства. Следует отметить, что такое максимальное значение подсчета VC или значение ID VC соответствуют минимальному значению для расширенного поля подсчета VC соединенных конечных точек. И, таким образом, в данном случае, такое максимальное значение VC соединения установлено, как значение 011b.

Однако, если это не так, управление переходит, вместо этого, из ромба 830 к ромбу 840, где может быть определено, равна ли величина подсчета VC для локального устройства величине подсчета VC удаленного устройства. Если это так, управление переходит в блок 845, где максимальное значение VC соединения может быть установлено, как расширенное поле подсчета VC из локального устройства. В противном случае, управление переходит к ромбу 850, где определяют, является ли величина подсчета VC локального устройства меньшей, чем величина подсчета VC для удаленного устройства. В этом случае управление переходит в блок 855, где максимальное значение VC соединения может быть установлено, как расширенное поле величины подсчета VC из локального устройства.

Независимо от максимального значения VC соединения, установленного в одном из блоков 835, 845 и 855, управление переходит к следующему блоку 860, где может осуществляться доступ к накопителю конфигураций, такому как накопитель таблицы, имеющий эти максимальные значениям VC соединения. Более конкретно, в результате доступа к такому другому представлению в таблице может быть получено выбранное максимальное значение VC соединения. Как будет далее представлено со ссылкой на фиг. 9A, таблица может включать в себя множество входов, каждый из которых предоставляет 3-битное представление максимального значения соединения VC и соответствующее 8-битное представление того же самого значения. И, таким образом, управление переходит в блок 870, где могут быть получены индивидуальные биты входа, доступ к которому выполняется, где каждый бит соответствует одному из доступного количества виртуальных каналов и представляет доступное состояние соответствующего буфера аппаратных средств. Таким образом, в примере значение логической единицы обозначает активный буфер, и, соответственно, соответствующее подключенное состояние, и значение логического нуля обозначает неактивный буфер и, соответственно, соответствующее отключенное состояние. Конечно, возможны другие представления.

Далее, на фиг. 9A, представлена блок-схема накопителя конфигурации, в соответствии с вариантом осуществления. Как показано на фиг. 9A, накопитель 900 может присутствовать в требуемом местоположении в пределах системы, например, в отдельном энергонезависимом накопителе. Или копия информации в накопителе 900 конфигурации может присутствовать, например, в пространстве конфигураций каждого из устройств системы. Также, в дополнительных вариантах осуществления эта информация может сохраняться в еще одном местоположении, таком как внешние регистры или постоянное запоминающее устройство. Как можно видеть, накопитель 900 включает в себя множество входов 9100 - 910n. Каждый вход включает в себя первое поле 920 и второе поле 930. Первое поле 920 может соответствовать максимальному значению соединения VC и, таким образом, используется, как адресуемое средство для доступа к выбранному входу накопителя 900. В свою очередь, второе поле 930 предоставляет соответствующее 8-битное представление максимального значения VC соединения. В варианте осуществления 8-битное значение, отображаемое ID VC, может быть таким, что каждый бит соответствует буферу виртуального канала этой конечной точки или другой трассе, отображающей конечную точку; например, бит 0 отображается на VC0, бит 1 отображается на VC1 и, наконец, бит 7 отображается на VC7. В этом варианте осуществления двоичная единица 1 обозначает состояние "включено", тогда как 0 обозначает "отключено". В варианте осуществления эти состояния затем выводят в схему регулирования напряжения каждого буфера для управления подачей рабочего напряжения в буфер (или, в качестве альтернативы, для не подачи рабочего напряжения).

Далее, на фиг. 9B показаны выбранный вход 910x, полученный из таблицы, и его использование для управления подачей рабочего напряжения в соответствующие буферы аппаратных средств устройства. Более конкретно, на фиг. 9B показан набор вентилей 9500 - 950n "И". Каждый из этих логических вентилей выполнен с возможностью приема соответствующего бита из выбранного входа и соответствующего рабочего напряжения, например, полученного из регулятора напряжения за пределами кристалла. Конечно, рабочее напряжение может быть получено, вместо этого, из других местоположений либо на кристалле, или вне кристалла. Когда заданный бит представляет собой логически высокое значение, вентиль "И" является активным, и, таким образом, рабочее напряжение подают в соответствующий аппаратный буфер. В противном случае, вентиль "И" не пропускает рабочее напряжение в буфер, и буфер отключается во время нормальной работы, таким образом, улучшая потребление энергии. Хотя в данном варианте осуществления на фиг. 9B показан высокий уровень, следует понимать, что возможны вариации.

Далее, на фиг. 10, показана блок-схема части системы, в соответствии с вариантом осуществления. Как показано на фиг. 10, система 1000 может включать в себя различные компоненты. Для представленного здесь описания показаны просто два компонента, а именно, устройство 1010, которое может представлять собой интегральную схему любого типа, соединенную с другой схемой (не показана) через соединение 1005, и энергонезависимый накопитель 1080, соединенный с соединением 1090. В представленном варианте осуществления соединение 1005 может представлять собой PCIe™, имеющее однонаправленные последовательные соединения в направлении передачи и в направлении приема.

Устройство 1010 может представлять собой устройство любого типа, включающее в себя корневой комплекс, переключатель, периферийное устройство или так далее. Только части устройства 1010 показаны для простоты иллюстрации. Более конкретно, предусмотрен набор приемных буферов 10250-1025n,.

Эти каждый из этих аппаратных буферов может соответствовать заданному виртуальному каналу VC0-VCn.

Кроме того, также предусмотрен набор буферов 1020o-1020n передачи, и снова, здесь каждый буфер ассоциирован с конкретным виртуальным каналом. Следует отметить, что различные классы трафика (TC) могут быть назначены для маршрутизации через данные VC и соответствующие аппаратные буферы. Используя вариант осуществления настоящего изобретения, рабочее напряжение подают только во включенные из этих аппаратных буферов виртуального канала через вентильную логику 1060, которая, в свою очередь, принимает информацию управления из логики 1050 конфигурации, детали которой дополнительно описаны ниже.

Также, со ссылкой на устройство 1010, буферы 1020 и 1025 могут связываться с другой схемой физического уровня (не показана для простоты иллюстрации на фиг. 10. Исходя из этого, обмен данными может продолжиться с логикой 1030 соединения для выполнения различной обработки уровня соединения. После этого, обмен данными может продолжиться с логикой 1035 формирования транзакций, которая может выполнять обработку уровня транзакции.

После этого, обмен данными может происходить с логикой 1040 ядра, которая может представлять собой основную логическую схему устройства 1010. Например, в контексте многоядерного процессора, логика 1040 ядра может представлять собой одно или больше ядер процессора или других модулей обработки. В качестве другого примера, где устройство 1010 представляет собой устройство графического ускорителя, логика 1040 ядра может представлять собой модуль обработки графики.

Также, на фиг. 10 показана логика 1050 конфигурации, которая может быть выполнена как аппаратные средства, программное средство и/или встроенное программное обеспечение (или используя их комбинации) для выполнения операций конфигурации, когда подают питание в систему 1000, когда выполняют перезагрузку устройства 1010, или когда происходят другие динамические изменения во время работы. В варианте осуществления логика 1050 конфигурации может включать в себя логику для выполнения описанного здесь управления администрированием питанием. Таким образом, в варианте осуществления, показанном на фиг. 10, логика 1050 конфигурации включает в себя логику 1055 администрирования питанием, которая может быть выполнена с возможностью исполнения способа, такого как описанный выше способ 800.

С этой целью, логика 1050 конфигурации может связываться с накопителем 1070 конфигурации. В различных вариантах осуществления накопитель 1070 конфигурации может представлять собой энергонезависимый накопитель устройства 1010, которое включает в себя пространство сохранения конфигурации PCIe™. Среди различной информации конфигурации, сохраненной здесь, находится расширенное поле 1075 подсчета VC, такое, как описано здесь. Следует, конечно, понимать, что дополнительная информация конфигурации также сохранена в накопителе 1070.

В конкретном варианте осуществления может быть предусмотрена таблица отображения, которая ассоциирует 3-битную максимальную величину подсчета VC с соответствующей 8-битной величиной. Конечно, в зависимости от количества возможных виртуальных каналов, буферов аппаратных средств или других схем, которыми следует управлять, количество кодированных битов и индивидуальных представлений бита может изменяться. В представленном варианте осуществления, отдельный энергонезависимый накопитель 1080 может включать в себя таблицу 1085 отображения. Таблица 1085 отображения может, таким образом, ассоциировать максимальную величину подсчета VC с отображениями трасс. Другими словами, обозначение максимального количества поддерживаемых виртуальных каналов может быть отображено на соответствующий набор индикаторов включения, которые могут использоваться для управления подавать или нет рабочее напряжение в один или больше аппаратных буферов, каждый из которых ассоциирован с соответствующим виртуальным каналом. Конечно, при описании этого варианта осуществления, под управлением аппаратными буферами на основе включенных виртуальных каналов следует понимать, что можно аналогично управлять дополнительными аппаратными средствами в устройстве. В качестве примера, такие дополнительные аппаратные средства, которыми можно управлять на основе из трассы в трассу или основе виртуального канала, могут включать в себя видеокарту, дочернюю карту, такую как карта USB-в-PCIe™ или SATA-в-PCIe™, или другие такие устройства.

Варианты осуществления, таким образом, обеспечивается включение питания в неиспользуемых аппаратных средствах, таких как аппаратные буферы VC под управлением конфигурации, например, логикой конфигурации. Таким образом, питание системы может быть уменьшено, поскольку питание получают только аппаратные средства, которые фактически используются.

Следующие примеры относятся к дополнительным вариантам осуществления.

В примере устройство содержит: множество аппаратных буферов, каждый из которых содержит информацию, ассоциированную с одним или больше виртуальными каналами; логику конфигурации для определения идентификатора, соответствующего максимальному количеству виртуальных каналов, которые обычно поддерживаются первым устройством и вторым устройством, соединенными через соединение, и для получения значения управления на основе идентификатора; и вентильную логику для подачи рабочего напряжения в соответствующее множество аппаратных буферов на основе значения управления.

Вентильная логика может быть выполнена с возможностью предотвращения подачи рабочего напряжения, по меньшей мере, в один из множества аппаратных буферов, когда максимальное количество виртуальных каналов меньше, чем количество аппаратных буферов, в варианте осуществления.

В примере логика конфигурации должна определять максимальное количество виртуальных каналов на основе первой величины подсчета виртуального канала, ассоциированной с первым устройством, и второй величины подсчета виртуального канала, ассоциированной со вторым устройством.

В примере логика конфигурации должна получать первую величину подсчета виртуального канала из области подсчета виртуального канала накопителя конфигурации первого устройства и получать вторую величину подсчета виртуального канала из поля подсчета виртуального канала накопителя конфигурации второго устройства.

В одном примере вентильная логика включает в себя множество логических схем, каждая из которых должна принимать бит, значение управления и рабочее напряжение и должна предоставлять рабочее напряжение в один из множества аппаратных буферов на основе значение бита.

В одном примере энергонезависимый накопитель, включающий в себя таблицу отображения, имеющую множество входов, каждый из которых должен ассоциировать идентификатор со значением управления, может быть соединен с устройством. В одном варианте осуществления логика конфигурации должна получать значение управления из входа таблицы отображения, доступ к которой выполняется, используя идентификатор. Значение управления может включать в себя множество битов, каждый из которых ассоциирован с одним из множества аппаратных буферов, каждый из битов первого состояния должен обозначать, что ассоциированный аппаратный буфер должен быть включен, и второго состояния, для обозначения, что ассоциированный аппаратный буфер должен быть отключен.

В примере первое устройство содержит накопитель конфигурации, предназначенный для сохранения величины подсчета максимального количества виртуальных каналов, поддерживаемых первым устройством, и для дополнительного сохранения копии одного или больше входов таблицы отображения. В варианте осуществления энергонезависимый накопитель представляет собой отдельный компонент от первого устройства и соединен с первым устройством через второе соединение.

Следует отметить, что упомянутое выше устройство может быть воплощено, используя различные средства.

В одном примере процессор содержит систему на кристалле (SoC), встроенную в устройство, включаемое прикосновением оборудования пользователя.

В другом примере система содержит дисплей и запоминающее устройство, и включает в себя устройство, в соответствии с одним или больше представленными выше примерами.

В другом примере способ содержит: определяют общее количество виртуальных каналов, которые могут поддерживаться первой конечной точкой и второй конечной точкой, соединенными через соединение; выполняют доступ к накопителю, используя общее количество виртуальных каналов для получения установки управления, соответствующей общему количеству виртуальных каналов; и подают рабочее напряжение к выбранным первым аппаратным буферам первой конечной точки и выбранным вторым аппаратным буферам второй конечной точки на основе установок управления.

В примере предоставление рабочего напряжение включает в себя предоставление рабочего напряжения в выбранные первые и вторые аппаратные буферы, и не предоставление рабочего напряжения в не выбранные первые аппаратные буферы и не выбранные вторые аппаратные буферы.

В примере способ дополнительно содержит: передают данные между первой конечной точкой и второй конечной точкой, используя выбранные первые аппаратные буферы и выбранные вторые аппаратные буферы.

В примере способ дополнительно содержит: осуществляют доступ во время конфигурирования соединения, к накопителю, используя общее количество виртуальных каналов, в котором накопитель выполнен отдельным от первой и второй конечных точек, и включает в себя множество входов, каждый из которых содержит общее количество виртуальных каналов и установок управления.

В примере способ дополнительно содержит, в ответ на изменение конфигурации соединения: определяют второе общее количество виртуальных каналов, которые могут поддерживаться первой и второй конечными точками; осуществляют доступ к накопителю, используя второе общее количество виртуальных каналов для получения второй установки управления; и предоставляют рабочее напряжение в другие одни из первых аппаратных буферов, кроме выбранных первых аппаратных буферов, и в другие одни из вторых аппаратных буферов, кроме выбранных вторых аппаратных буферов, на основе второй установки управления.

В другом примере считываемый компьютером носитель информации включает себя инструкции, предназначенные для выполнения способа по любому из представленных выше примеров.

В другом примере устройство содержит средство для выполнения способа по любому из представленных выше примеров.

В еще одном примере устройство содержит: первый интерфейс соединения, предназначенный для формирования интерфейса устройства с соединением, включенным между устройством и вторым устройством, первый интерфейс соединения, включающий в себя множество независимых цепей, каждая из которых должна передавать данные соответствующего класса трафика; первый накопитель конфигурации, предназначенный для сохранения максимального поддерживаемого значения, соответствующего количеству множества независимых цепей; логику конфигурации, предназначенную для определения максимального значения соединения, соответствующего минимальному из максимального поддерживаемого значения, содержащегося в первом накопителе конфигурации, и максимальному поддерживаемому значению, содержащемуся во втором накопителе конфигурации второго устройства, и для получения разных представлений максимального значения соединения; и схему управления, выполненную с возможностью включения первого набора из множества независимых цепей, и отключения второго набора из множества независимых цепей, в ответ на разные представления, когда максимальное значение соединения меньше, чем количество множества независимых цепей.

В примере максимальное поддерживаемое значение, содержащееся в первом накопителе конфигурации, дополнительно соответствует виртуальному значению величины подсчета канала для устройства.

В одном примере энергонезависимый накопитель, соединенный с устройством, включает в себя таблицу отображения, имеющую множество входов, каждый из которых ассоциирует максимальное значение соединения с разными представлениями максимального значения соединения. Доступ к таблице отображения может осуществляться, используя максимальное значение соединения, определенное логикой конфигурации.

В примере разное представление включает в себя множество битов, каждый из которых ассоциирован с одной из множества независимых цепей, и каждый из битов первого состояния предназначен для обозначения, что должна быть включена ассоциированная независимая цепь, и каждый из битов второго состояния предназначен для обозначения, что ассоциированная независимая цепь должна быть отключена.

В примере схема управления включает в себя множество логических цепей, каждая из которых должна принимать бит из множества битов разного представления и рабочее напряжение из регулятора напряжения, и предоставлять рабочее напряжение в одну из множества независимых цепей на основе значения бита.

В примере множества независимых цепей каждая содержит, аппаратный буфер, ассоциированный с виртуальным каналом.

В еще одном примере система содержит: первое устройство, включающее в себя первый интерфейс соединения, имеющий первое множество аппаратных буферов, каждый из которых предназначен для сохранения информации, ассоциированной с одним или больше виртуальными каналами, и второе устройство, соединенное с первым устройством через соединение. В варианте осуществления второе устройство включает в себя: второй интерфейс соединения, имеющий второе множество аппаратных буферов, каждый из которых предназначен для сохранения информации, ассоциированной с одним или больше из виртуальных каналов, где второе множества аппаратных буферов превышает первое множество аппаратных буферов; контроллер, предназначенный для определения максимального количества виртуальных каналов, совместно поддерживаемых первым и вторым устройствами, максимальное количество, соответствующее количеству множества первых аппаратных буферов, и используется для получения значения управления на основе максимального количества; и вентильную логику, предназначенную для включения меньше, чем всех из множества вторых аппаратных буферов в ответ на значение управления.

В примере первое устройство содержит первый накопитель конфигурации, включающий в себя первую максимальную величину подсчета виртуального канала, и второе устройство содержит второй накопитель конфигурации, включающий в себя вторую максимальную величину подсчета виртуального канала.

В примере контроллер должен определять максимальное число совместно поддерживаемых виртуальных каналов, используя первую максимальную величину подсчета виртуального канала и вторую максимальную величину подсчета виртуального канала.

В примере энергонезависимый накопитель включает в себя таблицу отображения, имеющую множество входов, каждый из которых предназначен для ассоциирования максимального числа совместно поддерживаемых виртуальных каналов.

В примере контроллер может получать значение управления из входа таблицы отображения, доступ к которой осуществляется, используя определенное максимальное число совместно поддерживаемых виртуальных каналов. Значение управления включает в себя множество битов, каждый из которых ассоциирован с одним из второго множества аппаратных буферов, каждый из битов первого состояния должен обозначать, что ассоциированный второй аппаратный буфер должен быть включен, и второго состояния, для обозначения, что ассоциированный второй аппаратный буфер должен быть отключен, в варианте осуществления.

В примере вентильная логика включает в себя множество логических цепей, каждая из которых предназначена для приема битов, значения управления и рабочего напряжения и для предоставления рабочего напряжения в один из множества вторых аппаратных буферов на основе значения этого бита.

Следует понимать, что возможны различные комбинации представленных выше примеров.

Варианты осуществления могут использоваться во множестве разных типов систем. Например, в одном варианте осуществления устройство передачи данных может быть выполнено с возможностью выполнения различных описанных здесь способов и технологий. Конечно, объем настоящего изобретения не ограничен устройством передачи данных, и вместо этого другие варианты осуществления могут быть направлены на другие типы устройства для обработки инструкций или один или больше считываемых устройством носителей информации, включающих в себя инструкции, которые, в ответ на их исполнение вычислительным устройством, обеспечивает выполнение описанных здесь устройством одного или больше способов и технологий.

Варианты осуществления могут быть воплощены в коде и могут быть сохранены на энергонезависимом накопителе информации, на котором содержатся инструкции, которые могут использоваться для программирования системы для выполнения инструкций. Носитель информации может включать в себя, но не ограничен этим, любой тип диска, включая в себя гибкие диски, оптические диски, твердотельные приводы (SSD), постоянное запоминающее устройство на компактных дисках (CD-ROM), компактные диски с возможностью перезаписи (CD-RW) и магнитооптические диски, полупроводниковые устройства, такие как постоянные запоминающие устройства (ROM), оперативные запоминающее устройства (RAM), такие как динамические оперативные запоминающие устройства (DRAM), статические оперативные запоминающие устройства (SRAM), стираемые программируемые постоянные запоминающие устройства (EPROM), запоминающие устройства флэш, электрически стираемые программируемые постоянные запоминающие устройства (EEPROM), магнитные или оптические карты, или любой другой тип носителя, пригодный для сохранения электронных инструкций.

В то время как настоящее изобретение было описано в отношении ограниченного количества вариантов осуществления, для специалиста в данной области техники будут понятные различные модификации и вариации на их основе. Предполагается, что приложенная формула изобретения охватывает все такие модификации и вариации, поскольку они попадают в пределы истинной сущности и объема этого настоящего изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ, УСТРОЙСТВО И СИСТЕМА УМЕНЬШЕНИЯ ВРЕМЕНИ ВОЗОБНОВЛЕНИЯ РАБОТЫ ДЛЯ КОРНЕВЫХ ПОРТОВ И КОНЕЧНЫХ ТОЧЕК, ИНТЕГРИРОВАННЫХ В КОРНЕВЫЕ ПОРТЫ | 2014 |

|

RU2645596C1 |

| СПОСОБ, УСТРОЙСТВО И СИСТЕМА УМЕНЬШЕНИЯ ВРЕМЕНИ ВОЗОБНОВЛЕНИЯ РАБОТЫ ДЛЯ КОРНЕВЫХ ПОРТОВ И КОНЕЧНЫХ ТОЧЕК, ИНТЕГРИРОВАННЫХ В КОРНЕВЫЕ ПОРТЫ | 2014 |

|

RU2586022C2 |

| ПРЕДСТАВЛЕНИЕ ФИЛЬТРАЦИИ НАБЛЮДЕНИЯ, АССОЦИИРОВАННОЙ С БУФЕРОМ ДАННЫХ | 2013 |

|

RU2608000C2 |

| УСТРОЙСТВО, СИСТЕМА И СПОСОБ УЛУЧШЕНИЯ КОРРЕКЦИИ ЗАДАВАЕМЫМ АППАРАТУРОЙ АЛГОРИТМОМ | 2014 |

|

RU2580404C2 |

| ФИЗИЧЕСКИЙ УРОВЕНЬ ВЫСОКОПРОИЗВОДИТЕЛЬНОГО МЕЖСОЕДИНЕНИЯ | 2013 |

|

RU2599971C2 |

| НЕЧУВСТВИТЕЛЬНЫЙ К ЗАДЕРЖКЕ БУФЕР ТРАНЗАКЦИИ ДЛЯ СВЯЗИ С КВИТИРОВАНИЕМ | 2014 |

|

RU2598594C2 |

| ФИЗИЧЕСКИЙ УРОВЕНЬ ВЫСОКОПРОИЗВОДИТЕЛЬНОГО МЕЖСОЕДИНЕНИЯ | 2013 |

|

RU2579140C1 |

| УСОВЕРШЕНСТВОВАНИЕ ИНТЕРФЕЙСА PCI EXPRESS | 2013 |

|

RU2645288C2 |

| НЕОГРАНИЧЕННАЯ ТРАНЗАКЦИОННАЯ ПАМЯТЬ С ГАРАНТИЯМИ ПРОДВИЖЕНИЯ ПРИ ПЕРЕСЫЛКЕ, ИСПОЛЬЗУЯ АППАРАТНУЮ ГЛОБАЛЬНУЮ БЛОКИРОВКУ | 2014 |

|

RU2597506C2 |

| ЗВЕНО СВЯЗИ МНОГОКРИСТАЛЬНОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ | 2013 |

|

RU2656732C2 |

Группа изобретений относится к средствам администрирования питания. Технический результат – создание энергосберегающих канальных интерфейсов. Для этого предложено устройство управления питанием канальных интерфейсов, включающее в себя: множество аппаратных буферов, каждый из которых содержит информацию, ассоциированную с виртуальными каналами; логическую схему конфигурации для определения идентификатора, соответствующего максимальному количеству виртуальных каналов, которые обычно поддерживаются первым устройством и вторым устройством, и для получения значения управления и вентильную логическую схему для подачи напряжения в аппаратные буферы, в котором вентильная логическая схема выполнена с возможностью предотвращения подачи рабочего напряжения по меньшей мере в один из множества аппаратных буферов, когда максимальное количество виртуальных каналов меньше, чем количество аппаратных буферов. 4 н. и 23 з.п. ф-лы, 11 ил.

1. Устройство управления питанием канальных интерфейсов, включающее в себя:

множество аппаратных буферов, каждый из которых содержит информацию, ассоциированную с одним или больше виртуальными каналами;

логическую схему конфигурации для определения идентификатора, соответствующего максимальному количеству виртуальных каналов, которые обычно поддерживаются первым устройством и вторым устройством, соединенными через соединение, и для получения значения управления на основе идентификатора; и

вентильную логическую схему для подачи рабочего напряжения в соответствующее множество аппаратных буферов на основе значения управления,

в котором вентильная логическая схема выполнена с возможностью предотвращения подачи рабочего напряжения по меньшей мере в один из множества аппаратных буферов, когда максимальное количество виртуальных каналов меньше, чем количество аппаратных буферов.

2. Устройство по п. 1, в котором логическая схема конфигурации выполнена с возможностью определять максимальное количество виртуальных каналов на основе первой величины подсчета виртуального канала, ассоциированной с первым устройством, и второй величины подсчета виртуального канала, ассоциированной со вторым устройством.

3. Устройство по п. 2, в котором логическая схема конфигурации выполнена с возможностью получать первую величину подсчета виртуального канала из области подсчета виртуального канала накопителя конфигурации первого устройства и получать вторую величину подсчета виртуального канала из поля подсчета виртуального канала накопителя конфигурации второго устройства.

4. Устройство по п. 1, в котором вентильная логическая схема включает в себя множество логических схем, каждая из которых выполнена с возможностью принимать бит, значение управления и рабочее напряжение и выполнена с возможностью предоставлять рабочее напряжение в один из множества аппаратных буферов на основе значение бита.