ОБЛАСТЬ ТЕХНИКИ

Техническое решение относится к области вычислительной техники, в частности к способам обработки видеосигнала, и может применяться в системах виртуальной и дополненной реальности (AR/VR) для снижения задержки системы визуализации.

УРОВЕНЬ ТЕХНИКИ

Проблема задержки отображения видеосигнала является актуальной проблемой при реализации большинства технологий AR/VR, основанных на системах трекинга. В системах AR/VR с трекингом виртуальная среда изменяется в ответ на движение пользователя. Величина задержки – это полное время между движением пользователя и соответствующим изменением изображения на дисплее.

Особенности зрительного восприятия трехмерных объектов приводят к тому, что запаздывание реакции системы на изменение положения пользователя воспринимается не как временное явление, а как явление пространственное, то есть мозг не воспринимает задержку системы, но видит, как объект кубической формы изменяет свои пропорции во время движения наблюдателя, и реалистичное восприятие достигается лишь в моменты, когда пользователь неподвижен в течение времени, равного или большего времени задержки системы.

Вследствие явного несоответствия зрительной информации и информации о положении пользователя, поступающей от вестибулярного аппарата, задержка является наиболее частой причиной проявления у пользователей симптомов морской болезни: головокружения, тошноты, слабости.

Выбор устройства отображения прямо влияет на величину полной задержки отображения системы, поскольку большинство современных дисплеев, в отличие от устаревших ЭЛТ-дисплеев, выполняют буферизацию и дополнительную обработку изображения для улучшения его качества, а это приводит к задержке вывода, зачастую весьма существенной.

Таким образом, получается, что для серийных телевизионных ЖК-дисплеев реальная задержка отображения значительно выше, чем минимальное время вывода изображения на экран, обусловленное физическими характеристиками экрана. Так, для ЖК-дисплеев с временем отклика в 2 мс, реальная задержка отображения составляет 20-140 мс за счет дополнительной обработки изображения на управляющей панели экрана.

Дополнительная обработка для телевизионных панелей призвана улучшить качество входного сигнала и актуальна в ситуации, когда неизвестно качество входного телевизионного сигнала. Однако для AR/VR-системы, в которой система рендеринга на графическом сервере изначально готовит изображение высокого качества, дополнительная обработка на плате управления экраном являются избыточными.

Помимо большой задержки отображения серьезным ограничением серийных ЖК-дисплеев большого формата (от 32’’ и выше) является низкое разрешение в формате 3D (режим 120 Гц).

На сегодняшний день протокол HDMI позволяет передавать изображение 1280х720 (HD) с частотой 120 кадров в секунду (60 кадров на глаз). Для вывода изображения 1920х1080 (FullHD) поддерживается режим 48 Гц (24 кадра на глаз): подобный режим является приемлемым при просмотре фильмов, однако для динамических сцен при перемещении пользователя относительно экрана является некомфортным. Стоит отметить, что спецификация HDMI описывает также формат передачи 1920х1080@120fps, но этот формат относится к необязательным и его поддержка не встречается среди серийных телевизионных ЖК-панелей.

Авторами изобретения разработана плата обработки видеосигнала для ЖК-панели с околонулевой задержкой, с поддержкой разрешения 1920х1080 (FullHD) в режиме 120 Гц. Околонулевая задержка обработки достигается за счет применения высокоскоростных параллельных алгоритмов обработки сигнала с использованием ПЛИС.

Из патента US 5546530A известен способ и устройство рендеринга изображений с использованием параллельной обработки. Данное решение предлагает рендеринг и обработку посредством деления целого изображения. Рендеринг изображения на данном устройстве происходит за счет распараллеливания обработки информации по процессорам, после чего пиксели с каждого процессора направляются в отдельный буфер для дальнейшего формирования одного целого и подачи на выход.

Из патента US 20080018789 известно портативное устройство, интегрируемое с функцией внешнего видеосигнала. Данное устройство включает в себя интерфейс видеоввода, дисплей, чип отображения и контроллер. Интерфейс видеоввода получает внешний видеосигнал, а чип отображения выдает внутреннее видео. Контроллер включает в себя первый интерфейс ввода, второй интерфейс ввода и интерфейс вывода. Данное устройство включает в себя дополнительную обработку пикселей и буферизацию, что приводит к увеличению задержки.

В приведенных выше примерах используется постобработка изображения, большой объем буферизации, что, несмотря на использование распараллеливания в некоторых из них, приводит к увеличению задержки.

СУЩНОСТЬ ТЕХНИЧЕСКОГО РЕШЕНИЯ

Задачей, на решение которой направлено заявленное техническое решение, является обработка видеосигнала с минимальной задержкой.

Технический результат, обеспечиваемый заявленным техническим решением, заключается в снижении величины задержки при выводе видеосигнала на экран.

В общем виде, задача, на решение которой направленно заявленное техническое решение, достигается посредством применения алгоритмов FIFO, запрограммированных на ПЛИС, и чипов, принимающих сигнал с разъема HDMI и осуществляющих буферизацию менее одной строки пикселей, что позволяет снизить величину задержки.

ПЛИС по системе FIFO1 и FIFO2 выводит видеосигнал через LVDS-трансмиттер на экран порционно для каждой половины экрана, не объединяясь, что также позволяет снизить величину задержки.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Признаки и преимущества заявленного технического решения станут очевидными из приводимого ниже подробного описания и прилагаемых чертежей, на которых:

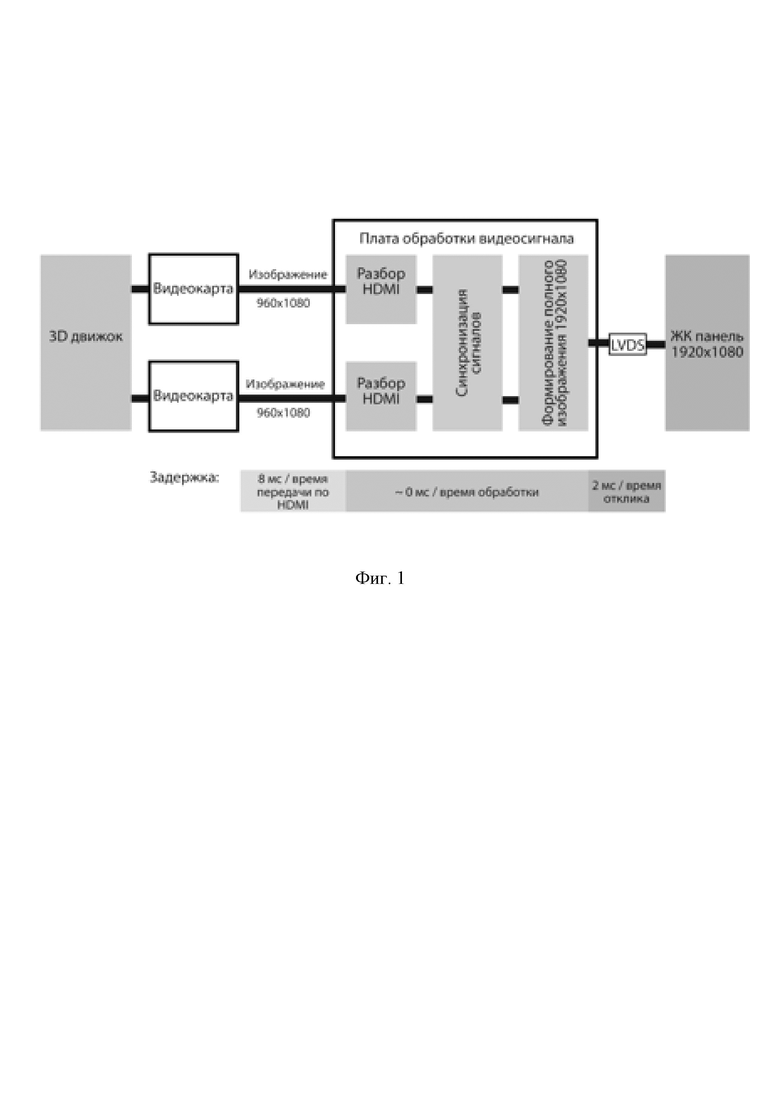

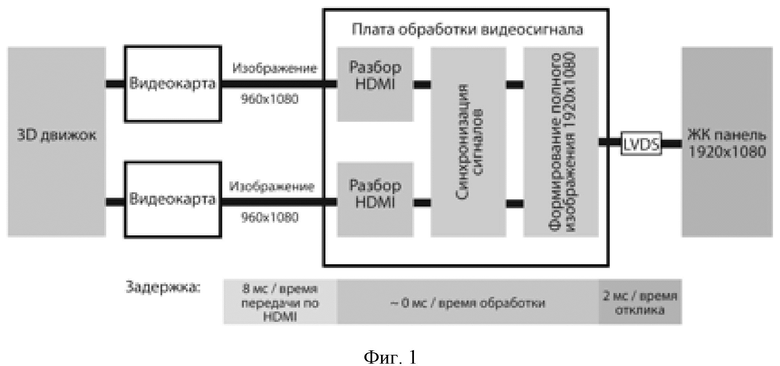

На Фиг. 1 показана схема цикла обработки видеосигнала.

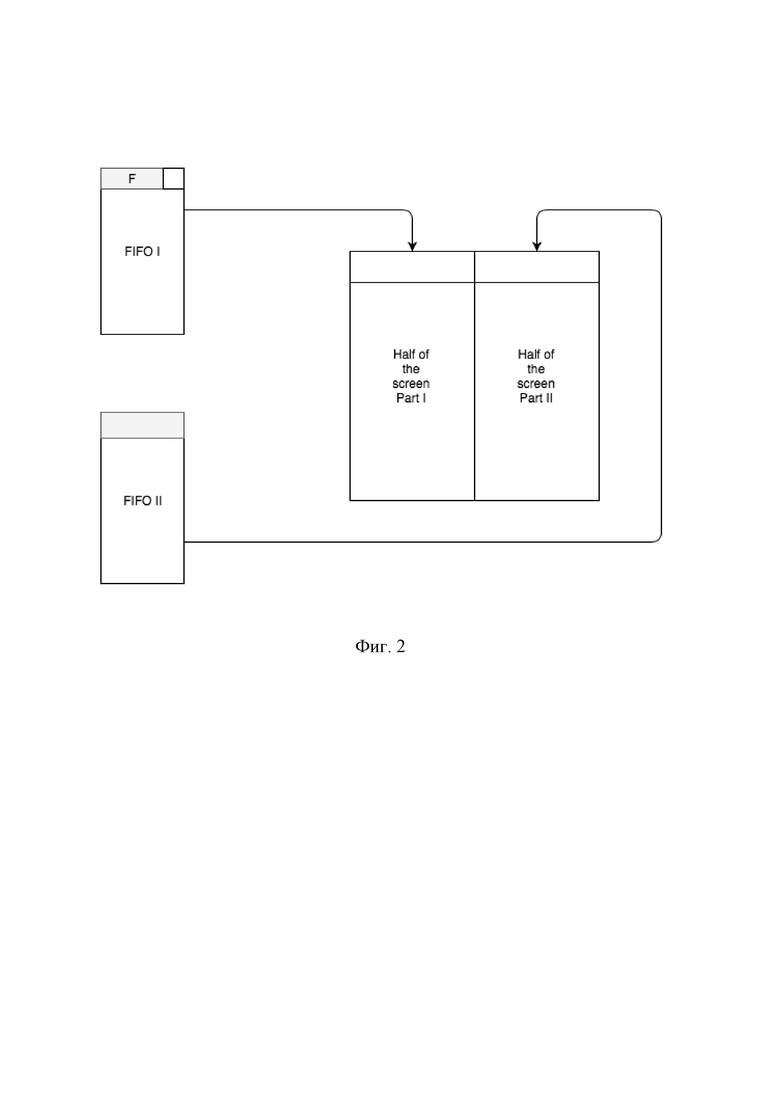

На Фиг. 2 показана схема алгоритма работы ПЛИС.

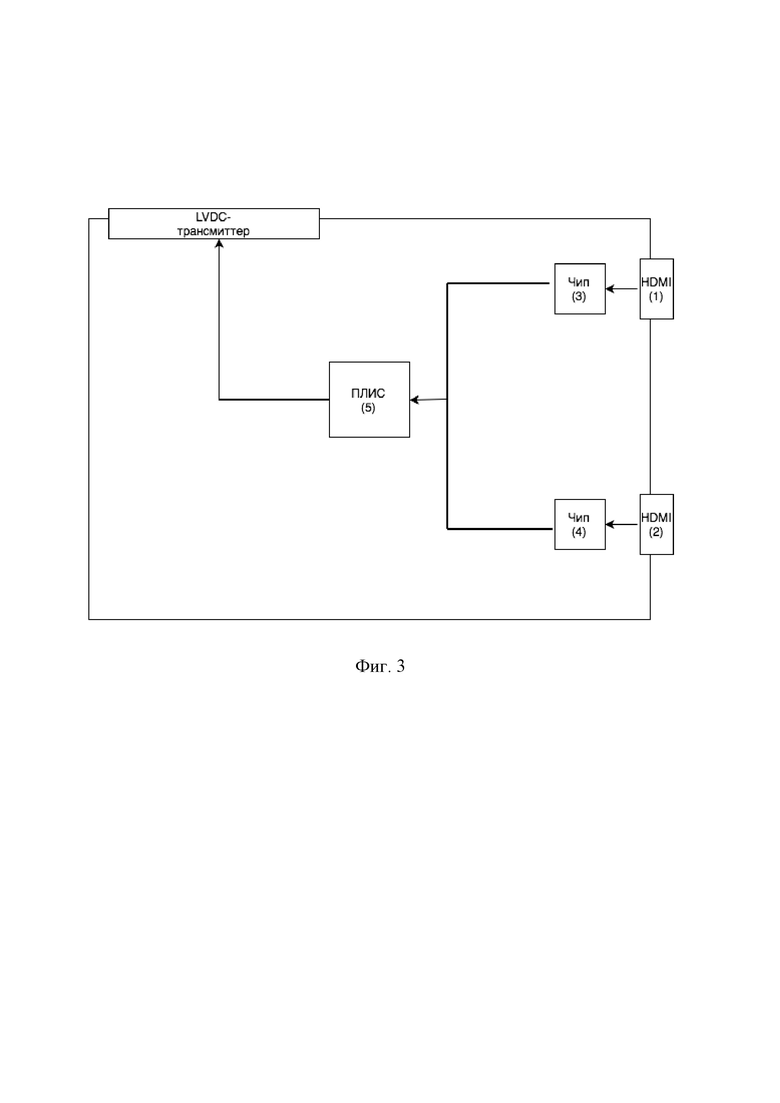

На Фиг. 3 показана схема платы обработки видеосигнала.

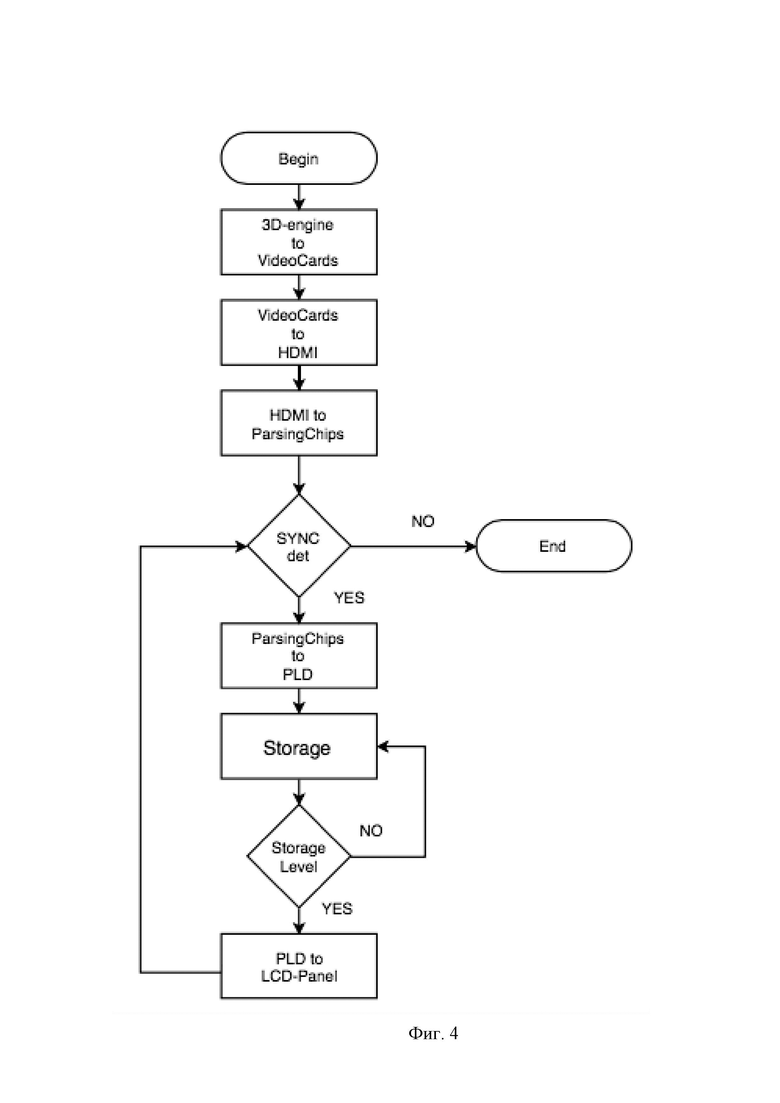

На Фиг. 4 показана блок-схема алгоритма обработки видеосигнала.

ПОДРОБНОЕ ОПИСАНИЕ ТЕХНИЧЕСКОГО РЕШЕНИЯ

Здесь и далее будут описаны термины, используемые в заявке.

Программируемая логическая интегральная схема (ПЛИС, англ. programmable logic device, PLD) – электронный компонент, используемый для создания цифровых интегральных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования.

High Definition Multimedia Interface (HDMI) – интерфейс для мультимедиа высокой чёткости, позволяющий передавать цифровые видеоданные высокого разрешения и многоканальные цифровые аудиосигналы с защитой от копирования.

HD – разрешение 1280×720 точек (пикселей).

Full HD – разрешение 1920×1080 точек (пикселей). Это маркетинговое название было впервые введено компанией Sony в 2007 году для ряда продуктов. Применяется в трансляциях телевидения высокого разрешения (HDTV), в телевизорах, компьютерных дисплеях, в камерах смартфонов, в видеопроекторах и т.п.

FIFO (акроним First In, First Out – «первым пришёл – первым ушёл») – способ организации и манипулирования данными относительно времени и приоритетов. Это выражение описывает принцип технической обработки очереди или обслуживания конфликтных требований путём упорядочения процесса по принципу: «первым пришёл – первым обслужен». Тот, кто приходит первым, тот и обслуживается первым, пришедший следующим ждёт, пока обслуживание первого не будет закончено, и так далее.

Дополненная реальность (англ. augmented reality, AR – «расширенная реальность») – результат введения в поле восприятия любых сенсорных данных с целью дополнения сведений об окружении и улучшения восприятия информации.

Виртуальная реальность (ВР, англ. virtual reality, VR, искусственная реальность) – созданный техническими средствами мир (объекты и субъекты), передаваемый человеку через его ощущения: зрение, слух, обоняние, осязание и другие. Виртуальная реальность имитирует как воздействие, так и реакции на воздействие. Для создания убедительного комплекса ощущений реальности компьютерный синтез свойств и реакций виртуальной реальности производится в реальном времени.

Низковольтная дифференциальная передача сигналов (англ. low-voltage differential signaling или LVDS) — способ передачи электрических сигналов, позволяющий передавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары.

Интегральная схема, микросхема, чип (англ. chip – тонкая пластинка – первоначально термин относился к пластинке кристалла микросхемы) – микроэлектронное устройство – электронная схема произвольной сложности, изготовленная на полупроводниковой подложке и помещённая в неразборный корпус или без такового, в случае вхождения в состав микросборки.

Заявленное техническое решение работает следующим образом.

Кадр формируется 3D-движком с последующим выводом на два видеовыхода. Возможна схема с двумя видеовыходами одной видеокарты или с двумя видеовыходами двух разных видеокарт. С каждого видеовыхода передается видеосигнал разрешением 960х1080 пикселей на плату через соответствующие порты HDMI. С помощью системы проверки синхронизации видеосигнала проверяется наличие видеосигнала на входах платы. При наличии видеосигнала осуществляется его передача на ПЛИС, которая синхронизирует и объединяет сигналы с двух видеовыходов в единый видеосигнал разрешением 1920х1080 пикселей и передает его через LVDS-трансмиттер на экран.

Для минимизации задержки используется ПЛИС, работающая с двумя системами FIFO, цикл работы которой выполняется следующим образом.

Происходит накопление пикселей в первой системе FIFO с синхронным накоплением пикселей во второй системе FIFO до достижения в первой системе FIFO порогового значения, достаточного для вывода одной строки пикселей на первую половину экрана.

Происходит вывод строки пикселей на первую половину экрана с синхронным накоплением пикселей во второй системе FIFO.

После окончания вывода строки пикселей на первую половину экрана начинается вывод строки пикселей на вторую половину экрана с синхронным накоплением пикселей следующей строки в первой и второй системах FIFO.

Повторение цикла производится до тех пор, пока все пиксели кадра не будут выведены на экран. После вывода всех пикселей кадра цикл начинается сначала для следующего кадра.

В конечном итоге максимальная задержка вышеприведенного способа обработки видеосигнала составит менее одной строки кадра, что соответствует величине менее 10 микросекунд.

На данном этапе развития технологий на рынке потребительской электроники аналогов заявленного решения для кардинального уменьшения задержки нет, а заявленное техническое решение является уникальным в своем роде. Заявленное техническое решение также может служить не только для использования совместно с технологией MotionParallax3D и соответствующими ЖК-дисплеями, но и для общего назначения на стандартных ЖК-дисплеях. Также важно отметить, что такая реализация решения поддерживает разрешение FullHD в режиме 3D при 120 Гц.

Заявленное техническое решение является промышленно применимым, поскольку для его реализации используют промышленно изготовленные и промышленно применимые ресурсы.

Хотя заявленное техническое решение описано конкретным примером его реализации, это описание не является ограничивающим, но приведено лишь для иллюстрации и лучшего понимания существа технического решения, объем которого определяется прилагаемой формулой.

Изобретение относится к технологиям обработки видеосигнала. Техническим результатом является снижение величины задержки при выводе видеосигнала на экран. Предложен способ обработки видеосигнала. Способ содержит этап, на котором при помощи, по меньшей мере, одного HDMI порта получают видеосигнал с, по меньшей мере, одной видеокарты. Далее при помощи, по меньшей мере, одного чипа разделяют полученный видеосигнал и передают разделенный сигнал на ПЛИС. Обрабатывают видеосигнал при помощи ПЛИС следующим образом. Накапливают пиксели в первой системе FIFO с синхронным накоплением пикселей во второй системе FIFO до достижения в первой системе FIFO порогового значения, достаточного для вывода одной строки пикселей на первую половину экрана. При помощи LVDS-трансмиттера выводят строку пикселей на первую половину экрана с синхронным накоплением пикселей во второй системе FIFO. 4 ил.

Способ обработки видеосигнала, содержащий этапы, на которых:

при помощи, по меньшей мере, одного HDMI порта получают видеосигнал с, по меньшей мере, одной видеокарты;

при помощи, по меньшей мере, одного чипа разделяют полученный видеосигнал и передают разделенный сигнал на ПЛИС;

обрабатывают видеосигнал при помощи ПЛИС следующим образом:

накапливают пиксели в первой системе FIFO с синхронным накоплением пикселей во второй системе FIFO до достижения в первой системе FIFO порогового значения, достаточного для вывода одной строки пикселей на первую половину экрана;

при помощи LVDS-трансмиттера выводят строку пикселей на первую половину экрана с синхронным накоплением пикселей во второй системе FIFO;

после окончания вывода строки пикселей на первую половину экрана начинают вывод строки пикселей на вторую половину экрана при помощи LVDS-трансмиттера с синхронным накоплением пикселей следующей строки в первой и второй системах FIFO;

повторяют цикл до тех пор, пока все пиксели кадра не будут выведены на экран.

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| US 5546530 A, 13.08.1996 | |||

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| US 5323272 A, 21.06.1994 | |||

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| УСТРОЙСТВО СЪЕМКИ ДВИЖУЩИХСЯ ИЗОБРАЖЕНИЙ, СИСТЕМА И УСТРОЙСТВО ОБРАБОТКИ ИНФОРМАЦИИ И СПОСОБ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 2012 |

|

RU2570195C2 |

Авторы

Даты

2018-03-16—Публикация

2017-03-31—Подача