Изобретение относится к области микро- и наноэлектроники и может быть использовано для построения надежных сверхбольших запоминающих матриц с энергонезависимой памятью, высокой степенью интеграции элементов и малым энергопотреблением.

Известна матрица запоминающего устройства для программируемых логических устройств на базе транзисторов с плавающим затвором (Zhigang W., Fethi D., McCollum S., Vidyadhara B. Array and control method for flash based FPGA cell. / US Patent №8120955 B2 Feb. 21, 2012. Filed: Feb. 13, 2009). Устройство представляет собой NOR Flash память на базе n-канальных транзисторов с плавающим затвором (размером 10 F2). Каждая ячейка содержит дополнительно два адресных высоковольтных транзистора: n-МОП и р-МОП (более 10 F2 каждый). Большие размеры ячеек и, соответственно, малая степень интеграции налагают ограничения на итоговый размер матрицы. В Flash ячейке необходимо контролировать избыточное стирание во время работы, что требует точного контроля напряжения и усложняет периферийную схемотехнику.

Известна концепция создания реконфигурируемого массива из комплементарных мемристорных ячеек, реализующего логические функции (Levy Y., Bruck J., Cassuto Y., et al. Logic operations in memory using a memristive Akers array / Microelectronics Journal. 2014. V. 45. P. 1429-1437; Kvantinsky S., Kolodny A, Hanein Y. Memristive Akers Logic Array / Patent № US 9548741 B1. Jan. 17, 2017. Filed: Jul. 14, 2015). Устройство обладает недостатками, основной из которых заключается в низкой степени интеграции элементов из-за большого количества ключей (2 или 4) на одну пару мемристоров. С другой стороны, авторы, высказывая возможность комплементарного соединения мемристоров, не предлагают способов разделения цепей записи и считывания, которые требуются при объединении таких ячеек в сверхбольшие матрицы в запоминающих устройствах. Последовательное включение мемристоров ограничивает итоговый размер массива из-за затухания входного сигнала (при отношении сопротивлений мемристоров в разных состояниях, равном 1000, в массиве из 1282 элементов минимальная деградация сигнала составит 10%). Для поддержания достаточного уровня сигнала такие массивы придется разбивать на небольшие блоки, перемежающиеся со схемами усиления, что также снижает степень интеграции.

Задачей, которую решает изобретение, является обеспечение устойчивой работы сверхбольшой запоминающей матрицы на основе комплементарной мемристорно-диодной ячейки памяти с малым энергопотреблением, обеспечивающей параллельный и последовательный доступ к записи и считыванию данных.

Техническим результатом является разработка схемотехники и топологии мемристорно-диодной ячейки, которая дает возможность высокой степени интеграции при объединении таких ячеек в сверхбольшую матрицу.

Это достигается путем формирования ячейки памяти из комплементарных мемристоров (последовательно соединенных) и ответвлением от общей точки мемристоров через разделяющий диод Зенера. Предложенные топологии мемристорно-диодных ячеек дают возможность добиться высокой степени интеграции при объединении их в сверхбольшую матрицу, в которой крупные КМОП-транзисторы являются общими для больших строк ячеек. При этом вся площадь матрицы заполняется мемристорными ячейками нанометрического размера (минимальный размер ячейки ограничен размером диода 4F2, так как мемристоры размером 1F2 расположены над ним и не занимают дополнительную площадь), а крупные элементы вынесены на периферию и не расходуют площадь кристалла.

Ячейки можно реализовать на кристалле в виде их матричной организации с параллельным и побитным доступом в составе запоминающего устройства. Разработанная запоминающая матрица решает проблему взаимовлияния узлов, характерную для простейших мемристорных схем кроссбаров, поскольку общее сопротивление ячеек всегда остается высоким, а сквозной ток через комплементарные мемристоры минимальным.

Сущность изобретения поясняется фиг. 1-7.

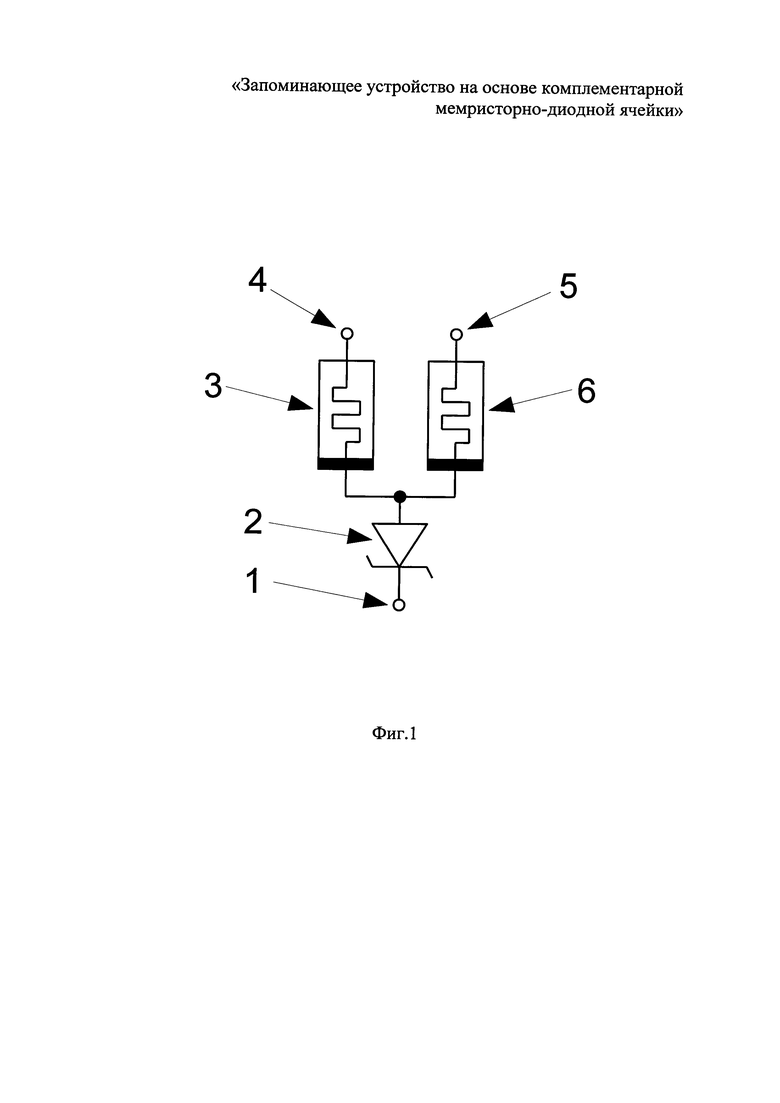

На фиг. 1 показана электрическая схема ячейки, образованной двумя комплементарными мемристорами и одним диодом Зенера, где 1 - катод диода, 2 - диод Зенера, 3 - мемристор, 4 - контакт первого мемристора, 5 - контакт второго мемристора, 6 - мемристор.

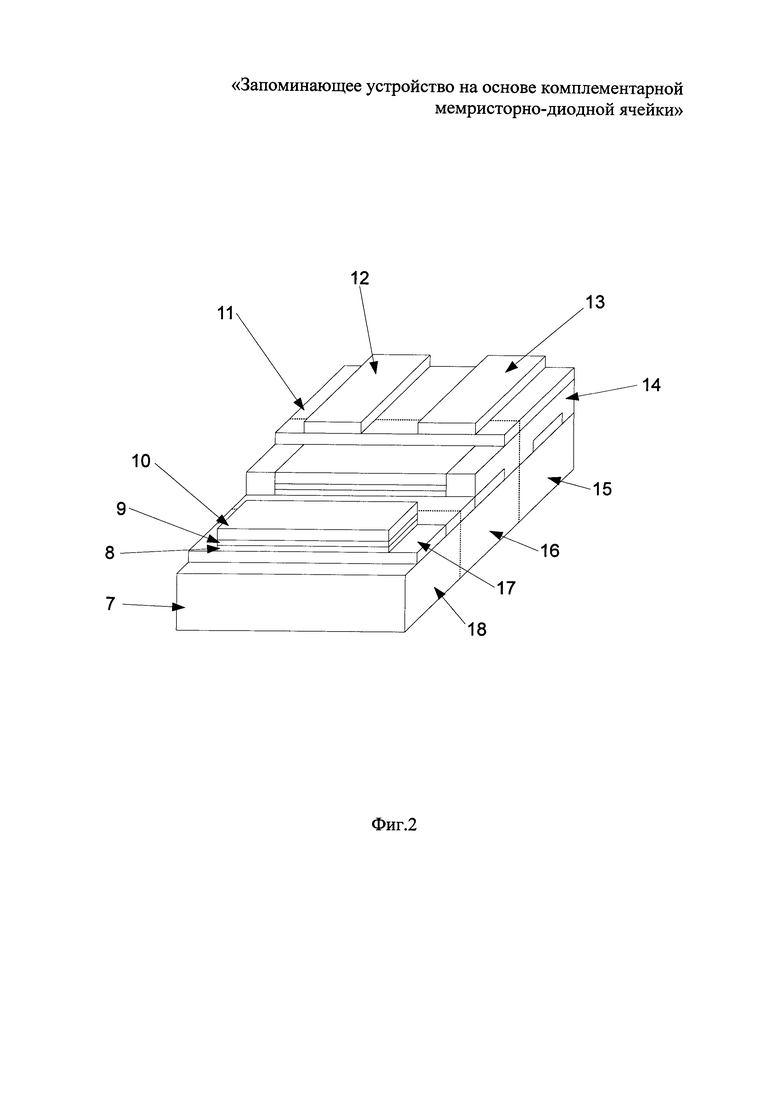

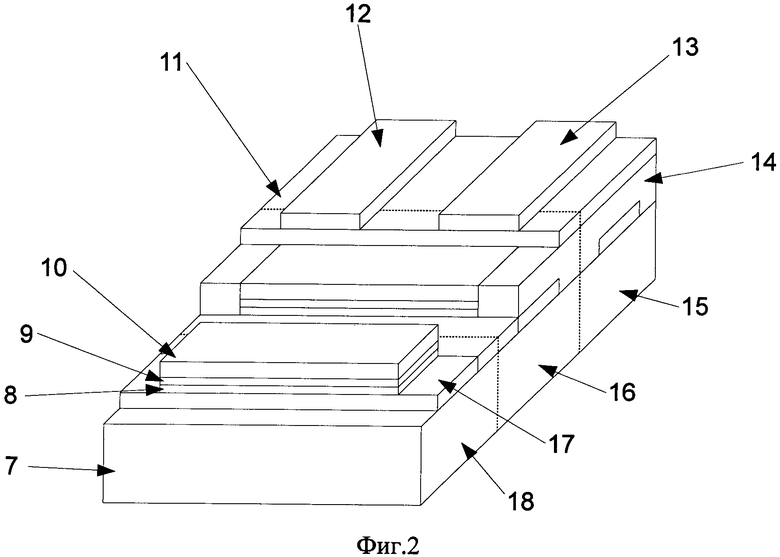

На фиг. 2 представлены топологические приемы построения фрагмента параллельной матрицы из предлагаемых ячеек, состоящего, например, из трех коммутационных ячеек, где 7 - подложка, 8 - n+ - полупроводник, 9 - n - полупроводник, 10 - р-полупроводник, 11 - мемристорный слой, 12 - проводящая шина, 13 - проводящая шина, 14 - изолятор, 15 - отдельная ячейка, 16 - отдельная ячейка, 17 - проводящая шина, 18 - отдельная ячейка.

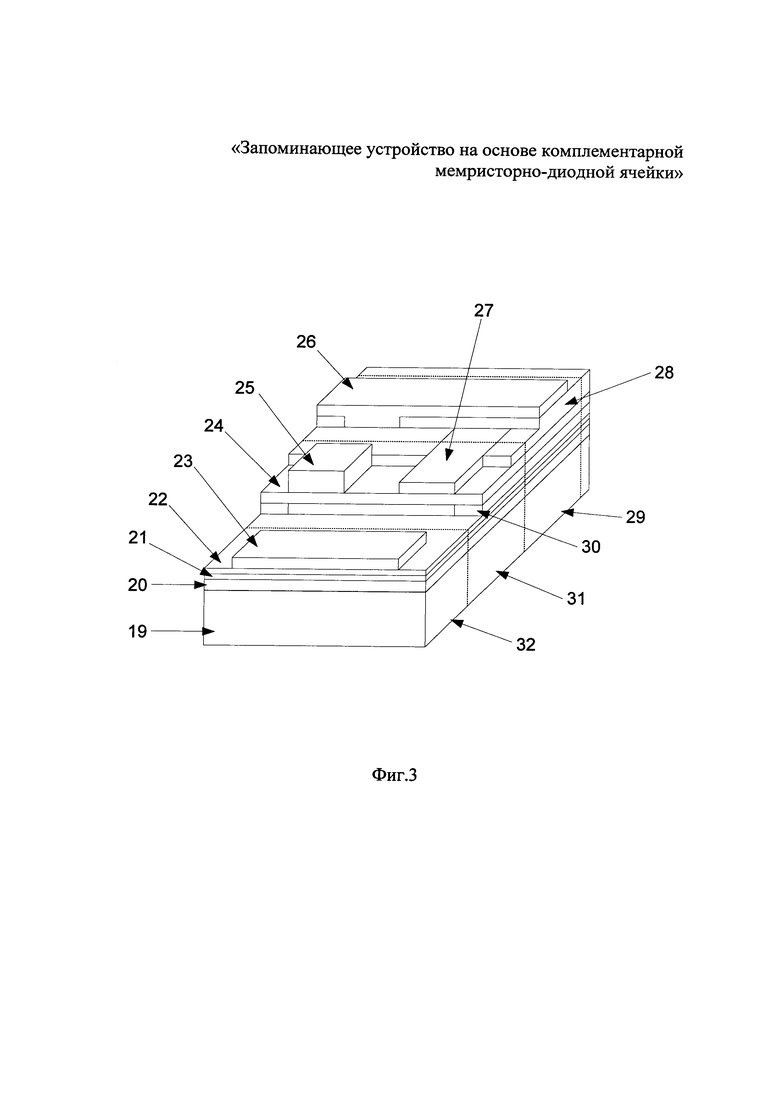

На фиг. 3 представлены топологические приемы построения фрагмента матрицы из предлагаемых ячеек с побитовым доступом, где 19 - подложка, 20 - проводящий слой, 21 - n+ - полупроводник, 22 - n - полупроводник, 23 - р-полупроводник, 24 - мемристивный слой, 25 - соединительный проводник, 26 - проводящая шина, 27 - проводящая шина, 28 - изолятор, 29 - отдельная ячейка, 30 - изолятор, 31 - отдельная ячейка, 32 - отдельная ячейка.

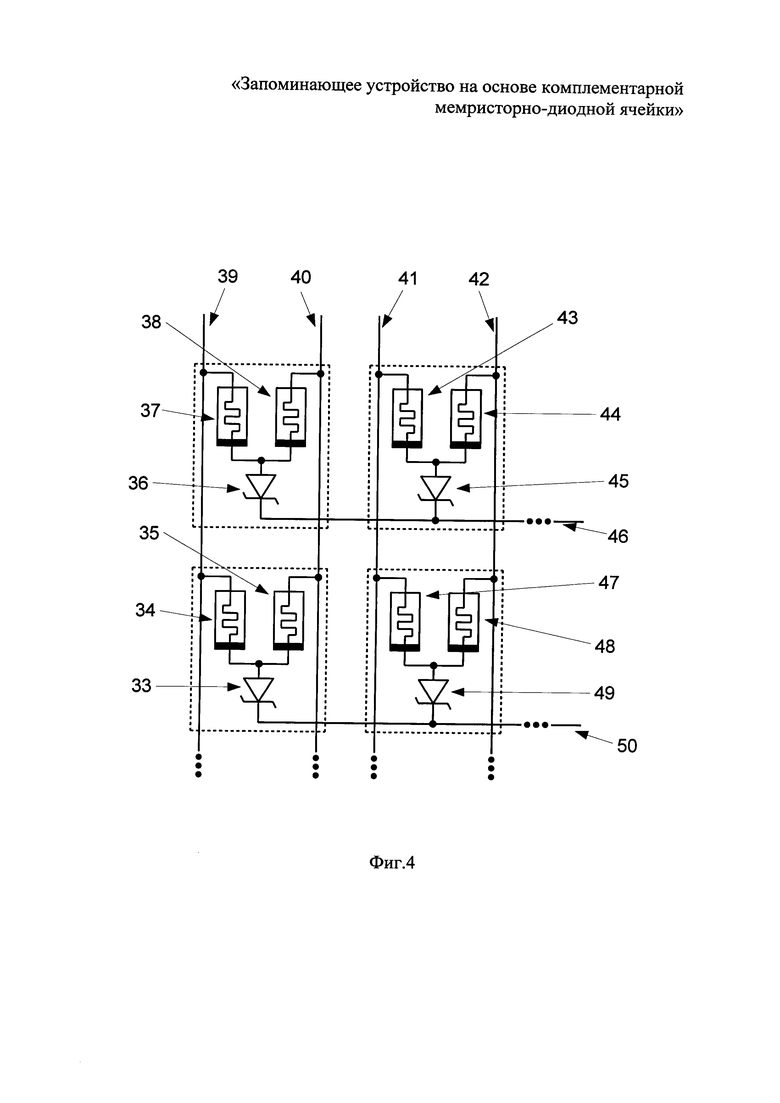

На фиг. 4 показан фрагмент матрицы с параллельным включением предлагаемых ячеек, где 33 - диод Зенера, 34 - мемристор, 35 - мемристор, 36 - диод Зенера, 37 - мемристор, 38 - мемристор, 39 - соединительная шина / вход матрицы X1, 40 - соединительная шина / вход матрицы Y1, 41 - соединительная шина / вход матрицы Х2, 42 - соединительная шина / вход матрицы Y2, 43 - мемристор, 44 - мемристор, 45 - диод Зенера, 46 - соединительная шина / выход матрицы Q1, 47 - мемристор, 48 - мемристор, 49 - диод Зенера, 50 - соединительная шина / выход матрицы Q2.

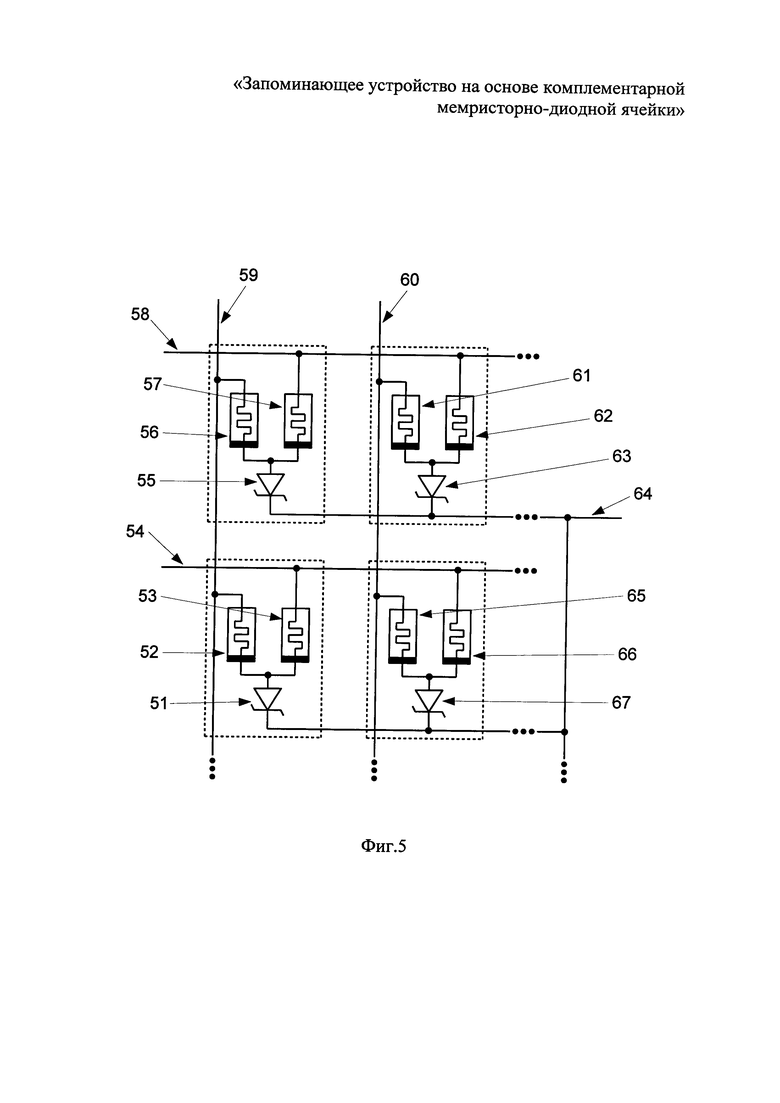

На фиг. 5 показан фрагмент матрицы из трех предлагаемых ячеек с побитовым доступом, где 51 - диод Зенера, 52 - мемристор, 53 - мемристор, 54 - соединительная шина / вход матрицы Y2, 55 - диод Зенера, 56 - мемристор, 57 - мемристор, 58 - соединительная шина / вход матрицы Y1, 59 - соединительная шина / вход матрицы X1, 60 - соединительная шина / вход матрицы Х2, 61 - мемристор, 62 - мемристор, 63 - диод Зенера, 64 - соединительная шина / последовательный выход матрицы Q1, 65 - мемристор, 66 - мемристор, 67 - диод Зенера.

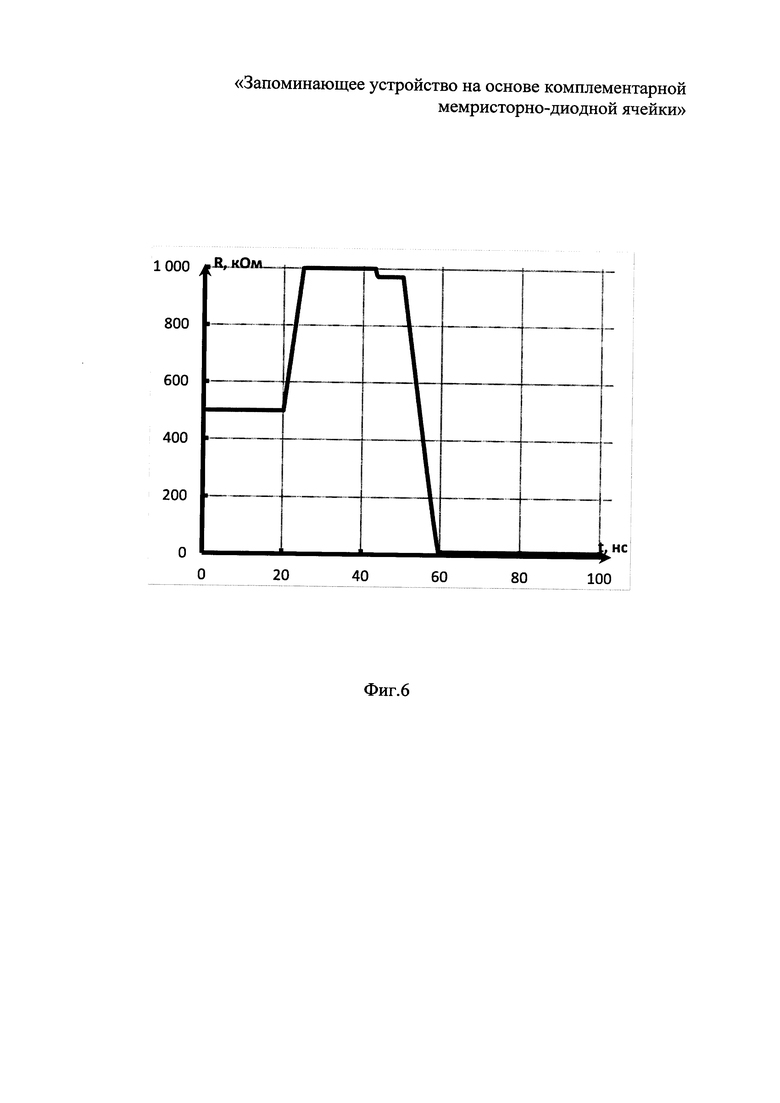

На фиг. 6 представлена кривая изменения сопротивления от времени первого мемристора 37 на фиг 4 первой ячейки в матрице из четырех ячеек.

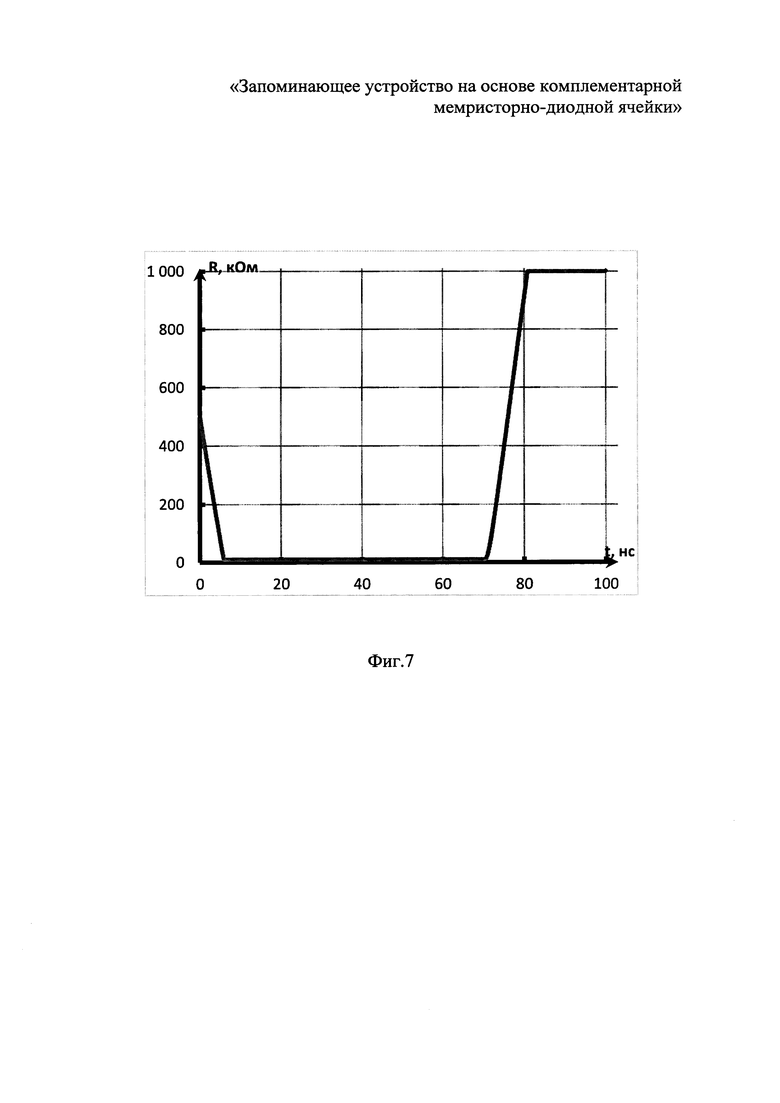

На фиг. 7 представлена кривая изменения сопротивления от времени второго мемристора 38 на фиг 4 первой ячейки в матрице из четырех ячеек.

Рассмотрим работу устройства.

Топология комплементарной мемристорно-диодной ячейки, позволяющей организовать матрицу запоминающего устройства с параллельным выводом данных, представлена на фиг. 2. На подложке 7 в изолирующем материале 14 создана матрица вертикально ориентированных диодов с эффектом Зенера (слои 8-10). Внизу сформированы области легированного и высоколегированного полупроводника n-типа 8 и 9 соответственно, являющиеся катодами диодов Зенера. Катоды объединены построчно проводниками 17, показанными в плоскости чертежа топологии горизонтальными линиями. Методом вакуумного магнетронного осаждения сверху на аноды диодов наносится слой мемристивного материала 11 на основе оксида титана. При этом анод диода 10, являющийся областью p-типа, располагается под мемристивным слоем 11 и представляет собой общий контакт комплементарных мемристоров в соответствии с электрической схемой (фиг. 1). Комплементарные мемристоры образованы внутри активного слоя 11 между анодным контактом диода 10 и двумя верхними проводниками 12 и 13, которые показаны сверху уходящими проводниками на топологическом чертеже (фиг. 2).

Другой тип топологии комплементарной мемристорно-диодной ячейки позволяет реализовать матрицу запоминающего устройства с побитным доступом и с последовательным выводом данных через общую шину. Для этого в топологии, показанной на фиг. 3, объединены ячейки в кроссбар по внешним линиям комплементарной пары мемристоров. В новой топологии изменено расположение одной из верхних линий 26, подключенной к мемристорам, с вертикального прохождения на горизонтальное. При этом полученное пересечение проводников разделено в пространстве слоем диэлектрика 28. Для соединения кросспроводника с нижними мемристорами сформированы проводящие переходные колодцы 25. Линии электрической связи диодных катодов в ячейках 21 соединили в один проводящий слой, являющейся общей шиной последовательного вывода данных 20. Роль катодного слоя может играть подложка легированного полупроводника n-типа.

Следует отметить, что ячейка для матрицы с последовательным выводом информации технологически более сложная. Она требует нанесения верхнего слоя диэлектрика и имеет дополнительную технологическую трудоемкость при создании переходных проводящих колодцев. Однако в этой ячейке не требуется литография для создания проводников катодов, и соединение катодов осуществляется с помощью одного проводящего слоя легированного акцепторной примесью полупроводника. Преимуществом более сложной ячейки является значительное уменьшение межшинной емкости, что увеличивает энергоэффективность при работе матрицы на высоких скоростях записи.

Проводники 39-42, 46, 50, показанные на фиг. 4, являются для ячейки параллельной матрицы шинами, предназначенными для передачи сигналов и питания. Каждая ячейка подключена к двум верхним шинам и одной нижней. Верхняя пара шин 39 и 40, непосредственно подключенная к контактам мемристоров 34, 35, 37, 38, уходит на периферию, где соединяется с КПОМ драйверами управляющих сигналов по столбцам. Нижние шины 46 и 50, которые объединяют катоды диодов 33, 36, 45, 49 ячеек, находящихся на одной линии, уходят на другую сторону периферии матрицы. Сигналы с 46 и 50 шин подаются на входные драйверы строк в параллельном коде.

Линии 59, 60 и 54, 58 на фиг. 5, накрест пронизывая объем матрицы второго типа, объединяют ячейки в электрическую сеть по принципу построения кроссбаров. Каждая ячейка включена в перекрестье для организации побитного доступа, по аналогии с традиционными схемами DRAM. Информация из матрицы считывается последовательно при помощи входного драйвера строк по нижней шине 64, на которую сигнал подается через диод выбранной ячейки, при этом диоды остальных ячеек остаются в закрытом состоянии.

Входные драйверы представляют собой усилители сигналов с мемристоров и формирователи уровней напряжений для их передачи в последующие логические устройства. Драйверы выполняют функции подачи на шины питания: высокого надпорогового напряжения для записи верхних или нижних мемристоров и низкого подпорогового напряжения для считывания данных через объединенные катоды диодов с помощью входных драйверов.

Логика работы выходных драйверов заключается в последовательной подаче импульса тока для закрытия открытого мемристора, а затем импульса напряжения для открытия другого мемристора. При этом общее сопротивление пары все время удерживается высоким, а сквозной ток через комплементарные мемристоры остается минимальным, что повышает энергоэффективность всей матрицы. Подача импульса тока осуществляется через прямосмещенный диод Зенера, а импульс напряжения подается при лавинном пробое на обратной полярности. Первая формовка ячеек, необходимая для установления рабочей полярности многих мемристивных материалов, выполняется аналогично рабочим переключениям с помощью выходных драйверов, но на большей длительности и амплитуде импульсов.

Результат записи в первую ячейку, полученный в ходе SPICE моделирования матрицы из 2×2 ячеек, представлен на фиг. 6 и фиг. 7, из которых видно, что комплементарные мемристоры при считывании всегда находятся в противоположных состояниях. Изначально все мемристоры находились в промежуточном состоянии 500 кОм. При записи в первую ячейку сопротивление одного мемристора 37 увеличивается до предела (1 МОм), а второго 38 уменьшается до минимального (10 кОм). Таким образом, общее сопротивление пары остается высоким.

Отличающийся более высокой скоростью принцип переключения комплементарных ячеек без участия диода Зенера возможен только для матрицы с побитным доступом, показанной на фиг. 5. В этом случае, с помощью драйверов управляющих сигналов подается импульс надпорогового напряжения на выбранную в перекрестье ячейку, при этом в комплементарной паре закрытый мемристор открывается, а затем другой мемристор через первый закрывается. Также не исключена обратная последовательность переключения комплементарных мемристоров. Однако чтобы ячейка эффективно работала по механизму с переключением, необходим подбор мемристивного материала с определенными электрофизическими характеристиками.

| название | год | авторы | номер документа |

|---|---|---|---|

| 3D запоминающая матрица на основе комплементарной мемристорно-диодной ячейки | 2017 |

|

RU2697623C2 |

| Многослойная логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2682548C2 |

| Логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2643650C1 |

| ОДНОЭЛЕКТРОННЫЙ МЕМРИСТОР (НАНОЯЧЕЙКА) И СПОСОБ ПРИМЕНЕНИЯ | 2023 |

|

RU2823967C1 |

| СПОСОБ УПРАВЛЕНИЯ РАБОТОЙ МЕМРИСТИВНОЙ КОНДЕНСАТОРНОЙ СТРУКТУРЫ МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК | 2018 |

|

RU2706197C1 |

| МЕМРИСТОР НА ОСНОВЕ СМЕШАННОГО ОКСИДА МЕТАЛЛОВ | 2011 |

|

RU2472254C9 |

| Способ формирования мемристивных структур на основе композитных оксидов с агломератами наночастиц | 2021 |

|

RU2767721C1 |

| СПОСОБ ФОРМИРОВАНИЯ СИНАПТИЧЕСКОГО МЕМРИСТОРА НА ОСНОВЕ НАНОКОМПОЗИТА МЕТАЛЛ-НЕСТЕХИОМЕТРИЧЕСКИЙ ОКСИД | 2017 |

|

RU2666165C1 |

| Оптически управляемый мемристор на основе МДП-структуры ITO/ZrO2(Y)/Si с наноостровками Ge | 2022 |

|

RU2803506C1 |

| ДРАЙВЕР ПИКСЕЛЬНОЙ ЯЧЕЙКИ OLED ДИСПЛЕЯ | 2012 |

|

RU2494472C1 |

Использование: для построения надежных сверхбольших запоминающих матриц с энергонезависимой памятью, высокой степенью интеграции элементов и малым энергопотреблением. Сущность изобретения заключается в том, что запоминающее устройство на основе комплементарной мемристорно-диодной ячейки, представляющее собой матрицу электрически перепрограммируемых ячеек с параллельным или последовательным доступом к записи и чтению по общим электрическим шинам, отличается тем, что в каждой ячейке памяти последовательно включены мемристоры и к их общему контакту подключен диод Зенера, так что ячейка имеет подключенные к общим электрическим шинам три вывода, два из которых соединены с контактами мемристоров и еще один - с контактом диода Зенера. Технический результат: обеспечение возможности высокой интеграции при объединении ячеек в сверхбыструю матрицу. 7 ил.

Запоминающее устройство на основе комплементарной мемристорно-диодной ячейки, представляющее собой матрицу электрически перепрограммируемых ячеек с параллельным или последовательным доступом к записи и чтению по общим электрическим шинам, отличающееся тем, что в каждой ячейке памяти последовательно включены мемристоры и к их общему контакту подключен диод Зенера, так что ячейка имеет подключенные к общим электрическим шинам три вывода, два из которых соединены с контактами мемристоров и еще один с контактом диода Зенера.

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

| WO 2016175822 A1, 03.11.2016 | |||

| US 5646879 A1, 08.07.1997 | |||

| US 20160189775 A1, 30.06.2016 | |||

| WO 2010087852 A1, 05.08.2010. | |||

Авторы

Даты

2018-04-04—Публикация

2017-03-20—Подача