Изобретение относится к области микро- и наноэлектроники и может быть использовано для создания многослойной запоминающей матрицы с энергонезависимой памятью и высокой степенью интеграции элементов.

Известно устройство планарной запоминающей матрицы на основе комплементарной мемристорно-диодной ячейки, которая представляет собой двухслойное соединение комплементарных мемристоров и одного разделяющего диода Зенера (Удовиченко С.Ю., Маевский О.В., Писарев А.Д., Бусыгин А.Н., Комплементарная мемристорно-диодная ячейка для запоминающей матрицы нейроморфного процессора. // Сборник тезисов VIII конференции Нанотехнологического общества России. 2017. С. 37-40). Основными недостатками построения сверхбольшой логической матрицы в планарной геометрии являются низкая степень интеграции элементов и большая длина соединительных проводников.

Известно устройство с трехмерной организацией запоминающей матрицы на основе транзисторов с плавающим затвором (Jiyoung Kim et al. А stacked memory device on logic 3D technology for ultra-high-density data storage. Nanotechnology (2011) 22:254006 и Konevecki M., Dunton V., Radigan S. Vertical bit line non-volatile memory with recessed word lines / US Patent №9450023 B1 Sep. 20, 2016 Filled Apr. 8, 2015). Устройство представляет собой NAND Flash память на базе n-канальных транзисторов с плавающим затвором (размером 10 F2). Для управления программированием в матрицу включены высоковольтные МОП транзисторы, размер которых превышает 10 F2. Большие размеры ячеек и, соответственно, малая степень интеграции налагают ограничения на итоговый размер матрицы. Во Flash ячейке необходимо контролировать избыточное стирание во время работы, что требует точного контроля напряжения и усложняет периферийную схемотехнику. Общим недостатком Flash памяти по сравнению с мемристорами является высокое энергопотребление при записи, причем процесс записи является медленным, около 100 мс.

Известно энергонезависимое запоминающее устройство на основе ячеек униполярного резистивного переключения, включенных последовательно с нелинейным элементом (Bandyopadhyay A., Scheuerlein R.E., Gorla C.R., Le В. FET low current 3D ReRAM non-volatile storage / US Patent №2015/0070965 A1 Mar. 12, 2015 Filled Sep.12, 2013). В такой схеме исключение взаимовлияния соседних ячеек реализовано с помощью обычного полупроводникового диода. Недостатками использования эффекта униполярного резистивного переключения являются высокое энергопотребление ячейки при переключении в низкопроводящее состояние, более высокий разброс параметров мемристоров и быстрая деградация по сравнению с биполярным резистивным переключением. Кроме того, предложенная в патенте топология предполагает большое число производственных операций из-за горизонтального относительно подложки расположения областей с разной технологией изготовления.

Задачей, которую решает изобретение, является создание электрической схемы и топологии сверхбольшой запоминающей матрицы на основе биполярных мемристорных элементов при небольшой занимаемой площади на кристалле устройства.

Техническим результатом является высокая степень интеграции элементов, малое энергопотребление и высокое быстродействие устройства.

Это достигается путем объединения планарных (двухслойных) запоминающих матриц в 3D структуру и использования энергонезависимых переключающихся элементов - биполярных мемристоров, имеющих малый размер (1 F2) и высокую скорость переключения (менее 30 нс). Технология изготовления 3D структуры достаточно проста и включает формирование топологии из одинаковых горизонтально расположенных комбинированных кроссбаров, включающих активный мемристорный слой и полупроводниковый слой диодов Зенера. Оба слоя изготавливаются промышленным способом - в магнетронном технологическом модуле. При этом легированный полупроводник образуется путем одновременного распыления двух катодов (Kim Н.К. et al. Erbium Doped Semiconductor Thin Films Prepared by RF Magnetron Sputtering // Mat.Res.Soc.Symp.Proc. 1993. Vol. 301. C. 55-60).

Комплементарное включение мемристоров позволяет уменьшить сквозной ток через ячейку в ходе операции считывания и, соответственно, энергопотребление, а также влияние неоднородности характеристик мемристоров на выходное напряжение ячейки. С другой стороны, добавление в ячейку мемристор-диод комплементарного мемристора незначительно уменьшает интеграцию устройства. Применение в ячейке диода Зенера, пропускающего ток в обоих направлениях в отличии от обычного диода, позволяет исключить взаимовлияние ячеек при биполярном резистивном переключении. Таким образом устранены основные недостатки запоминающего устройства, построенного на униполярных мемристорах.

Сущность изобретения поясняется на фиг. 1 - фиг. 5.

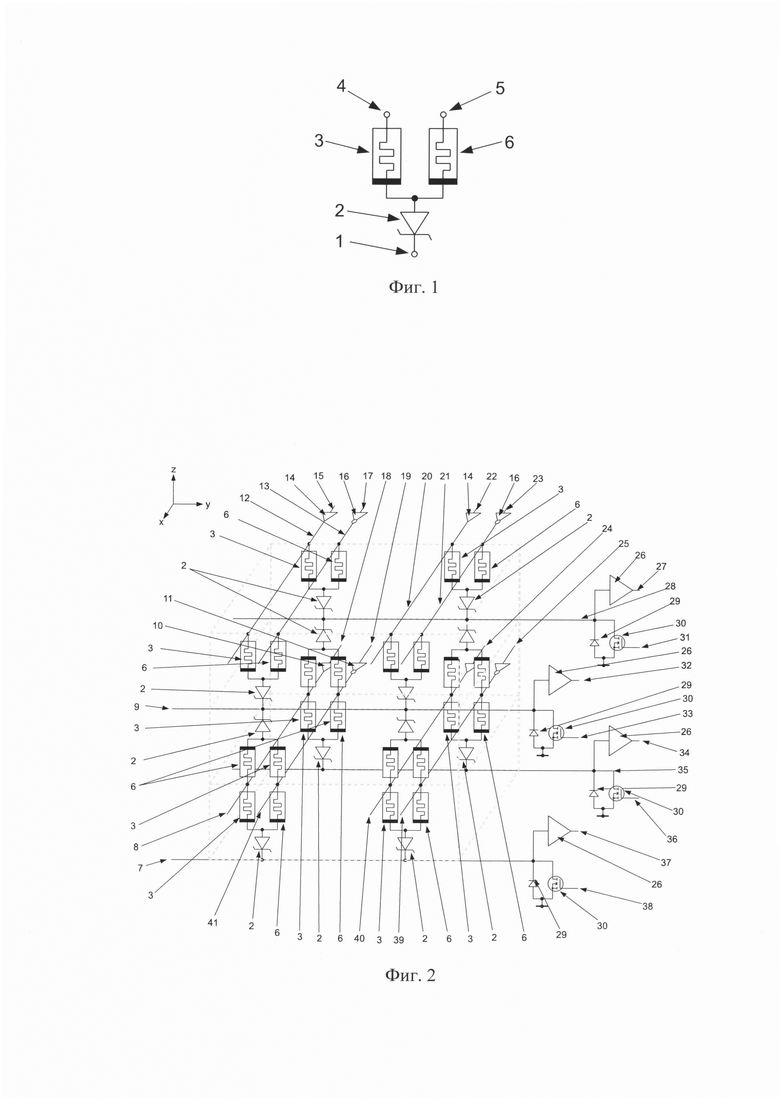

На фиг. 1. представлена электрическая схема ячейки, где 1 - выходной контакт ячейки; 2 - диод Зенера; 3 - первый мемристор комплементарной пары; 4 - первый вход ячейки; 5 - второй вход ячейки; 6 - второй мемристор комплементарной пары.

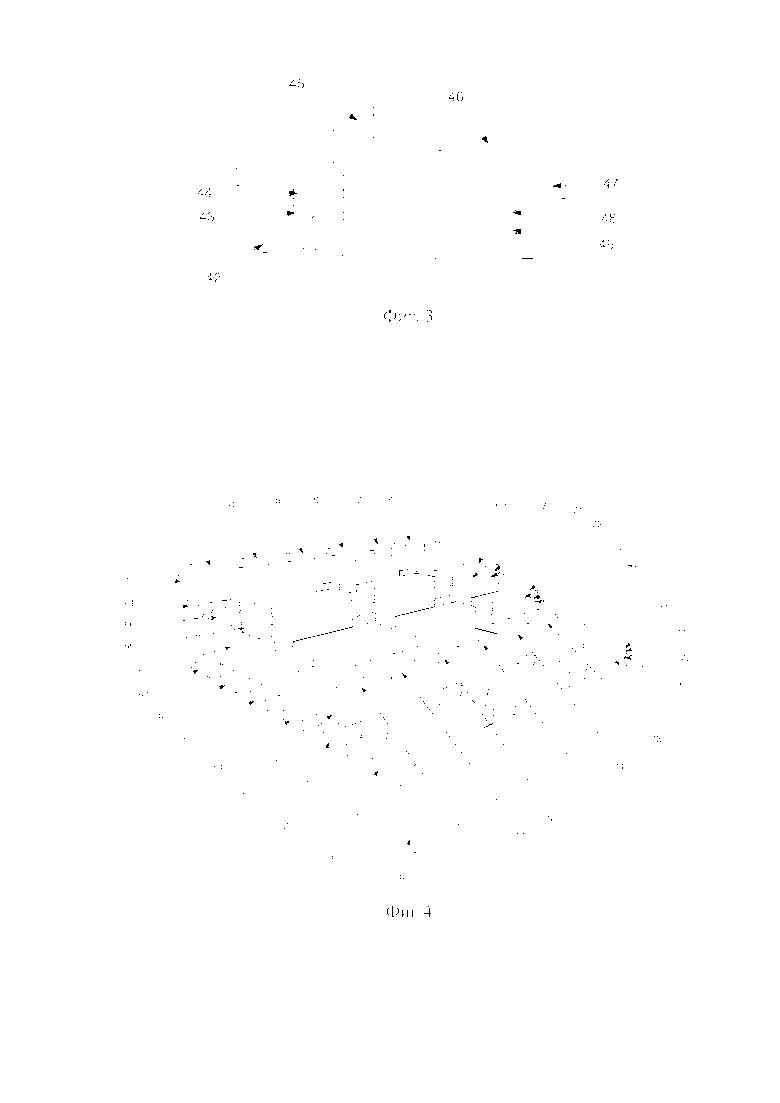

На фиг. 2. показана электрическая схема трехмерной запоминающей матрицы, где 7 - выходная шина второй строки нижнего слоя ячеек; 8 - общая входная шина нижнего и среднего слоев ячеек; 9 - общая выходная шина второй строки среднего и верхнего слоев ячеек; 10 - усилитель среднего и нижнего слоев ячеек; 11 - инвертор среднего и нижнего слоев ячеек; 12 - входная шина первого столбца верхнего слоя ячеек; 13 - входная шина первого столбца верхнего слоя ячеек; 14 - усилитель верхнего слоя ячеек; 15 - неинвертирующий вход первого столбца верхнего слоя ячеек; 16 - инвертор верхнего слоя ячеек; 17 - инвертирующий вход первого столбца верхнего слоя ячеек; 18 - общий неинвертирующий вход первого столбца нижнего и среднего слоев ячеек; 19 - общий инвертирующий вход первого столбца нижнего и среднего слоев ячеек; 20 - входная шина второго столбца верхнего слоя ячеек; 21 - входная шина второго столбца верхнего слоя ячеек; 22 - неинвертирующий вход второго столбца верхнего слоя ячеек; 23 - инвертирующий вход второго столбца верхнего слоя ячеек; 24 - общий неинвентирующий вход второго столбца нижнего и среднего слоев ячеек; 25 - общий инвертирующий вход второго столбца нижнего и среднего слоев ячеек; 26 - выходной драйвер; 27 - общий выход первой строки верхнего и среднего слоев ячеек; 28 - общая выходная шина первой строки верхнего и среднего слоев ячеек; 29 - диод; 30 - n-МОП транзистор; 31 - общий вход управления записью первой строки верхнего и среднего слоев ячеек; 32 - общий выход второй строки верхнего и среднего слоев ячеек; 33 - общий вход управления записью второй строки верхнего и среднего слоев ячеек; 34 - выход первой строки нижнего слоя ячеек; 35 - выходная шина первой строки нижнего слоя ячеек; 36 - вход управления записью первой строки нижнего слоя ячеек; 37 - выход второй строки нижнего слоя ячеек; 38 - вход управления записью второй строки нижнего слоя ячеек; 39 - общая входная шина второго столбца нижнего и среднего слоев ячеек; 40 - общая входная шина второго столбца нижнего и среднего слоев ячеек; 41 - общая входная шина первого столбца нижнего и среднего слоев ячеек.

На фиг. 3. приведена топология отдельной ячейки, где 42 - нижний проводник кроссбара; 43 - слаболегированный n-полупроводник; 44 - общий электрод мемристоров ячейки; 45 - верхний проводник кроссбара/электрод первого мемристора; 46 - верхний проводник кроссбара/электрод второго мемристора; 47 - мемристорный слой; 48 - р-полупроводник; 49 - сильнолегированный n-полупроводник.

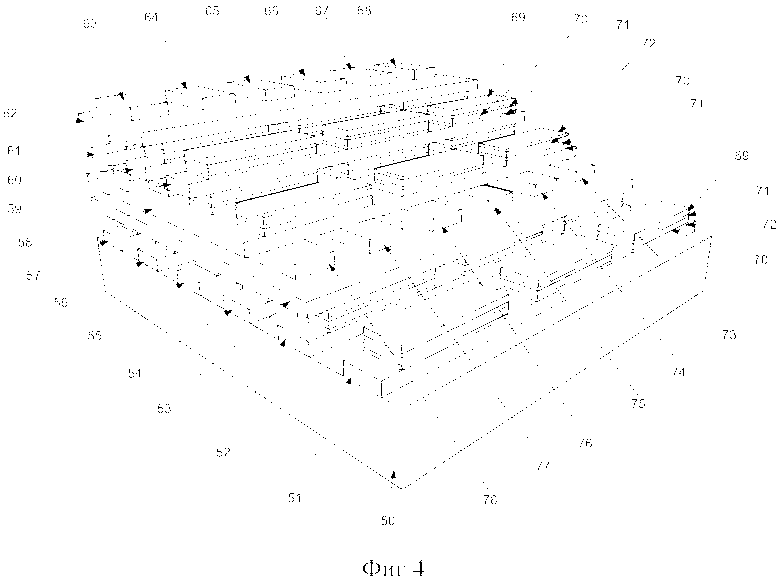

На фиг. 4. представлена топология трехслойной запоминающий матрицы, образованной тремя 3×6 кроссбарами, где 50 - подложка; 51 -выходная шина шестой строки нижнего слоя ячеек; 52 - выходная шина пятой строки нижнего слоя ячеек; 53 - мемристорный слой нижнего кроссбара; 54 - выходная шина четвертой строки нижнего слоя ячеек; 55 - выходная шина третьей строки нижнего слоя ячеек; 56 - выходная шина второй строки нижнего слоя ячеек; 57 - выходная шина первой строки нижнего слоя ячеек; 58 - мемристорный слой среднего кроссбара; 59 - общая выходная шина третьей строки среднего и верхнего слоя ячеек; 60 - общая выходная шина второй строки среднего и верхнего слоя ячеек; 61 - общая выходная шина первой строки среднего и верхнего слоя ячеек; 62 - мемристорный слой верхнего кроссбара; 63 - первая входная шина первого столбца верхнего слоя ячеек; 64 - вторая входная шина первого столбца верхнего слоя ячеек; 65 - первая входная шина второго столбца верхнего слоя ячеек; 66 - вторая входная шина второго столбца верхнего слоя ячеек; 67 - первая входная шина третьего столбца верхнего слоя ячеек; 68 - вторая входная шина третьего столбца верхнего слоя ячеек; 69 - общий электрод мемристоров; 70 - слаболегированный n-полупроводник; 71 - р-полупроводник; 72 - сильнолегированный n-полупроводник; 73 - первая общая входная шина третьего столбца нижнего и среднего слоев ячеек; 74 - вторая общая входная шина третьего столбца нижнего и среднего слоев ячеек; 75 - первая общая входная шина второго столбца нижнего и среднего слоев ячеек; 76 - вторая общая входная шина второго столбца нижнего и среднего слоев ячеек; 77 - первая общая входная шина первого столбца нижнего и среднего слоев ячеек; 78 - вторая общая входная шина первого столбца нижнего и среднего слоев ячеек.

На фиг. 5. показана топология трехслойной запоминающий матрицы, образованной тремя 3×6 кроссбарами с полупроводниковыми шинами строк, где 79 - выходная шина шестой строки нижнего слоя ячеек / сильнолегированный n-полупроводник; 80 - выходная шина пятой строки нижнего слоя ячеек / сильнолегированный n-полупроводник; 81 - выходная шина четвертой строки нижнего слоя ячеек / сильнолегированный n-полупроводник; 82 - выходная шина третьей строки нижнего слоя ячеек / сильнолегированный n-полупроводник; 83 - выходная шина второй строки нижнего слоя ячеек / сильнолегированный n-полупроводник; 84 - выходная шина первой строки нижнего слоя ячеек / сильнолегированный n-полупроводник; 85 - общая выходная шина третьей строки верхнего и среднего слоев ячеек / сильнолегированный n-полупроводник; 86 - общая выходная шина второй строки верхнего и среднего слоев ячеек / сильнолегированный n-полупроводник; 87 - общая выходная шина первой строки верхнего и среднего слоев ячеек / сильнолегированный n-полупроводник;

Рассмотрим работу устройства.

Предлагаемая 3D запоминающая матрица на основе комплементарной мемристорно-диодной ячейки может работать в двух режимах: режиме записи и режиме чтения данных. Каждая ячейка состоит из двух мемристоров соединенных комплементарно, как показано на фиг. 1. Комплементарность в ячейке позволяет постоянно поддерживать высокое сопротивление между своими контактами 4 и 5 в рабочем режиме, что обеспечивает низкое энергопотребление. При этом возможны три комбинации высокоомного и низкоомного состояний мемристоров в паре. Таким образом, в ячейку можно записать три состояния, если мемристоры работают в режиме ключа и больше трех состояний, если мемристорный материал обеспечивает плавное переключение и несколько устойчивых значений проводимости.

Для записи данных в любую ячейку, например, состоящую из комплементарных мемристоров 3 и 6, на каждый мемристор последовательно по времени подается надпороговое напряжение для изменения их проводимости. Это напряжение поступает с одной стороны через проводящие шины 12, 13 (45, 46), являющиеся контактами мемристоров. С другой стороны напряжение подается через диод Зенера 2 по выходной шине 28 с программирующего драйвера, расположенного на периферии матрицы. Транзистор 30 и диод 29 осуществляют коммутацию тока на общую точку схемы при программировании. Диод Зенера выполняет функцию управляемого напряжением переключателя и работает в режиме пробоя во время записи мемристора. В такой схеме запись данных может производиться одновременно в несколько ячеек по шинам, расположенным параллельно.

В режиме чтения матрицы на контакты 4, 5 выбранной ячейки относительно общей точки схемы подаются низкие напряжения противоположной полярности, абсолютная величина которых меньше порогового напряжения программирования мемристора. В результате комплементарная пара мемристоров образует резистивный делитель напряжения. Напряжение со средней точки делителя через диод Зенера поступает на выходной драйвер. Входная схема драйвера 26 представляет собой многопороговый компаратор, который через прямосмещенный диод Зенера регистрирует уровень напряжения в средней точке комплементарной пары мемристоров, который соответствует состоянию, записанному в выбранной ячейке матрицы.

Новый компонент электроники - комбинированный кроссбар образован из ячеек, содержащих два комплементарных мемристора 3 и 6 с общим электродом, совмещенным с анодом диода Зенера 2, и образующихся в пересечении двух параллельных проводников с одной стороны кроссбара - шин, объединяющих соответствующие электроды мемристоров ячеек 4 и 5 в столбцы, и одного ортогонального к ним проводника с другой стороны, объединяющего катоды диодов Зенера 1 соседних ячеек в строки. На проводниках строк 42 расположены диоды Зенера, разделенные диэлектриком и состоящие из последовательно наносимых слоев сильнолегированного n-полупроводника 49, слаболегированного n-полупроводника 43 и сильнолегированного р-полупроводника 48. На аноде каждого диода располагается общий металлический электрод 44 комплементарных мемристоров, непосредственно соприкасающийся с вышележащим сплошным мемристорным слоем 47, на котором ортогонально проводникам строк расположены шины столбцов 45 и 46.

Сверхбольшая запоминающая матрица изготавливается согласно представленной топологии с помощью вакуумной магнетронной технологии. Сначала на подложку через маску наносятся проводники 51, 52, 54-57 путем распыления металлического катода. Затем пустое пространство между проводниками методом реактивного магнетронного распыления заполняется изолятором (например, диоксидом кремния). Далее через маску (или с помощью сухого травления) последовательно формируются три полупроводниковых слоя диодов Зенера с разной проводимостью 72, 70 и 71 в результате одновременного распыления в магнетроне катодов кремния и легирующей примеси. На диоды Зенера через ту же маску наносится общий металлический электрод 69 будущих комплементарных мемристоров. Свободное пространство между полученными структурами также заполняется диэлектриком. Затем реактивным магнетронным распылением наносится пленка оксида переходного металла (например, TiO2), являющаяся мемристорным слоем 53. Далее на эту пленку через маску наносятся проводники столбцов 73-78 ортогонально шинам строк 51, 52, 54-57 так, чтобы над каждым диодом проходило два проводника. Топология всей трехмерной матрицы выстраивается путем наложения следующего комбинированного кроссбара зеркально предыдущему, при этом проводники строк или столбцов у соседних кроссбаров будут общими.

Вакуумная технология нанесения мемристорного слоя и легированных полупроводниковых слоев диода Зенера в магнетронном технологическом модуле с двумя одновременно распыляющимися катодами является достаточно простой и позволяет изготавливать сверхбольшие запоминающие матрицы, которые в первую очередь могут быть использованы в нейропроцессорах. Для сравнения, при изготовлении 3D логической матрицы, ячейка которой состоит из мемристоров и комплементарных транзисторов, необходимо помимо магнетронного осаждения использовать сочетание нескольких трудоемких вакуумных технологий, таких как термодиффузионное легирование полупроводников для транзисторов (Vinet. M., Batude P., Tabone С.et al. 3D monolithic integration: Technological challenges and electrical results. //Microelectronic Engineering. 2011. Vol. 88. Pp. 331-335.), нанесение промежуточных слоев изолятора между слоями с транзисторами и их последующее выравнивание методом CMP (Zantye Р.В., Kumar A., Sikder А.К. Chemical mechanical planarization for microelectronics applications. //Materials Science and Engineering. 2004. Vol. 45, No 3-6. Pp. 89-220.), а также выполнение переходных отверстий в кремнии по технологии TSV (through silicon vias).

Предложенная 3D запоминающая матрица на основе комплементарной мемристорно-диодной ячейки может найти применение для аппаратной реализации программируемой архитектуры нейронной сети. Архитектура нейронной сети может быть предварительно запрограммирована в матрицу или изменяться в процессе работы. В этом случае сигнал на входные шины должен подаваться импульсами, в частоте следования которых закодирована информация, причем на один вход ячейки импульс приходит неизменным, а на другой - в инвертированном виде. Такой подход является биоморфным, потому что выбирается по аналогии с принципом работы биологических нейроных сетей, где информация кодируется спайками. Импульсы на общей шине создают колебания потенциала, которые поступают на вход драйвера. Входная схема драйвера 26 в этом случае играет роль сумматора, например, построенного по схеме классического интегратора, на выходе которого уровень напряжения определяется частотой поступающих импульсов на вход матрицы. Таким образом, импульсы напряжения в комплементарной паре мемристоров, работающих как делитель напряжения, взвешиваются аналогично синаптическому взвешиванию в нейронной сети, и в зависимости от записанных в мемристорах проводимостях поступают в сумматор.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многослойная логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2682548C2 |

| Запоминающее устройство на основе комплементарной мемристорно-диодной ячейки | 2017 |

|

RU2649657C1 |

| Логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2643650C1 |

| ОДНОЭЛЕКТРОННЫЙ МЕМРИСТОР (НАНОЯЧЕЙКА) И СПОСОБ ПРИМЕНЕНИЯ | 2023 |

|

RU2823967C1 |

| МАТРИЧНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2016 |

|

RU2727767C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ОБРАБОТКИ ДАННЫХ И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1999 |

|

RU2208267C2 |

| Способ генерации случайных чисел с помощью мемристорного источника стохастических сигналов и устройство для его осуществления | 2021 |

|

RU2787560C1 |

| МЕМРИСТОР НА ОСНОВЕ СМЕШАННОГО ОКСИДА МЕТАЛЛОВ | 2011 |

|

RU2472254C9 |

| НИЗКОВОЛЬТНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ БИПОЛЯРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КОМПЛЕМЕНТАРНЫХ СТРУКТУРАХ | 1999 |

|

RU2173915C2 |

| Оптически управляемый мемристор на основе МДП-структуры ITO/ZrO2(Y)/Si с наноостровками Ge | 2022 |

|

RU2803506C1 |

Изобретение относится к области микро- и наноэлектроники. Технический результат заключается в обеспечении высокой степени интеграции элементов, малого энергопотребления и высокого быстродействия устройства. 3D запоминающая матрица на основе комплементарной мемристорно-диодной ячейки, представляющая собой электронное интегральное устройство с энергонезависимой памятью, причем электронное интегральное устройство с энергонезависимой памятью представляет собой 3D структуру, образованную из нанесенных друг на друга комбинированных кроссбаров, состоящих из запоминающих ячеек, содержащих два мемристора с общим электродом, соединенным с одним из контактов диода Зенера, и образующихся в пересечении двух параллельных проводников с одной стороны кроссбара, объединяющих соответствующие электроды мемристоров ячеек в столбцы, и одного ортогонального к ним проводника с другой стороны, объединяющего контакты диодов Зенера соседних ячеек в строки, причем соседние кроссбары ориентированы зеркально по отношению друг к другу и имеют общие шины строк или столбцов. 5 ил.

3D запоминающая матрица на основе комплементарной мемристорно-диодной ячейки, представляющая собой электронное интегральное устройство с энергонезависимой памятью, отличающееся тем, что оно представляет собой 3D структуру, образованную из нанесенных друг на друга комбинированных кроссбаров, состоящих из запоминающих ячеек, содержащих два мемристора с общим электродом, соединенным с одним из контактов диода Зенера, и образующихся в пересечении двух параллельных проводников с одной стороны кроссбара, объединяющих соответствующие электроды мемристоров ячеек в столбцы, и одного ортогонального к ним проводника с другой стороны, объединяющего контакты диодов Зенера соседних ячеек в строки, причем соседние кроссбары ориентированы зеркально по отношению друг к другу и имеют общие шины строк или столбцов.

| Автомобиль-сани, движущиеся на полозьях посредством устанавливающихся по высоте колес с шинами | 1924 |

|

SU2017A1 |

| Автомобиль-сани, движущиеся на полозьях посредством устанавливающихся по высоте колес с шинами | 1924 |

|

SU2017A1 |

| T | |||

| POTTEIGER et al | |||

| "A one Zener diode, one memristor crossbar architecture for a write-time-based PUF", опубл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Г | |||

| КРИВУЛЯ и др | |||

| "Особенности применения наномемристорной логики для проектирования цифровых систем", ВЕСТНИК ХНТУ N1(46), 2013 г., с | |||

| СПОСОБ ПОЛУЧЕНИЯ ЧИСТОГО ГЛИНОЗЕМА И ЕГО СОЛЕЙ ИЗ СИЛИКАТОВ ГЛИНОЗЕМА, ПРОСТЫХ ГЛИН И. Т.П. | 1915 |

|

SU280A1 |

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

| US 9450023 B1, 20.09.2016. | |||

Авторы

Даты

2019-08-15—Публикация

2017-11-07—Подача