Изобретение относится к области микро- и наноэлектроники и может быть использовано для создания сверхбольшой логической матрицы с энергонезависимой памятью и высокой степенью интеграции элементов.

Известно устройство планарной логической матрицы на основе коммутационной ячейки, которая представляет собой двухслойное соединение транзисторной КМОП структуры и одного мемристора (Маевский О.В., Писарев А.Д., Бусыгин А.Н., Удовиченко С.Ю. Логический коммутатор и запоминающее устройство на основе мемристорных ячеек для электрической схемы нейропроцессора // Вестник ТюмГУ. Физико-математическое моделирование. Нефть, газ, энергетика. 2016. №4. С. 100-111). Матрица реализует функцию дизъюнктивной нормальной формы (ДНФ) с возможностью перепрограммируемой коммутации, которая удобна для построения логики работы нейроморфного устройства. Недостатком подхода реализации только ДНФ в коммутируемой логике на мемристорах является нерациональное использование логических ресурсов матрицы при построении логических схем. Другой недостаток построения сверхбольшой логической матрицы в планарной геометрии связан с ограниченными размерами кристалла микропроцессора.

Известно предложение по монолитной трехмерной интеграции памяти и логических схем, которая может значительно повысить производительность и энергоэффективность вычислительной техники Adam G.C. Optimized stateful material implication logic for 3D data manipulation / G.C. Adam, B.D. Hoskins, M. Prezioso, D.V. Strukov et. al. // Nano Research. 2016. V. 9. №12. Pp. 3914-3923). Представлен принцип построения топологии при вертикальной интеграции мемристоров в два слоя без управляющих транзисторов.

Известно устройство 3D логической схемы, которое может быть изготовлено с использованием стандартной КМОП технологии в отдельных слоях и их соединения по технологии Through Silicon Vias (Or-Bach Z, Wurman Z. Integrated circuit with logic 3D / US Patent №8492886 B2 Jul. 23, 2013 Filled Aug. 2, 2012). Электрическое соединение слоев производится спайкой межкремниевых проводников без непосредственного контакта слоев. Недостатком такого устройства является низкая интеграция элементов без применения мемристоров, а также низкая плотность упаковки слоев большой толщины (около 500 мкм).

Задачей, которую решает изобретение, является создание электрической схемы и топологии сверхбольшой логической матрицы на основе мемристорных переключателей при небольшой занимаемой площади на кристалле устройства.

Техническим результатом является высокая степень интеграции элементов, малое энергопотребление и высокое быстродействие устройства.

Это достигается путем объединения планарных (двухслойных) логических матриц в 3D структуру и использования энергонезависимых переключающихся элементов - мемристоров, имеющих малый размер (1 F2) и высокую скорость переключения (менее 30 нс). Создание 3D логической матрицы возможно по известной технологии изготовления многослойных чипов, содержащих КМОП структуры в каждом слое (Vinet. М., Batude P., Tabone С. et al. 3D monolithic integration: Technological challenges and electrical results. // Microelectronic Engineering. 2011. Vol. 88. Pp. 331-335.) Технология предусматривает введение примеси в полупроводник с помощью термической диффузии для транзисторов, выравнивание верхней поверхности разделяющего слои изолятора и изготовление транзисторов в верхних слоях с введением примеси в полупроводник при пониженной температуре, чтобы избежать перегрева структуры. Выравнивание поверхности межслойного диэлектрика выполнятся по методу химико-механической полировки (Zantye Р.В., Kumar A., Sikder А.К. Chemical mechanical planarization for microelectronics applications. // Materials Science and Engineering. 2004. Vol. 45, No 3-6. Pp. 89-220). Приведенные технологии позволяют создавать монолитные 3D структуры на кремнии.

Применение трехмерной организации электрической схемы матрицы значительно уменьшает длину соединительных проводников, что увеличивает быстродействие и снижает энергопотребление по сравнению с планарной геометрией.

Сущность изобретения поясняется на фиг. 1 - фиг. 6.

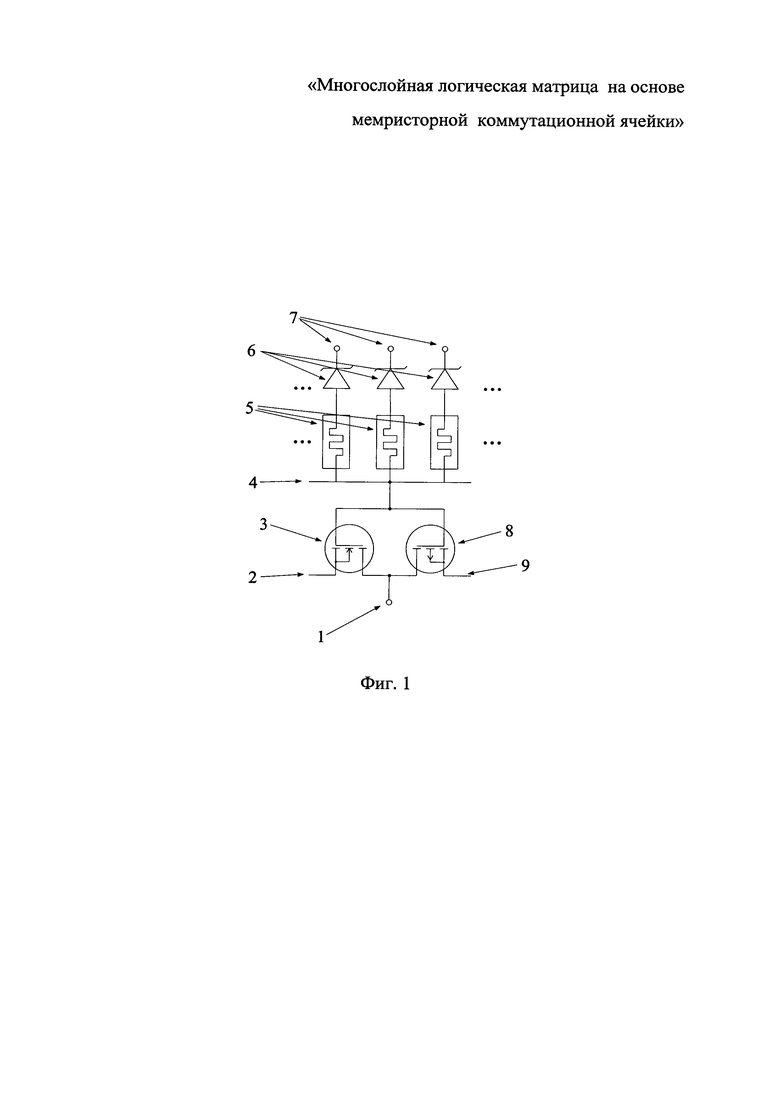

На фиг. 1. представлена электрическая схема элементарной ячейки логической матрицы, где 1 - выход ячейки; 2 - исток n-МОП транзистора; 3 - n-МОП транзистор; 4 - вход КМОП инвертора; 5 - мемристоры; 6 - диоды Зенера; 8 - р-МОП транзистор; 9 - исток р-МОП транзистора.

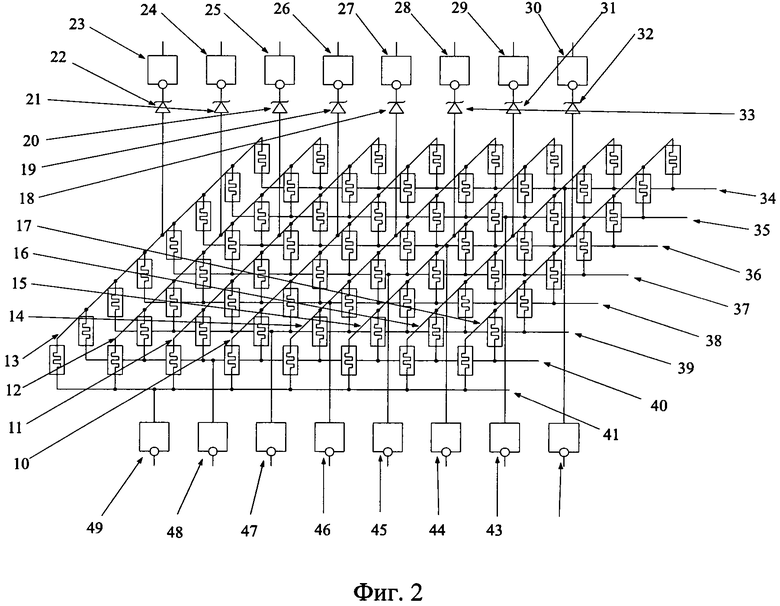

На фиг. 2. представлена электрическая схема логического блока логической матрицы, где 10 - 4й столбец мемристорного кроссбара; 11 - 3й столбец мемристорного кроссбара; 12 - 2й столбец мемристорного кроссбара; 13 - 1й столбец мемристорного кроссбара; 14 - 5й столбец мемристорного кроссбара; 15 - 6й столбец мемристорного кроссбара; 16 - 7й столбец мемристорного кроссбара; 17 - 8й столбец мемристорного кроссбара; 18 - диод Зенера; 19 - диод Зенера; 20 - диод Зенера; 21 - диод Зенера; 22 - диод Зенера; 23 - входной инвертор; 24 - входной инвертор; 25 - входной инвертор; 26 - входной инвертор; 27 - входной инвертор; 28 - входной инвертор; 29 - входной инвертор; 30 - входной инвертор; 31 - диод Зенера; 32 - диод Зенера; 33 - диод Зенера; 34 - 1я строка мемристорного кроссбара; 35 - 2я строка мемристорного кроссбара; 36 - 3я строка мемристорного кроссбара; 37 - 4я строка мемристорного кроссбара; 38 - 5я строка мемристорного кроссбара; 39 - 6я строка мемристорного кроссбара; 40 - 7я строка мемристорного кроссбара; 41 - 8я строка мемристорного кроссбара; 42 - выходной инвертор; 43 - выходной инвертор; 44 - выходной инвертор; 45 - выходной инвертор; 46 - выходной инвертор; 47 - выходной инвертор; 48 - выходной инвертор; 49 - выходной инвертор.

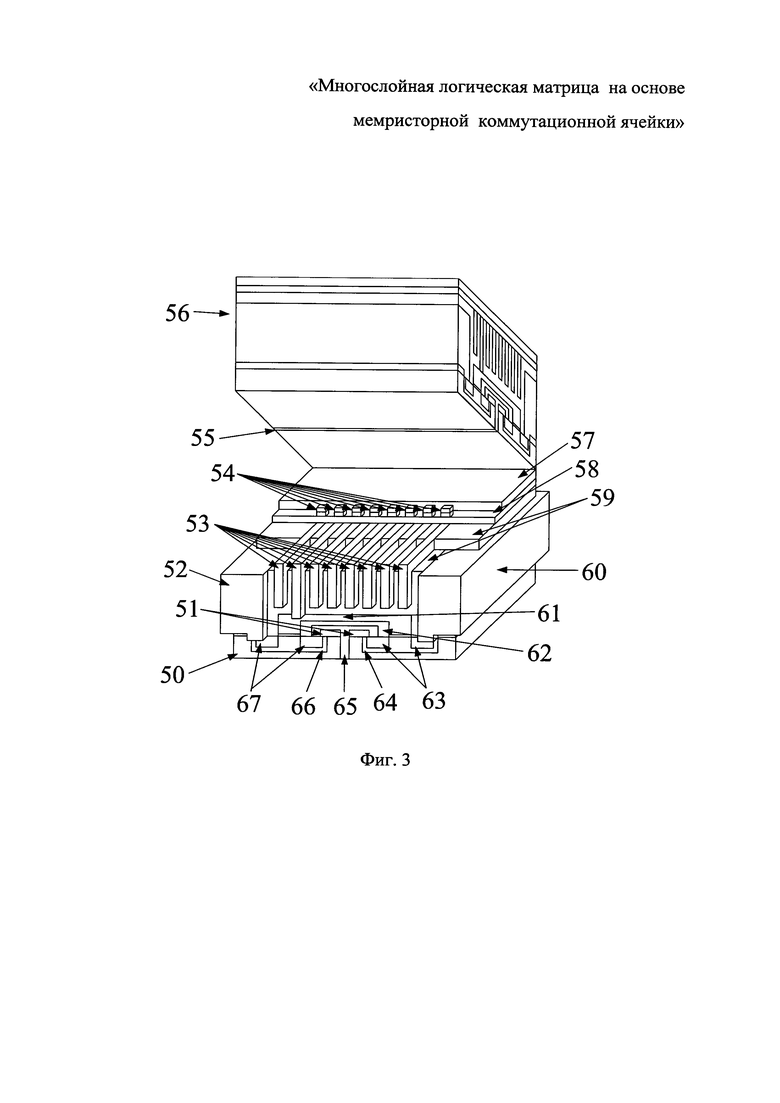

На фиг. 3. представлено изображение топологии 2 элементарных ячеек логической матрицы из соседних вертикальных пластов, где 50 - монокристаллический кремний; 51 - диэлектрик; 52 - шина питания Vss; 53 - сигнальные шины; 54 - диоды Зенера; 55 - верхний проводник кроссбара / выход инвертора вышележащей ячейки; 56 - вышележащая ячейка; 57 - диэлектрик; 58 - мемристивный слой; 59 - диэлектрик; 60 - шина питания Vdd; 61 - поликристаллический кремний/объединенные затворы транзисторов; 62 - диэлектрик; 63 - полупроводник р-типа; 64 -полупроводник n-типа; 65 - выход ячейки; 66 - полупроводник р-типа; 67 - полупроводник n-типа.

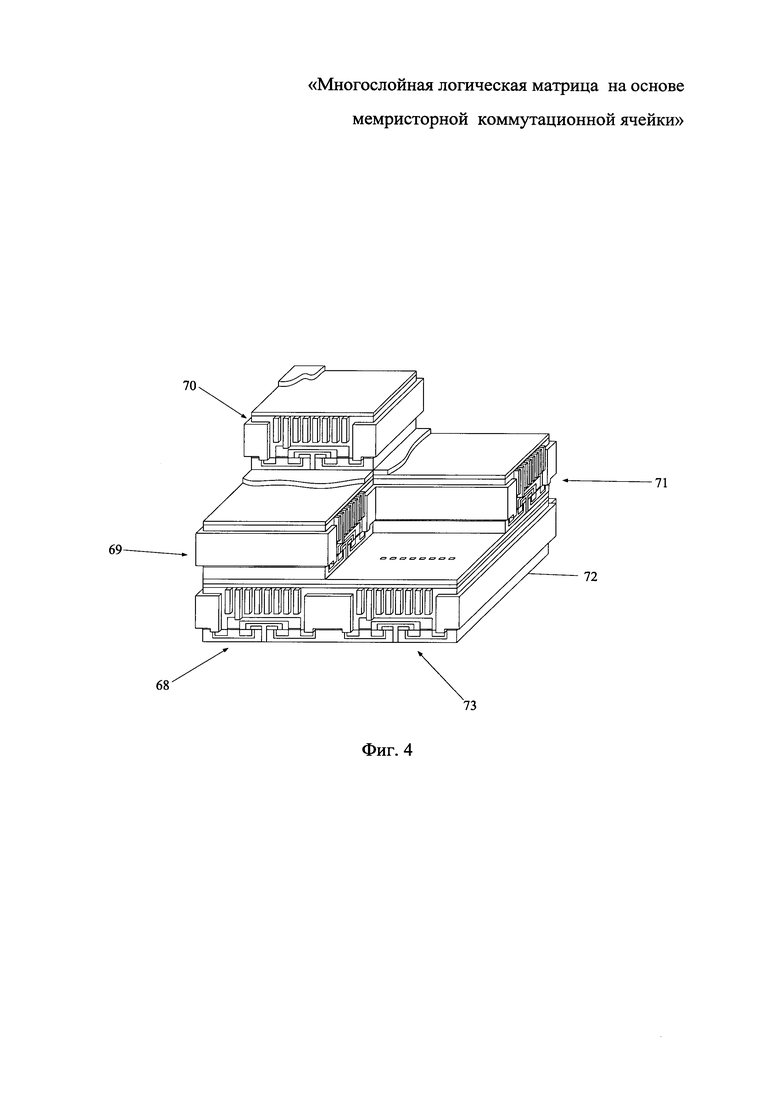

На фиг. 4. приведен принцип пространственного расположения элементарных ячеек, где 68 - ячейка нижнего слоя; 69 - ячейка среднего слоя; 70 - ячейка верхнего слоя; 71 - ячейка среднего слоя; 72 - мемристивный слой; 73 - ячейка нижнего слоя.

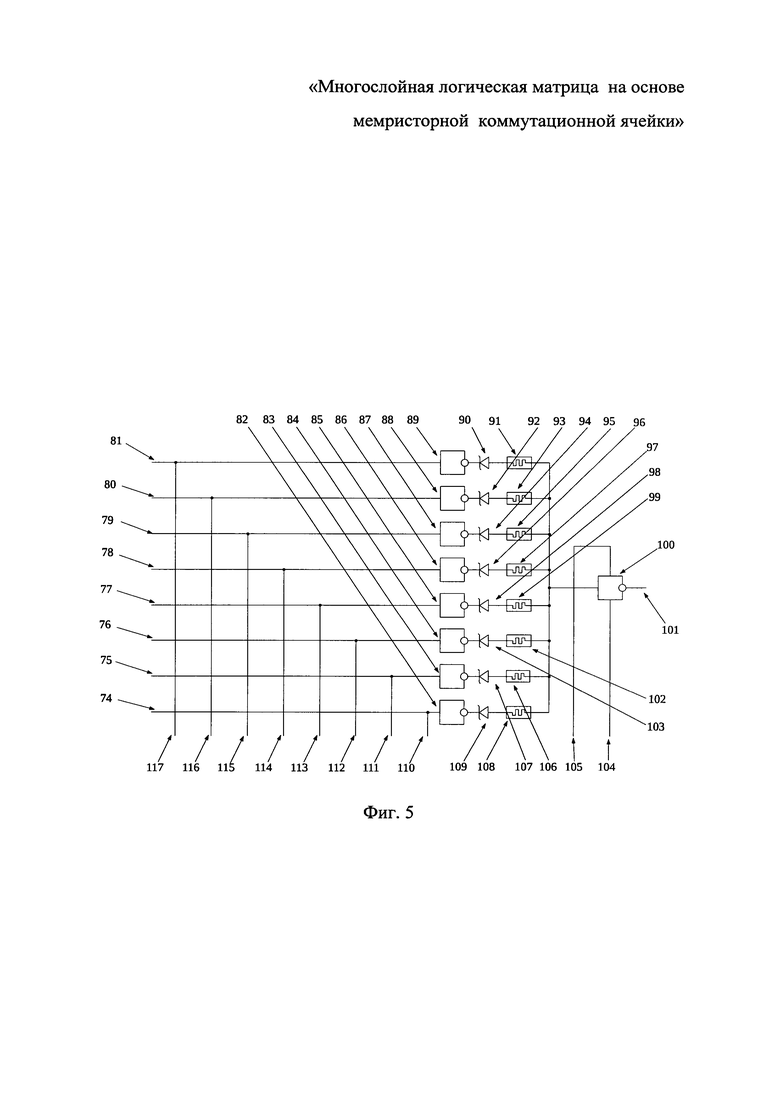

На фиг. 5 представлена электрическая схема межслойного соединения двух элементарных ячеек логической матрицы, где 74 - вход 8го инвертора; 75 - вход 7го инвертора; 76 - вход 6го инвертора; 77 - вход 5го инвертора; 78 - вход 4го инвертора; 79 - вход 3го инвертора; 80 - вход 2го инвертора; 81 - вход 1го инвертора; 82 - 8й инвертор; 83 - 7й инвертор; 84 - 6й инвертор; 85 - 5й инвертор; 86 - 4й инвертор; 87 - 3й инвертор; 88 - 2й инвертор; 89 - 1й инвертор; 90 - диод Зенера; 91 - мемристор; 92 - диод Зенера; 93 - мемристор; 94 - диод Зенера; 95 - мемристор; 96 - диод Зенера; 97 - мемристор; 98 - диод Зенера; 99 - мемристор; 100 - выходной инвертор; 101 - выход инвертора; 102 - мемристор; 103 - диод Зенера; 104 - вход питания инвертора Vdd; 105 - вход питания инвертора Vss; 106 - мемристор; 107 - диод Зенера; 108 - мемристор; 109 - диод Зенера; 110 - шина программирования; 111 - шина программирования; 112 - шина программирования; 113 - шина программирования; 114 - шина программирования; 115 - шина программирования; 116 - шина программирования; 117 - шина программирования.

На фиг. 6 представлена принципиальная электрическая схема соединения двух логических блоков, где 118 - вход питания Vss; 119 - 7й вход логического блока; 120 - 6й вход логического блока; 121 - 5й вход логического блока; 122 - выходные инверторы предыдущего блока; 123 - 4й вход логического блока; 124 - 3й вход логического блока; 125 - 2й вход логического блока; 126 - 1й вход логического блока; 127 - логический блок; 128 - мемристорный кроссбар 8×8; 129 - 1й выход логического блока; 130 - 2й выход логического блока; 131 - 3й выход логического блока; 132 - 4й выход логического блока; 133 - 5й выход логического блока; 134 - 6й выход логического блока; 135 - 7й выход логического блока; 136 - 8й выход логического блока; 137 - вход питания Vdd; 138 - вход питания Vss; 139 - 8й вход программирования; 140 - 7й вход программирования; 141 - 6й вход программирования; 142 - 5й вход программирования; 143 - 4й вход программирования; 144 - 3й вход программирования; 145 - 2й вход программирования; 146 - 1й вход программирования; 147 - 8й вход логического блока; 148 - вход питания Vdd.

Рассмотрим работу устройства.

Электрическая схема элементарной ячейки логической матрицы, показанная на фиг. 1, отличается от использованной в планарной логической матрице: ячейка имеет восемь коммутирующихся через мемристоры 5 входов с разделительными диодами Зенера 6, исключающих возможную перезапись мемристоров при работе матрицы. На напряжениях выше туннельного пробоя диод Зенера позволяет программировать мемристор надпороговым напряжением, проводя ток в обоих направлениях. Использование 8 мемристоров на один инвертор позволяет коммутировать сигнал по многим направлениям, создавая сложные логические зависимости, при этом степень интеграции элементов на кристалле остается высокой, потому что мемристоры занимают маленькую площадь.

Предлагаемая логическая матрица, состоящая из КМОП инверторов и мемристоров, в основном режиме работы реализует сложную булеву функцию, построенную на основе дизъюнктивной многовходовой логики с отрицанием типа «ИЛИ-НЕ», которая предварительно скоммутирована мемристорными переключателями в режиме обучения. Операция ИЛИ производится в мемристорном кроссбаре 10-17 и 34-41, а операцию НЕ выполняет стоящий за ним инвертор 42-49. Элементы многослойной матрицы объединены в кластеры по 8 ячеек с одинаковой принципиальной схемой, которая показана на фиг. 2. Связи между логическими элементами организованы в виде симплексной коммутируемой полносвязанной мемристорной сети по принципу «каждый с каждым» между кластерами разных пластов.

На уровне соединения пластов многослойной матрицы в кластере элементарных ячеек после логической операции «НЕ» сигналы с инверторных выходов могут быть объединены по логике «ИЛИ» с помощью мемристорного кроссбара 10-17 и 34-41. Объединение происходит на входе инвертора следующего кластера, например, 49, элементы которого находятся на нижележащем пласте. Для исключения неопределенности в случае, когда все мемристоры находятся в высокоомном состоянии, входы инверторов подтянуты к нижнему питанию источником тока, имеющим среднее значение тока открытого и закрытого мемристора на подпороговом напряжении. Источники тока реализованы на периферии матрицы и подключены к каждой шине программирования, являющиеся строками кроссбара 34-41.

Возможность перепрограммирования состояния мемристоров обеспечивают специальные схемы драйверы, вынесенные на периферию кристалла. Они подают сигналы на шины программирования, подключенные к контактам мемристоров 34-41, а также управляют напряжением питания и состояния инверторов матрицы. Шины 53 присоединены к каждому инвертору по отдельности и выходят на периферию, как показано на фиг. 3. Питание инверторов осуществляется по параллельным шинам 52 и 60. Во время программирования мемристоров одного кластера драйверы подают на его шины 53 повышенное «надпороговое» напряжение питания. Для исключения взаимовлияния напряжение с других кластеров во время программирования снимается.

Программирование мемристоров 91, 93, 95, 97, 99, 102, 106 осуществляется по шинам 74-81, подключенным к входам соответствующих инверторов 85-89 (см. фиг. 5). Проблему взаимовлияния при программировании мемристоров решает алгоритм управления, реализованный в драйвере, который расположен на периферии кристалла. При программировании драйвер подает подпороговые напряжения на положительные 104 и отрицательные 105 шины питания инверторов не выбранного кластера и надпороговое напряжение для кластера инверторов 82-89 с программируемыми мемристорами 91, 93, 95, 97, 99, 102, 106.

Слой мемристоров соединяет пласты разного уровня, являющиеся аналогами планарных двухслойных логических матриц, содержащие в нижнем слое транзисторы, а в верхнем - мемристоры. На фиг. 3 представлено изображение топологии 2 элементарных ячеек логической матрицы из соседних пластов. Мемристивный материал 58 наносится методом магнетронного напыления. Под мемристивным слоем созданы параллельные проводники 53, горизонтально пронизывающие матрицу и являющиеся контактами мемристоров, которые подключены к затворам КМОП транзисторов 66-67 и 63-64. Каждая шина 53 соединяется с затворами КМОП транзисторов 61 только одной ячейки. Транзисторы ячейки сформированы в нижележащем слое из нелегированного кремния 50 по стандартной КМОП технологии с применение методов литографии, магнетронного напыления, ионной имплантации, низкотемпературной диффузии и плазменного травления.

Топология всего кристалла состоит из одинаковых пластов, состоящих из слоев, наносимых в последовательных технологических операциях так, что каждый верхний пласт перпендикулярно ориентирован к нижнему пласту, при этом образуется трехмерная конструкция, показанная на фиг. 4. Элементарные ячейки при переходе от пласта к пласту соединяются через слой мемристорного материала 58. Выходы инверторов одного пласта не соединяются между собой согласно электрической схеме соединения двух логических блоков (фиг. 6).

Таким образом, существенными преимуществами предложенной конструкции многослойной матрицы многовходовых элементов «ИЛИ-НЕ» является высокая степень интеграции, которая достигается за счет транзисторной трехмерной КМОП структуры и использования мемристорного кроссбара, обладающего небольшим размером и высокой скоростью работы в качестве коммутатора сигналов между слоями. Запись состояний мемристоров осуществляется при помощи шин, проходящих сквозь кристалл и образующих в разных уровнях на перекрестьях связанные кластеры логических элементов. Причем логические элементы внутри кластера соединяются с помощью кроссбара по принципу «каждый с каждым».

В матрице отсутствует проблема затухания сигнала при прохождении большого числа мемристорных коммутаторов, которая обычно проявляется в пассивных кроссбарах. В связи с тем, что после каждого мемристорного слоя установлен инвертор, выполняющий роль формирователя сигнала за счет своего питания, в многослойной матрице количество слоев может быть очень большим.

Предложенная матрица лучше всего подходит для построения логики работы нейроморфного устройства, в котором вес каждой синоптической связи определяется бинарным состоянием мемристоров. Многослойная организация мемристоров с инверторами представляет собой биоморфный подход, который является подобным принципам обработки информации в биологических системах, где информационный сигнал в процессе проходит по кортикальным слоям.

Одна из областей применения представленной многослойной матрицы - это построение электронных систем для распознавания образов с параллельной обработкой информации методом нейронных сетей. В этом случае фоточувствительные пиксельные элементы могут быть нанесены на верхний слой представленной 3D матрицы, так чтобы оптический сигнал попадал на инверторы, расположенные в верхней части матрицы и представлял собой импульсы, несущие информацию о градациях цветовой интенсивности в каждой точке изображения. Вероятности присутствия тех или иных образов в оптических изображениях можно вычислить при параллельном прохождении импульсов через множество логических слоев, состоящих из элементов ИЛИ-НЕ, скоммутированных мемристорными кроссбарами при обучении. Обучение матрицы может выполняться как отдельной операцией, так и в процессе ее работы. Предложенный способ отличается высоким быстродействием и малым энергопотреблением.

Представленная топология позволяет создать сверхбольшую многослойную логическую матрицу с перепрограммируемой коммутацией и с высокой степенью интеграции элементов, которая необходима для построения логики работы нейроморфного процессора.

| название | год | авторы | номер документа |

|---|---|---|---|

| 3D запоминающая матрица на основе комплементарной мемристорно-диодной ячейки | 2017 |

|

RU2697623C2 |

| Логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2643650C1 |

| Запоминающее устройство на основе комплементарной мемристорно-диодной ячейки | 2017 |

|

RU2649657C1 |

| ОДНОЭЛЕКТРОННЫЙ МЕМРИСТОР (НАНОЯЧЕЙКА) И СПОСОБ ПРИМЕНЕНИЯ | 2023 |

|

RU2823967C1 |

| Способ формирования мемристивных структур на основе композитных оксидов с агломератами наночастиц | 2021 |

|

RU2767721C1 |

| МЕМРИСТОР НА ОСНОВЕ СМЕШАННОГО ОКСИДА МЕТАЛЛОВ | 2011 |

|

RU2472254C9 |

| РАДИАЦИОННО-СТОЙКАЯ ЭНЕРГОНЕЗАВИСИМАЯ ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 2014 |

|

RU2563548C2 |

| СПОСОБ УПРАВЛЕНИЯ РАБОТОЙ МЕМРИСТИВНОЙ КОНДЕНСАТОРНОЙ СТРУКТУРЫ МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК | 2018 |

|

RU2706197C1 |

| Устройство считывания для программируемой логической матрицы | 1988 |

|

SU1566410A1 |

| НИЗКОВОЛЬТНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ БИПОЛЯРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КОМПЛЕМЕНТАРНЫХ СТРУКТУРАХ | 1999 |

|

RU2173915C2 |

Использование: для создания сверхбольшой логической матрицы с энергонезависимой памятью и высокой степенью интеграции элементов. Сущность изобретения заключается в том, что многослойная логическая матрица на основе мемристорной коммутационной ячейки, представляющая собой электронное интегральное устройство на основе логических элементов ИЛИ-НЕ, в котором архитектура электрических цепей является трехмерной, а само устройство образовано перпендикулярно ориентированными пластами, коммутируемыми через мемристивные кроссбары, и состоит из ячеек с последовательно формируемыми слоями: монокристаллического кремния со сквозными проводниками по технологии монолитной 3D интеграции; слоем планарных КМОП инверторов, каждый из которых образован двумя комплементарными полевыми транзисторами с объединенными затворами - входом инвертора, объединенными стоками - выходом инвертора и подключенными к соответствующим шинам питания истокам; слоем сигнальных проводников; мемристивным слоем; слоем с диодами Зенера, причем соединенные последовательно с диодами Зенера мемристоры находятся в перекрестиях выходов КМОП инверторов и сигнальных проводников нижележащего пласта. Технический результат - обеспечение возможности высокой интеграции элементов, малого энергопотребления, высокого быстродействия устройства. 6 ил.

Многослойная логическая матрица на основе мемристорной коммутационной ячейки, представляющая собой электронное интегральное устройство на основе логических элементов ИЛИ-НЕ, отличающаяся тем, что архитектура электрических цепей является трехмерной, а само устройство образовано перпендикулярно ориентированными пластами, коммутируемыми через мемристивные кроссбары, и состоит из ячеек с последовательно формируемыми слоями: монокристаллического кремния со сквозными проводниками по технологии монолитной 3D интеграции; слоем планарных КМОП инверторов, каждый из которых образован двумя комплементарными полевыми транзисторами с объединенными затворами - входом инвертора, объединенными стоками - выходом инвертора и подключенными к соответствующим шинам питания истокам; слоем сигнальных проводников; мемристивным слоем; слоем с диодами Зенера, причем соединенные последовательно с диодами Зенера мемристоры находятся в перекрестиях выходов КМОП инверторов и сигнальных проводников нижележащего пласта.

| US 20150349026 A1, 03.12.2015 | |||

| US 8492886 B2, 23.07.2013 | |||

| US 20120182801 A1, 19.07.2012 | |||

| US 9461649 B2, 04.10.2016 | |||

| US 20150249096 A1, 03.09.2015 | |||

| WO 2015016916 A1, 05.02.2015. |

Авторы

Даты

2019-03-19—Публикация

2017-06-27—Подача