Изобретение относится к вычислительной технике и предназначено для обнаружения и коррекции ошибки, возникающей в модулярном коде при вычислении и передаче данных.

В качестве основы для представления модулярных чисел выступает система остаточных классов (СОК), в которой целое число представляется в виде остатков от деления на набор модулей, а арифметические операции над числами заменяются на операциями над остатками. Выполнение операций происходит параллельно без межразрядных переносов, что позволяет эффективно реализовать сложение, вычитание и умножение. Независимость выполнения действий над каждым модулем обеспечивает внутренние корректирующие способности модулярного кода, поскольку каждый остаток содержит информацию о всем числе.

Известна нейронная сеть для обнаружения, локализации и исправления ошибок в системе остаточных классов (Патент РФ №2301442, опубл. 20.06.2007), которая содержит входной слой, нейронные сети конечного кольца для определения синдрома ошибок, блок памяти для хранения констант, нейронные сети для вычисления правильного результата и элемент ИЛИ для определения наличия ошибки.

Недостатком данного устройства является низкое быстродействие, большие аппаратные затраты и жесткие условия, накладываемые на абсолютную надежность каналов по избыточным модулям.

Известна адаптивная параллельно-конвейерная нейронная сеть для коррекции ошибок (Патент РФ №2279131, опубл. 27.06.2006), которая содержит блок обнаружения ошибок, блок реконфигурации и локализации ошибок, блок исправления ошибок, блок нейронной сети конечного кольца формирования цифр в представлении обобщенной позиционной системы.

Недостатками данного устройства являются сложность, которая объясняется наличием большого количества нейронных сетей конечного кольца и низкое быстродействие, которое пропорционально количеству модулей системы остаточных классов.

Наиболее близким к предлагаемому устройству, выбранным в качестве прототипа, является устройство для обнаружения переполнения динамического диапазона, определения ошибки и локализации неисправности вычислительного канала в ЭВМ, функционирующих в системе остаточных классов (Патент РФ №2483346, опубл. 27.05.2013). Устройство содержит входной регистр, содержащий n+r разрядных регистров для временного хранения контролируемого числа А, представленного по модулям p1, р2, …, pn+r, схему формирования проекций Ai числа А по основаниям pi [i=[1,n+r]), (число Ai, полученное из А зачеркиванием цифры α1 называется проекцией числа по основанию pi); блоки памяти, содержащие n+r элементов памяти для хранения констант по модулям pi; сумматор для суммирования произведения разрядных констант и соответствующих цифр разрядов числа; блок анализа на равенство, больше или меньше рабочего диапазона; триггер для запуска и остановки счетчика проекций; блок логических элементов «И», содержащий n+r элементов «И» для локализации неисправного канала pi; входные шины для подачи контролируемого числа А, схему формирования проекций константы, соответствующей рабочему диапазону; блок хранения констант рабочего диапазона, состоящий из n+r элементов; сумматор; шину, сигнализирующую о неисправности pi канала; шину сигнала «ошибка не установлена» и шину для подключения разрядов константы, соответствующей рабочему диапазону; шину «переполнение диапазона и ошибка», сигнализирующую о переполнении рабочего диапазона и появлении ошибки.

Недостатком данного изобретения является ограниченные функциональные возможности, связанные с невозможностью получения скорректированного числа.

Техническим результатом является расширение функциональных возможностей, а именно возможность не только обнаружения, но и коррекции ошибки модулярных чисел.

Данный технический результат достигается тем, что в устройство обнаружения и коррекции ошибки модулярного кода, содержащее n+2 входа остатка αi, где i=1, …, n+2, n+2 регистра хранения остатка αi, блок формирования проекций, n+2 блока хранения произведений kiαi, 2 блока хранения произведений kn+1mn+1 и kn+2mn+2 соответственно, сумматор произведений kiαi, сумматор произведений kn+1mn+1 и kn+2mn+2, счетчик, блок сравнения, n+2 элемента И локализации ошибки по модулю pi, причем каждый из входов остатка αi подключен ко входу соответствующего регистра хранения остатка αi, выходы которых подключены ко входам блока формирования проекций, первые выходы которого подключены к первым входам соответствующих блоков хранения произведений kiαi и блоков хранения произведений k n+1mn+1 и kn+2mn+2, выходы блоков хранения произведений kiαi подключены к входам сумматора произведений kiαi, выходы блоков хранения произведений kn+1mn+1 и kn+2mn+2 соединены со входами сумматора произведений kn+1mn+1 и kn+2mn+2, выход сумматора произведений kiαi подключен к первому входу блока сравнения, выход сумматора произведений kn+1mn+1 и kn+2mn+2 подключен ко второму входу блока сравнения, выход которого соединен со входами соответствующих элементов И локализации ошибки по модулю pi, введены 2 регистра хранения остатков mn+1 и mn+2, блок управления, n+2 регистра хранения скорректированного остатка αi, n+2 выхода скорректированного остатка αi, в блок формирования проекций, содержащий счетчик, добавлено n+2 элемента И формирования проекции αi, 2 элемента И формирования проекций mn+1 и mn+2, в блок управления, содержащий блок сравнения и n+2 элемента И локализации ошибки по модулю pi, добавлены n+3 - битный циклический регистр сдвига, n+2 модулярных умножителя на Pi по модулю pi, n+2 мультиплексора выбора корректного остатка αi, причем выходы регистров хранения остатка αi подключены ко входам блока управления, выходы регистров хранения остатков mn+1 и mn+2 подключены ко входам блока формирования проекций, вторые выходы которого подключены ко вторым входам соответствующих блоков хранения произведений kiαi и блоков хранения произведений kn+1mn+1 и kn+2mn+2, выходы сумматора произведений kiαi и сумматора произведений kn+1mn+1 и kn+2mn+2 подключены ко входам блока управления, управляющий выход которого соединен с управляющим входом блока формирования проекций, выходы блока управления подключены к входам соответствующих регистров хранения скорректированного остатка αi, выходы которых соединены с соответствующими выходами скорректированного остатка αi, при этом старший, n+3-й бит управляющего входа блока формирования проекций соединен со входом счетчика, младший, 1-й бит подключен ко вторым входам элементов И формирования проекции αn+2 и mn+2, 2-й бит подключен ко вторым входам элементов И формирования проекции αn+1 и mn+1, оставшиеся n бит управляющего входа подключены соответственно ко вторым входам элементов И формирования проекции αn, …, α1, к первым входам элементов И формирования проекции αi подключены входы блока формирования проекций, соединенные с регистрами хранения остатка αi, к первым входам элементов И формирования проекции mn+1 и mn+2 подключены входы блока формирования проекций, соединенные с регистрами хранения остатков mn+1 и mn+2, выходы элементов И формирования проекции αi и элементов И формирования проекций mn+1 и mn+2 подключены к соответствующим первым выходам блока формирования проекций, вторые выходы которого соединены с выходом счетчика; в блоке управления первый вход блока сравнения, подключенный к выходу сумматора произведений kiαi, соединен со входами модулярных умножителей на Pi по модулю pi, выход блока сравнения подключен ко входу n+3-битного циклического регистра сдвига, выход которого подключен к управляющему выходу блока управления, а также по битам, начиная с младшего, одновременно к входам элементов И локализации ошибки по модулю pi и управляющим входам мультиплексоров выбора корректного остатка αi соответственно; выходы регистров хранения остатка αi, соединенные со входами блока управления, подключены к входам соответствующих элементов И локализации ошибки по модулю pi, выходы которых подключены ко вторым входам соответствующих мультиплексоров выбора корректного остатка αi, первые входы которых подключены к выходам соответствующих модулярных умножителей на Pi по модулю pi, а выходы подключены к выходам блока управления и соединены с входами соответствующих регистров хранения скорректированного остатка αi.

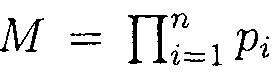

Сущность изобретения основана на следующем математическом аппарате. В системе остаточных классов любое число А<М однозначно представляется набором остатков αi от деления А на взаимно простые модули СОК pi, где αi = A mod pi,  - рабочий диапазон, i=[1,n]. Для обнаружения и исправления ошибки в СОК добавляют два избыточных модуля pn+1 и pn+2 и тогда диапазон избыточной системы остаточных классов составит

- рабочий диапазон, i=[1,n]. Для обнаружения и исправления ошибки в СОК добавляют два избыточных модуля pn+1 и pn+2 и тогда диапазон избыточной системы остаточных классов составит  Разрешенным считается число А=(α1, α2, …, αn, αn+1,αn+2), если А∈[0,М], в случае же А∈(М,Р] можно сказать, что число содержит ошибку. При этом М представляется в избыточной СОК и очевидно, что М=(0, …, 0, mn+1,mn+2), где mn+1=Mmodpn+1, mn+2=Mmodpn+2.

Разрешенным считается число А=(α1, α2, …, αn, αn+1,αn+2), если А∈[0,М], в случае же А∈(М,Р] можно сказать, что число содержит ошибку. При этом М представляется в избыточной СОК и очевидно, что М=(0, …, 0, mn+1,mn+2), где mn+1=Mmodpn+1, mn+2=Mmodpn+2.

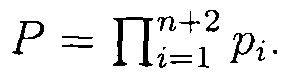

Для эффективной аппаратной реализации берут относительное приближенное значение

,

,

где  - константа выбранной СОК,

- константа выбранной СОК,  - мультипликативная инверсия. В данном случае для определения ошибки используется сравнение относительной величины

- мультипликативная инверсия. В данном случае для определения ошибки используется сравнение относительной величины  с константой

с константой  .

.

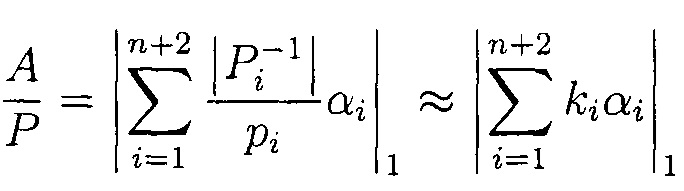

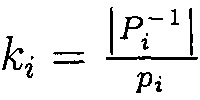

В для обнаружения и исправления ошибок применяется метод проекций, который заключается в следующем. Предполагают, что ошибка допущена по первому модулю p1 и повторяют вычисления без участия этого модуля, т.е. берут в качестве избыточного диапазона  , для нового диапазона вычисляют новые константы ki, и в конечном счете сравнивают

, для нового диапазона вычисляют новые константы ki, и в конечном счете сравнивают  с константой

с константой  . В случае, если

. В случае, если  , то считают, что ошибка произошла по модулю pi и для нахождения точного значения остатка А по модулю р1 умножают

, то считают, что ошибка произошла по модулю pi и для нахождения точного значения остатка А по модулю р1 умножают  на Р1 и находят остаток по модулю р1. В случае

на Р1 и находят остаток по модулю р1. В случае  можно сказать, что ошибка еще присутствует и для ее обнаружения и исправления вместо pi исключают р2 и проводят аналогичную проверку. Такие проекции строятся по всем модулям p1, …, pn+2.

можно сказать, что ошибка еще присутствует и для ее обнаружения и исправления вместо pi исключают р2 и проводят аналогичную проверку. Такие проекции строятся по всем модулям p1, …, pn+2.

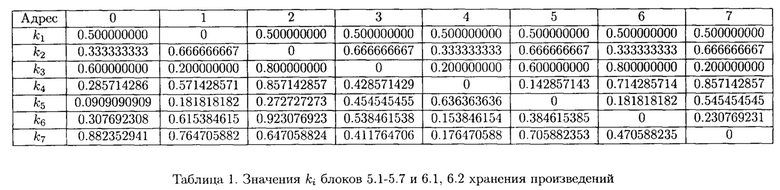

Значения констант k1 берут с точностью N, необходимой для корректных вычислений.

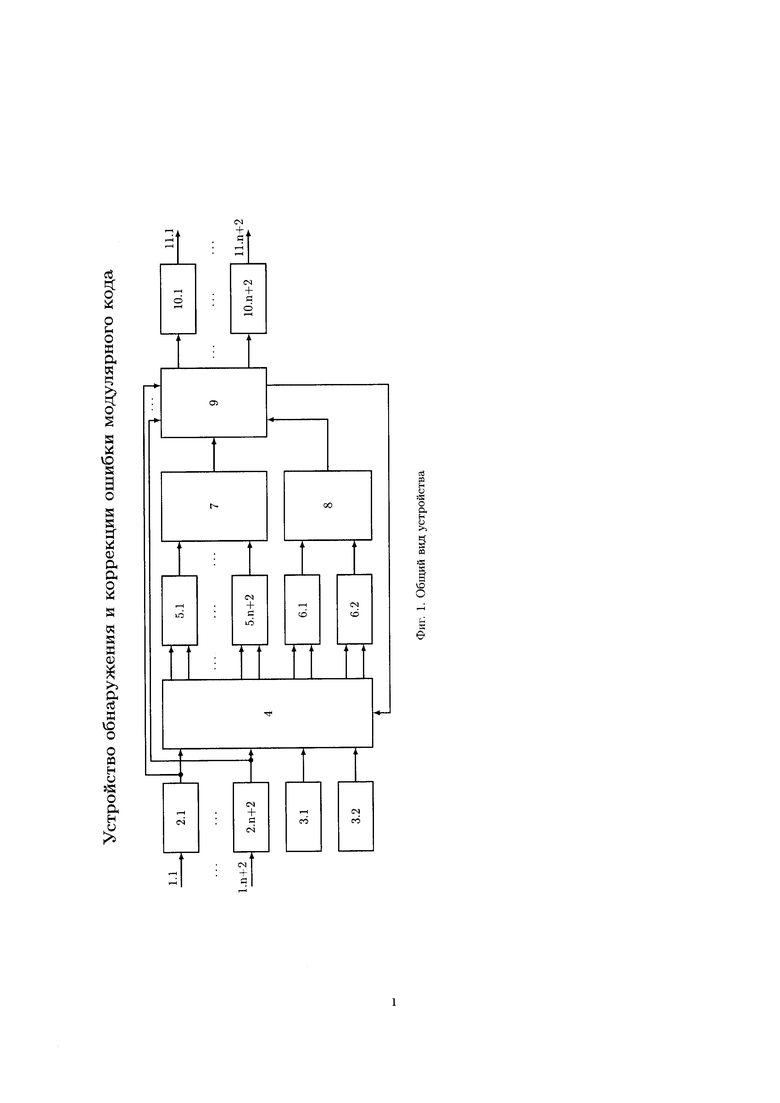

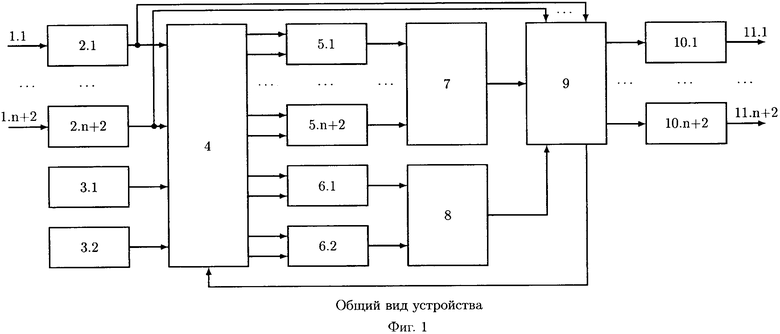

Данное устройство обнаружения и коррекции ошибки модулярного кода поясняется фигурами 1-3. На фигуре 1 представлен общий вид устройства, которое содержит входы 1.i остатка αi, где i=1, …, n+2, регистры 2.i хранения остатка αi, регистры 3.1 и 3.2 хранения остатков mn+1 и mn+2 соответственно, блок формирования проекций 4, блоки 5.i хранения произведений kiαi, блоки 6.1 и 6.2 хранения произведений kn+1mn+1 и kn+2mn+2 соответственно, сумматор 7 произведений kiαi, сумматор 8 произведений kn+1mn+1 и kn+2mn+2, блок управления 9, регистры 10.i храпения скорректированного остатка αi, выходы 11.i скорректированного остатка αi.

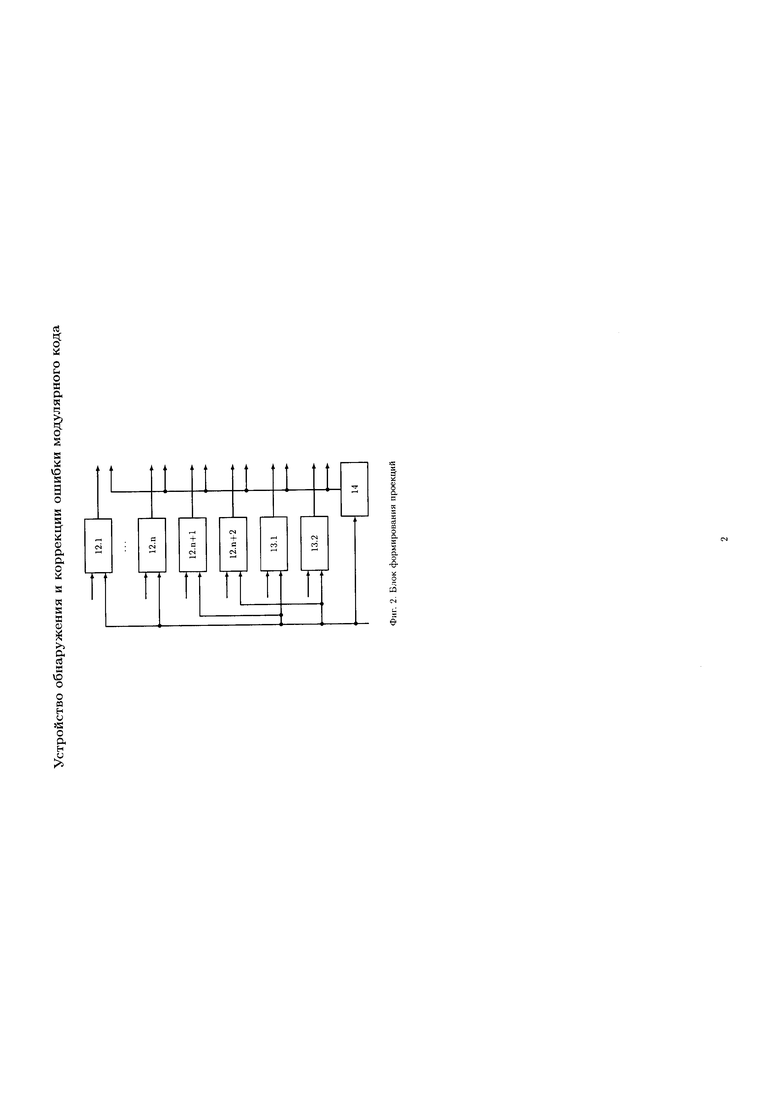

На фиг. 2 показано устройство блока формирования проекций 4, состоящего из элементов И 12.i формирования проекций αi, элементов И 13.1 и 13.2 формирования проекций mn+1 и mn+2 соответственно и счетчика 14.

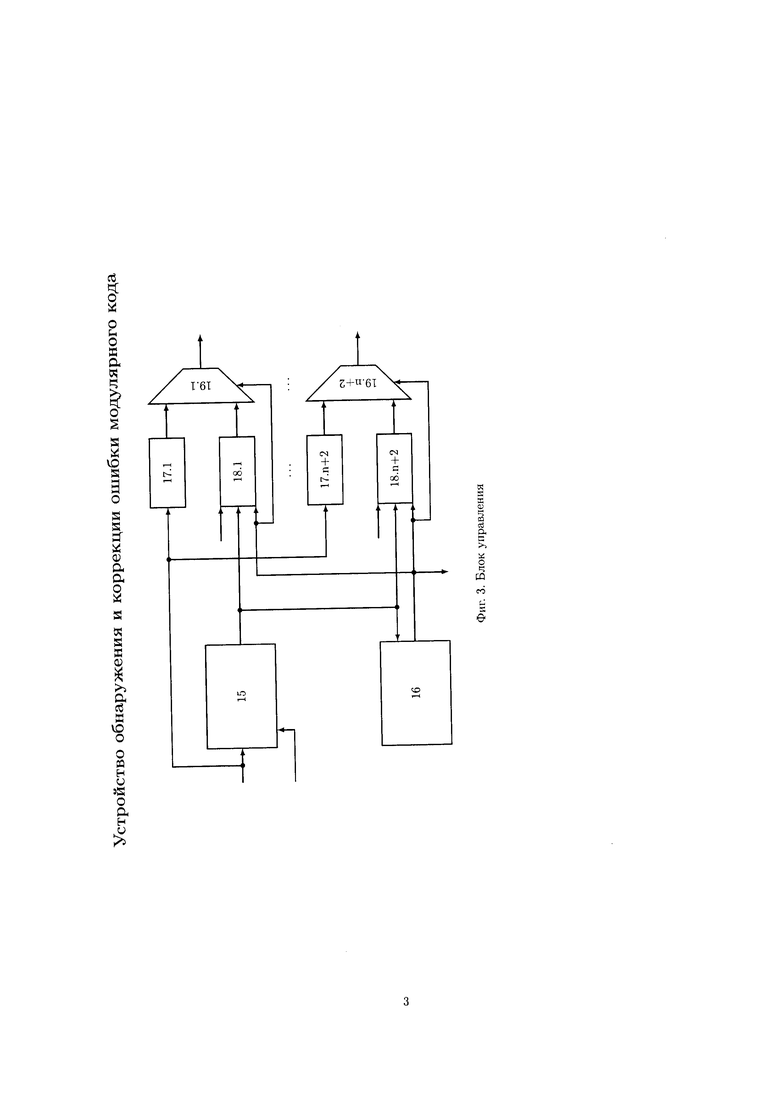

На фиг. 3 представлен блок управления 9, который состоит из блока сравнения 15, n+3-битного циклического регистра сдвига 16, модулярных умножителей 17.i на Pi по модулю pi, элементов И 18.i локализации ошибки по модулю pi, мультиплексоров 19.i выбора корректного остатка αi.

Поясним работу устройства примерами. Пусть задана система остаточных классов с модулями р1=2, p2=3, р3=5, р4=7, р5=11, р6=13, р7=17, следовательно n=5. Значение рабочего диапазона М=2310. В качестве сомножителей в модулярных умножителях 17.i на Pi по модулю pi используются следующие значения: Р1=255255, Р2=170170, Р3=102102, Р4=72930, Р5=46410, Р6=39270, Р7=30030.

В блок 5.1 хранения произведения k1α1 записывают все произведения k1⋅α1 при α1=[0,p1)=[0,1] и ki, выбираемом из Таблицы 1 в зависимости от адреса со счетчика 14. Так, например, на вход блока 5.1 хранения произведения k1α1 подается значение α1=1 и адрес 0, тогда k1=0.5 и на выход блока 5.1 хранения произведения k1α1 будет подано значение 0.5.

Аналогично в блоке 5.2 хранения произведения k2α2 записаны все произведения k2⋅α2 при α2=[0,р2)=[0,2] и k2, выбираемом из Таблицы 1 в зависимости от адреса со счетчика 14. В блоке 5.3 хранения произведения k3α3 записаны все произведения k3⋅α3 при α3=[0,р3)=[0,4] и k3, выбираемом из Таблицы 1 в зависимости от адреса со счетчика 14. В блоке 5.4 хранения произведения k4α4 записаны все произведения k4⋅α4 при α4=[0,p4)=[0,6] и k4, выбираемом из Таблицы 1 в зависимости от адреса со счетчика 14. В блоке 5.5 хранения произведения k5α5 записаны все произведения k5⋅α5 при α5=[0,p5)=[0,10] и k5, выбираемом из Таблицы 1 в зависимости от адреса со счетчика 14. В блоках 5.6 хранения произведения k6α6 и 6.1 хранения произведения k6m6 записаны все произведения k6⋅α6 и k6⋅m6 при α6=[0,р6)=[0,12], m6={0,М mod р6}={0,9} и k6, выбираемом из Таблицы 1 в зависимости от адреса со счетчика 14. В блоках 5.7 хранения произведения k7α7 и 6.2 хранения произведения k7m7 записаны все произведения k7⋅α7 и k7⋅m7 при α7=[0,р7)=[0,16], m7={0,М mod р7}={0,15} и k7, выбираемом из Таблицы 1 в зависимости от адреса со счетчика 14.

Рассмотрим конструкцию и принцип работы n+3-битного циклического регистра сдвига 16. В начале работы он содержит значение "0111 …11". Старший бит, который на первом шаге равен 0 подается на счетчик 14, который подает адрес 0 па блоки 5.1-5.7 и 6.1-6.2 хранения произведений kiαi и k6m6 и k7m7. Остальные биты данного числа подаются на элементы И 12.1-12.7 формирования проекций αi, элементы И 13.1-13.2 формирования проекций m6 и m7, элементы И 18.1-18.7 локализации ошибки по модулю pi. В случае возникновения ошибки с блока сравнения 15 в n+3-битный циклический регистр сдвига 16 поступает сигнал и его значение меняется на "1011 …11". Тогда на счетчик 14 подается старший бит, равный 1 и адрес 1 подается на блоки 5.1-5.7 и 6.1-6.2 хранения произведений kiαi и k6m6 и k7m7. Остальные биты данного числа подаются на элементы И 12.1-12.7 формирования проекций αi, элементы И 13.1-13.2 формирования проекций m6 и m7, элементы И 18.1-18.7 локализации ошибки по модулю pi. При этом n+2-й бит со значением 0 подается на элемент И 12.1 формирования проекций α1 и элемент И 18.1 локализации ошибки по модулю p1 что соответствует вычеркиванию первого основания в методе проекций. Аналогично пулевой бит на каждом шаге сдвигается вправо до достижения значения "1111 …10", при этом нулевой бит во всех случаях в результате логического умножения подает на выход соответствующих элементов нулевое значение, что означает выбор проекции.

Рассмотрим работу устройства на примере значения А=(1,0,1,6,10,12,12)=2001. На входы 1.1-1.7 остатков α1, …, α7 подаются соответственно значения 1,0,1,6,10,12,12, которые затем записываются в регистры 2.1-2.7 хранения остатков α1, …, α7. Значения поступают в блок формирования проекций 4, где проходя через элементы И 12.1-12.7 формирования проекций α1, …, α7 поступают на соответствующие первые входы блоков 5.1-5.7 хранения произведений kiαi, на второй вход которых подается адрес 0. С выходов блоков 5.1-5.7 хранения произведений kiαi значения соответствующих произведений поступают на сумматор 7 произведений kiαi где происходит суммирование по модулю 1 и на выходе сформируется значение, эквивалентное 0.0039196. В это время аналогичные процессы проходят для коэффициентов m6 и m7 и на выходе сумматора 8 произведений k6m6 и k7m7 получится значение 0.0045249. В блоке сравнения 15 данные значения сравниваются и поскольку 0.0039196<0.0045249, то на выходе блока сравнения 16 будет значение 1, которое поступает на входы элементов И 18.1-18.7 локализации ошибки по модулю pi, на вход которых также поступают значения 1,0,1,6,10,12,12 с выходов регистров 2.1-2.7 хранения остатков α1, …, α7. С выхода n+3-битного циклического регистра сдвига 16 на входы элементов И 18.1-18.7 локализации ошибки по модулю pi и на управляющие входы мультиплексоров 19.1-19.7 выбора корректного остатка αi поступают значения 1. Таким образом, мультиплексоры 19.1-19.7 выбора корректного остатка αi подают значения 1,0,1,6,10,12,12 с выходов элементов И 18.1-18.7 локализации ошибки по модулю pi на соответствующие регистры 10.1-10.7 хранения скорректированного остатка αi, откуда значения поступают на выходы 11.1-11.7 скорректированного остатка α1, …, α7. Таким образом на выход устройства подается корректное значение.

Рассмотрим случай, когда по третьему основанию возникла ошибка и на входы 1.1-1.7 остатков α1, …, α7 поступило значение (1,0,4,6,10,12,12)=410409. Работа устройства происходит аналогично и на выходе сумматора 7 произведений kiαi формируется сигнал, эквивалентный 0.8039196. Поскольку 0.8039196>0.0045249, то на выходе блока сравнения 16 будет значение 0, и в результате на выходах 11.1-11.7 скорректированного остатка α1, …, α7 будут значения 0, при этом сигнал 0 с выхода блока сравнения 16 поступает на вход n+3-битного циклического регистра сдвига 16, где происходит сдвиг значения и формирования первой проекции в результате которой выходы элемента И 12.1 формирования проекций α1 и элемента И 18.1 локализации ошибки по модулю p1 будут нулевыми, а значение счетчика изменится на 1, что соответствует адресу 1 Таблицы 1.

Аналогично происходят вычисления сумм и на выходе сумматора 7 произведений kiαi формируется сигнал, эквивалентный 0.6078392, на выходе сумматора 8 произведений k6m6 и k7m7 формируется сигнал, эквивалентный 0.0090497 и поскольку 0.6078392>0.0090497, то на выходе блока сравнения 16 будет значение 0, что соответствует наличию ошибки и в n+3-битном циклическом регистре сдвига 16 происходит сдвиг и формирование второй проекции.

В результате вычислений по второй проекции на выходе сумматора 7 произведений kiαi формируется сигнал, эквивалентный 0.4117588, на выходе сумматора 8 произведений k6m6 и k7m7 формируется сигнал, эквивалентный 0.0135747 и поскольку 0.4117588>0.0135747, то на выходе блока сравнения 16 будет значение 0, что соответствует наличию ошибки и в n+3-битном циклическом регистре сдвига 16 происходит сдвиг и формирование третьей проекции.

В результате вычислений по третьей проекции па выходе сумматора 7 произведений kiαi формируется сигнал, эквивалентный 0.0195980, на выходе сумматора 8 произведений k6m6 и k7m7 формируется сигнал, эквивалентный 0.0226244 и поскольку 0.0195980<0.0226244, то на выходе блока сравнения 16 будет значение 1, что соответствует отсутствию ошибки и следующий сдвиг в n+3-битном циклическом регистре сдвига 16 не происходит. Следовательно ошибка произошла по третьему основанию. Значение 0.0195980 с выхода сумматора 7 произведений kiαi, поступает па модулярный умножитель 17.3 на Р3 по модулю р3, на выходе которого формируется значение 1. Поскольку значение, подаваемое на управляющий вход мультиплексора 19.3 выбора корректного остатка α3, равно нулю, то на выход подается значение 1 с выхода модулярного умножителя 17.3 на Р3 по модулю р3. На остальные управляющие входы мультиплексоров 19.1-19.2, 19.4-19.7 выбора корректного остатка αi подаются значения 1 и на выход подаются значения с соответствующих элементов И 18.1-18.2, 18.4-18.7 локализации ошибки по модулю pi, которые равны полученным αi, которые хранятся в регистрах 2.1-2.7 хранения остатков Таким образом на выходы 11.1-11.7 скорректированного остатка α1, …, α7 поступают значения 1,0,1,6,10,12,12, что соответствует исправленному значению.

Устройство обнаружения и коррекции ошибки модулярного кода

| название | год | авторы | номер документа |

|---|---|---|---|

| Система распределенного хранения данных | 2021 |

|

RU2780148C1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПЕРЕПОЛНЕНИЯ ДИНАМИЧЕСКОГО ДИАПАЗОНА, ОПРЕДЕЛЕНИЯ ОШИБКИ И ЛОКАЛИЗАЦИИ НЕИСПРАВНОСТИ ВЫЧИСЛИТЕЛЬНОГО КАНАЛА В ЭВМ, ФУНКЦИОНИРУЮЩИХ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2011 |

|

RU2483346C1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ОБНАРУЖЕНИЯ, ЛОКАЛИЗАЦИИ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2005 |

|

RU2301442C2 |

| Устройство коррекции ошибок в модулярном коде на основе расширения системы оснований | 2017 |

|

RU2652446C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАКА МОДУЛЯРНОГО ЧИСЛА | 2011 |

|

RU2503995C2 |

| АДАПТИВНАЯ ПАРАЛЛЕЛЬНО-КОНВЕЙЕРНАЯ НЕЙРОННАЯ СЕТЬ ДЛЯ КОРРЕКЦИИ ОШИБОК | 2003 |

|

RU2279131C2 |

| Система надежного облачного хранения с регулируемой избыточностью данных | 2021 |

|

RU2782681C1 |

| УСТРОЙСТВО СПЕКТРАЛЬНОГО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ ОШИБОК В КОДАХ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ | 2005 |

|

RU2301441C2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД С ПЕРЕСЧЕТОМ ОРТОГОНАЛЬНЫХ БАЗИСОВ | 2005 |

|

RU2298873C1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ПРЕОБРАЗОВАНИЯ ОСТАТОЧНОГО КОДА В ДВОИЧНЫЙ ПОЗИЦИОННЫЙ КОД | 2006 |

|

RU2318238C1 |

Изобретение относится к вычислительной технике и предназначено для обнаружения и коррекции ошибки, возникающей в модулярном коде при вычислении и передаче данных. Техническим результатом является обеспечение возможности коррекции ошибки модулярных чисел. Устройство содержит n+2 входа остатка αi (где i=1, …, n+2), n+2 регистров хранения остатка αi, 2 регистра хранения остатков mn+1 и mn+2, блок формирования проекций, n+2 блока храпения произведений kiαi, 2 блока хранения произведений kn+1mn+1 и kn+2mn+2, сумматор произведений kiαi, сумматор произведений kn+1mn+1 и kn+2mn+2, блок управления, n+2 регистра хранения скорректированного остатка αi, n+2 выхода скорректированного остатка αi. 3 ил., 1 табл.

Устройство обнаружения и коррекции ошибки модулярного кода, содержащее n+2 входа остатка αi, где i = 1, …, n+2, n+2 регистра хранения остатка αi, блок формирования проекций, n+2 блока хранения произведений kiαi, 2 блока храпения произведений kn+1mn+1 и kn+2mn+2 соответственно, сумматор произведений kiαi, сумматор произведений kn+1mn+1 и kn+2mn+2, счетчик, блок сравнения, n+2 элемента И локализации ошибки по модулю pi, причем каждый из входов остатка αi подключен ко входу соответствующего регистра хранения остатка αi, выходы которых подключены ко входам блока формирования проекций, первые выходы которого подключены к первым входам соответствующих блоков хранения произведений kiαi и блоков хранения произведений kn+1mn+1 и kn+2mn+2, выходы блоков хранения произведений kiαi подключены к входам сумматора произведений kiαi, выходы блоков хранения произведений kn+1mn+1 и kn+2mn+2 соединены со входами сумматора произведений kn+1mn+1 и kn+2mn+2, выход сумматора произведений kiαi подключен к первому входу блока сравнения, выход сумматора произведений kn+1mn+1 и kn+2mn+2 подключен ко второму входу блока сравнения, выход которого соединен со входами соответствующих элементов И локализации ошибки по модулю pi, отличающееся тем, что в него введены 2 регистра храпения остатков mn+1 и mn+2, блок управления, n+2 регистра хранения скорректированного остатка αi, n+2 выхода скорректированного остатка αi, в блок формирования проекций, содержащий счетчик, добавлено n+2 элемента И формирования проекции αi, 2 элемента И формирования проекций mn+1 и mn+2, в блок управления, содержащий блок сравнения и n+2 элемента И локализации ошибки по модулю pi, добавлены n+3-битный циклический регистр сдвига, n+2 модулярных умножителя на Pi по модулю pi, n+2 мультиплексора выбора корректного остатка αi, причем выходы регистров хранения остатка αi подключены ко входам блока управления, выходы регистров хранения остатков mn+1 и mn+2 подключены ко входам блока формирования проекций, вторые выходы которого подключены ко вторым входам соответствующих блоков хранения произведений kiαi и блоков хранения произведений kn+1mn+1 и kn+2mn+2, выходы сумматора произведений kiαi и сумматора произведений kn+1mn+1 и kn+2mn+2 подключены ко входам блока управления, управляющий выход которого соединен с управляющим входом блока формирования проекций, выходы блока управления подключены к входам соответствующих регистров хранения скорректированного остатка αi, выходы которых соединены с соответствующими выходами скорректированного остатка αi, при этом старший, n+3-й бит управляющего входа блока формирования проекций соединен со входом счетчика, младший, 1-й бит подключен ко вторым входам элементов И формирования проекции αn+2 и mn+2, 2-й бит подключен ко вторым входам элементов И формирования проекции αn+1 и mn+1, оставшиеся n бит управляющего входа подключены соответственно ко вторым входам элементов И формирования проекции αn, … ,α1, к первым входам элементов И формирования проекции αi подключены входы блока формирования проекций, соединенные с регистрами хранения остатка αi, к первым входам элементов И формирования проекции mn+1 и mn+2 подключены входы блока формирования проекций, соединенные с регистрами хранения остатков mn+1 и mn+2, выходы элементов И формирования проекции αi и элементов И формирования проекций mn+1 и mn+2 подключены к соответствующим первым выходам блока формирования проекций, вторые выходы которого соединены с выходом счетчика; в блоке управления первый вход блока сравнения, подключенный к выходу сумматора произведений kiαi, соединен со входами модулярных умножителей на Pi по модулю pi, выход блока сравнения подключен ко входу n+3-битного циклического регистра сдвига, выход которого подключен к управляющему выходу блока управления, а также по битам, начиная с младшего, одновременно к входам элементов И локализации ошибки по модулю pi и управляющим входам мультиплексоров выбора корректного остатка αi соответственно; выходы регистров хранения остатка αi, соединенные со входами блока управления, подключены к входам соответствующих элементов И локализации ошибки по модулю pi, выходы которых подключены ко вторым входам соответствующих мультиплексоров выбора корректного остатка αi, первые входы которых подключены к выходам соответствующих модулярных умножителей на Pi по модулю pi, а выходы подключены к выходам блока управления и соединены с входами соответствующих регистров хранения скорректированного остатка αi.

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПЕРЕПОЛНЕНИЯ ДИНАМИЧЕСКОГО ДИАПАЗОНА, ОПРЕДЕЛЕНИЯ ОШИБКИ И ЛОКАЛИЗАЦИИ НЕИСПРАВНОСТИ ВЫЧИСЛИТЕЛЬНОГО КАНАЛА В ЭВМ, ФУНКЦИОНИРУЮЩИХ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2011 |

|

RU2483346C1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ОБНАРУЖЕНИЯ, ЛОКАЛИЗАЦИИ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2005 |

|

RU2301442C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ИСПРАВЛЕНИЯ ОШИБОК В ИЗБЫТОЧНОМ МОДУЛЯТОРНОМ КОДЕ | 1991 |

|

RU2022472C1 |

| Устройство для обнаружения ошибок в модулярном коде | 1985 |

|

SU1295528A1 |

| JPS 63286026 A, 22.11.1988 | |||

| JPS6328133 A, 05.02.1988 | |||

| JPS 5544691 A, 29.03.1980. | |||

Авторы

Даты

2018-05-07—Публикация

2017-07-21—Подача