Область техники, к которой относится изобретение

Настоящие технологии, в общем, относятся к доступу к памяти. Более конкретно, настоящие технологии относятся к постоянно доступному пути к памяти сверхнизкой мощности.

Уровень техники

Мобильные SOC включают в себя множество автономных подсистем, таких как модем, аудиоподсистема, датчики или концентратор датчиков, криптографические подсистемы и т.п., которые должны быть активными во время всех состояний питания системы. Компьютерные устройства обычно переходят во множество различных состояний питания. Каждая из автономных подсистем может быть разработана с возможностями внутренней памяти, что обеспечивает максимальную эффективность потребления энергии на основе рабочих нагрузок этих подсистем. SOC с интегрированными подсистемами может потреблять энергию для того, чтобы сделать доступным путь для передачи данных в память и также для поддержания требований качества обслуживания (QoS) для каждой подсистемы. Использование общего пути к памяти может не удовлетворять требованиям латентности подсистем.

Краткое описание чертежей

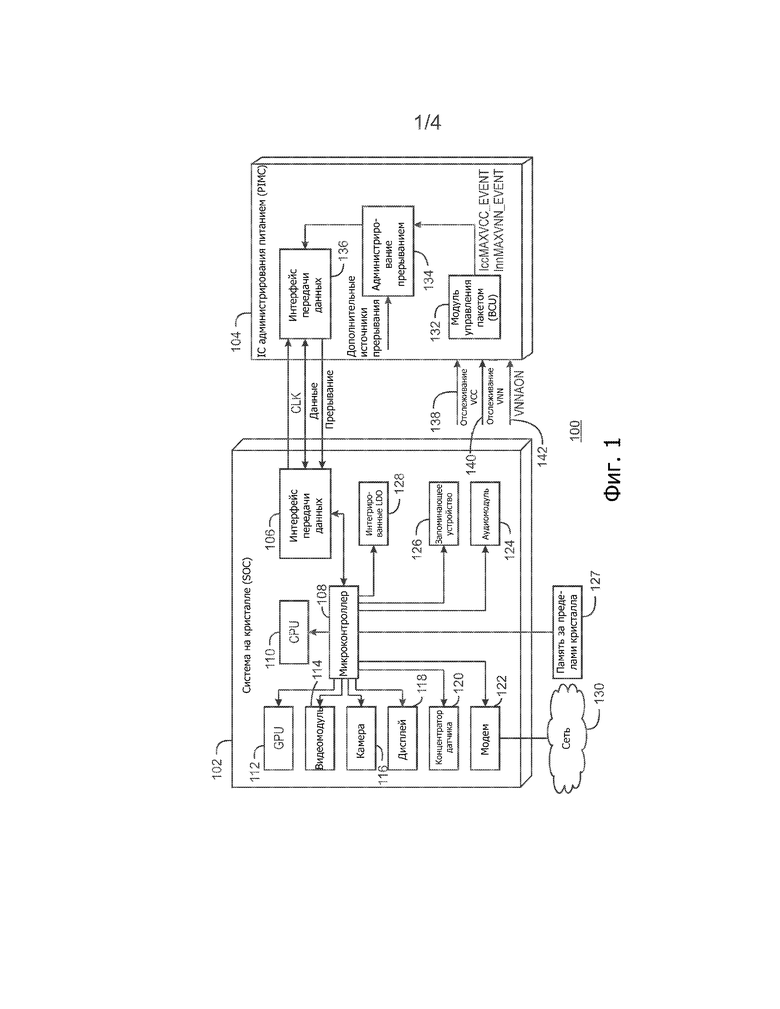

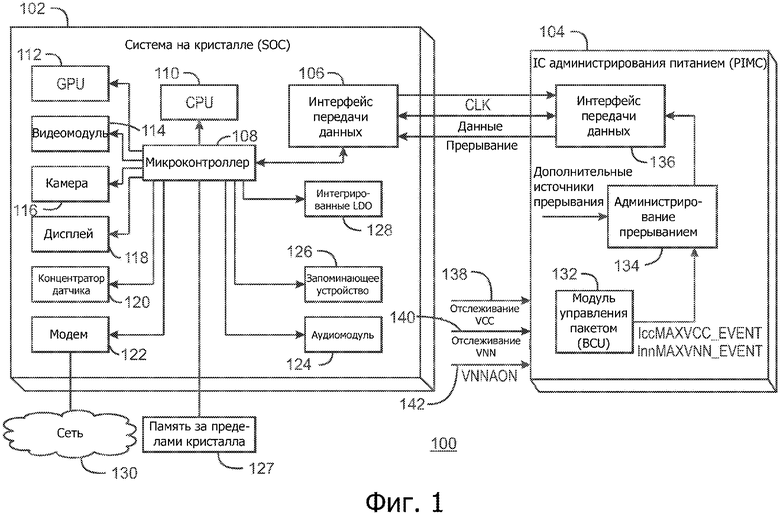

На фиг. 1 показана блок-схема компьютерной системы;

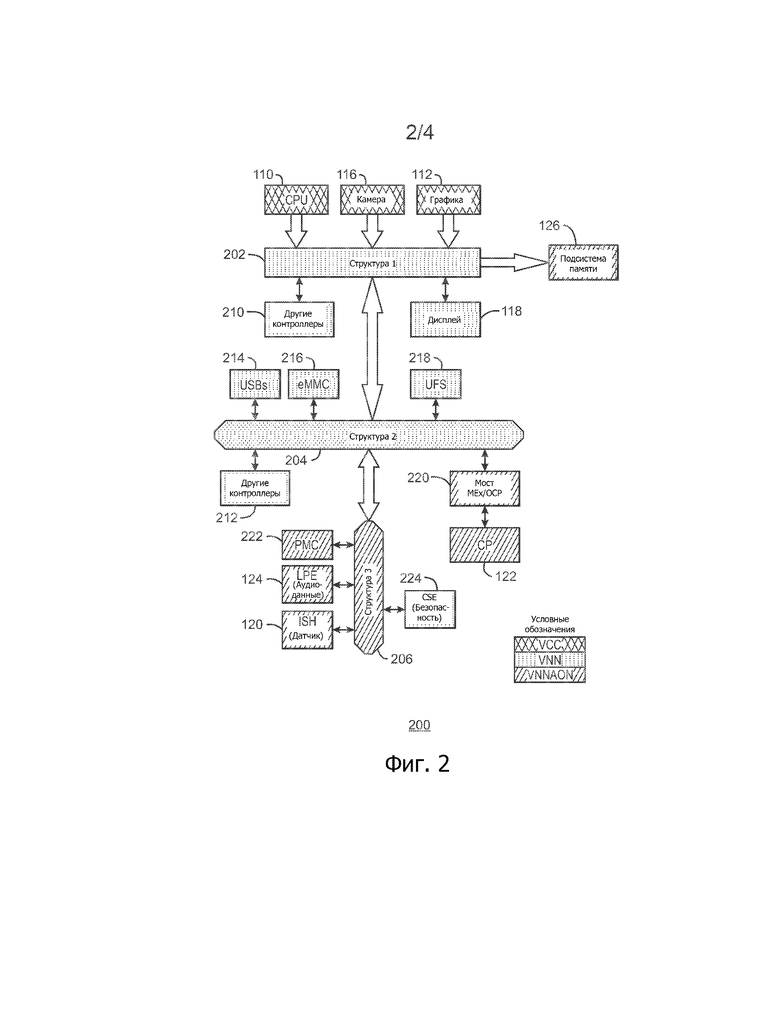

на фиг. 2 - блок-схема SOC;

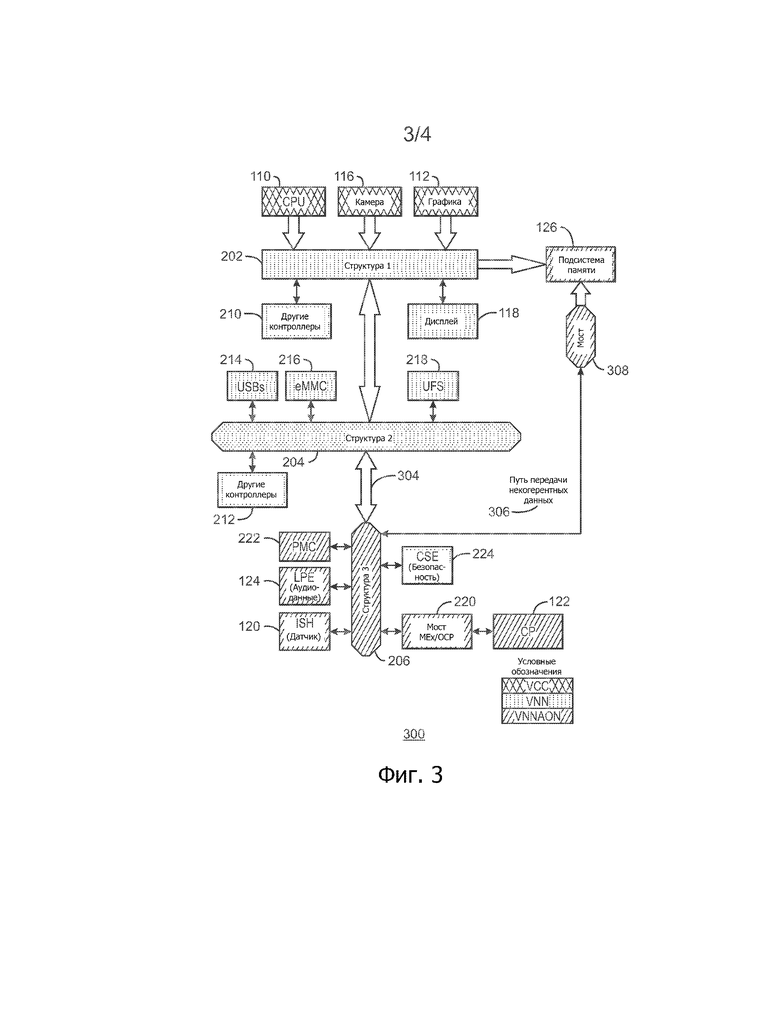

на фиг. 3 - блок-схема SOC с постоянно включенной структурой (AON); и

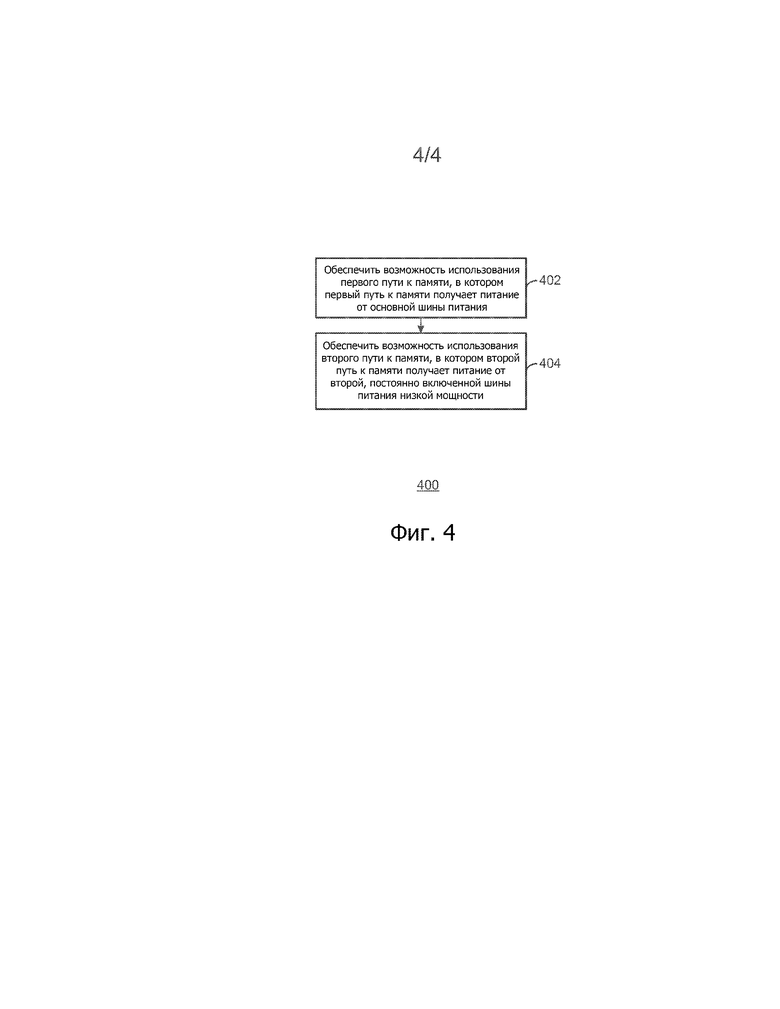

на фиг. 4 - схема обработки способа для обеспечения постоянно включенного пути к запоминающему устройству.

Одинаковые номера ссылочных позиций используются в раскрытии и на чертежах для обозначения одинаковых компонентов и свойств. Числа в последовательностях 100 относятся к свойствам, которые изначально можно найти на фиг. 1; числа в последовательности 200 относятся к свойствам, которые первоначально можно найти на фиг. 2; и т.д.

Подробное описание изобретения

Как отмечено выше, компьютерные устройства обычно переходят во множество различных состояний питания. В зависимости от конкретной операционной системы, эти состояния могут называться состояниями “S”. Например, S0 может представлять собой активное состояние, S3 может представлять собой состояние ожидания, S4 может обозначать спящее состояние, и S5 может представлять собой отключенное состояние. Дополнительные состояния сна могут быть воплощены через интерфейсы и подсистемы компьютерного устройства во время активного состояния S0, и могут называться состояниями S0ix. В состоянии S0ix различные подсистемы могут находиться в режимах пониженного потребления энергии, даже притом, что система находится в состоянии S0 (активное состояние). В состоянии S0ix “i” может представлять собой период ожидания в течение состояния S0, и “x” может представлять собой указатель места размещения периода ожидания, при этом большие значения “x” представляют большую длительность.

В любом заданном SOC, обычно один путь используется для поддержания оперативной памяти всеми подсистемами. В зависимости от архитектуры SOC, пробуждение одной подсистемы из состояния S0ix может привести к выходу других подсистем из состояния S0ix и потреблению энергии. Описанные здесь варианты осуществления включают постоянно доступную чрезвычайно низкую мощность питания, постоянно включенный (AON) путь для поддержания оперативной памяти для подсистем. В вариантах осуществления путь AON к памяти используется с подсистемами, которые остаются активными в течение всех состояний системы, включая в себя глубокие состояния S0ix. Некоторые подсистемы могут выходить из состояния S0ix и получать доступ к пути AON к памяти, в то время как другие подсистемы остаются в состоянии S0ix.

В дальнейшем описании и в формуле изобретения могут использоваться термины "соединенный" и "связанный", вместе с их производными. Следует понимать, что эти термины не предназначены для использования в качестве синонимов друг друга. Скорее, в конкретных вариантах осуществления, "соединенный" может использоваться для обозначения того, что два или больше элемента находятся в прямом физическом или электрическом контакте друг с другом. "Подключенный" может означать, что два или больше элемента находятся в прямом физическом или электрическом контакте. Однако, "соединенный" может также означать, что два или больше элемента не находятся в прямом контакте друг с другом, но все еще взаимодействуют или влияют друг на друга.

Некоторые варианты осуществления могут быть воплощены в одном или в комбинации из аппаратного обеспечения, встроенного программного обеспечения и программного обеспечения. Некоторые варианты осуществления также могут быть воплощены, как инструкции, сохраненные на считываемом в машине носителе информации, которые могут быть считаны и могут быть выполнены компьютерной платформой для выполнения операций, описанных здесь. Считываемый машиной носитель информации может включать в себя любой механизм для сохранения или передачи информации в форме, считываемой машиной, например, компьютером. Например, считываемый машиной носитель информации может включать в себя постоянное запоминающее устройство (ROM); оперативное запоминающее устройство (RAM); носители информации на магнитных дисках; оптические носители информации; устройства памяти типа флэш; или электрические, оптические, акустические или другие формы распространяющихся сигналов, например, несущих волн, инфракрасных сигналов, цифровых сигналов или интерфейсов, которые передают и/или принимают сигналы, помимо прочего.

Вариант осуществления представляет собой воплощение или пример. Ссылка в описании на "вариант осуществления", "один вариант осуществления", “некоторые варианты осуществления”, “различные варианты осуществления” или "другие варианты осуществления" означает, что конкретное свойство, структура, или характеристика описанные в связи с вариантами осуществления, включена в, по меньшей мере, некоторые варианты осуществления, но не обязательно во все варианты осуществления, настоящих технологий. Различные появления фраз "вариант осуществления", "один вариант осуществления" или “некоторые варианты осуществления” не обязательно все относятся к одним вариантам осуществления. Элементы или аспекты из варианта осуществления могут быть скомбинированы с элементами или аспектами другого варианта осуществления.

Не все компоненты, свойства, структуры, характеристики и т.д., описанные и представленные здесь, должны быть включены в конкретный вариант или варианты осуществления. Если в спецификации указаны компонент, свойство, структура или характеристика "может", "должна быть", или "могла бы" быть включена, например, этот конкретный компонент, свойство, структуру или характеристику не требуется включать. Если в спецификации или в формуле изобретения указано "a" («an») элемент, это не обязательно означает, что присутствует только один элемент. Если в спецификации или в формуле изобретения упомянут "дополнительный" элемент, это не исключает, что присутствует более, чем один дополнительный элемент.

Следует отметить, что хотя некоторые варианты осуществления были описаны со ссылкой на конкретные варианты осуществления, другие варианты осуществления возможны, в соответствии с некоторыми вариантами осуществления. Кроме того, компоновка и/или порядок элементов цепей или других свойств, представленных на чертежах и/или описанных здесь, не обязательно должны быть размещены определенным способом, как представлено и описано. Множество других компоновок возможны, в соответствии с некоторыми вариантами осуществления.

В каждой системе, показанной на чертеже, каждый элемент в некоторых случаях может иметь одинаковый номер ссылочной позиции или разные номера ссылочных позиций, что предполагает, что представленные элементы могут быть разными и/или аналогичными. Однако элемент может быть достаточно гибким, чтобы иметь другие варианты осуществления и может работать с некоторыми или всеми из систем, показанных или описанных здесь. Различные элементы, показанные на фигурах, могут быть такими же или другими. Какой из них называется первым элементом, и какой из них называется вторым элементом, установлено произвольно.

На фиг. 1 показана блок-схема компьютерной системы 100. Компьютерное устройство 100 может представлять собой, например, переносной компьютер, настольный компьютер, планшетный компьютер, ультрабук, мобильное устройство или сервер, помимо прочего. Компьютерное устройство 100 может включать в себя систему 102 на кристалле (SOC). SOC 102 может быть соединена через интерфейс с интегральной схемой 104 администрирования питанием (PMIC). SOC 102, представленная здесь, может включать в себя такие компоненты, как интерфейс 106 передачи данных, который связан с микроконтроллером 108. Микроконтроллер 108 функционально может быть соединен с некоторыми другими подсистемами, включая центральное процессорное устройство (CPU) 110, модуль 112a графической обработки (GPU) видеокомпонент 114, камеру 116, дисплей 118, концентратор 120 датчиков, модем 122, аудиомодуль 124, одно или больше запоминающих устройств 126, и один или больше интегрированных регуляторов 128 с малыми потерями данных (LDO). В некоторых сценариях CPU 110 могут работать от силовой шины источника питания VCC, в то время как GPU 112, видео компонент 114, камера 116, дисплей 118, концентратор 120 датчиков, модем 122, аудиомодуль 124, запоминающие устройства 126 и LDO 128 могут получать питание от шины источника питания VNN. В вариантах осуществления всегда доступные подсистемы, такие как концентратор 120 датчиков, модем 122 и аудиомодуль 124 получают питание от постоянно включенного источника питания (Vnnaon).

GPU 112 может быть выполнено с возможностью выполнять любое количество графических операций в компьютерной системе 100. Например, GPU 112 может быть выполнено с возможностью визуализации или манипуляции графическими изображениями, графическими кадрами, видеоданными и т.п. для отображения для пользователя компьютерной системы 100. Дисплей 118 может быть подключен к устройствам, включающим в себя экран дисплея, который представляет собой встроенный компонент компьютерной системы 100. Дисплей 118 также может быть соединен с компьютерным монитором, телевизионным устройством или проектором, помимо прочих, которые подключаются снаружи к компьютерному устройству 100.

Концентратор 120 датчиков можно рассматривать, как автономную подсистему, которая интегрирует и обрабатывает данные от различных датчиков. В некоторых случаях, автономная подсистема представляет собой подсистему, которая может функционировать независимо от CPU, GPU или других подсистем, и может отвечать или реагировать независимо. Автономная подсистема также может представлять собой подсистему, для которой не требуется использование компьютерной операционной системы для координации и/или управления всеми аспектами работы подсистемы. Таким образом, автономной подсистеме не требуется операционная система для доступа к подсистеме памяти, как описано в соответствии с настоящими технологиями. В результате, автономная подсистема с целью доступа к памяти существует независимо и без внешнего управления со стороны операционной системы может отвечать и/или реагировать самостоятельно.

Модем 122 может включать в себя различные антенны для передачи и приема беспроводных данных, и также может представлять собой автономную подсистему. Модем 122 может быть выполнен с возможностью подключения компьютерной системы 100 через шину 106 к сети 130. Сеть 130 может представлять собой глобальную вычислительную сеть (WAN), локальную вычислительную сеть (LAN) или Интернет, помимо прочих. В мобильной SOC модем 122 может соединять мобильное устройство с базовой станцией. Аудиоподсистема может быть соединена с множеством громкоговорителей и устройствами вывода звука. В некоторых случаях, аудиоподсистема 124 представляет собой автономную подсистему. Запоминающее устройство 126 может включать в себя оперативное запоминающее устройство (RAM), постоянное запоминающее устройство (ROM), запоминающее устройство флэш или любые другие соответствующие системы памяти. Например, запоминающее устройство 126 может включать в себя динамическое оперативное запоминающее устройство (DRAM) или статическое оперативное запоминающее устройство (SRAM). SOC также может быть соединена с запоминающим устройством 127 за пределами микросхемы. Запоминающее устройство 127 пределами микросхемы может включать в себя, например, DRAM или SRAM.

В некоторых случаях, концентратор 120 датчика, модем 122, аудиоподсистемы 124 являются автономными, активными, и обращаются к памяти, в то время как остальные подсистемы на SOC 102 находятся в состоянии ожидания S0ix. Автономные подсистемы, такие как концентратор 120 датчика, модем 122, аудиоподсистема 124 могут быть помещены на низком уровне в иерархической структуре SOC 102. Пробуждение автономных подсистем для доступа к подсистеме 126 памяти может привести к пробуждению всех структур и подсистем, поскольку автономные подсистемы находятся на низком уровне в иерархической структуре. Шина подачи питания VNNAON может обеспечивать питание для автономных подсистем, для их включения и доступа к подсистеме 126 памяти, без необходимости вывода других подсистем из спящего состояния. В примере CPU 110 может получать питание от шины подачи питания VCC, в то время как GPU 112, видеокомпонент 114, камера 116, дисплей 118 и LDO 128 могут получать питание от шины подачи питания VNN. Всегда доступная, всегда включенная шина подачи питания VNNAON может использоваться для подачи питания к автономным подсистемам, таким как концентратор 120 датчиков, модем 122 и аудиомодуль 124. Используемый здесь термин постоянно доступный относится к питанию, которое включено в течение состояний S0ix и любого другого глубокого спящего состояния, при котором обычно отключают питание в шине подачи питания. Шина подачи питания VNn, шина подачи питания VCC, или любая их комбинация может представлять собой первую шину подачи питания, и может подавать питание в множество подсистем. Шина подачи питания VNNAON может представлять собой вторую шину подачи питания, и может подавать питание в множество автономных подсистем, где шина подачи питания VNNAON всегда должна быть включена и должна подавать малую мощность.

PMIC 104 может включать в себя дополнительные компоненты, такие как модуль 132 управления пакетом (BCU), компонент 134 администрирования прерыванием и интерфейс 136 передачи данных. BCU 132 может во время работы принимать и обрабатывать данные из одного или больше компараторов, обозначающих текущие уровни на шинах подачи питания, таких как шина подачи питания VCC, шина подачи питания VNN, и шина подачи питания VNNAON SOC 102. В соответствии с этим, отслеживание шины подачи питания VCC представлено под номером 138 ссылочной позиции. Отслеживание шины подачи питания VNN обозначено номером 140 ссылочной позиции, и отслеживание шины подачи питания VNNAON обозначено номером 142 ссылочной позиции. В некоторых случаях, во время работы обеспечивается множество состояний питания, в которых PMIC может выполнять переход автономной подсистемы из спящего состояния в активное состояние, где автономная подсистема является активной и получает питание с низкой мощностью питания от постоянно включенной шины подачи питания VNNAON, в то время как вторая подсистема должна оставаться в спящем состоянии и получать питание от шины подачи питания VNN, шины подачи питания VCC, или используя любую их комбинацию.

Результат такого отслеживания тока различных шин подачи питания, может быть передан в компонент 134 администрирования прерыванием для дальнейшей обработки. Компонент 134 администрирования прерыванием может во время работы формировать прерывание, когда отслеживаемый текущий уровень пересекает установленный порог. Установленный порог может также называться программируемой точкой срабатывания. Прерывание может включать в себя данные, обозначающие, произошло ли превышение текущим уровнем тока в шине подачи питания установленного порога на чрезмерный уровень, или произошел ли возврат обратно к нормальному уровню. Прерывание может затем быть перенаправлено в интерфейс 136 передачи данных по PMIC 104. Интерфейс 136 передачи данных затем может перенаправлять это прерывание из PMIC 104 в SOC 102. Хотя здесь описан PMIC 104, PMIC не обязательно требуется использовать в настоящих технологиях.

В типичной мобильной SOC основную шину питания SOC VNN отключают во время состояния питания S0ix. В некоторых случаях, PMIC переключает шину подачи питания VNN во время состояния питания S0ix. В результате, основная шина VNN получает питание, и ее питание отключается для каждого доступа к памяти автономными подсистемами, в случае, когда отсутствует постоянно включенный путь к памяти. С таким переключением шины VNN связаны затраты, относящиеся к латентности передачи данных в PMIC и энергии, требуемой для перевода системы в состояние, в котором она имеет возможность выполнять передачу данных. Представленные здесь технологии исключают эти затраты путем исключения необходимости частого переключения шины VNN. Скорее, шина подачи питания VNNAON может использоваться для нескольких автономных подсистем без пробуждения других подсистем и включения питания в шине подачи питания VNN.

Блок-схема на фиг. 1 не предназначена для обозначения того, что система 100 должна включать в себя все компоненты, показанные на фиг. 1. Кроме того, система 100 может включать в себя любое количество дополнительных компонентов, не показанных на фиг. 1, в зависимости от деталей конкретного воплощения. Кроме того, SOC 102 является примерной. Другие компоненты или комбинации компонентов могут использоваться в зависимости от конкретных вариантов осуществления и функций SOC 102. Варианты осуществления не ограничены примером SOC 102.

На фиг. 2 показана блок-схема SOC 200. SOC 200 включает в себя структуру 202, структуру 204 и структуру 206. В примерах структура представляет собой группу узлов, соединенных взаимными соединениями с широкой полосой пропускания. Каждую подсистему можно рассматривать, как узел, соединенный со структурой. Кроме того, каждая структура может быть соединена иерархически.

Как представлено, структура 202 представляет собой самую высокую структуру в иерархии. Структура 202 взаимно соединяет CPU 110, камеру 116, графические подсистемы 112, дисплей 118 и другие контроллеры 210. Другие контроллеры 210 включают в себя, но не ограничены этим, модули отладки, модули распознавания речи, и любой другой общий интегрированный пакет (IP). Следующая структура в иерархии представляет собой структуру 204. Структура 204 соединяет несколько контроллеров 212. В некоторых случаях, другие контроллеры 212 включают в себя, но не ограничены этим, контроллеры универсальной последовательной шины (USB), IP сохранения и любые другие общие IP. Структура 204 также соединяет подсистемы 214 USB, подсистему 216 встроенного мультимедийного контроллера (eMMC), и подсистему 218 универсального накопителя типа флэш (UFS). Структура 204 также соединяет модем 122 через мост 220 протокола с открытым ядром (OCP). Структура 206 соединяет контроллер 222 администрирования питанием (PMC), аудиоподсистему 124, концентратор 120 датчика, и подсистему 224 установления безопасности передачи данных (CSE). Хотя некоторые подсистемы и контроллеры представлены, как соединенные с SOC 200 через определенные структуры, компоновка различных настоящих технологий может использоваться с любой компоновкой множества подсистем.

Как показано на фиг. 2, структура 202 помещена на высоком уровне в иерархии структур с непосредственным доступом к подсистеме 126 памяти. Структура 204 находится ниже структуры 202 и обращается к подсистеме 126 памяти через структуру 204. В соответствии с этим, структура 204 может пробуждать структуру 202 из спящего состояния S0ix для доступа к подсистеме 126 памяти. Аналогично, структура 206 находится ниже структуры 204 и структуры 202. Структура 206 обращается к подсистеме 126 памяти через структуру 204 и структуру 202. В соответствии с этим, структура 204 может пробуждать структуру 204 и структуру 202 из спящего состояния S0ix, для доступа к подсистеме 126 памяти. Как представлено на фиг. 2, модем 122 был соединен выше в иерархии структуры для уменьшения латентности доступа к памяти модема 122. Другими словами, расположение модема 122 в иерархии структуры предназначено для уменьшения количества времени, которое требуется для доступа модема 122 к подсистеме 126 памяти.

На фиг. 3 показана блок-схема SOC 300 с постоянной включенной (AON) структурой 206. SOC 300 включает в себя структуру 202 и структуру 204. Однако автономные подсистемы по-другому размещены в структуре 206 AON. Автономные подсистемы включают в себя подсистемы, которые могут независимо обращаться к подсистеме 126 памяти, в то время, как с остальная SOC 300 находится в спящем состоянии. В некоторых случаях структура AON получает питание во всех состояниях системы.

Структура 206 AON может разделять когерентный и некогерентный трафик по разным путям через систему. Когерентные данные могут включать в себя данные, которые совместно используются в узлах в пределах SOC 300. С целью последовательности данных, путь 304 когерентных данных направляет когерентные данные через другие структуры SOC 300. Путь 306 некогерентных данных направляет некогерентные данные в подсистему 126 памяти без доступа к структуре 204 или структуре 202. Малый мост 308 используется для отбора некогерентного трафика из структуры 206 AON из пути 306 некогерентных данных и передачи в подсистему 126 памяти.

К части памяти обращаются по обходному пути низкой мощности, по которому передают некогерентный трафик, при этом перемежение канала может быть оптимизировано в отношении мощности, вместо рабочих характеристик. Такое перемежение канала уменьшает количество модулей данных (Dunits), активируемых для конкретного доступа устройства и также для поддержания большего количества микросхем DRAM в состоянии самостоятельного обновления. В примерах Dunit используется для генерирования команд или инструкций, необходимых для передачи запросов на доступ к памяти. Dunit также может формировать очередь из пакетов, включая в себя команды или инструкции для передачи через шину памяти. Кроме того, Dunit также синхронизирует передачу данных, которые пересекают границу тактовой частоты между тактовой частотой ядра и собственной тактовой частотой шины памяти.

Как представлено на фиг. 3, подсистемы SOC 300 могут работать, получая питание из различных шин подачи питания. CPU 110, камера 116 и GPU 112 могут получать питание из шины подачи питания VCC, обозначенной штриховкой накрест на каждом из этих компонентов. Аналогично, структура 202, другие контроллеры 210, дисплей 118, подсистема 214 USB, подсистема 216 eMMC, подсистема 218 UFS, структура 204 и CSE 224 могут получать питание, используя шины подачи питания VNN. Это представлено точками, через каждый из этих компонентов. PMC 222, аудиоподсистема 124, концентратор 120 датчика, мост 220 OCP и модем 122 могут получать питание, используя шину подачи питания VNNAON. Это представлено диагональными линиями через каждый из этих компонентов. Подсистема 126 памяти может получать питание в соответствии с компонентом, который обращается к подсистеме 126 памяти. Как представлено диагональными линиями и точками через подсистему 126 памяти, подсистема 126 памяти может получать питание от шины источника питания VNN или шины источника питания VNNAON.

В случае модема, соответствующего проекту долгосрочного развития (LTE), существует строгое требование к латентности доступа к памяти ~300нс, которое требует подключения очень близко к Dunit. Подробности стандарта LTE обозначены в различных выпусках 3GPP. Настоящие технологии обеспечивают специализированный путь AON для доступа к памяти модема LTE. В результате, точка прикрепления модема может быть перемещена в более низкое положение в иерархии структуры. В некоторых случаях, каждая из подсистем, подключенных к структуре AON, включая в себя саму структуру AON, работает, используя тактовую частоту генератора с калиброванным кольцом. Тактовая частота генератора с калиброванным кольцом может использоваться для предотвращения использования энергии, ассоциированного с подачей питания в генераторы тактовой частоты в контуре фазовой синхронизации (PLL). В соответствии с этим, настоящие технологии могут использоваться для поддержки различных модемов с низкими требованиями к латентности для доступа к памяти, без изменения архитектуры подсистем внутреннего модема для поддержания низкой латентности.

В примерах описанная здесь SOC может быть включена в мобильное устройство. Компоненты мобильного устройства могут быть всегда включены. Например, модем может выполнять пинговый запрос в базовую станцию через регулярные интервалы для синхронизации мобильного устройства с базовой станцией. Обмен данными с базовой станцией также может включать в себя доступ к подсистеме памяти. Путем классификации доступов к памяти, в соответствии с подсистемой, доступы к памяти не обрабатываются равнозначно по SOC. Когда автономная подсистема обращается к памяти на SOC, для доступа может использоваться узкая полоса пропускания, путь с малой латентностью к памяти, когда данные являются некогерентными. Таким образом, затраты на пробуждение всей SOC (которая разработана для доступа к значительной части данных с широкой полосой пропускания) могут быть исключены. В результате, настоящие технологии позволяют уменьшить потребление энергии SOC.

На фиг. 4 показана блок-схема последовательности операций способа 400 для обеспечения постоянно включенного пути к памяти. В блоке 402, представлен первый путь для подачи питания к памяти. В некоторых случаях, первый путь для подачи питания к памяти представляет собой основной путь к памяти. Основной путь к памяти может использоваться когерентным трафиком и может поддерживать очень широкую полосу пропускания данных. Кроме того, первый путь к памяти может получать питание от основной шины питания. В блоке 404 представлен второй путь подачи питания к памяти. Второй путь к памяти всегда должен быть включен, и по нему можно передавать малую мощность. Постоянно включенный путь используется некогерентным трафиком и оптимизируется для передачи данных с малой мощностью. Второй путь к памяти может получать питание от второй, более низкой мощности, всегда подключенной шины подачи питания. Вторая шина подачи питания может иметь более низкую мощность по сравнению с основной шиной подачи питания. В некоторых случаях, вторая шина подачи питания имеет более низкую мощность, по сравнению с другими шинами подачи питания системы. Первая шина подачи питания в память и вторая шина подачи питания не включаются в каком-либо конкретном порядке. Скорее, второй путь подачи питания может быть включен перед первым путем подачи питания, или первый путь подачи питания и второй путь подачи питания включаются одновременно.

В примерах, по мере того, как количество пробуждений увеличивается в системе, использование питания может оставаться постоянным или стабильным, в соответствии с настоящими технологиями. В соответствии с этим, настоящие технологии приводят к значительной экономии энергии по сравнению с системами без постоянно включенного пути к памяти. Кроме того, настоящие технологии могут быть полезными в мобильных устройствах, поскольку мобильные устройства обычно имеют большое количество приложений (apps), которые работают в фоновом режиме и приводят к частому пробуждению системы.

Настоящие технологии могут также уменьшить общее потребление энергии системой, благодаря отсутствию необходимости выхода из самых глубоких состояний S0ix. Как описано выше, любой доступ к памяти из автономных подсистем может привести к пробуждению всей SOC и привести к выходу всей SOC из глубокого состояния S0ix. Это приводит к дополнительной потере энергии из-за переходной энергии при переключении в глубокие состояния S0ix и из них. В обычной SOC проецируемая энергия, потребляемая во время сохранения и восстановления состояния SOC и для заряда конденсаторов большой емкости (например, Vnn и SRAM), может составлять приблизительно 100,2 микроджоуля, что составляет более чем 100 микроватт для сохранения и восстановления каждую секунду. Затраты на переход энергии для входа в и выхода из состояния глубокого сна системы, могут привести к неконкурентоспособным мобильным устройствам с очень малым сроком службы аккумуляторной батареи. В некоторых примерах частые пробуждения могут привести к тому, что вход в состояние S0ix не будет выполняться вообще. Кроме того, при использовании обычных SOC, латентность для доступа к оперативной памяти диктуется глубокими латентностями выхода из S0ix. Варианты использования могут не позволять использовать большие значения латентности при доступе к памяти, и могут предотвращать переход подсистемы в самое глубокое состояние S0ix для исключения латентности при доступе к памяти. Когда предотвращается переход подсистемы в самое глубокое состояние S0ix, минимальная потребляемая энергия увеличивается, и система остается в самом низком состоянии S0ix. Это приводит к потерям энергии. В результате перемещения автономных подсистем в постоянно включенную структуру, в соответствии с настоящими технологиями, части системы могут входить и оставаться в глубоком спящем состоянии, удовлетворяя при этом любые требования к латентности, экономя, таким образом, энергию.

В настоящих технологиях может использоваться преимущество увеличенного количества автономных подсистем, которые могут быть найдены по мере установления новых случаев использования. Такие новые автономные подсистемы могут потребовать, автономную подсистему, активную в глубоких состояниях S0ix. В результате ограничений обычных SOC, в подсистемах проявляется тенденция разработки подсистем с большими размерами внутренней SRAM. Например, концентратор датчика может иметь более чем 600 Кбит SRAM, и модем может иметь больше, чем 12,5MB SRAM. Однако, энергия утечки SRAM, в частности, при удержании данных, постоянно увеличивается, по мере уменьшения размера транзистора. Кроме того, SRAM способствует большей мощности утечки в глубоких спящих состояниях. Например, в концентраторе датчика может происходить утечка больше, чем 370 микроватт энергии в глубоком спящем состоянии. Настоящие технологии обеспечивают уменьшение размеров SRAM таких подсистем. Кроме того, настоящие технологии обеспечивают отключение питание части SRAM в спящем состоянии, уменьшая, таким образом, мощность утечки и площадь, занимаемую подсистемами на кристалле.

Кроме того, конкретные варианты использования, такие как GeoFencing, могут быть воплощены, используя настоящие технологии. В некоторых случаях, GeoFencing обеспечивает определение электронным устройством географических границ. Система Глобальной навигации (GPS) или радиочастотная идентификация (RFID) может использоваться для определения географических границ. GeoFencing может быть очень неэффективной с точки зрения потребления энергии, с учетом большого количества потерь страниц в секунду при доступе к памяти, и может приводить к большим затратам энергии, взаимосвязанным с каждой такой потерей. Каждая потеря обычно требует включения шины VNN, с последующим включением питания остальных подсистем и всей иерархии структуры. Настоящие технологии обеспечивают существенное уменьшение затрат энергии, связанных с потерями страниц и, таким образом, обеспечивают такие новые случаи использования без значительного влияния на срок службы аккумуляторной батареи.

В настоящих технологиях также используется меньшее количество зависимостей от совместно используемых ресурсов, таких как структуры, синхронизация по тактовой частоте и канал памяти, таким образом, что задержка доступа к оперативной памяти может быть уменьшена. В частности, внутренняя временная SRAM/Cache в каждой подсистеме может быть уменьшена. Кроме того, обеспечивается уменьшение архитектурной сложности текущей “основной структуры”. Основная структура может представлять собой структуру, которая соединяет запоминающее устройство, CPU, GFx, дисплей и ISP, такая как структура 1 202 (фиг. 2). Поскольку латентность не является критерием для основного пути в соответствии с настоящими технологиями, основная структура и путь могут быть оптимизированы только для полосы пропускания и, таким образом, может представлять собой более эффективный путь к памяти. В примерах настоящие технологии требуют, чтобы автономные подсистемы были размещены рядом друг с другом в одной структуре. Это обеспечивает формирование одного большого острова питания AON, вместо малых распределенных островов AON по SOC, что упрощает воплощение.

Кроме того, настоящие технологии открывают возможности для повторного разделения, в то время, как все автономные подсистемы AON могут быть перемещены на отдельный вспомогательный кристалл. Такой вспомогательный кристалл может быть изготовлен, используя обработку, приводящую к чрезвычайно низким утечкам. Это приводит к изготовлению SOC, используя обработку, настроенную на самые высокие рабочие характеристики и в которой все автономные подсистемы перемещены на вспомогательный кристалл, который изготовляют, используя другую обработку, оптимизированную для сверхнизкой утечки. Для отдельного вспомогательного кристалла может быть полезно использовать путь к памяти с низкой мощностью по кристаллу через соединение с малой латентностью, такое как интерфейс с малой латентностью (LLI).

Пример 1

Здесь описано устройство с архитектурой c ультранизкой мощностью. Устройство включает в себя первую шину подачи питания и вторую шину подачи питания. Множество подсистем должны получать питание через первую шину подачи питания, и множество автономных подсистем должны получать питание от шины подачи питания. Вторая шина подачи питания должна быть постоянно включена, всегда доступна и имеет низкую мощность.

Устройство может представлять собой систему на кристалле. Автономные подсистемы могут непосредственно получать доступ к памяти устройства. Доступ к памяти множества автономных подсистем не приводит к выходу из состояния системы S0ix. Кроме того, в котором автономная подсистема может быть активной во время спящего состояния S0ix. Устройство также может включать в себя путь передачи когерентных данных в подсистему памяти из множества автономных подсистем, и путь передачи некогерентных данных в подсистему памяти из множества автономных подсистем. Множество автономных подсистем может быть размещено на той же самой структуре устройства, или множество автономных подсистем может быть перемещено на отдельный вспомогательный кристалл устройства. Множество автономных подсистем включают в себя концентратор датчиков, модем, аудиомодуль, любую подсистему, которая позволяет осуществлять независимый доступ к памяти, или любую их комбинацию. Кроме того, устройство может представлять собой мобильное устройство. Путь с большой полосой пропускания к памяти может быть включен с использованием первой шины подачи питания, и первая шина подачи питания может получать питание в большинстве состояний. Путь с узкой полосой пропускания к памяти может быть включен, используя постоянно включенную, постоянно доступную вторую шину подачи питания.

Пример 2

Здесь описана интегральная схема администрирования питанием (PMIC). Интегральная схема администрирования питанием во время работы обеспечивает множество состояний питания, в которой интегральная схема администрирования питанием может обеспечивать переход автономной подсистемы из спящего состояния в активное состояние. Автономная подсистема может быть активной и может получать питание от постоянно включенного источника питания низкой мощности, в то время как вторая подсистема может оставаться в спящем состоянии.

Постоянно включенный источник питания низкой мощности может обеспечивать питание пути передачи некогерентных данных в память. Автономная подсистема может использовать путь передачи некогерентных данных для доступа во время случая использования низкой мощности. Кроме того, интегральная схема администрирования питанием может выводить вторую подсистему из спящего состояния, когда автономная подсистема предоставляет когерентные данные по пути передачи когерентных данных в память. Кроме того, интегральная схема администрирования питанием может не переключать основную шину питания в ответ на некогерентный доступ к памяти автономной подсистемы. Интегральная схема администрирования питанием может также администрировать множеством автономных подсистем. Множество автономных подсистем могут быть размещены в той же структуре. Может быть уменьшена латентность доступа к оперативной памяти. Автономная подсистема и вторая подсистема могут представлять собой компоненты системы на кристалле. Кроме того, интегральная схема администрирования питанием может обеспечивать множество спящих состояний на основе каждой подсистемы.

Пример 3

Здесь описан способ для предоставления архитектуры с ультранизкой мощностью. Способ включает в себя: обеспечивают возможность использования первого пути в памяти для мобильной системы на кристалле, в котором первый путь к памяти может получать питание от основной шины питания. Способ также включает в себя: обеспечивают возможность использования второго пути памяти для мобильной системы на кристалле, в котором путь к памяти может получать питание от второй постоянно включенной шины питания низкой мощности.

Первый путь к памяти может представлять собой путь передачи данных с высокой латентностью, с большой полосой пропускания. Второй путь к памяти может представлять собой путь для передачи данных с низкой латентностью, с малой полосой пропускания. Автономная подсистема может выполнять доступ к памяти, используя второй путь для памяти, без выхода второй подсистемы из состояния системы S0ix. Кроме того, первый путь к памяти может представлять собой путь передачи данных когерентных данных в подсистему памяти из множества автономных подсистем. Второй путь к памяти может представлять собой путь для передачи некогерентных данных в подсистему памяти из множества автономных подсистем. Кроме того, доступ ко второму пути к памяти может осуществляться множеством автономных подсистем, которые размещены в той же структуре мобильной системы на кристалле. Доступ ко второму пути к памяти может осуществляться множеством автономных подсистем, которые размещены на отдельном вспомогательном кристалле мобильной системы на кристалле. Автономная подсистема может включать в себя концентратор датчиков, модем, аудиомодуль, любую подсистему, которая может независимо выполнять доступ к памяти, или любую их комбинацию. Использование энергии питания мобильной системой на кристалле может быть уменьшено.

Пример 4

Здесь описано устройство с архитектурой с ультранизкой мощностью. Устройство включает в себя первое средство для подачи питания в устройство памяти устройства. Устройство также включает в себя средство для подачи питания во второе устройство, устройство, в котором второе средство может быть всегда включено и может иметь малую мощность.

Множество автономных подсистем могут получать питание от второго средства для подачи питания. Второе средство для подачи питания может осуществлять питание, постоянно включенного, постоянно доступного, имеющего малую полосу пропускания и низкую латентность пути передачи данных в память. Доступ к памяти множеством автономных подсистем может не выводить систему из состояния S0ix. Кроме того, автономная подсистема может быть активной в течение глубокого спящего состояния S0ix. Устройство может включать в себя путь передачи когерентных данных в подсистему памяти из множества автономных подсистем и путь передачи некогерентных данных в подсистему памяти из множества автономных подсистем. Множество автономных подсистем может быть размещено на той же структуре устройства. Кроме того, множество автономных подсистем может быть перемещено на отдельный вспомогательный кристалл устройства. Кроме того, множество автономных подсистем может включать в себя концентратор датчиков, модем, аудиомодуль, любую подсистему, которая позволяет независимо выполнять доступ к памяти, или любую их комбинацию. Устройство может представлять собой мобильное устройство. Кроме того, может обеспечиваться возможность использования второго средства для подачи питания в устройство памяти, используя постоянно включенную, постоянно доступную вторую шину подачи питания.

Пример 5

Здесь описана система с архитектурой ультранизкой мощности. Система включает в себя дисплей, радиомодуль, запоминающее устройство и процессор. Запоминающее устройство может быть предназначено для сохранения инструкций и может быть соединено с возможностью обмена данными с дисплеем. Процессор соединен с возможностью обмена данными с радиомодулем и запоминающим устройством. Система также включает в себя первую шину подачи питания и вторую шину подачи питания. Множество подсистем должны получать питание от первой шины подачи питания, и множество автономных подсистем должны получать питание от второй шины подачи питания, в котором вторая шина подачи питания должна быть постоянно включена и постоянно доступна.

Автономные подсистемы могут непосредственно выполнять доступ к памяти через путь к памяти с низкой латентностью, малой полосой пропускания. Доступ к памяти множеством автономных подсистем может не выводить систему из состояния S0ix. Кроме того, автономная подсистема, получающая питание от второй шины подачи питания, может быть активной в течение глубокого спящего состояния S0ix, в котором первая шина подачи питания может быть отключена. Система также может включать в себя путь для передачи когерентных данных в подсистему памяти из множества автономных подсистем, которые могут получать питание от первой шины подачи питания, и путь передачи некогерентных данных в подсистему памяти из множества автономных подсистем, которые могут получать питание от второй шины подачи питания. Множество автономных подсистем может быть размещено в той же структуре системы. Кроме того, множество автономных подсистем может быть перемещено на отдельный вспомогательный кристалл системы. Множество автономных подсистем может включать в себя концентратор датчиков, модем, аудиомодуль, любую подсистему, которая может независимо осуществлять доступ к памяти, или любую их комбинацию. Система может представлять собой мобильное устройство. Питание пути с большой полосой пропускания может обеспечиваться от первой шины подачи питания, которая может быть отключена большую часть времени. Путь к памяти с малой полосой пропускания может обеспечиваться, используя постоянно включенную и постоянно доступную вторую шину подачи питания.

Следует понимать, что специфика в упомянутых выше примерах может использоваться в одном или больше вариантах осуществления. Например, все необязательные свойства компьютерного устройства, описанные выше, также могут быть воплощены либо в отношении любого из способов, описанных здесь, или в отношении считываемого компьютером носителя информации. Кроме того, хотя блок-схемы последовательности операций и/или диаграммы состояний могут использоваться здесь для описания вариантов осуществления, настоящие технологии не ограничены этими диаграммами или соответствующими их описаниями. Например, поток не обязательно должен проходить через каждый представленный прямоугольник или состояние в точно том же порядке, как представлено и описано здесь.

Настоящие технологии не ограничены конкретными деталями, описанными здесь. Действительно, специалисты в данной области техники смогут оценить преимущество данного раскрытия, состоящее в том, что множество других вариантов на основе представленного выше описания и чертежей могут быть выполнены в пределах объема настоящих технологий. В соответствии с этим, следующая формула изобретения включает в себя любые дополнения в ее отношении, которые определяют объем настоящих технологий.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРХИТЕКТУРА НАКРИСТАЛЬНОГО МЕЖСОЕДИНЕНИЯ | 2015 |

|

RU2625558C2 |

| СИСТЕМА И СПОСОБ ЗАЩИТЫ ЭЛЕКТРОННЫХ ДОКУМЕНТОВ, СОДЕРЖАЩИХ КОНФИДЕНЦИАЛЬНУЮ ИНФОРМАЦИЮ, ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2020 |

|

RU2759210C1 |

| УПРАВЛЕНИЕ КОЛЕБАНИЯМИ ИНИЦИАТОРА ВВОДА/ВЫВОДА ПРИ ПЕРЕДАЧЕ | 2014 |

|

RU2644536C2 |

| СПОСОБ И СИСТЕМА АВТОРИЗАЦИИ НОСИТЕЛЯ ЦИФРОВОГО КЛЮЧА | 2018 |

|

RU2709281C1 |

| АДМИНИСТРИРОВАНИЕ ЗАЩИЩЕННЫМИ УСТРОЙСТВАМИ | 2010 |

|

RU2557756C2 |

| РАСПРЕДЕЛЕННАЯ КОММУТАЦИОННАЯ СИСТЕМА СВЯЗИ | 1994 |

|

RU2138134C1 |

| ЭЛЕКТРОННОЕ УСТРОЙСТВО И ЕГО СПОСОБ ИСПОЛЬЗОВАНИЯ ПРОСТРАНСТВА ДЛЯ ХРАНЕНИЯ | 2020 |

|

RU2815054C2 |

| СИСТЕМА ПРИВОДА СЕЛЬСКОХОЗЯЙСТВЕННОЙ МАШИНЫ | 2016 |

|

RU2730031C2 |

| СПОСОБ УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ УСТРОЙСТВОМ И ЭЛЕКТРОННОЕ УСТРОЙСТВО | 2006 |

|

RU2419823C2 |

| АРХИТЕКТУРА БЕСПРОВОДНОГО СЕНСОРНОГО УЗЛА С АВТОНОМНОЙ ПОТОКОВОЙ ПЕРЕДАЧЕЙ ДАННЫХ | 2009 |

|

RU2507571C2 |

Группа изобретений относится к технологии доступа к памяти. Технический результат – обеспечение возможности использования несколько шин подачи питания для уменьшения потребления энергии. Для этого предложено устройство, которое включает в себя первую шину подачи питания, в котором множество подсистем должны получать питание от первой шины подачи питания. Устройство также включает в себя вторую шину подачи питания, в котором множество автономных подсистем должны получать питание от шины подачи питания, в котором вторая шина подачи питания должна быть постоянно включена, постоянно доступна и иметь малую мощность. 3 н. и 19 з.п. ф-лы, 4 ил.

1. Устройство с архитектурой низкой мощности, содержащее:

первую шину подачи питания, в котором множество подсистем должны получать питание от первой шины подачи питания;

вторую шину подачи питания, в котором множество автономных подсистем должны получать питание от второй шины подачи питания, в котором вторая шина подачи питания должна быть всегда включена, всегда доступна и иметь низкую мощность по сравнению с первой шиной подачи питания;

путь передачи когерентных данных в подсистему из множества автономных подсистем; и

путь передачи некогерентных данных в подсистему памяти из множества автономных подсистем.

2. Устройство по п. 1, в котором устройство представляет собой систему на кристалле.

3. Устройство по п. 1, в котором автономные подсистемы непосредственно обращаются к памяти устройства.

4. Устройство по п. 1, в котором доступ к памяти множеством автономных подсистем не выводит систему из состояния S0ix.

5. Устройство по п. 1, в котором автономная подсистема является активной во время глубокого спящего состояния S0ix.

6. Устройство по п. 1, в котором множество автономных подсистем размещено на той же самой структуре устройства.

7. Устройство по п. 1, в котором множество автономных подсистем перемещено на отдельный вспомогательный кристалл устройства.

8. Устройство по п. 1, в котором множество автономных подсистем включают в себя концентратор датчиков, модем, аудиомодуль, любую подсистему, которая позволяет осуществлять независимый доступ к памяти, или любую их комбинацию.

9. Устройство по п. 1, представляющее собой мобильное устройство.

10. Устройство по п. 1, в котором путь с большой полосой пропускания к памяти может быть включен с использованием первой шины подачи питания.

11. Устройство по п. 1, в котором путь с узкой полосой пропускания к памяти может быть включен, используя постоянно включенную, постоянно доступную вторую шину подачи питания.

12. Интегральная схема администрирования питанием (PMIC) системы, выполненная с возможностью обеспечения множества состояний питания, в которой интегральная схема администрирования питанием должна обеспечивать переход автономной подсистемы из спящего состояния в активное состояние и в которой автономная подсистема является активной и получает питание от постоянно включенного источника питания низкой мощности, что является низкой мощностью по сравнению с другой мощностью системы, в то время, как вторая подсистема должна оставаться в спящем состоянии, в которой постоянно включенный источник питания низкой мощности предназначен для подачи питания в путь передачи некогерентных данных в память.

13. Интегральная схема администрирования питанием по п. 12, в которой автономная подсистема использует путь передачи некогерентных данных для доступа к памяти во время случая использования низкой мощности.

14. Интегральная схема администрирования питанием по п. 12, в которой интегральная схема администрирования питанием предназначена для вывода второй подсистемы из спящего состояния, когда автономная подсистема должна предоставлять когерентные данные по пути передачи когерентных данных в память.

15. Интегральная схема администрирования питанием по п. 12, в которой интегральная схема администрирования питанием не выполняет переключение основной шины питания в соответствии с некогерентным доступом к памяти автономной подсистемой.

16. Интегральная схема администрирования питанием по п. 12, в которой интегральная схема администрирования питанием управляет множеством автономных подсистем.

17. Способ для предоставления архитектуры питания низкой мощности, содержащий:

обеспечение возможности использования первого пути к памяти мобильной системы на кристалле, в котором первый путь к памяти получает питание от основной шины питания, при этом первый путь к памяти представляет собой путь передачи данных с высокой латентностью и большой полосой пропускания; и

обеспечение возможности использования второго пути к памяти мобильной системы на кристалле, в котором путь к памяти получает питание от второй постоянно включенной шины питания низкой мощности, что является низкой мощностью по сравнению с основной шиной питания.

18. Способ по п. 17, в котором второй путь к памяти представляет собой путь передачи данных с низкой латентностью, малой полосой пропускания.

19. Способ по п. 17, в котором автономная подсистема получает доступ к памяти, используя второй путь к памяти, без вывода второй подсистемы из состояния системы S0ix.

20. Способ по п. 17, в котором первый путь к памяти представляет собой путь передачи когерентных данных в подсистему из множества автономных подсистем.

21. Способ по п. 17, в котором второй путь к памяти представляет собой путь передачи некогерентных данных в подсистему памяти из множества автономных подсистем.

22. Способ по п. 17, в котором доступ ко второму пути к памяти осуществляется множеством автономных подсистем, которое размещено на той же самой структуре устройства.

| US 8766707 B1, 01.07.2014 | |||

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| БЫСТРАЯ ИНИЦИАЛИЗАЦИЯ И ВКЛЮЧЕНИЕ ДИСПЛЕЯ | 2007 |

|

RU2427031C2 |

Авторы

Даты

2018-08-17—Публикация

2015-06-23—Подача