Изобретение относится к области цифровой вычислительной техники и автоматики и может быть использовано для анализа и сложения двоичных кодов в блоках и устройствах ЭВМ.

Известны способы и устройства сравнения и сложения двоичных кодов, заключающиеся в последовательном выполнении элементарных операций приема и сравнения кодов чисел в схемах, содержащие триггерные регистры, элементы СЛОЖЕНИЕ ПО MOD2, элементы формирования переноса в каждом разряде.

Способы и устройство сравнения и суммирования двоичных кодов детально рассмотрены в кн.: Карцев М.А. «Арифметика цифровых машин». М.: изд-во «Наука», 1969 г., с. 247-252, рис. 2.45 и Дроздов Е.А. и др. «Электронные вычислительные машины Единой системы». М.: изд-во «Машиностроение», 1981 г., с. 76-80. При увеличений разрядности сложность этих схем сравнения быстро растет и существенно снижается их надежность. Поэтому для сравнения многоразрядных чисел используют следующий алгоритм. Сначала сравнивают значения старших разрядов: если они различны, то эти разряды и определяют результаты сравнения; если же они равны, то необходимо сравнивать следующие за ними последующие младшие разряды и т.д.

Общим недостатком известных устройств является необходимость использования трех регистров, выполненных на основе RS-триггеров, и затрат не менее четырех-пяти временных тактов для выполнения операции сравнения. Это определяет малое быстродействие работы и большие затраты оборудования для построения устройства.

Наиболее близким, принятым за прототип, является устройство [1], содержащее четыре элемента СЛОЖЕНИЕ ПО MOD2, четыре замыкающих ключа и четыре размыкающих ключа.

Недостатком прототипа является ограниченность разрядности сравниваемых кодов и низкое быстродействие, зависящее от разрядности сравниваемых кодов.

Задача изобретения - создать устройство, обеспечивающее расширение функциональных возможностей за счет обработки n-разрядных кодов для сравнения и повышение среднего быстродействия устройства.

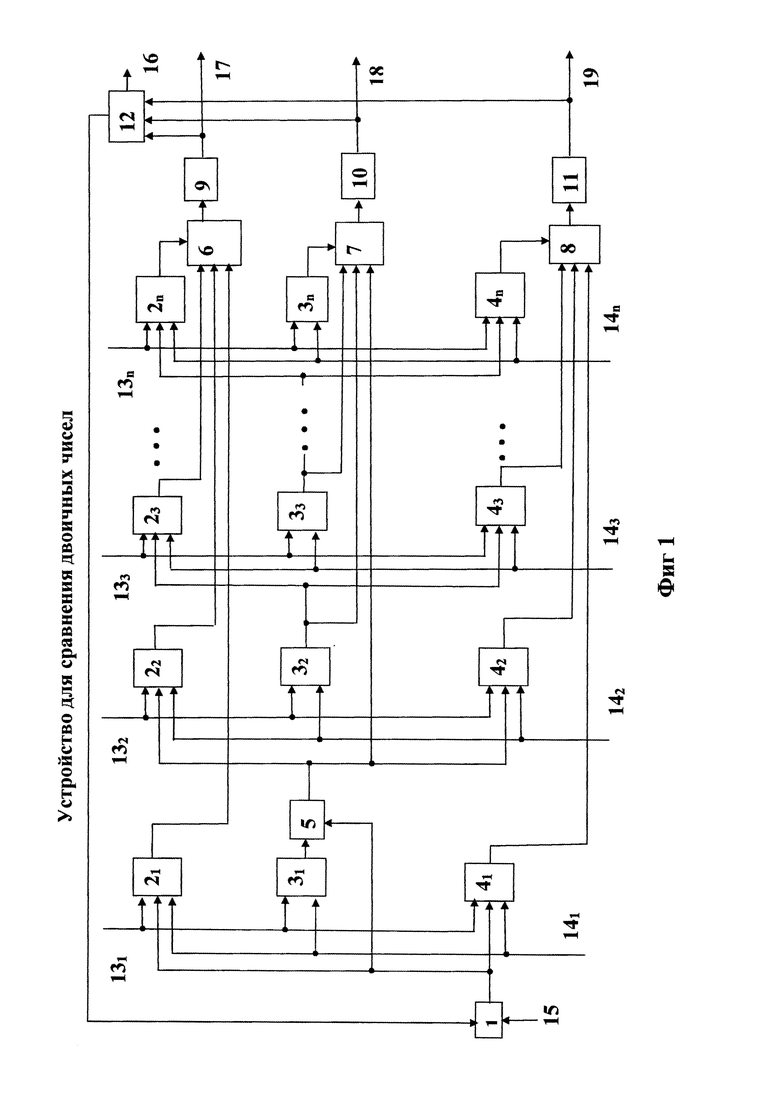

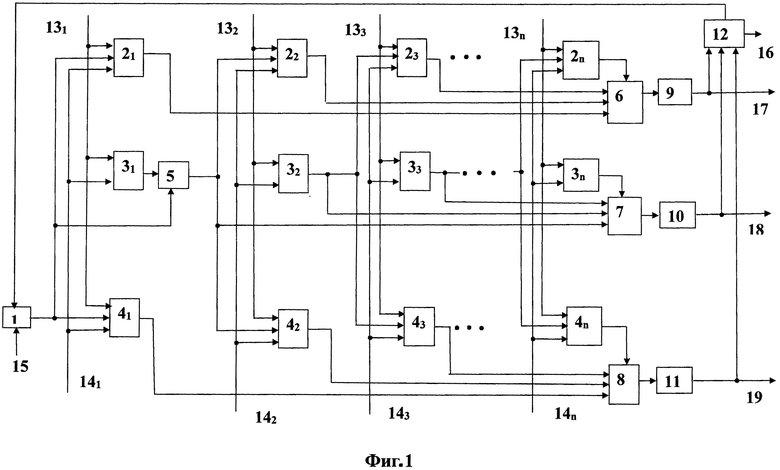

Это решение достигается тем, что в устройство, содержащее первую группу элементов И 2i (i=1…n, где n - разрядность сравниваемых двоичных кодов чисел А и В), группу 3i (i=1…n) элементов СЛОЖЕНИЕ ПО MOD2, первый и второй входы i-го элемента (i=1…n) СЛОЖЕНИЕ ПО MOD2 соединены соответственно с 13i (i=1…n) и 14i (i=1…n) входами устройства, вход 13i (i=1…n) подсоединен к первому входу элемента И 2i (i=1…n), отличающееся тем, что в него дополнительно введены второй элемент И 1, третий элемент И 5, группа четвертых элементов И 4i (i=1…n), первый элемент ИЛИ 6, пятый элемент И 7, второй элемент ИЛИ 8, первый триггер 9, второй триггер 10, третий триггер 11, третий элемент ИЛИ 12, вход 15 устройства подсоединен к первому входу второго элемента И 1, второй вход которого подсоединен к инверсному выходу третьего элемента ИЛИ 12, а выход - к первому входу третьего элемента И 5, к управляющим входам первой группы элементов И 21 и к первому входу четвертой группы элементов И 41, второй вход третьего элемента И 5 подсоединен к выходу элемента 31 СЛОЖЕНИЕ ПО MOD2, а выход - к управляющим входам первой группы элементов И 22 и к первому входу четвертой группы элементов И 42, входы устройства 13i (i=1…n) подсоединены к инверсным входам четвертой группы элементов И 4i, входы устройства 14i (i=1…n) подсоединены к инверсным входам первой группы элементов И 2i, выходы i-го элемента (i=2…n) СЛОЖЕНИЕ ПО MOD2 3i подсоединены к одноименным входам пятого элемента И 7, к управляющим входам первой группы элементов И 2i (i=2…n) и четвертой группы элементов И 4i, вторые входы четвертой группы элементов И 4i (i=2…n) подсоединены к входам устройства 14i (i=1…n), выходы четвертой группы элементов И 4i подсоединены к одноименным входам второго элемента ИЛИ 8, выход которого подсоединен к входу третьего триггера 11, выход которого является выходом 19 устройства и подсоединен к первому входу третьего элемента ИЛИ 12, выход пятого элемента И 5 подсоединен к первому входу пятого элемента И 7, выход которого подсоединен к входу второго триггера 10, выход которого является выходом 18 устройства и подсоединен к второму входу третьего элемента ИЛИ 12, выходы первой группы элементов И 2i (i=1…n) подсоединены к одноименным входам первого элемента ИЛИ 6, выход которого подсоединен к входу первого триггера 9, выход которого является выходом 17 устройства и подсоединен к третьему входу третьего элемента ИЛИ 12, прямой выход которого является выходом 16 окончания работы устройства.

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

Сущность изобретения поясняется чертежом (фиг. 1), где представлены элемент И 1, группа элементов И 21 … И 2n, группа элементов СЛОЖЕНИЕ ПО MOD2 31…3n, группа элементов И 41 … И 4n, элемент И 5, элемент ИЛИ 6, элемент И 7, элемент ИЛИ 8, триггер 9, триггер 10, триггер 11, элемент ИЛИ 12, входы 131…13n, входы 141…14n, вход 15, выход 16, выход 17, выход 18, выход 19.

В исходном состоянии на входы 131…13n подается двоичный код числа А (на a1 поступает старший разряд), а на входы 141…14n подается двоичный код числа В (на b1 поступает старший разряд). В случае равенства кодов (А=В) на выходах элементов СЛОЖЕНИЕ ПО MOD2 31…3n будет единичный сигнал, который, кроме первого, подается на одноименный вход элемента И 7. Триггеры 9, 10 и 11 находятся в нулевом состоянии.

Работа предлагаемого устройства осуществляется следующим образом. На его пусковой вход 15 подается единичный сигнал, после чего в случае равенства кодов (если А=В) на инверсных выходах элементов СЛОЖЕНИЕ ПО MOD2 31…3n будет единичный сигнал, который, кроме первого, подается на одноименный вход элемента И 7, а с выхода элемента СЛОЖЕНИЕ ПО MOD2 31 единичный сигнал через открытый элемент И 5 подается на одноименный вход элемента И 7.

В случае неравенства кодов (если a1>b1) на первом входе элемента И 21 будет единичный сигнал (так как a1=1), на втором (управляющем) входе элемента И 21 будет единичный пусковой сигнал с выхода элемента И 1, на третьем инверсном входе элемента И 21 будет нулевой сигнал, так как b1=0. Поэтому на выходе элемента И 21 будет единичный сигнал, который через элемент ИЛИ 6 устанавливает в единичное состояние триггер 9. Единичный сигнал на выходе триггера 9 поступает на выход 17 устройства и на одноименный вход элемента ИЛИ 12, с инверсного выхода которого нулевой сигнал закрывает элемент И 1. С прямого выхода элемента ИЛИ 12 единичный сигнал поступает на выход 16 - конец работы устройства.

Аналогично в случае неравенства кодов (если a1<b1) на первом инверсном входе элемента И 41 будет нулевой сигнал (a1=0), на втором (управляющем) входе элемента И 41 будет единичный пусковой сигнал с выхода элемента И 1, на третьем входе элемента И 41 будет единичный сигнал, так как b1=1. Поэтому на выходе элемента И 41 будет единичный сигнал, который через элемент ИЛИ 8 устанавливает в единичное состояние триггер 11. Единичный сигнал на выходе триггера 11 поступает на выход 19 устройства и на одноименный вход элемента ИЛИ 12, с инверсного выхода которого нулевой сигнал закрывает элемент И 1. С прямого выхода элемента ИЛИ единичный сигнал поступает на выход 16 - конец работы устройства.

В случае равенства a1=b1 на выходе элемента И 5 будет единичный сигнал, который подается на одноименный вход элемента И 7 и на управляющие входы элемента И 22 и элемента И 42, после чего сравнение очередных двух младших разрядов чисел А и В будет продолжаться аналогично. При этом с выхода элемента 31 единичный сигнал через открытый элемент И 5 подается на одноименный вход элемента И 7.

Единичный сигнал на выходе элемента И 7 устанавливает в единичное состояние триггер 10. Единичный сигнал на выходе триггера 10 поступает на выход 18 устройства и на одноименный вход элемента ИЛИ 12, с инверсного выхода которого нулевой сигнал закрывает элемент И 1. С прямого выхода элемента ИЛИ единичный сигнал поступает на выход 16 - конец работы устройства.

Таким образом, минимальное время Тзад работы устройства равно времени задержки сигнала элементами И1, И 2, ИЛИ 6 и триггером 9, а среднее время составляет (Тзад*n)/2, где n - разрядность сравниваемых кодов.

Результатом работы устройства являются единичные сигналы на выходах 17 - (если А>В), 18 - (если А=В), 19 - (если А<В) и 16 - конец работы устройства.

Использованные источники

1. SU N 2504825, кл. G06F 7/02.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования графика работы сотрудников учреждения | 2018 |

|

RU2685980C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ГРАФИКА РАБОТЫ СОТРУДНИКОВ УЧРЕЖДЕНИЯ | 2010 |

|

RU2434273C1 |

| Устройство для распределения заданий | 1991 |

|

SU1833873A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ГРАФИКА РАБОТЫ СОТРУДНИКОВ УЧРЕЖДЕНИЯ | 2011 |

|

RU2480827C1 |

| Устройство для моделирования нейрона | 1991 |

|

SU1831715A3 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ПРЕДПОЧТИТЕЛЬНОГО УРОВНЯ УНИФИКАЦИИ ТЕХНИЧЕСКИХ СРЕДСТВ | 2014 |

|

RU2586573C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ГРАФИКА РАБОТЫ СОТРУДНИКОВ УЧРЕЖДЕНИЯ | 2013 |

|

RU2526005C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ ЗАЩИТЫ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 2007 |

|

RU2335016C1 |

| МНОГОВЫХОДНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2613536C1 |

| Устройство для решения задачи о назначениях | 2016 |

|

RU2613523C1 |

Изобретение относится к области цифровой вычислительной техники и автоматики. Технический результат заключается в повышении быстродействия устройства для сравнения двоичных чисел. Технический результат достигается за счет устройства для сравнения двоичных чисел, содержащего первую группу элементов И 2i, группу 3i (i=1…n) элементов СЛОЖЕНИЕ ПО MOD2, первый и второй входы i-го элемента (i=1…n) СЛОЖЕНИЕ ПО MOD2, второй элемент И 1, третий элемент И 5, группу четвертых элементов И 4i (i=1…n), первый элемент ИЛИ 6, пятый элемент И 7, второй элемент ИЛИ 8, первый триггер 9, второй триггер 10, третий триггер 11, третий элемент ИЛИ 12. 1 ил.

Устройство для сравнения двоичных чисел, содержащее первую группу элементов И 2i (i=1…n, где n - разрядность сравниваемых двоичных кодов чисел А и В), группу 3i (i=1…n) элементов СЛОЖЕНИЕ ПО MOD2, первый и второй входы i-го элемента (i=1…n) СЛОЖЕНИЕ ПО MOD2 соединены соответственно с 13i (i=1…n) и 14i (i=1…n) входами устройства, вход 13i (i=1…n) подсоединен к первому входу элемента И 2i (i=1…n), отличающееся тем, что в него дополнительно введены второй элемент И 1, третий элемент И 5, группа четвертых элементов И 4i (i=1…n), первый элемент ИЛИ 6, пятый элемент И 7, второй элемент ИЛИ 8, первый триггер 9, второй триггер 10, третий триггер 11, третий элемент ИЛИ 12, вход 15 устройства подсоединен к первому входу второго элемента И 1, второй вход которого подсоединен к инверсному выходу третьего элемента ИЛИ 12, а выход - к первому входу третьего элемента И 5, к управляющим входам первой группы элементов И 21 и к первому входу четвертой группы элементов И 41, второй вход третьего элемента И 5 подсоединен к выходу элемента 31 СЛОЖЕНИЕ ПО MOD2, а выход - к управляющим входам первой группы элементов И 22 и к первому входу четвертой группы элементов И 42, входы устройства 13i (i=1…n) подсоединены к инверсным входам четвертой группы элементов И 4i, входы устройства 14i (i=1…n) подсоединены к инверсным входам первой группы элементов И 2i, выходы i-го элемента (i=2…n) СЛОЖЕНИЕ ПО MOD2 3i подсоединены к одноименным входам пятого элемента И 7, к управляющим входам первой группы элементов И 2i (i=2…n) и четвертой группы элементов И 4i, вторые входы четвертой группы элементов И 4i (i=2…n) подсоединены к входам устройства 14i (i=1…n), выходы четвертой группы элементов И 4i подсоединены к одноименным входам второго элемента ИЛИ 8, выход которого подсоединен к входу третьего триггера 11, выход которого является выходом 19 устройства и подсоединен к первому входу третьего элемента ИЛИ 12, выход пятого элемента И 5 подсоединен к первому входу пятого элемента И 7, выход которого подсоединен к входу второго триггера 10, выход которого является выходом 18 устройства и подсоединен к второму входу третьего элемента ИЛИ 12, выходы первой группы элементов И 2i (i=1…n) подсоединены к одноименным входам первого элемента ИЛИ 6, выход которого подсоединен к входу первого триггера 9, выход которого является выходом 17 устройства и подсоединен к третьему входу третьего элемента ИЛИ 12, прямой выход которого является выходом 16 окончания работы устройства.

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2012 |

|

RU2504825C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2011 |

|

RU2475812C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

Авторы

Даты

2018-08-28—Публикация

2018-02-05—Подача