Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также для анализа свойств генераторов псевдослучайных последовательностей двоичных чисел.

Известны система и способ подсчета начальных нулевых разрядов и подсчета начальных единичных разрядов в цифровом процессоре сигналов (RU №2409837 С2, МПК G06F 7/74, заявлен 27.07.2006, опубликовано 20.01.2011, Бюл. №2) в котором определяется количество разрядов для различных размеров слов данных. В устройстве проводится расширение входных данных знаком до временного шестидесятичетырехразрядного слова данных. При подсчете нулевых разрядов проводится инвертирование разрядов слова. Для подсчета начальных разрядов используется двоичный счетчик.

Недостатком данного устройства является низкое быстродействие, а также подсчет только начальных нулевых разрядов и начальных единичных разрядов в цифровом сигнале.

Известно устройство для определения количества единиц в упорядоченном двоичном числе (RU №2522875, МПК Н03К 21/12, заявлено 24.05.2012, опубликовано 20.07.2014, Бюл. №20), содержащее буферы с тремя состояниями с прямым и инверсным входами разрешения, n разрядов входного двоичного числа, (k+1) разрядов выходного двоичного кода (k=[log2n] меньшее целое), причем буферы с тремя состояниями объединены в пирамидальную структуру, состоящую из (m-1) ступеней (m=]log2n[ большее целое), и в выходной блок, содержащий k буферов с тремя состояниями с инверсным входом разрешения и k буферов с тремя состояниями с прямым входом разрешения, при этом каждая i-я ступень (i=1, …, (m-1)) содержит (2i-1) буферов с тремя состояниями с инверсным входом разрешения и 2i-1 буферов с тремя состояниями с прямым входом разрешения.

Недостатком данного устройства является определение количества единиц в только упорядоченном двоичном числе, а не в группах нулевых и единичных разрядов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство для определения количества единиц (нулей) в двоичном числе (RU №2446442, МПК G06F 7/50, Н03К 21/00, заявлено 11.04.2011, опубликовано 27.03.2012, Бюл. №9), содержащее блок управляемой инверсии, состоящий из n-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ» (n - количество разрядов входного числа), элементы ИЛИ и модули, состоящие из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, которые объединены в группы, состоящие из ярусов, и объединены в k-каскадов (k=]log2n[), так, что каждый i-й каскад содержит g(i)=n/2i групп (i=1, …, k), каждая группа i-го каскада разделена на j ярусов (j=1, …, i), при этом первый ярус каждой группы i-го каскада содержит i модулей, а каждый j-й ярус каждой группы i-го каскада (j=2, …, i,) содержит (i-j) модулей и элемент «ИЛИ».

Недостатком данного устройства является определение только общего количества единиц (нулей) в двоичном числе, а не по группам нулевых и единичных разрядов.

К причинам, препятствующим достижению указанного ниже технического результата, относится отсутствие средств для выделения групп и определения количества нулевых и единичных разрядов в группах, и определение общего количества групп.

Техническим результатом изобретения является расширение функциональных возможностей в части возможности определения количества единичных и нулевых разрядов по группам в двоичных числах и определение общего количества групп, а также простое увеличение разрядности входной информации.

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для определения количества нулей и единиц по группам в двоичном числе

содержит N разрядов входного двоичного числа D1, D2, …, DN, (N+1) групп выходных данных G1, G1, …, G(N+1), выходную группу К количества групп нулей и единиц, группу из (N-1) внутренних шин упорядоченных двоичных чисел S1, S2, …, S(N-1), (N-1) каскадов формирователя упорядоченных двоичных чисел 11, 12, …, 1N, которые объединены в пирамидальную структуру, причем каждый i-й каскад 1i (i=1, …, (N-1)) содержит группу из (N-i) элементов ИЛИ 21, 22, …, 2(N-i), группу из (N-i) элементов XOR 31, 32, …, 3(N-i), группу из (N+1-i) входов A1, А2, …, A(N+1-i), группу из (N-i) выходов Q1, Q2, …, Q(N-i) в следующий каскад и группу из (N+1-i) выходов разрядов соответствующей i-й внутренней шины Si из группы S1, S2, …, S(N-1),

а также в устройство введены первая группа из (N-i) блоков счета младших упорядоченных единиц 41, 42, …, 4(N-i), группа из N сумматоров 51, 52, …, 5N, с инверсной группой входов второго слагаемого, элемент ИЛИ с одним инверсным входом 6 и второй блок счета младших упорядоченных единиц 7, причем каждый i-й сумматор 5i содержит ]log2(N+3-i)[ (большее целое) разрядов, а последний N-й сумматор 5N содержит два разряда,

причем N разрядов входного двоичного числа D1, D2, …, DN соединены с одноименными входами A1, А2, …, AN первого каскада 11,

в каждом i-м каскаде первые (N-i) входов A1, А2, …, A(N-i), кроме последнего входа A(N+1-i), также соединены со вторыми входами соответствующих одноименных элементов ИЛИ 21, 22, …, 2(N-i) и вторыми входами одноименных элементов XOR 31, 32, …, 3(N-i), а первые входы первых (N-i-1) элементов 21, 22, …, 2(N-i-1) из группы элементов ИЛИ соединены с выходами соответствующих последующих элементов 22, 23, …, 2(N-i) из группы элементов ИЛИ, первый вход последнего элемента 2(N-i) из группы элементов ИЛИ соединен с последним входом запроса A(N+1-i) i-го каскада, выходы (N-i) элементов ИЛИ 21, 22, …, 2(N-i) соединены также с первыми входами соответствующих одноименных элементов XOR 31, 32, …, 3(N-i), выходы которых являются группой (N-i) выходов Q1, Q2, …, Q(N-i) в следующий каскад каждого i-го каскада, а выходы всех (N-i) элементов ИЛИ 21, 22, …, 2(N-i) являются одноименными первыми младшими (N-i) разрядами соответствующей i-й внутренней шины Si из группы S1, S2, …, S(N-1), а последний вход A(N+1-i) i-го каскада является старшим (N+1-i)-м разрядом соответствующей i-й внутренней шины Si,

причем в первых (N-2) каскадах, кроме последнего (N-1)-го каскада, (N-i) выходов в следующий (i+1)-й каскад Q1, Q2, …, Q(N-i) соединены с соответствующими (N-i) одноименными входами A1, А2, …, A(N-i) следующего (i+1)-го каскада,

все разряды каждой i-й внутренней шины Si из группы S1, S2, …, S(N-1) соединены с входами соответствующего одноименного блока 4i из первой группы из (N-i) блоков счета младших упорядоченных единиц, а выходы каждого i-го блока 4i соединены с инверсной группой входов второго слагаемого i-го сумматора 5i и первой группой прямых входов первого слагаемого (i+1)-го сумматора 5(i+1) из группы из N сумматоров 51, 52, …, 5N, выходы которых являются соответствующими первыми N группами выходных данных G1, G2, …, GN, а последний одноразрядный выход G(N+1) соединен с выходом Q1 последнего (N-1) каскада 1(N-1), который также соединен со второй инверсной группой входов последнего N-го сумматора 5N и первым прямым входом элемента ИЛИ с одним инверсным входом 6, второй инверсный вход которого соединен со старшим N-м разрядом DN входного двоичного числа,

на группу первых прямых входов первого сумматора 51 подано двоичное число «N», а на входы переносов CI всех N сумматоров 51, 52, …, 5N подано значение логической единицы,

младшие первые разряды всех (N-1) внутренних шин упорядоченных двоичных чисел S1, S2, …, S(N-1) соединены с соответствующими входами второго блока счета младших упорядоченных единиц 7, а также соответствующий N-й вход которого соединен с выходом элемента ИЛИ с одним инверсным входом 6, а выходы второго блока счета младших упорядоченных единиц 7 являются выходной группой К количества групп нулей и единиц, причем количество групп К содержит ]log2(N+1)[ (большее целое) разрядов.

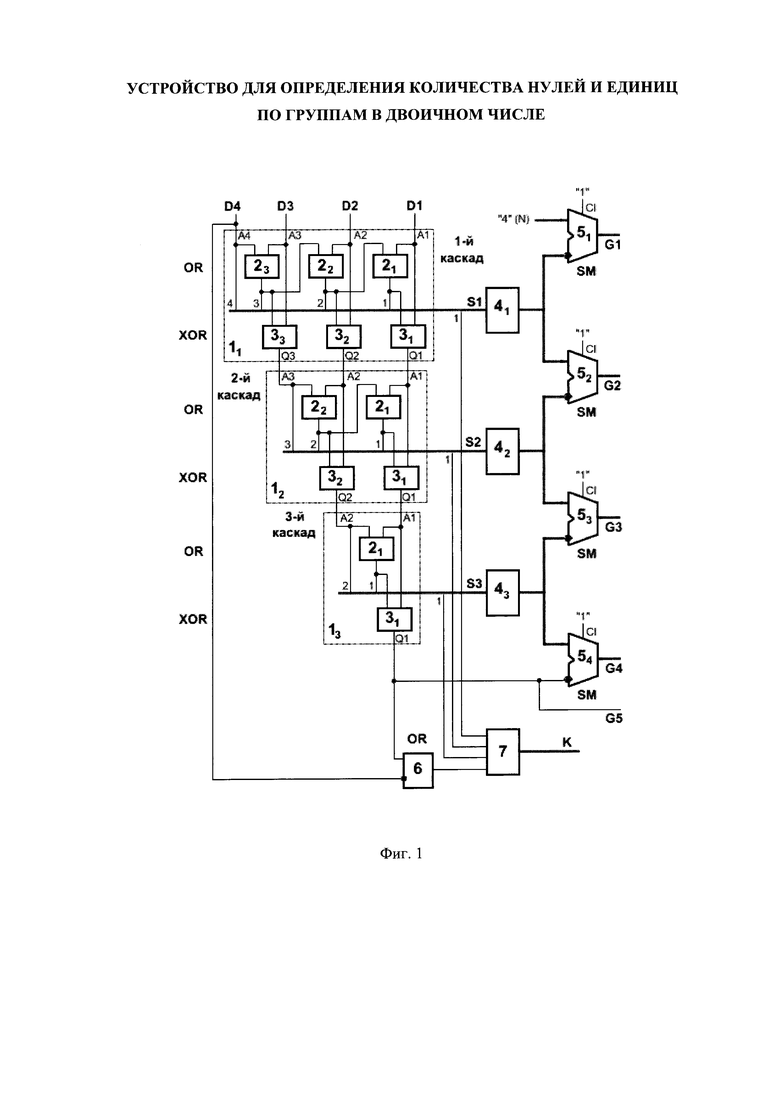

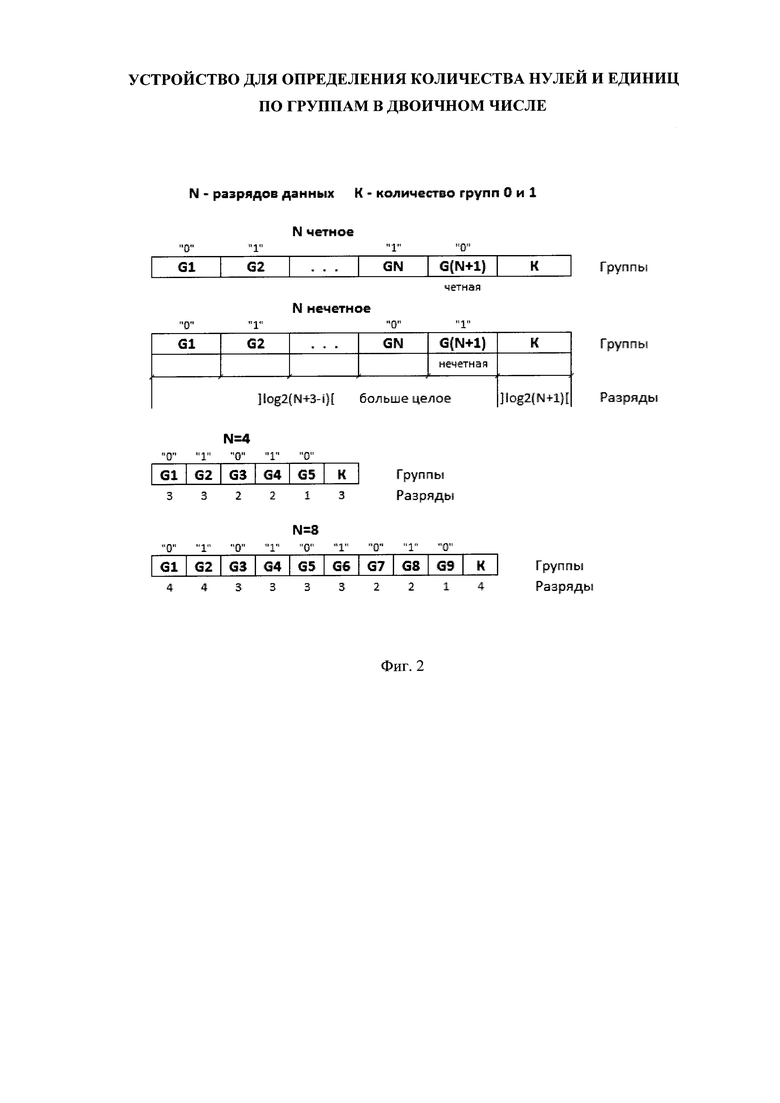

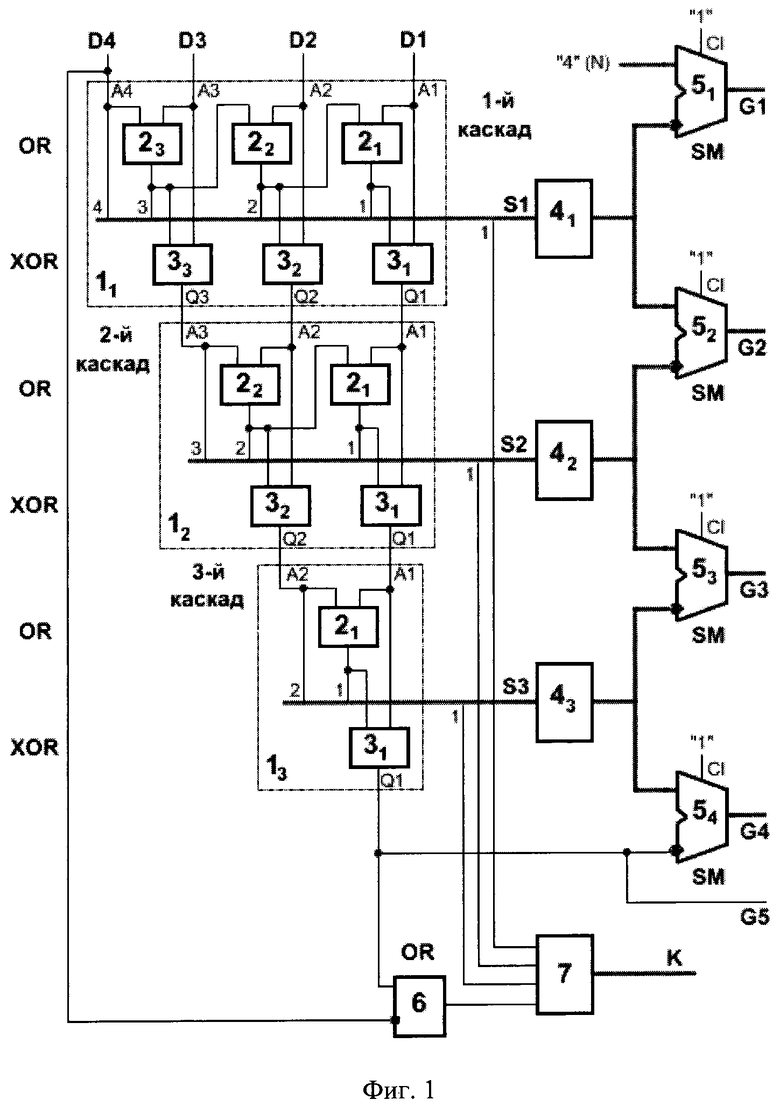

На фиг. 1 представлена схема предлагаемого устройства для определения количества нулей и единиц по группам в двоичном числе при N=4. На фиг. 2 приведен формат выходных данных для N разрядов входных данных и для N=4 и N=8. В таблице 1 приведены примеры формирования значений количества нулей и единиц по группам G1, G1, …, G5 и общего количества групп К при N=4.

На фиг. 1 и в тексте приняты следующие обозначения:

A1, А2, …, A(N+1-i) - входы i-го каскада (i=1, …, (N-1)) формирователя упорядоченных двоичных чисел,

CI - входы переносов сумматоров,

D1, D2, …, D4 (DN) - N разрядов входного двоичного числа (при N=4),

G1, G1, …, G5 (GN+1) - (N+1) групп выходных данных (при N=4), каждая из которых содержит ]log2(N+3-i)[ (большее целое) разрядов,

K - выходная группа количества групп нулей и единиц, содержит ]log2(N+1)[ (большее целое) разрядов.

Q1, Q2, …, Q(N-i) - выходы i-го каскада в следующий каскад формирователя упорядоченных двоичных чисел,

S1, S2, S3 (SN-1) - (N-1) внутренних шин упорядоченных двоичных чисел,

SM - сумматоры,

11, 12, 13 (1(N-1)) - (N-1) каскадов формирователя упорядоченных двоичных чисел,

21, 22, 23 (2N-i) - группа из (N-i) элементов ИЛИ i-го каскада формирователя упорядоченных двоичных чисел,

31, 32, 33 (3N-i) - группа из (N-i) элементов XOR i-го каскада формирователя упорядоченных двоичных чисел,

41, 42, 43 (4N-i) - первая группа из (N-i) блоков счета младших упорядоченных единиц,

51, 52, 53, 54 (5N) - группа из N сумматоров,

6 - элемент ИЛИ с одним инверсным входом,

7 - второй блок счета младших упорядоченных единиц.

Предлагаемое устройство для определения количества нулей и единиц по группам в двоичном числе содержит N разрядов входного двоичного числа D1, D2, …, DN, (N+1) групп выходных данных G1, G1, …, G(N+1), выходную группу К количества групп нулей и единиц, группу из (N-1) внутренних шин упорядоченных двоичных чисел S1, S2, …, S(N-1), (N-1) каскадов формирователя упорядоченных двоичных чисел 11, 12, …, 1N, которые объединены в пирамидальную структуру, причем каждый i-й каскад 1i (i=1, …, (N-1)) содержит группу из (N-i) элементов ИЛИ 21, 22, …, 2(N-i), группу из (N-i) элементов XOR 31, 32, …, 3(N-i), группу из (N+1-i) входов A1, А2, …, A(N+1-i), группу из (N-i) выходов Q1, Q2, …, Q(N-i) в следующий каскад и группу из (N+1-i) выходов разрядов соответствующей i-й внутренней шины Si из группы S1, S2, …, S(N-1), а также в устройство введены первая группа из (N-i) блоков счета младших упорядоченных единиц 41, 42, …, 4(N-i), группа из N сумматоров 51, 52, …, 5N, с инверсной группой входов второго слагаемого, элемент ИЛИ с одним инверсным входом 6 и второй блок счета младших упорядоченных единиц 7, причем каждый i-й сумматор 5i содержит ]log2(N+3-i)[ (большее целое) разрядов, а последний N-й сумматор 5N содержит два разряда.

Причем N разрядов входного двоичного числа D1, D2, …, DN соединены с одноименными входами A1, А2, …, AN первого каскада 11.

В каждом i-м каскаде первые (N-i) входов A1, А2, …, A(N-i), кроме последнего входа A(N+1-i), также соединены со вторыми входами соответствующих одноименных элементов ИЛИ 21, 22, …, 2(N-i) и вторыми входами одноименных элементов XOR 31, 32, …, 3(N-i), а первые входы первых (N-i-1) элементов 21, 22, …, 2(N-i-1) из группы элементов ИЛИ соединены с выходами соответствующих последующих элементов 22, 23, …, 2(N-i) из группы элементов ИЛИ, первый вход последнего элемента 2(N-i) из группы элементов ИЛИ соединен с последним входом запроса A(N+1-i) i-го каскада. Выходы (N-i) элементов ИЛИ 21, 22, …, 2(N-i) соединены также с первыми входами соответствующих одноименных элементов XOR 31, 32, …, 3(N-i), выходы которых являются группой (N-i) выходов Q1, Q2, …, Q(N-i) в следующий каскад каждого i-го каскада. Выходы всех (N-i) элементов ИЛИ 21, 22, …, 2(N-i) являются одноименными первыми младшими (N-i) разрядами соответствующей i-й внутренней шины Si из группы S1, S2, …, S(N-1), а последний вход A(N+1-i) i-го каскада является старшим (N+1-i)-м разрядом соответствующей i-й внутренней шины Si.

В первых (N-2) каскадах, кроме последнего (N-1)-го каскада, (N-i) выходов в следующий (i+1)-й каскад Q1, Q2, …, Q(N-i) соединены с соответствующими (N-i) одноименными входами A1, А2, …, A(N-i) следующего (i+1)-го каскада.

Все разряды каждой i-й внутренней шины Si из группы S1, S2, …, S(N-1) соединены с входами соответствующего одноименного блока 4i из первой группы из (N-i) блоков счета младших упорядоченных единиц, а выходы каждого i-го блока 4i соединены с инверсной группой входов второго слагаемого i-го сумматора 5i и первой группой прямых входов первого слагаемого (i+1)-го сумматора 5(i+1) из группы из N сумматоров 51, 52, …, 5N.

Выходы группы из N сумматоров 51, 52, …, 5N являются соответствующими первыми N группами выходных данных G1, G2, …, GN, а последний одноразрядный выход G(N+1) соединен с выходом Q1 последнего (N-1) каскада 1(N-1), который также соединен со второй инверсной группой входов последнего N-го сумматора 5N и первым прямым входом элемента ИЛИ с одним инверсным входом 6, второй инверсный вход которого соединен со старшим N-м разрядом DN входного двоичного числа.

На группу первых прямых входов первого сумматора 51 подано двоичное число «N», а на входы переносов CI всех N сумматоров 51, 52, …, 5N подано значение логической единицы.

Младшие первые разряды всех (N-1) внутренних шин упорядоченных двоичных чисел S1, S2, …, S(N-1) соединены с соответствующими входами второго блока счета младших упорядоченных единиц 7, а также соответствующий N-й вход которого соединен с выходом элемента ИЛИ с одним инверсным входом 6.

Выходы второго блока счета младших упорядоченных единиц 7 являются выходной группой К количества групп нулей и единиц, причем количество групп К содержит ]log2(N+1)[ (большее целое) разрядов.

Принцип работы предлагаемого устройства состоит в следующем.

На входы устройства поступает входное N разрядное двоичное число без знака D1, D2, …, DN, которое поступает на входы A1, А2, …, AN первого каскада 11. Старший разряд DN является старшим разрядом входного двоичного числа.

На первом шаге анализируется наличие единичных значений во входных данных и в первом 11 каскаде N разрядное двоичное число D1, D2, …, DN на выходах группы элементов ИЛИ 21, 22, …, 2(N-i), объединенных в цепочку, преобразуется в упорядоченный двоичный код «00…011…1» с единицами расположенными подряд, начиная с младших разрядов, где левая единица соответствует старшей единице во входном двоичном числе, который одновременно со старшим разрядом входных данных DN поступают на внутреннюю шину S1. Количество единиц является дополнением до N к количеству нулей во входном двоичном числе и соответствует сумме всех разрядов кроме первой «нулевой» группы.

Далее в первом блоке 41 счета младших упорядоченных единиц проводится подсчет количества единиц. Полученное количество единиц поступает на вторую инверсную группу второго слагаемого первого сумматора 51 и вычитается из количества разрядов N входных данных, заданном двоичным кодом «N» на входах первого слагаемого и при единичном значении на входе переноса CI=1, что соответствует операции вычитания для чисел без знака. При этом полученная разность на выходе первого сумматора 51 соответствует количеству нулей в первой «нулевой» группе входного двоичного числа D1, D2, …, DN, которое поступает на внешние выходы первой группы G1«0» устройства.

Далее младшие разряды входного двоичного числа D1, D2, …, D(N-1), соответствующие единичным значениям в упорядоченном двоичном коде «00…011…1» на выходах группы элементов ИЛИ 21, 22, …, 2(N-i), инвертируются в группе элементов XOR 31, 32, …, 3(N-i), которые можно рассматривать как элементы «управляемый инвертор», и поступают на выходы Q1, Q2, …, Q(N-i) первого каскада 11 и далее на входы A1, А2, …, A(N-i) следующего второго каскада 12. При этом первая «единичная» группа входного двоичного числа D1, D2, …, DN преобразуется в нулевые значения, а вторая «нулевая» группа (третья группа во входном числе) преобразуется в единичные значения и т.д.

Во втором каскаде 12 аналогично формируется упорядоченный двоичный код «00…011…1» который поступает на внутреннюю шину S2, где левая единица соответствует старшей единице - началу третьей группы во входном двоичном числе D1, D2, …, DN, а количество нулей соответствует сумме двух групп - первой группе нулей и второй группе единиц во входном двоичном числе D1, D2, …, DN. Во втором блоке 42 счета младших упорядоченных единиц аналогично проводится подсчет количества единиц. Полученное количество единиц на втором сумматоре 52 вычитается из суммы разрядов всех групп кроме первой, которое поступает с выходов первого блока 41 счета младших упорядоченных единиц, и формируется значение, соответствующее количеству единиц во второй «единичной» группе входного двоичного числа D1, D2, …, DN, которое поступает на внешние выходы второй группы G2«1» устройства.

Далее аналогично инвертируются младшие разряды входных данных второго каскада 12, которые поступают на выходы Q1, Q2, …, Q(N-i) второго каскада.

Затем аналогично проводится вычисление и формирование сумм в третьем, четвертом и последующих каскадах.

Выход Q1 последнего (N-1) каскада 1(N-1) поступает на первый прямой вход элемента ИЛИ с одним инверсным входом 6, на второй инверсный вход которого поступает значение старшего N-го разряда DN входного двоичного числа.

Кроме того, первые младшие разряды всех внутренних шин из группы S1, S2, …, S(N-1) и выход элемента ИЛИ 6 поступают на входы второго блока 7 счета младших упорядоченных единиц, в котором проводится подсчет количества единиц, и это значение соответствует количеству групп нулей и единиц во входном двоичном числе D1, D2, …, DN, и поступает на выходную группу К.

В таблице 1 приведены примеры формирования значений количества нулей и единиц по группам G1, G1, …, G5 (GN+1) и общего количества групп К при N=4.

Формат выходных данных приведен на фиг. 2. Общее количество групп может быть равно (N+1). При этом в выходных данных первая группа G1«0» и последующие нечетные группы содержат количество разрядов в «нулевых» группах, а вторая группа G2«1» и последующие четные группы содержат количество разрядов в «единичных» группах. Количество разрядов в каждой группе равно ]log2(N+3-i)[ (большее целое). Общее количество групп К содержит ]log2(N+1)[ (большее целое) разрядов.

Предлагаемое устройство для определения количества нулей и единиц по группам в двоичном числе работает следующим образом.

На внешние входы устройства D1, D2, …, DN поступает N разрядное двоичное число без знака. Данные сигналы поступают на входы A1, А2, …, AN первого каскада 11. В первом каскаде 11 на выходах группы элементов ИЛИ 21, 22, …, 2(N-i), объединенных в цепочку, N разрядное двоичное число D1, D2, …, DN преобразуется в упорядоченный двоичный код «00…011…1» с единицами расположенными подряд, начиная с младших разрядов, где левая единица соответствует старшей единице во входном двоичном числе, который поступает на внутреннюю шину S1. Например, при N=4 для входного числа D4-D1=0010 (таблица 1) на выходах элементов ИЛИ 21, 22, 23 первого каскада 11 формируется упорядоченный двоичный код «011», который совместно со старшим разрядом D4=0 входных данных поступает на первую внутреннюю шину S1 и блоке 41 вычисляется код «2» суммы младших единиц. Далее этот код «2» поступает на инверсные входы первого сумматора 51 и вычитается из кода «4» количества разрядов N=4 входного числа (4-2). Таким образом, на выходах первой «нулевой» группы G1«0» будет сформирован код «2» соответствующий количеству первых старших нулей во входном числе.

Далее в группе элементов XOR 31, 32, 33 (3(N-i)) (при N=4) первого каскада 11 инвертируются два младших разряды, и формируется код «001» (для входных данных D4-D1=0010 в таблице 1), который поступает на соответствующие выходы Q1, Q2, Q3 и далее на входы A1, А2, A3 второго каскада 12.

Во втором каскаде 12 на выходах элементов ИЛИ 21, 22 формируется упорядоченный двоичный код «01», который совместно со значением старшего разряда D4=0 поступают на внутреннюю шину S2. Затем во втором блоке 42 вычисляется код суммы единиц «1» и далее на втором сумматоре 52 формируется код «1» как разность «2-1», соответствующий количеству единиц в первой группе во входном числе, и который поступает на выходы второй «единичной» группы G2«1». Затем в группе элементов XOR 31, 32 (3(N-i)) (при N=4) второго каскада 12 инвертируются младшие разряды, и формируется код «00», который поступает на соответствующие выходы Q1, Q2 и далее на входы A1, А2 третьего каскада 13.

В третьем каскаде 13 аналогично формируется упорядоченный двоичный код «0» на выходе элемента ИЛИ 21, который поступает на внутреннюю шину S3, далее в третьем блоке 43 вычисляется код суммы единиц «0» и далее на третьем сумматоре 53 формируется код «1» как разность «1-0», соответствующий количеству нулей во второй группе во входном числе. Таким образом, на выходах второй «нулевой» группы G3«0» будет сформирован код «1» соответствующий количеству нулей в третьей группе во входном числе.

Одновременно младшие разряды внутренних шин S1, S2, S3, на которых установлены значения «110», и инверсное значение старшего разряда D4 (DN) входных данных (единичное значение для входных данных 0010) с выхода элемента ИЛИ 6 поступают на входы второго блока 7 счета младших упорядоченных единиц, в котором будет сформирован код «3» соответствующий общему количеству групп нулей и единиц для входного двоичного числа D4-D1=0010, который поступает в выходную группу К=3. При этом также в группах будут установлены значения: G1«0»=2, G2«1»=1, G3«0»=1.

Аналогично для входного двоичного числа D4-D1=0101, при нулевом значении старшего разряда D4=0 (DN) входных данных, формируются значения нулей и единиц G1«0»=1, G2«1»=1, G3«0»=1, G4«1»=1 и общее количество групп К=4, соответствующее максимальному количеству групп при количестве разрядов N=4 входного числа.

Для входного двоичного числа «все нули» D4-D1=0000 на выходах элементов ИЛИ 21, 22, 23 первого каскада 11 формируется также «нулевой» упорядоченный двоичный код «000», и далее также формируется «нулевой» код суммы «0» младших единиц в блоке 41 (при этом D4=0), который поступает на инверсные входы первого сумматора 51 и вычитается из кода «4» количества разрядов N=4 входного числа (4-0). Таким образом, на выходах первой «нулевой» группы G1«0» будет сформирован код «4» (G1«0»=4), соответствующий количеству всех нулевых разрядов во входном числе D4-D1=0000. При этом нулевые значения также будут установлены на всех внутренних шинах S1, S2, S3, в том числе, и на младших первых разрядах шин, которые поступают на входы второго блока 7 счета младших упорядоченных единиц, на который также поступает единичное значение с выхода элемента ИЛИ 6 с одним инверсным входом, который соединен со старшим разрядом входных данных D4=0, и поэтому на выходах второго блока 7 будет сформирован код «1», который поступает на выходы общего количества групп К=1.

Для входных двоичных чисел D4-D1=1XXX, при единичном значении старшего разряда D4=1 (DN) входных данных, на выходах элементов ИЛИ 21, 22, 23 первого каскада 11 всегда формируется упорядоченный двоичный код все единицы «111», для которого совместно с D4=1 вычисляется код суммы «4» младших единиц в блоке 41, который поступает на инверсные входы первого сумматора 51 и вычитается из кода «4» количества разрядов N=4 входного числа (4-4). При этом на выходах первой «нулевой» группы G1«0» будет сформирован код «0», что соответствует входным данным, когда старший разряд имеет единичное значение D4=1.

Например, для входного двоичного числа D4-D1=1010, так как на выходах элементов ИЛИ 21, 22, 23 первого каскада 11 установлен упорядоченный двоичный код все единицы «111», то в группе элементов XOR 31, 32, 33 первого каскада 11 инвертируются все разряды, и формируется код «101», который поступает на соответствующие выходы Q1, Q2, Q3 и далее на входы A1, А2, A3 второго каскада 12.

Во втором каскаде 12 на выходах элементов ИЛИ 21, 22 формируется упорядоченный двоичный код «11», который совместно со значением старшего разряда D4=1 поступают на внутреннюю шину S2. Затем во втором блоке 42 вычисляется код суммы единиц «3» и далее на втором сумматоре 52 формируется код «1» как разность «4-3», соответствующий количеству единиц в первой группе во входном числе, и который поступает на выходы второй «единичной» группы G2«1»=1. Далее аналогично вычисляются последующие значения нулевых и единичных групп и на выходах групп устройства устанавливаются значения G1«0»=0, G2«1»=1, G3«0»=1, G4«1»=1, G5«0»=1. Одновременно единичные значения с младших разрядов всех внутренних шинах S1, S2, S3 и с выхода элемента ИЛИ 6 с одним инверсным входом (так как единичное значение установлено на выходе Q1 третьего каскада 13) поступают на входы второго блока 7 счета младших упорядоченных единиц и формируется код «4» общего количества групп К=4.

Для входного двоичного числа «все единицы» D4-D1=1111 на выходах элементов ИЛИ 21, 22, 23 первого каскада 11 формируется также упорядоченный двоичный код «111» и на внутренней шине S1 код «все единицы» «1111», для которого формируется код суммы «4» младших единиц в блоке 41 (так как при этом D4=1), который поступает на инверсные входы первого сумматора 51 и вычитается из кода количества разрядов N=4 входного числа (4-4). Таким образом, на выходах первой «нулевой» группы G1«0» будет сформирован код «0» (G1«0»=0), что соответствует отсутствию «нулевой» первой группы во входном числе. Далее в группе элементов XOR 31, 32, 33 (при N=4) первого каскада 11 инвертируются все младшие разряды, и формируется код «000», который поступает на соответствующие выходы Q1, Q2, Q3 и далее на входы A1, А2, A3 второго каскада 12. Затем во втором каскаде 12 на выходах элементов ИЛИ 21, 22 формируется двоичный код «00», который поступает на внутреннюю шину S2. Затем во втором блоке 42 вычисляется код суммы единиц «0», который вычитается из кода «4» с первого блока 41 (4-0) и формируется код «4» соответствующий количеству единиц в группе, который поступает на выходы второй «единичной» группы G2«1»=4. Одновременно единичное значение с младшего первого разряда первой внутренней шины S1 и нулевое значение с выхода элемента ИЛИ 6 поступают на вход второго блока 7 счета младших упорядоченных единиц и формируется код «1» общего количества групп К=1.

Таким образом, на выходах устройства G1, G1, …, G5(N+1) формируются двоичные коды, соответствующие количеству нулей и единиц в группах входного двоичного числа, при этом в нечетных группах Gнч указывается количество нулей, а в четных группах Gчт количество единиц, а также формируется общее количество групп К.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу - выделение групп, определение количества единичных и нулевых разрядов по группам и определение общего количества групп, обладает регулярностью узлов и связей, а также простым увеличением разрядности входных данных, т.е. соответствует заявляемому техническому результату.

Изобретение относится к области вычислительной техники. Технический результат заключается в расширении арсенала средств того же назначения. Устройство для определение количества нулей или единиц по группам в двоичном числе содержит N разрядов входного двоичного числа D1, …, DN, (N+1) групп выходных данных G1, …, G(N+1), выходную группу К количества групп нулей и единиц, группу из (N-1) внутренних шин упорядоченных двоичных чисел S1, …, S(N-1), (N-1) каскадов формирователя упорядоченных двоичных чисел 11, 12, …, 1N, и каждый i-й каскад 1i (i=1, …, (N-1)) содержит группу из (N-i) элементов ИЛИ 21,…, 2(N-i), группу из (N-i) элементов XOR 31, 32, …, 3(N-i), группу из (N+1-i) входов A1, …, A(N+1-i), группу из (N-i) выходов Q1, …, Q(N-i) в следующий каскад и группу из (N+1-i) выходов разрядов соответствующей i-й внутренней шины Si, а также в устройство введены первая группа из (N-i) блоков счета младших упорядоченных единиц 41, …, 4(N-i), группа из N сумматоров 51,…, 5N, с инверсной группой входов второго слагаемого, элемент ИЛИ с одним инверсным входом 6 и второй блок счета младших упорядоченных единиц 7, и каждый i-й сумматор 5i содержит ]log2(N+3-i)[ (большее целое) разрядов, последний N-й сумматор 5N содержит два разряда, а выходы количества групп К содержат ]log2(N+1)[ (большее целое) разрядов. 2 ил., 1 табл.

Устройство для определения количества нулей и единиц по группам в двоичном числе содержит N разрядов входного двоичного числа D1, D2, …, DN, (N+1) групп выходных данных G1, G1, …, G(N+1), выходную группу К количества групп нулей и единиц, группу из (N-1) внутренних шин упорядоченных двоичных чисел S1, S2, …, S(N-1), (N-1) каскадов формирователя упорядоченных двоичных чисел 11, 12, …, 1N, которые объединены в пирамидальную структуру, причем каждый i-й каскад 1i (i=1, …, (N-1)) содержит группу из (N-i) элементов ИЛИ 21, 22, …, 2(N-i), группу из (N-i) элементов XOR 31, 32, …, 3(N-i), группу из (N+1-i) входов A1, А2, …, A(N+1-i), группу из (N-i) выходов Q1, Q2, …, Q(N-i) в следующий каскад и группу из (N+1-i) выходов разрядов соответствующей i-й внутренней шины Si из группы S1, S2, …, S(N-1), а также в устройство введены первая группа из (N-i) блоков счета младших упорядоченных единиц 41, 42, …, 4(N-i), группа из N сумматоров 51, 52, …, 5N, с инверсной группой входов второго слагаемого, элемент ИЛИ с одним инверсным входом 6 и второй блок счета младших упорядоченных единиц 7, причем каждый i-й сумматор 5i содержит ]log2(N+3-i)[ (большее целое) разрядов, а последний N-й сумматор 5N содержит два разряда, причем N разрядов входного двоичного числа D1, D2, …, DN соединены с одноименными входами A1, А2, …, AN первого каскада 11, в каждом i-м каскаде первые (N-i) входов A1, А2, …, A(N-i), кроме последнего входа A(N+1-i), также соединены со вторыми входами соответствующих одноименных элементов ИЛИ 21, 22, …, 2(N-i) и вторыми входами одноименных элементов XOR 31, 32, …, 3(N-i), а первые входы первых (N-i-1) элементов 21, 22, …, 2(N-i-1) из группы элементов ИЛИ соединены с выходами соответствующих последующих элементов 22, 23, …, 2(N-i) из группы элементов ИЛИ, первый вход последнего элемента 2(N-i) из группы элементов ИЛИ соединен с последним входом запроса A(N+1-i) i-го каскада, выходы (N-i) элементов ИЛИ 21, 22, …, 2(N-i) соединены также с первыми входами соответствующих одноименных элементов XOR 31, 32, …, 3(N-i), выходы которых являются группой (N-i) выходов Q1, Q2, …, Q(N-i) в следующий каскад каждого i-го каскада, а выходы всех (N-i) элементов ИЛИ 21, 22, …, 2(N-i) являются одноименными первыми младшими (N-i) разрядами соответствующей i-й внутренней шины Si из группы S1, S2, …, S(N-1), а последний вход A(N+1-i) i-го каскада является старшим (N+1-i)-м разрядом соответствующей i-й внутренней шины Si, причем в первых (N-2) каскадах, кроме последнего (N-1)-го каскада, (N-i) выходов в следующий (i+1)-й каскад Q1, Q2, …, Q(N-i) соединены с соответствующими (N-i) одноименными входами A1, А2, …, A(N-i) следующего (i+1)-го каскада, все разряды каждой i-й внутренней шины Si из группы S1, S2, …, S(N-1) соединены с входами соответствующего одноименного блока 4i из первой группы из (N-i) блоков счета младших упорядоченных единиц, а выходы каждого i-го блока 4i соединены с инверсной группой входов второго слагаемого i-го сумматора 5i и первой группой прямых входов первого слагаемого (i+1)-го сумматора 5(i+1) из группы из N сумматоров 51, 52, …, 5N, выходы которых являются соответствующими первыми N группами выходных данных G1, G2, …, GN, а последний одноразрядный выход G(N+1) соединен с выходом Q1 последнего (N-1) каскада 1(N-1), который также соединен со второй инверсной группой входов последнего N-го сумматора 5N и первым прямым входом элемента ИЛИ с одним инверсным входом 6, второй инверсный вход которого соединен со старшим N-м разрядом DN входного двоичного числа, на группу первых прямых входов первого сумматора 51 подано двоичное число «N», а на входы переносов CI всех N сумматоров 51, 52, …, 5N подано значение логической единицы, младшие первые разряды всех (N-1) внутренних шин упорядоченных двоичных чисел S1, S2, …, S(N-1) соединены с соответствующими входами второго блока счета младших упорядоченных единиц 7, а также соответствующий N-й вход которого соединен с выходом элемента ИЛИ с одним инверсным входом 6, а выходы второго блока счета младших упорядоченных единиц 7 являются выходной группой К количества групп нулей и единиц, причем количество групп К содержит ]log2(N+l)[ (большее целое) разрядов.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА СТАРШИХ ЕДИНИЦ (НУЛЕЙ) В ДВОИЧНОМ ЧИСЛЕ | 2016 |

|

RU2633110C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ПОРЯДКА ПРИ НОРМАЛИЗАЦИИ ЧИСЕЛ | 2017 |

|

RU2638724C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ | 2016 |

|

RU2638732C1 |

| Автомобиль-сани, движущиеся на полозьях посредством устанавливающихся по высоте колес с шинами | 1924 |

|

SU2017A1 |

| US 6499044 B1, 24.12.2002. | |||

Авторы

Даты

2018-11-16—Публикация

2017-12-21—Подача