ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также для обработки результатов физических экспериментов.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известно устройство для определения количества единиц в упорядоченном двоичном числе (RU №2522875, МПК Н03К 21/12, заявлено 24.05.2012, опубликовано 20.07.2014, Бюл. №20), содержащее буферы с тремя состояниями с прямым и инверсным входами разрешения, n разрядов входного двоичного числа, (k+1) разрядов выходного двоичного кода (k=[log2n] меньшее целое), причем буферы с тремя состояниями объединены в пирамидальную структуру, состоящую из (m-1) ступеней (m=]log2n[большее целое), и в выходной блок, содержащий k буферов с тремя состояниями с инверсным входом разрешения и k буферов с тремя состояниями с прямым входом разрешения, при этом каждая i-я ступень (i=1, …, (m-1)) содержит (2i-1) буферов с тремя состояниями с инверсным входом разрешения и 2i-1 буферов с тремя состояниями с прямым входом разрешения.

Недостатком данного устройства является определение количества единиц в упорядоченном двоичном числе, а не выявление диапазона единичных бит.

Известно устройство для упорядочения единиц (SU №1751746 А1, МПК G06F 7/38, 7/06, заявлено 26.11.1990, опубликовано 30.07.1992, Бюл. №28), содержащее по (n-1)-й группе элементов И и ИЛИ (где n - четное число, разрядность операнда, n=2К), две группы К-разрядных входов упорядоченных единиц и n-разрядный выход упорядоченных единиц.

Недостатком данного устройства является формирование на выходах упорядоченного кода, а не выявление диапазона единичных бит.

Известно устройство для определения количества единиц (нулей) в двоичном числе (RU №2446442, МПК G06F 7/50, Н03К 21/00, заявлено 11.04.2011, опубликовано 27.03.2012, Бюл. №9), содержащее блок управляемой инверсии, состоящий из n-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ» (n - количество разрядов входного числа), элементы ИЛИ и модули, состоящие из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, которые объединены в группы, состоящие из ярусов, и объединены в k-каскадов (k=]log2n[), так, что каждый i-й каскад содержит g(i)=n/2i групп (i=1, …, k), каждая группа i-го каскада разделена на j ярусов (j=1, …, i), при этом первый ярус каждой группы i-го каскада содержит i модулей, а каждый j-й ярус каждой группы i-го каскада (j=2, …, i,) содержит (i-j) модулей и элемент «ИЛИ».

Недостатком данного устройства является определение только общего количества единиц (нулей) в двоичном числе, а не выявление диапазона единичных бит.

Известен указатель старшей единицы (Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ-Петербург, 2000. - 528 с., рис. 2.8 с. 50-54), содержащий группу элементов И и группу элементов запрета И с одним инверсным входом. В данном устройстве реализована цепочечная схема передачи сигнала опроса путем последовательного опроса, начиная со старшего разряда, и прекращения дальнейшего опроса при выявлении первой же единицы.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, указатель старшей единицы (Схемотехника ЭВМ. Сборник задач: учебное пособие. М.: НИЯУ МИФИ, 2012. - 240 с, рис. 53, с. 55-56), содержащий группу элементов ИЛИ объединенных в цепочку и группу элементов запрета И с одним инверсным входом.

Недостатком данных устройств является выявление только одного старшего единичного бита.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является выявление номера левого (старшего) единичного бита и номера правого (младшего) единичного бита во входных данных.

При обработке результатов физических экспериментов устройство предназначено для выявления диапазона событий.

Техническим результатом изобретения является расширение функциональных возможностей в части возможности выявления границ диапазона единичных бит.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для детектирования границ диапазона единичных бит, содержит N разрядную входную шину D, выходную шину QR номера младшего разряда и выходную шину QL номера старшего разряда содержащие по М разрядов, где M=]log2 (N+1)[(большее целое), группу из (N-1) элементов ИЛИ 11, 12, …, 1(N-1), группу из (N-1) элементов ИЛИ-НЕ 21, 22, …, 2(N-1), первый 31 и второй 32 блоки счета младших упорядоченных единиц, а также внутреннюю шину SR сдвига вправо и внутреннюю шину SL сдвига влево, которые содержат по N разрядов,

причем первые (N-1) разрядов D1, D2, …, D(N-1) входной шины D, начиная с первого до (N-1)-го разрядов, соединены со вторыми входами соответствующих (N-1) элементов ИЛИ, начиная с первого до (N-1)-го элементов 11, 12, …, 1(N-1), а также соединены с первыми прямыми входами соответствующих (N-1) элементов ИЛИ-НЕ, начиная с первого до (N-1)-го элементов 21, 22, …, 2(N-1),

при этом первые входы первых (N-2) элементов ИЛИ, начиная с первого до (N-2)-го элементов 11, 12, …, 1(N-2), соединены с выходами соответствующих последующих (N-2) элементов ИЛИ, начиная со второго до (N-1)-го элементов 12, 13, …, 1(N-1), а первый вход (N-1)-го элемента ИЛИ 1(N-1) соединен с N-м разрядом DN входной шины D,

кроме того выходы всех (N-1) элементов ИЛИ 11, 12, …, 1(N-1) являются соответствующими одноименными (N-1) разрядами внутренней шины SR сдвига вправо, у которой старший N-й разряд соединен с N-м разрядом DN входной шины D, а все разряды шины SR сдвига вправо подключены к входам первого 31 блока счета младших упорядоченных единиц,

причем третьи инверсные входы (N-2) элементов ИЛИ-НЕ, начиная со второго до (N-1)-го элементов 22, 23, …, 2(N-1), соединены с инверсными выходами соответствующих предыдущих (N-2) элементов ИЛИ-НЕ, начиная с первого до (N-2)-го элементов 21, 22, …, 2(N-2), кроме того вторые инверсные входы всех (N-1)-го элементов ИЛИ-НЕ 21, 22, …, 2(N-1) соединены между собой, а также подключены к выходу первого элемента ИЛИ 11,

кроме того инверсные выходы всех (N-1) элементов ИЛИ-НЕ 21, 22, …, 2(N-1) являются соответствующими (N-1) разрядами внутренней шины SL сдвига влево, начиная со второго до N-го разряда, а младший первый разряд шины SL сдвига влево соединен с выходом первого элемента ИЛИ 11, а все разряды шины SL сдвига влево подключены к входам второго 32 блока счета младших упорядоченных единиц,

причем выходы первого 31 и второго 32 блоков счета младших упорядоченных единиц являются соответствующими разрядами соответственно выходной шины QL номера старшего разряда и выходной шины QR номера младшего разряда.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

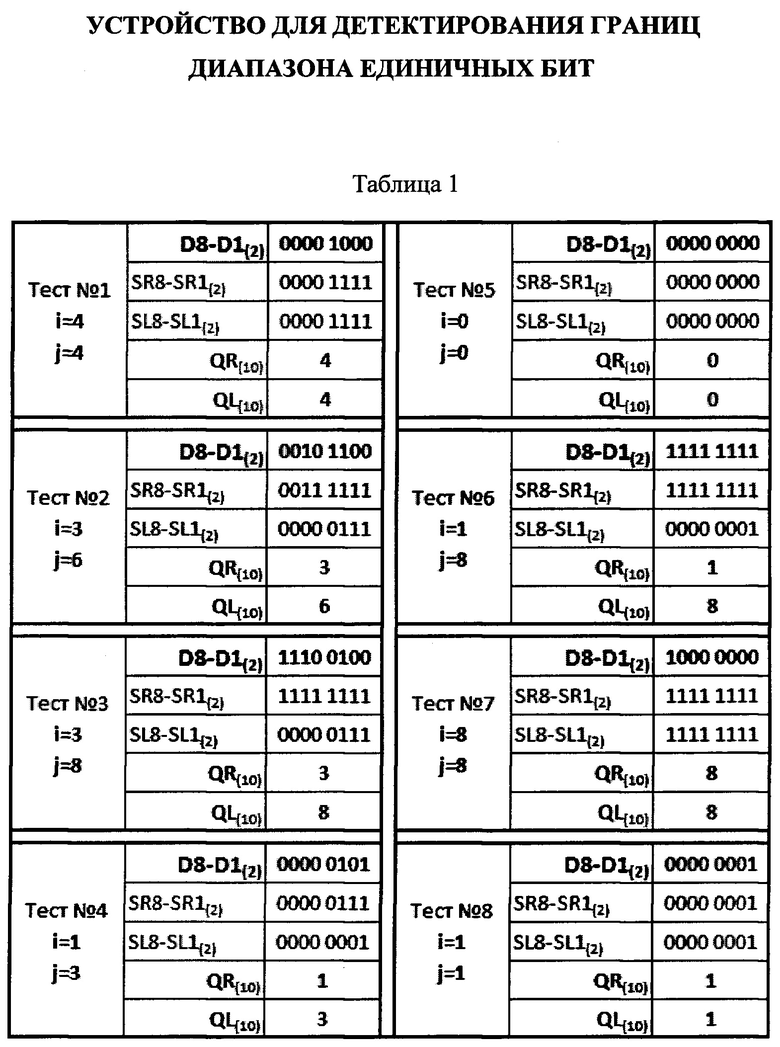

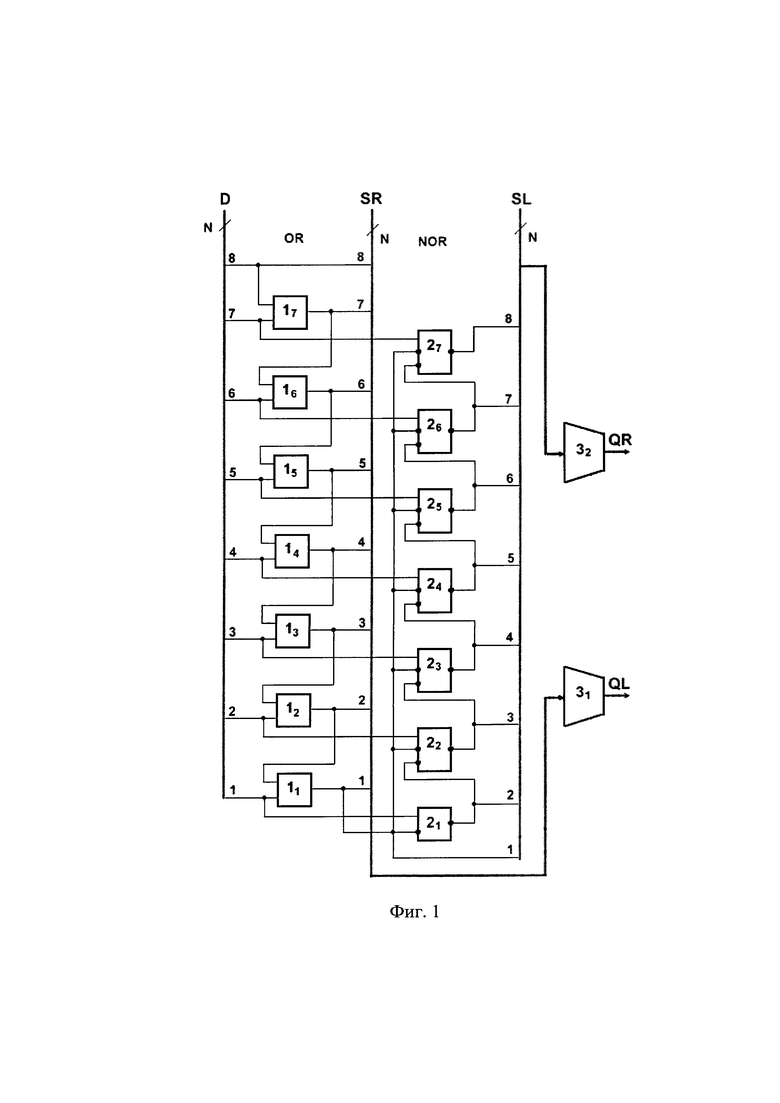

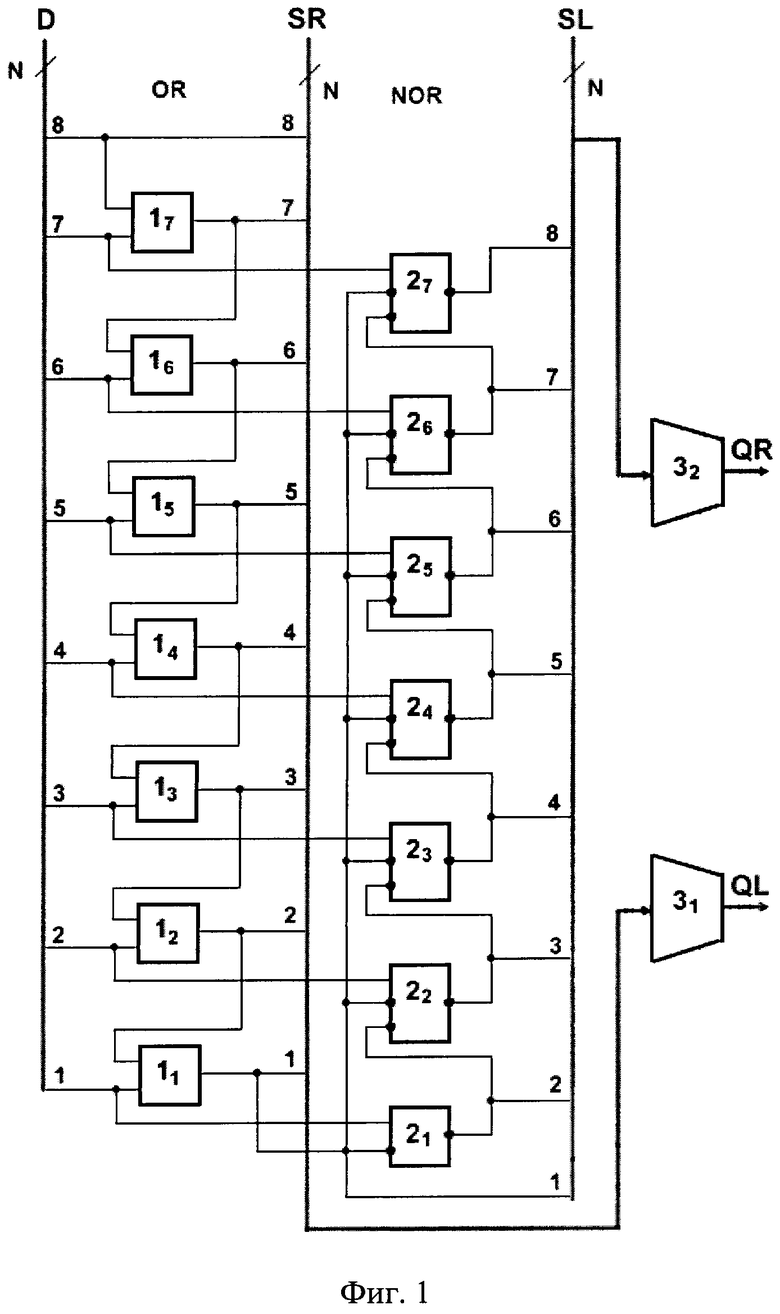

На фиг. 1 представлена функциональная схема предлагаемого устройства для детектирования границ диапазона единичных бит при количестве разрядов N=8 входной шины D - D1, D2, …, D8(N). В таблице 1 приведены тестовые примеры формирования границ диапазона при количестве разрядов N=8.

На фиг. 1 и в тексте введены следующие обозначения:

D - N разрядная входная шина;

D1, D2, …, D8 - двоичные разряды входной шины;

QR - М разрядная выходная шина номера младшего разряда, где M=]log2 (N+1)[(большее целое);

QL - М разрядная выходная шина номера старшего разряда;

SR - N разрядная внутренняя шина сдвига вправо в сторону младших разрядов;

SL - N разрядная внутренняя шина сдвига влево в сторону старших разрядов;

i - правый (младший) разряд, имеющий единичное значение, где 1≤i≤N;

j - левый (старший) разряд, имеющий единичное значение, где i≤j;

11, 12, …, 1(N-1) - группа из (N-1) элементов ИЛИ (OR);

21, 22, …, 2(N-1) - группа из (N-1) элементов ИЛИ-НЕ (NOR);

31, 32 - первый и второй блоки счета младших упорядоченных единиц.

Предлагаемое устройство для детектирования границ диапазона единичных бит, содержит N разрядную входную шину D, выходную шину QR номера младшего разряда и выходную шину QL номера старшего разряда содержащие по М разрядов, где M=]log2 (N+1)[(большее целое), группу из (N-1) элементов ИЛИ 11, 12, …, 1(N-1), группу из (N-1) элементов ИЛИ-НЕ 21, 22, …, 2(N-1), первый 31 и второй 32 блоки счета младших упорядоченных единиц, а также внутреннюю шину SR сдвига вправо и внутреннюю шину SL сдвига влево, которые содержат по N разрядов.

Первая группа элементов ИЛИ 11, 12, …, 1(N-1) предназначена для формирования упорядоченной группы единиц (подряд идущих) в младших разрядах, начиная с первого разряда до j-го левого (старшего) единичного разряда. Вторая группа элементов ИЛИ-НЕ 21, 22, …, 2(N-1) предназначена для формирования упорядоченной группы единиц в младших разрядах, начиная первого разряда до (i-1)-го разряда (где i-й правый (младший) единичный разряд). В первом 31 и втором 32 блоках счета Подсчет младших упорядоченных единиц в первом 31 и втором 32 блоках счета осуществляется с соответственно с шины SR сдвига вправо и с шины SL сдвига влево.

Причем первые (N-1) разрядов D1, D2, …, D(N-1) входной шины D, начиная с первого до (N-1)-го разрядов, соединены со вторыми входами соответствующих (N-1) элементов ИЛИ, начиная с первого до (N-1)-го элементов 11, 12, …, 1(N-1), а также соединены с первыми прямыми входами соответствующих (N-1) элементов ИЛИ-НЕ, начиная с первого до (N-1)-го элементов 21, 22, …, 2(N-1).

При этом первые входы первых (N-2) элементов ИЛИ, начиная с первого до (N-2)-го элементов 11, 12, …, 1(N-2), соединены с выходами соответствующих последующих (N-2) элементов ИЛИ, начиная со второго до (N-1)-го элементов 12, 13, …, 1(N-1). Кроме того первый вход (N-1)-го элемента ИЛИ 1(N-1) соединен с N-м разрядом DN входной шины D.

Кроме того выходы всех (N-1) элементов ИЛИ 11, 12, …, 1(N-1) являются соответствующими одноименными (N-1) разрядами внутренней шины SR сдвига вправо. Старший N-й разряд внутренней шины SR сдвига вправо соединен с N-м разрядом DN входной шины D. Все разряды шины SR сдвига вправо подключены к входам первого 31 блока счета младших упорядоченных единиц.

Причем третьи инверсные входы (N-2) элементов ИЛИ-НЕ, начиная со второго до (N-1)-го элементов 22, 23, …, 2(N-1), соединены с инверсными выходами соответствующих предыдущих (N-2) элементов ИЛИ-НЕ, начиная с первого до (N-2)-го элементов 21, 22, …, 2(N-2). Кроме того вторые инверсные входы всех (N-1)-го элементов ИЛИ-НЕ 21, 22, …, 2(N-1) соединены между собой, а также подключены к выходу первого элемента ИЛИ 11.

Кроме того инверсные выходы всех (N-1) элементов ИЛИ-НЕ 21, 22, …, 2(N-1) являются соответствующими (N-1) разрядами внутренней шины SL сдвига влево, начиная со второго до N-го разряда. Младший первый разряд шины SL сдвига влево соединен с выходом первого элемента ИЛИ 11. Все разряды шины SL сдвига влево подключены к входам второго 32 блока счета младших упорядоченных единиц.

Причем выходы первого 31 и второго 32 блоков счета младших упорядоченных единиц являются соответствующими разрядами соответственно выходной шины QL номера старшего разряда и выходной шины QR номера младшего разряда.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем.

Предлагаемое устройство позволяет детектировать правый (младший) i разряд (где 1≤i≤N) и левый (старший) j разряд (где i≤j) входной шины D, которые имеют единичное значение, и сформировать на выходах устройства номера младшего QR и старшего QL единичных разрядов. При отсутствии единичных значений в разрядах входной шины D на выходах номеров QR и QL границ диапазона устанавливаются нулевые значения.

На входы устройства одновременно поступают N двоичных разрядов входной шины D-D1, D2, …, DN.

При выявлении единичных значений в j-м и i-м разрядах, в группе элементов ИЛИ 11, 12, …, 1(N-1) единичные значения последовательно передаются в сторону младших разрядов по цепочке элементов ИЛИ, начиная от левого (старшего) единичного j-го разряда до первого разряда, и единичные значения устанавливаются на выходах элементов ИЛИ 11, …, 1j, которые далее поступают на внутреннюю шину SR сдвига вправо с первого разряда до j-го разряда. Одновременно при выявлении единичного значения в i-м разряде в группе элементов ИЛИ-НЕ 21, 22, …, 2(N-1) нулевые значения в разрядах меньше выявленного правого (младшего) единичного i-го разряда преобразуются в единичные значения на выходах в группе элементов ИЛИ-НЕ, начиная с первого элемента до (i-1)-го элемента ИЛИ-НЕ 21, …, 2i-1 и единичные значения устанавливаются на выходах элементов ИЛИ-НЕ 2i, …, 2(N-1). Далее значения с выходов группы элементов ИЛИ-НЕ 21, 22, …, 2(N-1) поступают на внутреннюю шину SL сдвига влево. Кроме того единичное значение i-го разряда на элементе ИЛИ-НЕ 2i преобразуется в нулевое значение, которое далее последовательно передается в сторону старших разрядов по цепочке элементов ИЛИ-НЕ, начиная от правого (младшего) единичного i-го разряда до последнего старшего (N-1) разряда. Также на первый разряд шины SL сдвига влево поступает значение с выхода первого элемента ИЛИ 11, которое принимает единичное значение при наличии хотя бы одного единичного бита на входной шине D.

Таким образом, на шине SR сдвига вправо формируются единичные значения с первого разряда до j-го разряда, сумма которых равна j, что соответствует номеру левого (старшего) единичного бита. Одновременно на шине SL сдвига влево также формируются единичные значения с первого разряда до i-го разряда, сумма которых равна i, что соответствует номеру правого (младшего) единичного бита во входных данных.

Далее значения с выходов внутренней шины SR сдвига вправо поступают на входы первого блока 31 счета младших упорядоченных единиц, а с выходов внутренней шины SL сдвига влево поступают на входы второго блока 32 счета младших упорядоченных единиц, на которых соответственно формируются номера j-го и i-го разрядов, которые далее передаются на выходные шины QL и QR.

При выявлении только одного единичного значения в i-м разряде (где 1≤i≤N, при этом j=i) входной шины D на выходах элементов ИЛИ, начиная с первого до i-го элементов, группы элементов ИЛИ 11, …, 1i устанавливаются единичные значения, которые поступают на внутреннюю шину SR сдвига вправо. Одновременно на выходах элементов ИЛИ-НЕ, начиная с первого до (i-1)-го элементов, группы элементов ИЛИ-НЕ 21, …, 2(i-1) также устанавливаются единичные значения, которые поступают на внутреннюю шину SL сдвига влево, на первый разряд которой передается единичное значение с первого элемента ИЛИ 11. Далее значения с выходов внутренней шины SR сдвига вправо и выходов внутренней шины SL сдвига влево поступают соответственно на первый 31 и второй 32 блоки счета младших упорядоченных единиц.

Далее в первом 31 и втором 32 блоках счета младших упорядоченных единиц формируется номер i-го разряда (при этом j=i) и передается на выходные шины QL и QR.

При отсутствии единичных значений на входной шине D нулевые значения устанавливаются во всех разрядах шины SR сдвига вправо. При этом нулевое значение с первого элемента ИЛИ 11, передается на инверсные входы всех элементов ИЛИ-НЕ 21, 22, …, 2(N-1), на инверсных выходах которых также устанавливаются нулевые значения и далее нулевые значения устанавливаются во всех разрядах шины SL сдвига влево.

Таким образом, в предлагаемом устройстве на выходных шинах номеров бит устанавливаются - номер левого (старшего) j-го разряда на шине QL и номер правого (младшего) i-го разряда на шине QR.

Предлагаемое устройство работает следующим образом.

На входную шину шины D одновременно поступают N разрядов - D1, D2, …, DN. Значения с входной шины D поступают на соответствующие входы группы элементов ИЛИ 11, 12, …, 1(N-1) и группы элементов ИЛИ-НЕ 21, 22, …, 2(N-1).

При выявлении единичных значений в правом (младшем) i-м разряде (где 1≤i≤N) и в левом (старшем) j-м разряде, единичные значение последовательно по цепочке передаются на выходы элементов ИЛИ в сторону младших разрядов, начиная с j-го до первого элементов ИЛИ 1j, …, 11, а также последовательно по цепочке передаются на выходы элементов ИЛИ-НЕ, начиная с первого до (i-1)-го элементов ИЛИ 21, …, 2(i-1).

В таблице 1 приведены тестовые примеры формирования границ диапазона при количестве разрядов N=8. В таблице 1 в скобках указано представление значений в двоичном коде (2) или десятичном коде (10).

В тесте №1 единичное значение поступает только в одном четвертом разряде D4 входной шины D, при этом i=4 и j=4. Поэтому единичные значения последовательно устанавливаются на выходах группы элементов ИЛИ 11, …, 14 и группы элементов ИЛИ-НЕ 21, …, 23, которые далее поступают на разряды шин соответственно SR сдвига вправо и SL сдвига влево. Кроме того на первый разряд шины SL сдвига влево передается единичное значение с выхода первого элемента ИЛИ 11. При этом на шинах SR сдвига вправо и SL сдвига влево в младших разрядах будет установлено по четыре единичных разряда, подсчет которых осуществляется соответственно в первом 31 и втором 32 блоках счета младших упорядоченных единиц и формируются коды номеров границ единичных бит - соответственно j=4 и i=4.

В тесте №2 единичные значения поступают в третьем D3, четвертом D4 и шестом D6 разрядах входной шины D. При этом детектируются единичные значения в правом (младшем) i=3 и левом (старшем) j=6 разрядах. Поэтому единичные значения последовательно устанавливаются на соответствующих выходах группы элементов ИЛИ 11, …, 16 и группы элементов ИЛИ-НЕ 22, …, 22. Далее единичные значения устанавливаются на шине SR сдвига вправо в шести младших разрядах и на шине SL сдвига влево в трех младших разрядах, подсчет которых осуществляется соответственно в первом 31 и втором 32 блоках счета младших упорядоченных единиц и формируются коды номеров границ единичных бит - соответственно j=6 и i=3.

В тестовых примерах №3 - №8 приведены особые случаи, когда по входной шине D поступают единичные значения по восьмому разряду D8 (тест №3) или первому разряду D1 (тест №4) одновременно с единичными значениями в других разрядах входной шины D, или поступают только нулевые значения (тест №5), или единичные значения поступают во всех разрядах (тест №6), или единичные значения поступают только по восьмому разряду D8 (тест №7) или только по первому разряду D1 (тест №8).

В тесте №3 единичные значения поступают в третьем D3, шестом D6, седьмом D7 и восьмом D8 разрядах входной шины D, т.е. единичное значение детектируется и в старшем N=8 разряде. При этом детектируются единичные значения в правом (младшем) i=3 и левом (старшем) j=8 разрядах. Поэтому единичные значения последовательно устанавливаются на выходах всех элементов ИЛИ 11, …, 17 и элементов ИЛИ-НЕ 22, …, 23, которые далее передаются на шину SR сдвига вправо в восьми разрядах и на шину SL сдвига влево в трех младших разрядах (при единичном значении на первом элементе ИЛИ 11), подсчет которых осуществляется соответственно в первом 31 и втором 32 блоках счета младших упорядоченных единиц и формируются коды номеров границ единичных бит - соответственно j=8 и i=3.

В тесте №4 единичные значения поступают в первом D1 и третьем D3 разрядах входной шины D, т.е. т.е. единичное значение детектируется и в младшем первом разряде. При этом детектируются единичные значения в правом (младшем) i=1 и левом (старшем) j=3 разрядах. Поэтому единичные значения последовательно устанавливаются на выходах элементов ИЛИ 13, 12, 11 и нулевые значения на всех элементах ИЛИ-НЕ 21, …, 27, и далее единичные значения передаются на шину SR сдвига вправо в трех разрядах, а на шине SL сдвига влево единичное значение устанавливается в одном первом младшем разряде с выхода первого элемента ИЛИ 11. Подсчет единичных значений осуществляется соответственно в первом 31 и втором 32 блоках счета младших упорядоченных единиц и формируются коды номеров границ единичных бит - соответственно j=3 и i=1.

В тесте №5 единичные значения отсутствуют в разрядах входной шины D, при этом i=0 и j=0. Поэтому нулевые значения устанавливаются на выходах всех ИЛИ 11, …, 17 и всех элементов ИЛИ-НЕ 21, …, 27. Далее нулевые значения устанавливаются во всех разрядах шины SR сдвига вправо и шины SL сдвига влево, при этом на шине SL сдвига влево за счет двойной инверсии нулевого значения с выхода первого элемента ИЛИ 11. Поэтому в первом 31 и втором 32 блоках счета младших упорядоченных единиц формируются нулевые коды - соответственно j=0 и i=0.

В тесте №6 единичные значения поступают во всех разрядах входной шины D. При этом детектируются единичные значения в правом (младшем) i=1 и левом (старшем) j=8 разрядах. Поэтому единичные значения устанавливаются на выходах всех элементов ИЛИ 11, …, 17 и нулевые значения на всех элементах ИЛИ-НЕ 21, …, 27. Далее единичные значения устанавливаются во всех разрядах шины SR сдвига вправо, а на шине SL сдвига влево единичное значение устанавливается только в первом разряде с выхода первого элемента ИЛИ 11. Поэтому в первом 31 и втором 32 блоках счета младших упорядоченных единиц формируются соответствующие коды - j=8 и i=1.

В тесте №7 единичное значение поступает только в одном восьмом разряде D8 входной шины D, при этом i=8 и j=8. Поэтому единичные значения последовательно устанавливаются на выходах всех элементов ИЛИ 11, …, 17 и единичные значения на выходах всех элементов ИЛИ-НЕ 21, …, 27, у которых с входной шины D на инверсные входы поступают нулевые значения, а также на первый младший разряд шины SL сдвига влево поступает единичное значение с выхода первого элемента ИЛИ 11. Поэтому во всех разрядах шины SR сдвига вправо и шины SL сдвига влево будут установлены единичные значения, по которым в первом 31 и втором 32 блоках счета младших упорядоченных единиц формируются соответствующие коды - j=8 и i=8.

В тесте №8 единичное значение поступает только в первом младшем разряде D1 входной шины D, при этом i=1 и j=1. Поэтому нулевые значения последовательно устанавливаются на выходах всех элементов ИЛИ-НЕ 21, …, 27 и единичное значения на выходе только одного первого элемента ИЛИ 11. Поэтому на шины SR сдвига вправо и шины SL сдвига влево будут установлены единичные значения только в младших первых разрядах, по которым в первом 31 и втором 32 блоках счета младших упорядоченных единиц формируются соответствующие коды - j=1 и i=1.

Значения с выходов первого 31 и втором 32 блоков счета младших упорядоченных единиц передаются на соответствующие выходные шины устройства, на которых устанавливаются - номер левого (старшего) j-го разряда на шине QL и номер правого (младшего) i-го разряда на шине QR.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу и соответствует заявляемому техническому результату - детектирование границ диапазона единичных бит.

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также для обработки результатов физических экспериментов. Технический результат изобретения заключается в расширении функциональных возможностей в части возможности выявления границ диапазона единичных бит. Технический результат достигается за счет того, что устройство для детектирования границ диапазона единичных бит содержит N-разрядную входную шину D, выходную шину QR номера младшего разряда и выходную шину QL номера старшего разряда, содержащие по М разрядов, где M=]log2 (N+1)[(большее целое), группу из (N-1) элементов ИЛИ 11, 12, …, 1(N-1), группу из (N-1) элементов ИЛИ-НЕ 21, 22, …, 2(N-1), первый 31 и второй 32 блоки счета младших упорядоченных единиц, а также внутреннюю шину SR сдвига вправо и внутреннюю шину SL сдвига влево, которые содержат по N разрядов. 1 ил., 1 табл.

Устройство для детектирования границ диапазона единичных бит содержит N-разрядную входную шину D, выходную шину QR номера младшего разряда и выходную шину QL номера старшего разряда, содержащие по М разрядов, где M=]log2 (N+1)[(большее целое), группу из (N-1) элементов ИЛИ 11, 12, …, 1(N-1), группу из (N-1) элементов ИЛИ-НЕ 21, 22, …, 2(N-1), первый 31 и второй 32 блоки счета младших упорядоченных единиц, а также внутреннюю шину SR сдвига вправо и внутреннюю шину SL сдвига влево, которые содержат по N разрядов,

причем первые (N-1) разрядов D1, D2, …, D(N-1) входной шины D, начиная с первого до (N-1)-го разрядов, соединены со вторыми входами соответствующих (N-1) элементов ИЛИ, начиная с первого до (N-1)-го элементов 11, 12, …, 1(N-1), а также соединены с первыми прямыми входами соответствующих (N-1) элементов ИЛИ-НЕ, начиная с первого до (N-1)-го элементов 21, 22, …, 2(N-1),

при этом первые входы первых (N-2) элементов ИЛИ, начиная с первого до (N-2)-го элементов 11, 12, …, 1(N-2), соединены с выходами соответствующих последующих (N-2) элементов ИЛИ, начиная со второго до (N-1)-го элементов 12, 13, …, 1(N-1), а первый вход (N-1)-го элемента ИЛИ 1(N-1) соединен с N-м разрядом DN входной шины D,

кроме того, выходы всех (N-1) элементов ИЛИ 11, 12, …, 1(N-1) являются соответствующими одноименными (N-1) разрядами внутренней шины SR сдвига вправо, у которой старший N-й разряд соединен с N-м разрядом DN входной шины D, а все разряды шины SR сдвига вправо подключены к входам первого 31 блока счета младших упорядоченных единиц,

причем третьи инверсные входы (N-2) элементов ИЛИ-НЕ, начиная со второго до (N-1)-го элементов 22, 23, …, 2(N-1), соединены с инверсными выходами соответствующих предыдущих (N-2) элементов ИЛИ-НЕ, начиная с первого до (N-2)-го элементов 21, 22, …, 2(N-2), кроме того, вторые инверсные входы всех (N-1)-го элементов ИЛИ-НЕ 21, 22, …, 2(N-1) соединены между собой, а также подключены к выходу первого элемента ИЛИ 11,

кроме того, инверсные выходы всех (N-1) элементов ИЛИ-НЕ 21, 22, …, 2(N-1) являются соответствующими (N-1) разрядами внутренней шины SL сдвига влево, начиная со второго до N-го разряда, а младший первый разряд шины SL сдвига влево соединен с выходом первого элемента ИЛИ 11, а все разряды шины SL сдвига влево подключены к входам второго 32 блока счета младших упорядоченных единиц,

причем выходы первого 31 и второго 32 блоков счета младших упорядоченных единиц являются соответствующими разрядами соответственно выходной шины QL номера старшего разряда и выходной шины QR номера младшего разряда.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ В УПОРЯДОЧЕННОМ ДВОИЧНОМ ЧИСЛЕ | 2012 |

|

RU2522875C2 |

| УСТРОЙСТВО ПИРАМИДАЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2019 |

|

RU2703335C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ (НУЛЕЙ) В ДВОИЧНОМ ЧИСЛЕ | 2011 |

|

RU2446442C1 |

| US 6938061 B1, 30.08.2005 | |||

| Токарный резец | 1924 |

|

SU2016A1 |

Авторы

Даты

2020-03-27—Публикация

2019-12-19—Подача