Изобретение относится к вычислительной технике и может быть использовано при получении информации для принятия оптимальных решений при эксплуатации сложных технических систем (СТС) с целью обеспечения заданных требований к их надежности.

Известно устройство для прогнозирования надежности, содержащее коррелятор, анализатор случайного процесса, вычислительный блок, блок возведения в степень, блок памяти, блок дифференцирования, сумматор, регистрирующий блок, блок транспонирования матриц и дополнительный вычислительный блок (авт. свид. СССР №746349, кл. G01R 31/28, 1980).

Недостатком этого устройства являются большие ошибки в определении синтезируемых свойств СТС. Задача синтеза требований к надежности СТС, является некорректной и решение ее методом квадратных корней или методом Гаусса приводит к получению результата, имеющего большие погрешности.

Наиболее близким аналогом, прототипом, является устройство ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ ДЛЯ ОБЕСПЕЧЕНИЯ УСТОЙЧИВОЙ РАБОТЫ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ, содержащее коррелятор, анализатор случайного процесса, вычислительный блок, блок возведения в степень, блок транспонирования матриц, элементы ИЛИ, блок умножения, блок управления, элементы И, блок формирования матриц, блок памяти, блок обращения матриц, сумматоры, блок сравнения, регистратор, группы входных регистров, входной регистр, коммутатор, группу блоков вычитания, группы квадраторов, группы блоков умножения, группу элементов ИЛИ, накопительные сумматоры, блоки извлечения квадратного корня, элементы задержки (ЭЗ), блок деления, группы регистров, группу коммутаторов, группы блоков индикации, блок оценки минимального значения, группу блоков сравнения, группу ЭЗ, генератор тактовых импульсов и распределитель импульсов (РИ). (Патент на изобретение №2475828 от 20.02.2013).

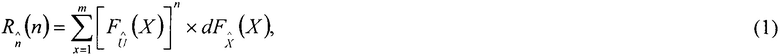

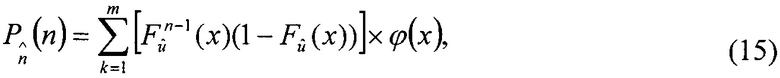

Устройство аппаратурно реализует выражение

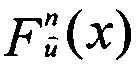

где  - функция надежности или вероятность того, что за время t=n×Δτ ни разу внешнее по отношению к эксплуатируемому устройству воздействие не превышает допустимого;

- функция надежности или вероятность того, что за время t=n×Δτ ни разу внешнее по отношению к эксплуатируемому устройству воздействие не превышает допустимого;

- функция распределения сопротивляемости, обоснования и исчерпывающая характеристика допустимого предела величин внешнего воздействия, приводящего устройство к отказу;

- функция распределения сопротивляемости, обоснования и исчерпывающая характеристика допустимого предела величин внешнего воздействия, приводящего устройство к отказу;

- наибольшее случайное воздействие на интервале времени, равном периоду корреляции;

- наибольшее случайное воздействие на интервале времени, равном периоду корреляции;

- функция распределения наибольших значений внешнего воздействия;

- функция распределения наибольших значений внешнего воздействия;

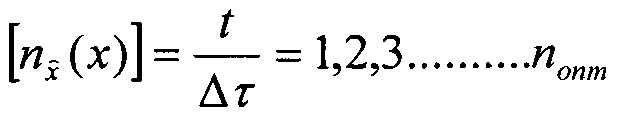

n - число периодов корреляции внешнего воздействия n=t/Δτ;

Δτ - период корреляции исследуемого сигнала;

- условная функция распределения внешнего воздействия относительно гипотезы о том, что предельное (допустимое) значение воздействия принадлежит элементарному отрезку

- условная функция распределения внешнего воздействия относительно гипотезы о том, что предельное (допустимое) значение воздействия принадлежит элементарному отрезку  ;

;

- вероятность элементарной гипотезы.

- вероятность элементарной гипотезы.

При синтезе свойств СТС устройство определяет из выражения (1) дискретные значения  плотности функции распределения сопротивляемости. Исходной информацией в этом случае для работы устройства являются заданные значения функции надежности

плотности функции распределения сопротивляемости. Исходной информацией в этом случае для работы устройства являются заданные значения функции надежности  и функции

и функции  распределения наибольших значений внешнего воздействия

распределения наибольших значений внешнего воздействия  .

.

При этом устройство реализует алгоритм, вытекающий из следующих преобразований.

В уравнении

представляющем компактную матричную форму записи уравнения (1), вектор  характеризует требования к синтезируемой СТС. Эффективным методом решения системы линейных алгебраических уравнений вида (2) является метод Зейделя.

характеризует требования к синтезируемой СТС. Эффективным методом решения системы линейных алгебраических уравнений вида (2) является метод Зейделя.

Для обеспечения положительной определенности матрицы задачи умножим левую и правую часть уравнения (2) на матрицу ВT. В результате вместо уравнения (2) решается уравнение

где - ВT транспортирования матрица  ;

;

- вектор правой части уравнения (2) - функция надежности.

- вектор правой части уравнения (2) - функция надежности.

Введем обозначения

Перепишем уравнения (3) с учетом введенных обозначений

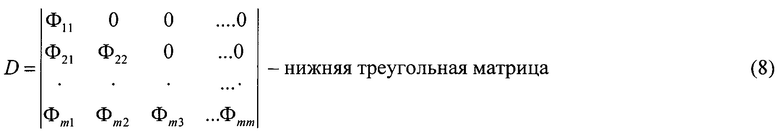

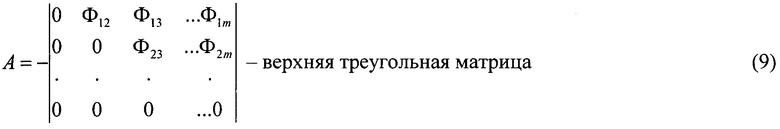

В векторно-матричной форме алгоритм решения системы (6) методом Зейделя (n+1)-ом шаге итерации имеет следующий вид:

где ϕn+1 - искомый вектор приближения на текущем (n+1)-ом шаге итерации;

ϕn - то же, на предыдущем шаге итерации.

которые получаются из исходной матрицы Ф.

Устойчивость решения осуществляется следующим образом. В первое слагаемое правой части формулы (7) в качестве сомножителя вводятся значения коэффициента стабильности αк:

где m - k-oe из количества последовательно подставляемых в формулу (10) значений коэффициента αk

αk - коэффициент регуляризации (стабильности) (его значения задаются на основе теоретических исследований).

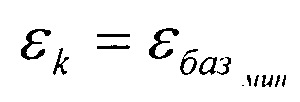

Оптимальность полученного решения оценивается по критерию минимума эвклидовой нормы отклонения площади под кривой  , от эталонного значения

, от эталонного значения  , которое является плотностью функции распределения проектного значения сопротивляемости. Величина этого отклонения εk определяется по следующей формуле:

, которое является плотностью функции распределения проектного значения сопротивляемости. Величина этого отклонения εk определяется по следующей формуле:

где  эталонное значение, которое является плотностью функции распределения проектного значения сопротивляемости.

эталонное значение, которое является плотностью функции распределения проектного значения сопротивляемости.

; k=1, …, m;

; k=1, …, m;

- полученные в результате решения (10) значения кривой плотности функции распределения сопротивляемости;

- полученные в результате решения (10) значения кривой плотности функции распределения сопротивляемости;

Δх - длина интервала разбиения аргумента х этой функции;

Р - число интервалов этого разбиения.

Недостатком этого устройства является значительное увеличение количества итераций при определении плотности функции распределения сопротивляемости  - полученные в результате решения уравнения (10), что в целом снижает оперативность вычислительного процесса.

- полученные в результате решения уравнения (10), что в целом снижает оперативность вычислительного процесса.

Техническим результатом заявленного изобретения является снижение количества итераций  при решении задачи оптимального управления надежностью методом ускоренного спуска, а также повышение оперативности и обеспечения стабильности (устойчивости) вычислений при решения данной задачи за счет введения параметров регуляризации. Все это, в конечном итоге, приводит к повышению точности оценки искомой плотности функции распределения различных параметров СТС и устойчивой их работы благодаря возможности корректировки этих параметров.

при решении задачи оптимального управления надежностью методом ускоренного спуска, а также повышение оперативности и обеспечения стабильности (устойчивости) вычислений при решения данной задачи за счет введения параметров регуляризации. Все это, в конечном итоге, приводит к повышению точности оценки искомой плотности функции распределения различных параметров СТС и устойчивой их работы благодаря возможности корректировки этих параметров.

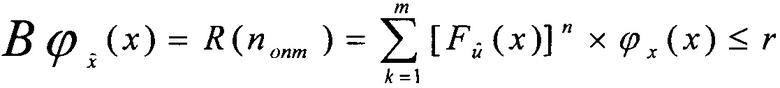

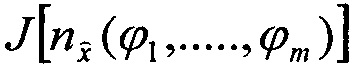

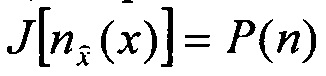

Для получения оптимального количества итераций  и оптимального значения проектного значения плотности функции распределения сопротивляемости

и оптимального значения проектного значения плотности функции распределения сопротивляемости  по формуле (10) нужно ввести целевой функционал

по формуле (10) нужно ввести целевой функционал  . Данный функционал вводится из уравнений связи между характеристиками комплекса испытаний и показателями надежности в виде

. Данный функционал вводится из уравнений связи между характеристиками комплекса испытаний и показателями надежности в виде

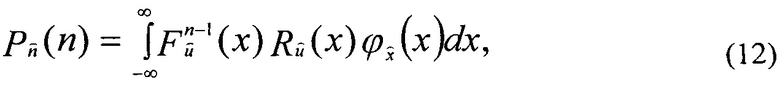

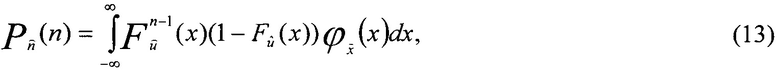

где  - функция надежности в виде:

- функция надежности в виде:

Запишем уравнение (12) в следующей форме

Уравнение (13) кратко записывается в операторном виде

где L - интегральный оператор в матричном виде.

Уравнение (14) теперь можно записать по аналогии с выражением (1) и (2) в виде

Соответственно уравнение (1) запишется в виде

где  - известная функция распределения наибольшего значения нагрузки после n испытаний.

- известная функция распределения наибольшего значения нагрузки после n испытаний.

Уравнение (16) записывается в операторном виде

где В - интегральный оператор в матричном виде.

Таким образом обобщенная устойчивая математическая модель прямой задачи оптимизации управления надежностью записывается в следующем виде

при следующих ограничениях:

t0≤t≤T;

Δτ>0

x(t0)=x0

x(t1)=x1

где x(t)={х1, …, хm} и n(x1, х2, …, xm)={n1, …, nn} - соответственно вектор-функции состояния объекта и управления с целевым функционалом  и управляющими функциями n(х1, …, хm),

и управляющими функциями n(х1, …, хm),

B и L соответственно интегральные операторы для уравнений целевого функционала и уравнения ограничений для заданной надежности,

- целевой функционал вероятности отказа в n(х1, …, хm)-й итерации,

- целевой функционал вероятности отказа в n(х1, …, хm)-й итерации,

Δτ - период корреляции стационарного случайного процесса,

n - число итераций выражения (10) или число испытаний СТС,

m - количество элементов в строке матричного уравнения,

r - заданная надежность СТС в матричном виде,

- известная функция распределения наибольшего значения нагрузки после n испытаний,

- известная функция распределения наибольшего значения нагрузки после n испытаний,

- случайная величина сопротивляемости, необратимые изменения которой в процессе испытаний не учитываются;

- случайная величина сопротивляемости, необратимые изменения которой в процессе испытаний не учитываются;

- есть плотность функции распределения случайной величины

- есть плотность функции распределения случайной величины  , которая является результатом решения модели (18).

, которая является результатом решения модели (18).

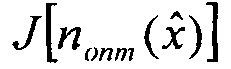

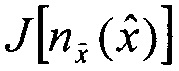

Решение данной задачи заключается в определении оптимального количества итераций  , при которых функционал

, при которых функционал  уравнения (18) или вероятность отказа СТС

уравнения (18) или вероятность отказа СТС  достигают минимальных значений для r.

достигают минимальных значений для r.

Устройство аппаратурно реализует выражение (18). В этом случае случайная величина  заменяется значением плотности функции распределения

заменяется значением плотности функции распределения  .

.

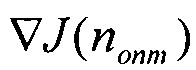

В дальнейших расчетах устройство реализует решение задачи минимизации функционала  уравнения (18) методом ускоренного спуска, сочетающего в себе метод найскорейшего спуска с использованием ускоренного метода перебора по следующему алгоритму:

уравнения (18) методом ускоренного спуска, сочетающего в себе метод найскорейшего спуска с использованием ускоренного метода перебора по следующему алгоритму:

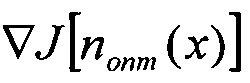

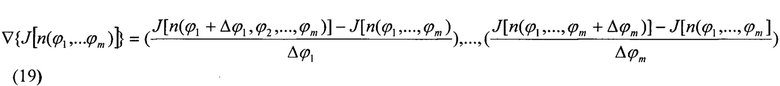

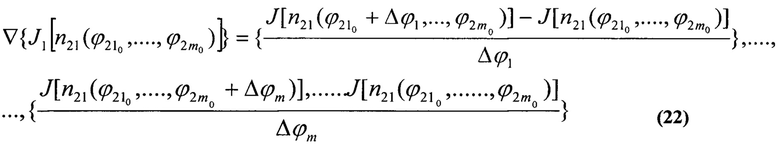

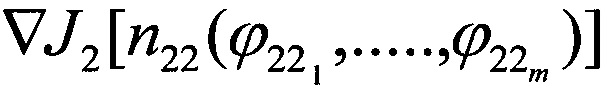

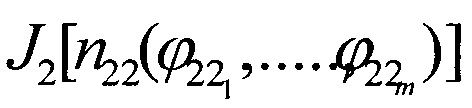

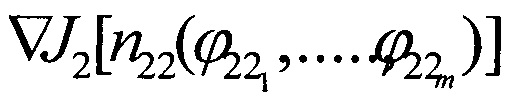

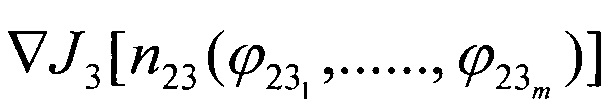

Определяется в общем виде градиент целевого функционала  по формуле

по формуле

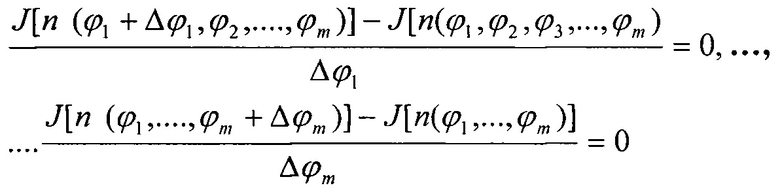

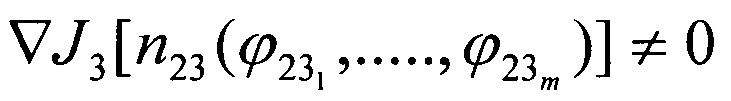

Необходимым условием минимизации целевого функционала  уравнения (18) является

уравнения (18) является

∇{J[n(ϕ1, …, ϕm)]}=0

т.е. все частные производные

Достаточное условие как правило входит в исходную информацию для работы данного устройства, для которой вторые частные производные функции  должны быть положительными.

должны быть положительными.

Далее устройство реализует построение итерационной последовательности n(ϕ1, …, ϕm)={nl, …, nn} по следующему сценарию:

Вся итерационная последовательность ni(ϕ1, …, ϕm) строится в два этапа.

Первый этап. Ускоренным методом перебора определяются первичные элементы n1i(ϕ11, …, ϕ1m) 1i-той итерационной последовательности для плотности распределения сопротивляемости  согласно (10), которая в начале увеличивается по линейному закону, что в целом предполагает возможность расчета искомой плотности функции распределения СТС

согласно (10), которая в начале увеличивается по линейному закону, что в целом предполагает возможность расчета искомой плотности функции распределения СТС  с минимальной погрешностью.

с минимальной погрешностью.

Процесс вычисления первичных элементов n1i(ϕ11, …, ϕ1m) 1i- итерационной последовательности для плотности функции распределения сопротивляемости  по формуле (10) вычисляется:

по формуле (10) вычисляется:

1-е допущение. Базовое значение погрешности плотности функции распределения СТС  задается по критерию минимума эвклидовой нормы отклонения площади под кривой

задается по критерию минимума эвклидовой нормы отклонения площади под кривой  от эталонного значения

от эталонного значения  , (формула 11)

, (формула 11)

при котором выполняются условия выполнения линейного закона, т.е. искомая плотность функции распределения СТС  вычисляется с минимальной погрешностью.

вычисляется с минимальной погрешностью.

В этом случае погрешность плотности функции распределения сопротивляемости СТС  определяется из прототипа

определяется из прототипа

Если погрешность определяется условием (20), то 1-е итерации n1i(,ϕ11…ϕ1m) исключаются из расчета  .

.

Процесс вычислений количества первичных элементов итерационной последовательности n1i(, ϕ11…ϕ1m) ускоренным методом перебора продолжается до тех пор, пока выполняется условие (20).

Момент окончания метода ускоренного перебора фиксируется номером итерационной последовательности n1i(ϕ11, …, ϕ1m), при котором погрешность плотности функции распределения СТС  определяется условием

определяется условием

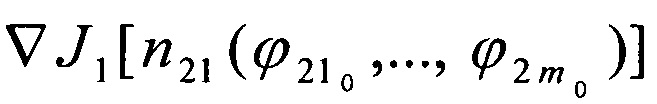

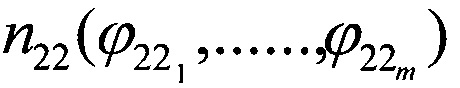

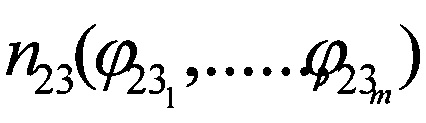

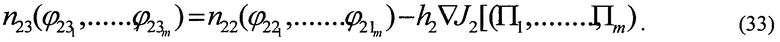

Второй этап. Методом найскорейшего спуска определяются элементы n2i(ϕ21, …, ϕ2m) 2i-ой итерационной последовательности по алгоритму:

- задаются начальные значения плотности распределения сопротивляемости для начальной итерации n2i(ϕ21, …, ϕ2m), которая является исходной точкой итерационной последовательности {n2i, …, n2n) итераций и совпадает с моментом окончания ускоренного метода перебора (условие (21) для 1-го этапа).

Обозначим начальную итерацию как  .

.

В определяемый градиент в общем виде  по формуле (19) подставляем координаты начальной итерации

по формуле (19) подставляем координаты начальной итерации  .

.

Определяем градиент

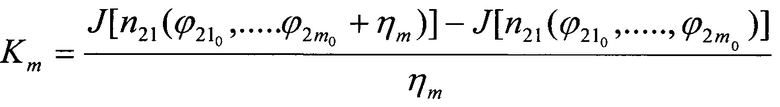

2-е допущение. Для повышения устойчивости вычислений по формуле (22) введем вместо приращений Δϕ1…Δϕm параметры регуляризации η1……ηm в формуле (19), которые задаются исходя из требуемой погрешности вычисления производных в формуле (19).

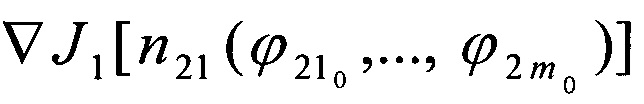

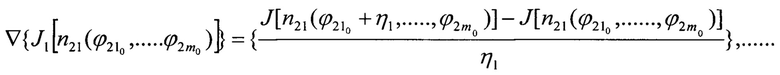

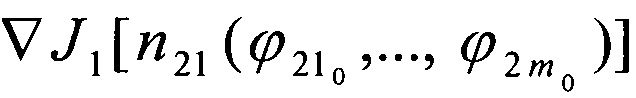

Тогда градиент  определяется в виде частных производных

определяется в виде частных производных

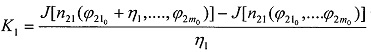

Введем следующие обозначения

;

;

Тогда градиент  определятся как

определятся как

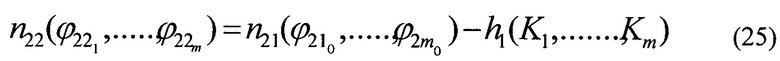

Затем определяется следующая итерация  по формуле

по формуле

где h1 - длина шага данной итерации, которая определяется по следующему алгоритму:

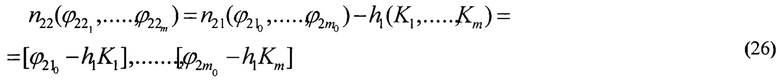

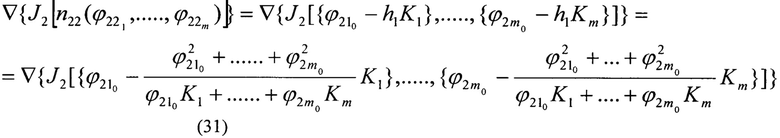

Перепишем уравнение (25) с учетом выражения (24) и введенных обозначений в следующем виде

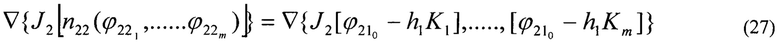

- Подставляя координаты точки  из уравнения (26) в уравнение (23), определяем градиент

из уравнения (26) в уравнение (23), определяем градиент  по формуле

по формуле

3-е допущение. Номера итерационной последовательности n2i(x2i, …, x2m) рассматриваются в виде ортогональных векторов.

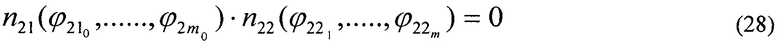

Тогда согласно свойству произведения ортогональных векторов составляется следующее уравнение

- Подставляя координаты 1-й итерации  и выражение (26) в формулу (28) получим

и выражение (26) в формулу (28) получим

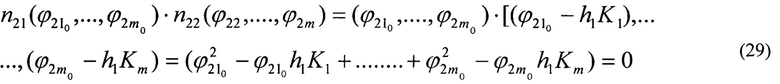

Из этого выражения определяем длину шага h1 в виде

Устройство аппаратурно реализует решение алгебраического уравнения (30) для определения h1.

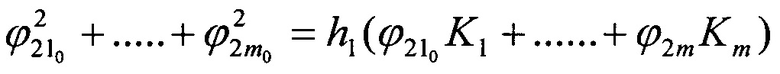

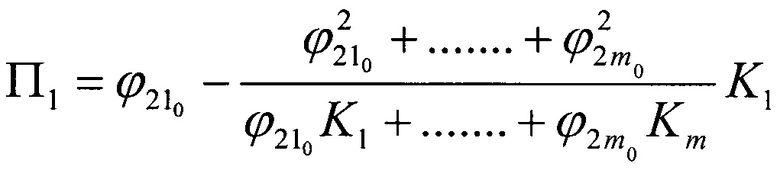

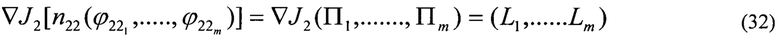

Подставляя выражение 30 в формулу (27) вычисляется

градиент  по формуле.

по формуле.

Введем обозначения

Тогда градиент  вычисляется в

вычисляется в

виде

и приравнивается 0.

L1, …… Lm - частные производные  по ϕ1……ϕm, которые вычисляются по аналогии с расчетом (23).

по ϕ1……ϕm, которые вычисляются по аналогии с расчетом (23).

4-е допущение. Для сокращения вычислений градиента  будем полагать, что

будем полагать, что  при условии, что все Пk=0

при условии, что все Пk=0

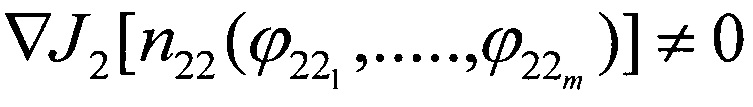

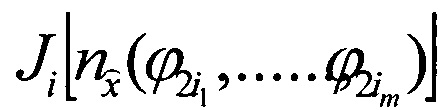

Если градиент  , то выполняется следующая итерация

, то выполняется следующая итерация

Длина шага h2 для уравнения (33) находится аналогично по ранее рассмотренному алгоритму.

Затем вычисляется градиент  по аналогии с расчетом (32).

по аналогии с расчетом (32).

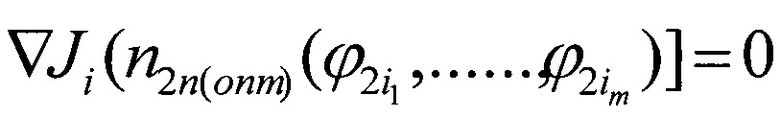

Если градиент  , то итерационный процесс вычислений элементов минимизируемой последовательности {n21, …, n2n} итераций, продолжается до тех пор пока не будет выполнятся условие минимизации

, то итерационный процесс вычислений элементов минимизируемой последовательности {n21, …, n2n} итераций, продолжается до тех пор пока не будет выполнятся условие минимизации  , при котором градиент

, при котором градиент  . В этом случае количество итераций

. В этом случае количество итераций  будет оптимальным или минимальным.

будет оптимальным или минимальным.

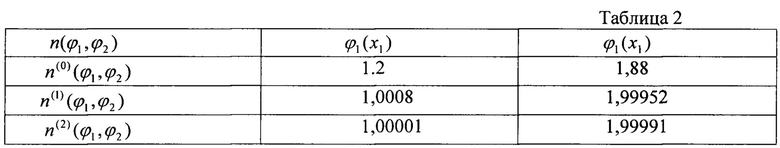

Технический результат подтверждается числовым примером решения 2-мерной задачи для уравнения 10 двумя методами: методом Зейделя и методом ускоренного спуска для уравнения (18).

Условие задачи. Определить оптимальные значения плотности распределения сопротивляемости  при заданной надежности

при заданной надежности  СТС для следующей задачи.

СТС для следующей задачи.

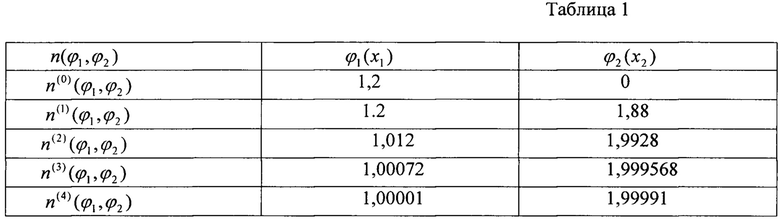

1. Решить следующую систему уравнений для 2-мерной задачи методом Зейделя по формуле (10)

где ϕ1(х1) - плотность распределения сопротивляемости СТС в момент времени t1

ϕ2(х2) - плотность распределения сопротивляемости СТС в момент времени t2

α=1 - параметр регуляризации.

Начальная итерация n(0)(ϕ1, ϕ2) для системы уравнений (34) задается как ϕ1(х1)=1,2 ϕ2(х1)=0

Решение системы (34) с точностью до 4-х знаков приводится в таблице 1

Из таблицы видно, что решение системы достигается 4-й итерацией n(4)(ϕ1, ϕ2), при этом соответственно ϕ1(х2)=1,00001 ϕ2(х2)=1,99991.

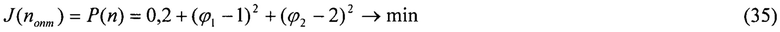

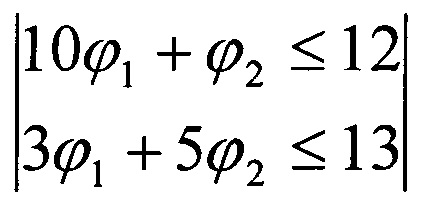

2. Решить предыдущую систему уравнений (33) методом ускоренного спуска по формуле (18).

Условие задачи. Определить такие значения плотности распределения сопротивляемости  , при которых при заданной надежности СТС обеспечивается минимальная вероятность отказа СТС.

, при которых при заданной надежности СТС обеспечивается минимальная вероятность отказа СТС.

Для решения данной задачи вводится целевой функционал для вероятности отказа  и составляется уравнение оптимального управления для системы уравнений (34) на основе уравнения (18).

и составляется уравнение оптимального управления для системы уравнений (34) на основе уравнения (18).

При следующих ограничениях

Начальная итерация для данной задачи n(0)(ϕ1, ϕ2) определяется методом ускоренного перебора: ϕ1(х1)=1,2; ϕ2(х2)=1,88 исходя из условия (21) и условия выполнения линейного закона: увеличения плотности распределения сопротивляемости  от номера итерации n(i)(ϕ1, ϕ2).

от номера итерации n(i)(ϕ1, ϕ2).

Затем находятся градиент  пo формуле (19) по частным производным уравнения (34) по ϕ1 и ϕ2 и приравнивается 0. Далее определяются такие ϕ1 и ϕ2, при которых градиент целевого функционала

пo формуле (19) по частным производным уравнения (34) по ϕ1 и ϕ2 и приравнивается 0. Далее определяются такие ϕ1 и ϕ2, при которых градиент целевого функционала  равен 0.

равен 0.

Решение данной системы с точностью до 4-х знаков приводится в таблице 2

Из таблицы видно, что расчет уравнения оптимального управления (34) достигается 2-й итерацией n(2)(ϕ1, ϕ2), при этом соответственно ϕ1(х2)=1,00001 ϕ2(х2)=1,99991.

Таким образом метод ускоренного спуска дает выигрыш по сравнения с методом ЗЕЙДЕЛЯ примерно в 2 раза по количеству итераций.

Устройство формирования оптимальных управляющих воздействий для обеспечения устойчивой работы сложных технических систем, содержащее коррелятор и анализатор случайного процесса, первый вход которого соединен с входом устройства, а второй вход - с выходом коррелятора, вход которого соединен с входом устройства, последовательно соединенные вычислительный блок, вход которого подключен к выходу анализатора случайного процесса, блок возведения в степень и блок транспортирования матриц, блок управления, первый сумматор, блок памяти, блок произведения, блок обращения матриц, регистратор, три элемента И, три элемента ИЛИ, блок формирования матриц, второй сумматор и первый блок сравнения, четыре входа блока памяти соединены соответственно с соответствующими выходами блока управления, пятый вход - с входом устройства, шестой вход - с первым выходом второго сумматора, с первого по третий выходы через первый элемент ИЛИ - с первым входом блока произведения, а четвертый выход - с первым входом второго сумматора, второй вход которого через второй элемент И соединен с выходом блока произведения, соединенным через третий элемент И с первым входом блока формирования матриц, первый выход которого соединен с первым входом второго элемента ИЛИ, а второй выход - через блок обращения матриц с четвертым входом первого элемента ИЛИ, третий вход второго сумматора соединен с выходом первого блока сравнения, выходы блока управления соединены с вторыми входами первого, второго и третьего элементов И и со вторым и третьим входами блока формирования матриц, а вход - с выходом первого блока сравнения, вход которого соединен через первый сумматор с первым выходом второго сумматора, второй выход которого соединен с регистратором, вход блока транспортирования матриц соединен с пятым входом первого элемента ИЛИ, а выход - со вторым входом второго элемента ИЛИ, подключенного выходом ко второму входу блока произведения, первую и вторую группы входных регистров, первая из которых состоит из m элементов, а вторая из Р элементов, первый входной регистр, коммутатор, блок умножения, первую группу блоков вычитания, первую и вторую группы квадраторов, первую и вторую группы блоков умножения, первую группу элементов ИЛИ, каждая из которых состоит из Р элементов, первый и второй накопительные сумматоры, первый и второй блоки извлечения квадратного корня, первый элемент задержки (ЭЗ), первый блок деления, первую группу регистров, группу коммутаторов, первую группу блоков индикации, каждая из которых состоит из m×р элементов, блок оценки минимального значения, вторую групп регистров, первую группу блоков сравнения, первую группу ЭЗ, вторую группу блоков индикации, каждая из которых состоит из m элементов, генератор тактовых импульсов и распределитель импульсов, тактовый вход которого соединен с выходом генератора тактовых импульсов, первый выход - с входами записи каждого элемента первой и второй группы входных регистров и входом записи первого входного регистра, с второго по 1+m-ый выходы - с входами считывания с первого по m-ый элементы первой группы входных регистров, 2+m-ый выход - с входом записи каждого элемента первого столбца первой группы регистров, 3+m-ый выход - с входом считывания каждого элемента второй группы входных регистров, 4+m-ый выход - с управляющим входом каждого элемента группы коммутаторов, 5+m-ый выход - с входом считывания первого входного регистра, 6+m-ый выход - с управляющим входом коммутатора, с 7+m-го по 6+2m-ый выходы - с входами записи с первого по m-ый элементы второй группы регистров, 1+3m-ый выход - с входом считывания каждого элемента первого столбца первой группы регистров, 4+4m-ый и 5+4m-ый выходы - соответственно с входами записи и считывания каждого элемента m-го столбца первой группы регистров, 1+5m-ый выход - с входом считывания каждого элемента второй группы регистров и с управляющим входом блока оценки минимального значения, информационные входы первой группы входных регистров являются входами задания исходной информации, на которые поступают величины αk, характеризующие значение коэффициента стабильности для k-то варианта вычислений, информационные входы второй группы входных регистров являются входами задания исходной информации, на которые подаются значения  , характеризующие эталонные значения функции распределения сопротивляемости, информационный вход первого входного регистра является входом задания исходной информации, на который поступает значение Δх, характеризующее значение длины интервала разбиения аргумента х функции распределения сопротивляемости, выходы с первого по m-ый элементов первой группы входных регистров соединены с первого по m-ый входами третьего элемента ИЛИ, выход которого подключен к первому входу блока умножения, выход которого соединен с седьмым входом блока памяти, а второй вход через первый элемент И - с выходами блока произведения, выход каждого элемента второй группы входных регистров подключен к входам уменьшаемого соответствующих элементов первой группы блоков вычитания и к входам соответствующих элементов первой группы квадраторов, выход каждого из которых соединен с первым входом соответствующего элемента первой группы блоков умножения, второй вход которого подключен к первому выходу коммутатора, а выход - к входам, с первого по Р-ый первого накопительного сумматора, выход которого через первый блок извлечения квадратного корня соединен с входом делимого первого блока деления, вход делителя которого подключен через последовательно соединенные первые ЭЗ и второй блок извлечения квадратного корня к выходу второго накопительного сумматора, с первого по Р-ый входы которого соединены с выходами с первого по Р-ый элементов второй группы блоков умножения, первые входы каждого из которых подключены ко второму выходу коммутатора, а вторые входы - к выходам соответствующих элементов второй группы квадраторов, вход каждого из которых соединен с выходом соответствующего элемента первой группы блоков вычитания, вход вычитаемого каждого из которых подключен к выходу соответствующего элемента первой группы элементов ИЛИ, с первого по m-ый входы каждого из которых соединены со вторыми выходами каждого элемента соответствующей строки группы коммутаторов, вторые выходы каждого из элемента которой подключены к входам соответствующих элементов первой группы блоков индикации, а информационные входы элементов группы коммутаторов - к выходам соответствующих элементов первой группы регистров, информационный вход каждого из которых соединен с множественным выходом второго сумматора, выход первого блока деления подключен к информационному входу каждого элемента второй группы регистров, выходы которых соединены с входами соответствующих элементов первой группы ЭЗ и с первого по m-ый входами блока оценки минимального значения, выход которого подключен к пороговому входу каждого элемента первой группы блоков сравнения, информационные входы которых соединены с выходами соответствующих элементов первой группы ЭЗ, а выходы - с входами соответствующих элементов второй группы блоков индикации, отличающееся тем, что оно дополнительно содержит вторую группу блоков вычитания, третью и четвертую группы блоков умножения, каждая из которых состоит из m×р элементов, группу накопительных сумматоров, состоящую из р элементов, вторую группу блоков сравнения, вторую группу ЭЗ, каждая из которых состоит из m×р элементов, вторую группу элементов ИЛИ, группу ключей, группу сумматоров, третью группу ЭЗ, каждая из которых состоит из р элементов, третью группу регистров, которая состоит из m×р элементов, третью группу входных регистров, четвертую группу ЭЗ, третью группу квадраторов, пятую группу ЭЗ, каждая из которых состоит из р элементов, третий накопительный сумматор, второй ЭЗ, второй блок деления, четвертый накопительный сумматор, третью и четвертую группы блоков вычитания, группу блоков деления, пятую и шестую группы блоков умножения, каждая из которых состоит из m элементов, шестую и седьмую группы ЭЗ, третью группу блоков сравнения, каждая из которых состоит из р элементов, четвертый элемент ИЛИ, счетчик, второй блок сравнения, блок индикации, восьмую группу ЭЗ, состоящую из р элементов, девятую группу ЭЗ, состоящую из (р-1) элементов, второй входной регистр, вход записи которого соединен с первым выходом распределителя импульсов, 2+5m-ый выход которого подключен к входу считывания каждого элемента третьей группы входных регистров и группы счетчиков, 3+5m-ый выход - к входу запуска счетчика, 4+5m-ый выход - к входу считывания второго входного регистра, а первый выход - также к входу записи каждого элемента третьей группы входных регистров, 2+3m-ый и 5+4m-ый выходы распределителя импульсов соединены с входами записи различных столбцов третьего регистра, информационные входы третьей группы входных регистров являются входами задания исходной информации, на которые подаются значения ηk, характеризующие приращения величины плотности распределения сопротивляемости, информационный вход второго входного регистра является входом задания исходной информации, на который поступает значение р, характеризующее значение числа интервалов разбиения плотности функции распределения сопротивляемости, входы вычитаемого каждого элемента второй группы блоков вычитания соединены с множественным выходом анализатора случайного процесса, выходы - с первыми входами каждого элемента третьей группы блоков умножения, вторые входы каждого элемента которой к множественному выходу блока возведения в степень, а выходы - к первым входам каждого элемента четвертой группы блоков умножения, вторые входы которых подключены к выходам соответствующих элементов первой группы регистров, а выходы каждой строки - к входам с первого по m-ый, соответствующих элементов группы накопительных сумматоров, выходы которых соединены с входами соответствующих элементов восьмой группы ЭЗ, выходы которых подключены к пороговым входам третьей группы блоков сравнения, информационные входы которых подключены к выходам соответствующих элементов четвертой группы блоков вычитания, а выход первого элемента - к первому входу четвертого элемента ИЛИ, выходы со второго по р-ый элементов третьей группы блоков сравнения - к входам соответствующих элементов девятой группы ЭЗ, выход которых соединен со вторым по р-ый входом четвертого элемента ИЛИ, выход которого соединен с информационным входом счетчика, выход которого подключен к информационному входу второго блока сравнения, пороговый вход которого соединен с выходом второго входного регистра, а выход - с входом блока индикации, пороговые входы каждого элемента второй группы блоков сравнения подключены к выходу блока оценки минимального значения, информационные входы к выходам соответствующих элементов второй группы ЭЗ, входы каждого из которых соединены с выходами соответствующих элементов первой группы регистров, выходы каждого элемента второй группы блоков сравнения подключены к входам считывания соответствующих элементов третьей группы регистров, информационные входы каждого из которых соединены с выходами соответствующих элементов второй группы ЭЗ, а выходы каждой строки - с входами, с первого по m-ый соответствующих элементов второй группы элементов ИЛИ, выходы которых подключены к входам соответствующих элементов ключей, выходы которых подключены к входам соответствующих элементов третьей группы ЭЗ, третьей группы квадраторов, пятой группы ЭЗ и первыми входами каждого элемента группы сумматоров, вторые входы которых соединены с выходами соответствующих элементов третьей группы входных регистров, выходы которой подключены также к входам соответствующих элементов четвертой группы ЭЗ, выходы которой соединены с входами делителя соответствующих элементов группы блоков деления, входы делимого которых подключены к выходам соответствующих элементов третьей группы блоков вычитания, входы вычитаемого и уменьшаемого которых соединены соответственно с элементами третьей группы ЭЗ и группы сумматоров, выходы группы блоков деления подключены к первым входам соответствующих элементов пятой группы блоков умножения и к входам шестой группы ЭЗ, выходы которой соединены с первыми входами шестой группы умножения, выходы которой подключены к входам вычитаемого соответствующих элементов четвертой группы блоков вычитания, входы уменьшаемого которых соединены с выходами соответствующих элементов седьмой группы ЭЗ, выходы пятой группы ЭЗ подключены к входам соответствующих элементов седьмой группы ЭЗ и по вторым входам соответствующих элементов пятой группы блоков умножения, выходы которых соединены с входами с первым по р-ый четвертого накопительного сумматора, выход которого подключен к входу делителя второго блока деления, выход которого соединен со вторыми входами каждого элемента шестой группы блоков умножения, а вход делимого - с выходом второго ЭЗ, вход которого подключен к выходу третьего накопительного сумматора, входы которого, с первого по р-ый, соединены с выходами соответствующих элементов третьей группы квадраторов.

, характеризующие эталонные значения функции распределения сопротивляемости, информационный вход первого входного регистра является входом задания исходной информации, на который поступает значение Δх, характеризующее значение длины интервала разбиения аргумента х функции распределения сопротивляемости, выходы с первого по m-ый элементов первой группы входных регистров соединены с первого по m-ый входами третьего элемента ИЛИ, выход которого подключен к первому входу блока умножения, выход которого соединен с седьмым входом блока памяти, а второй вход через первый элемент И - с выходами блока произведения, выход каждого элемента второй группы входных регистров подключен к входам уменьшаемого соответствующих элементов первой группы блоков вычитания и к входам соответствующих элементов первой группы квадраторов, выход каждого из которых соединен с первым входом соответствующего элемента первой группы блоков умножения, второй вход которого подключен к первому выходу коммутатора, а выход - к входам, с первого по Р-ый первого накопительного сумматора, выход которого через первый блок извлечения квадратного корня соединен с входом делимого первого блока деления, вход делителя которого подключен через последовательно соединенные первые ЭЗ и второй блок извлечения квадратного корня к выходу второго накопительного сумматора, с первого по Р-ый входы которого соединены с выходами с первого по Р-ый элементов второй группы блоков умножения, первые входы каждого из которых подключены ко второму выходу коммутатора, а вторые входы - к выходам соответствующих элементов второй группы квадраторов, вход каждого из которых соединен с выходом соответствующего элемента первой группы блоков вычитания, вход вычитаемого каждого из которых подключен к выходу соответствующего элемента первой группы элементов ИЛИ, с первого по m-ый входы каждого из которых соединены со вторыми выходами каждого элемента соответствующей строки группы коммутаторов, вторые выходы каждого из элемента которой подключены к входам соответствующих элементов первой группы блоков индикации, а информационные входы элементов группы коммутаторов - к выходам соответствующих элементов первой группы регистров, информационный вход каждого из которых соединен с множественным выходом второго сумматора, выход первого блока деления подключен к информационному входу каждого элемента второй группы регистров, выходы которых соединены с входами соответствующих элементов первой группы ЭЗ и с первого по m-ый входами блока оценки минимального значения, выход которого подключен к пороговому входу каждого элемента первой группы блоков сравнения, информационные входы которых соединены с выходами соответствующих элементов первой группы ЭЗ, а выходы - с входами соответствующих элементов второй группы блоков индикации, отличающееся тем, что оно дополнительно содержит вторую группу блоков вычитания, третью и четвертую группы блоков умножения, каждая из которых состоит из m×р элементов, группу накопительных сумматоров, состоящую из р элементов, вторую группу блоков сравнения, вторую группу ЭЗ, каждая из которых состоит из m×р элементов, вторую группу элементов ИЛИ, группу ключей, группу сумматоров, третью группу ЭЗ, каждая из которых состоит из р элементов, третью группу регистров, которая состоит из m×р элементов, третью группу входных регистров, четвертую группу ЭЗ, третью группу квадраторов, пятую группу ЭЗ, каждая из которых состоит из р элементов, третий накопительный сумматор, второй ЭЗ, второй блок деления, четвертый накопительный сумматор, третью и четвертую группы блоков вычитания, группу блоков деления, пятую и шестую группы блоков умножения, каждая из которых состоит из m элементов, шестую и седьмую группы ЭЗ, третью группу блоков сравнения, каждая из которых состоит из р элементов, четвертый элемент ИЛИ, счетчик, второй блок сравнения, блок индикации, восьмую группу ЭЗ, состоящую из р элементов, девятую группу ЭЗ, состоящую из (р-1) элементов, второй входной регистр, вход записи которого соединен с первым выходом распределителя импульсов, 2+5m-ый выход которого подключен к входу считывания каждого элемента третьей группы входных регистров и группы счетчиков, 3+5m-ый выход - к входу запуска счетчика, 4+5m-ый выход - к входу считывания второго входного регистра, а первый выход - также к входу записи каждого элемента третьей группы входных регистров, 2+3m-ый и 5+4m-ый выходы распределителя импульсов соединены с входами записи различных столбцов третьего регистра, информационные входы третьей группы входных регистров являются входами задания исходной информации, на которые подаются значения ηk, характеризующие приращения величины плотности распределения сопротивляемости, информационный вход второго входного регистра является входом задания исходной информации, на который поступает значение р, характеризующее значение числа интервалов разбиения плотности функции распределения сопротивляемости, входы вычитаемого каждого элемента второй группы блоков вычитания соединены с множественным выходом анализатора случайного процесса, выходы - с первыми входами каждого элемента третьей группы блоков умножения, вторые входы каждого элемента которой к множественному выходу блока возведения в степень, а выходы - к первым входам каждого элемента четвертой группы блоков умножения, вторые входы которых подключены к выходам соответствующих элементов первой группы регистров, а выходы каждой строки - к входам с первого по m-ый, соответствующих элементов группы накопительных сумматоров, выходы которых соединены с входами соответствующих элементов восьмой группы ЭЗ, выходы которых подключены к пороговым входам третьей группы блоков сравнения, информационные входы которых подключены к выходам соответствующих элементов четвертой группы блоков вычитания, а выход первого элемента - к первому входу четвертого элемента ИЛИ, выходы со второго по р-ый элементов третьей группы блоков сравнения - к входам соответствующих элементов девятой группы ЭЗ, выход которых соединен со вторым по р-ый входом четвертого элемента ИЛИ, выход которого соединен с информационным входом счетчика, выход которого подключен к информационному входу второго блока сравнения, пороговый вход которого соединен с выходом второго входного регистра, а выход - с входом блока индикации, пороговые входы каждого элемента второй группы блоков сравнения подключены к выходу блока оценки минимального значения, информационные входы к выходам соответствующих элементов второй группы ЭЗ, входы каждого из которых соединены с выходами соответствующих элементов первой группы регистров, выходы каждого элемента второй группы блоков сравнения подключены к входам считывания соответствующих элементов третьей группы регистров, информационные входы каждого из которых соединены с выходами соответствующих элементов второй группы ЭЗ, а выходы каждой строки - с входами, с первого по m-ый соответствующих элементов второй группы элементов ИЛИ, выходы которых подключены к входам соответствующих элементов ключей, выходы которых подключены к входам соответствующих элементов третьей группы ЭЗ, третьей группы квадраторов, пятой группы ЭЗ и первыми входами каждого элемента группы сумматоров, вторые входы которых соединены с выходами соответствующих элементов третьей группы входных регистров, выходы которой подключены также к входам соответствующих элементов четвертой группы ЭЗ, выходы которой соединены с входами делителя соответствующих элементов группы блоков деления, входы делимого которых подключены к выходам соответствующих элементов третьей группы блоков вычитания, входы вычитаемого и уменьшаемого которых соединены соответственно с элементами третьей группы ЭЗ и группы сумматоров, выходы группы блоков деления подключены к первым входам соответствующих элементов пятой группы блоков умножения и к входам шестой группы ЭЗ, выходы которой соединены с первыми входами шестой группы умножения, выходы которой подключены к входам вычитаемого соответствующих элементов четвертой группы блоков вычитания, входы уменьшаемого которых соединены с выходами соответствующих элементов седьмой группы ЭЗ, выходы пятой группы ЭЗ подключены к входам соответствующих элементов седьмой группы ЭЗ и по вторым входам соответствующих элементов пятой группы блоков умножения, выходы которых соединены с входами с первым по р-ый четвертого накопительного сумматора, выход которого подключен к входу делителя второго блока деления, выход которого соединен со вторыми входами каждого элемента шестой группы блоков умножения, а вход делимого - с выходом второго ЭЗ, вход которого подключен к выходу третьего накопительного сумматора, входы которого, с первого по р-ый, соединены с выходами соответствующих элементов третьей группы квадраторов.

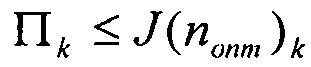

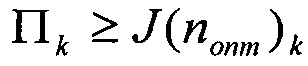

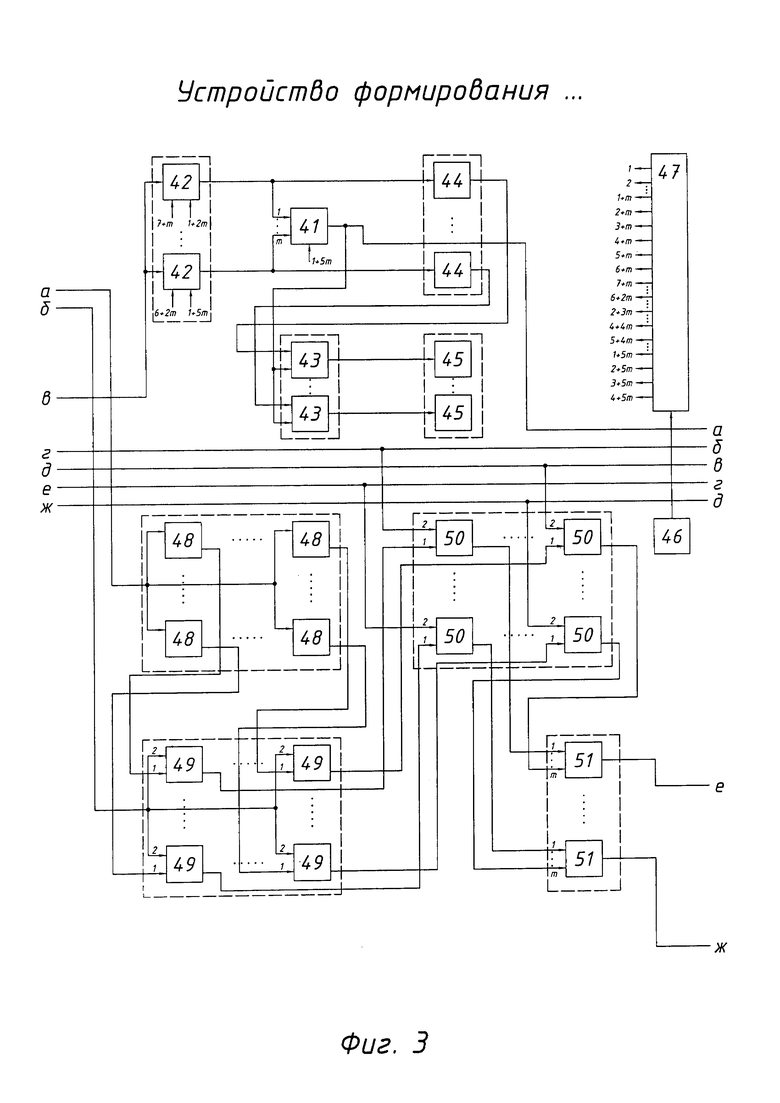

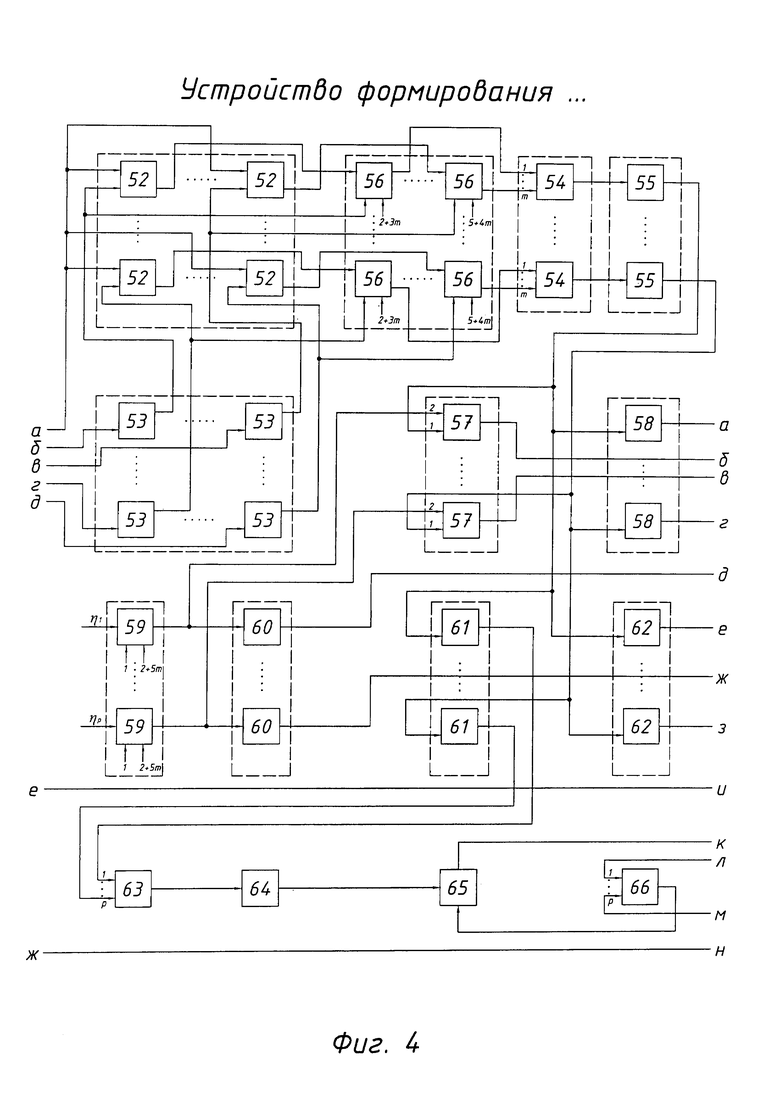

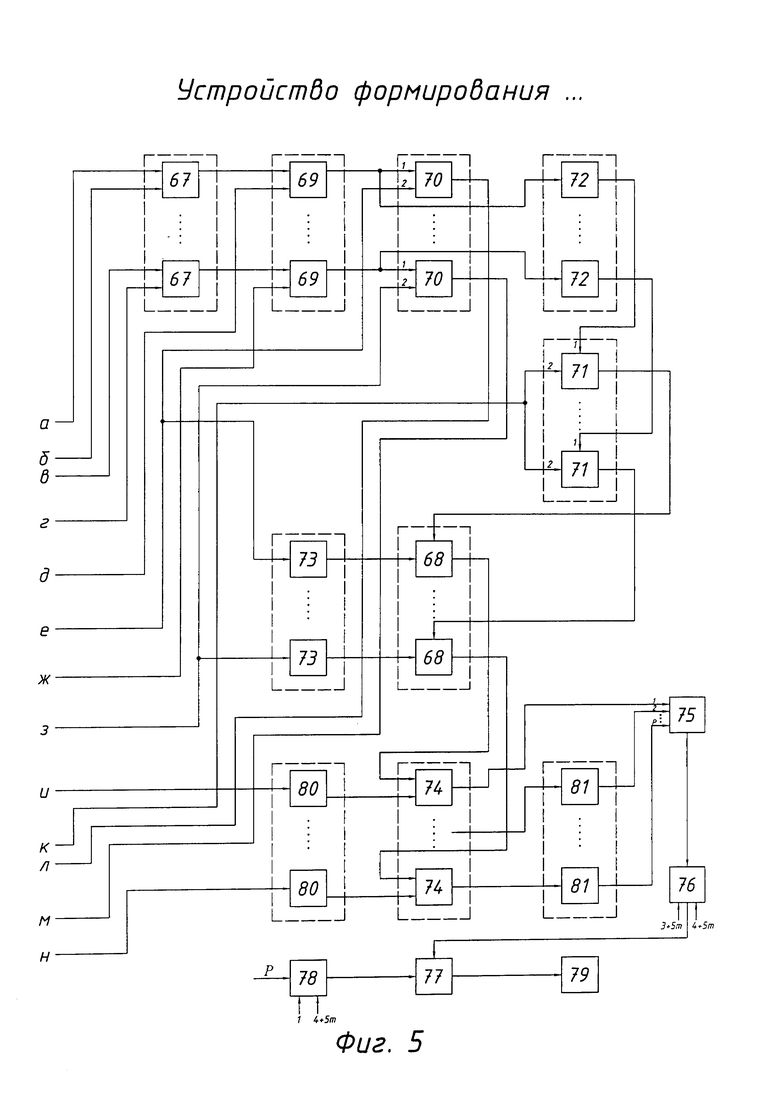

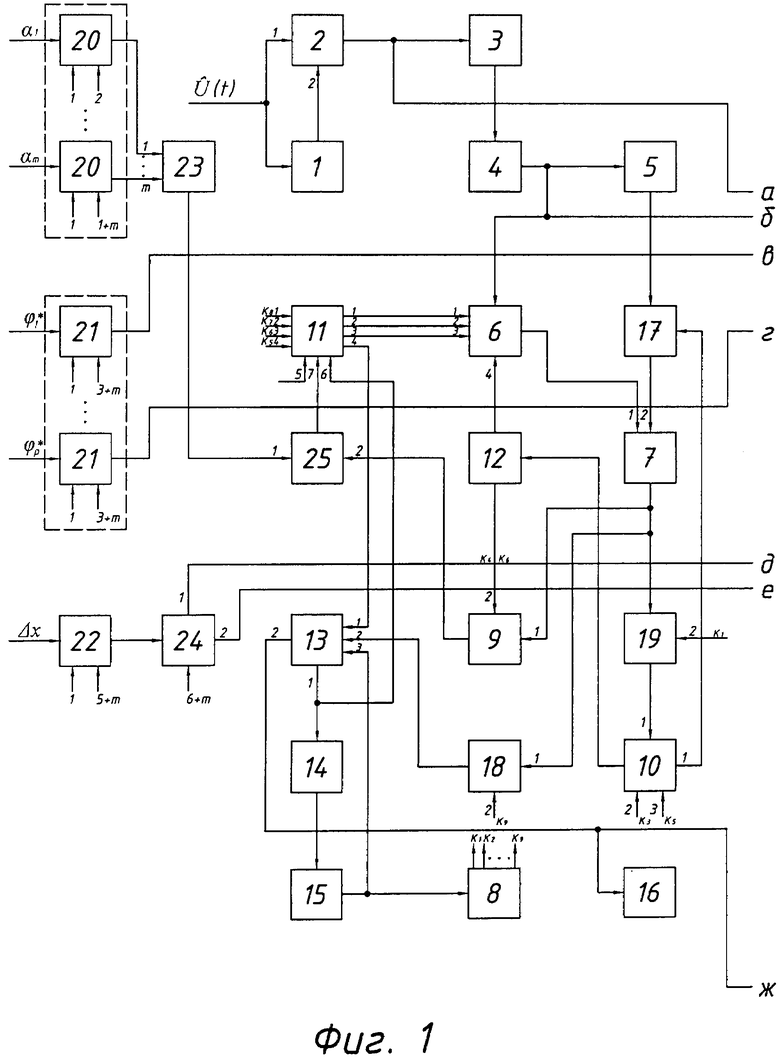

На фиг 1, 2 ,3, 4, 5 представлена функциональная схема устройства для принятия оптимального решения при эксплуатации сложных технических систем (для исключения громоздкости связи между РИ и управляющими входами соответствующих блоков показаны не полностью, а обозначены путем нумерации входов и выходов).

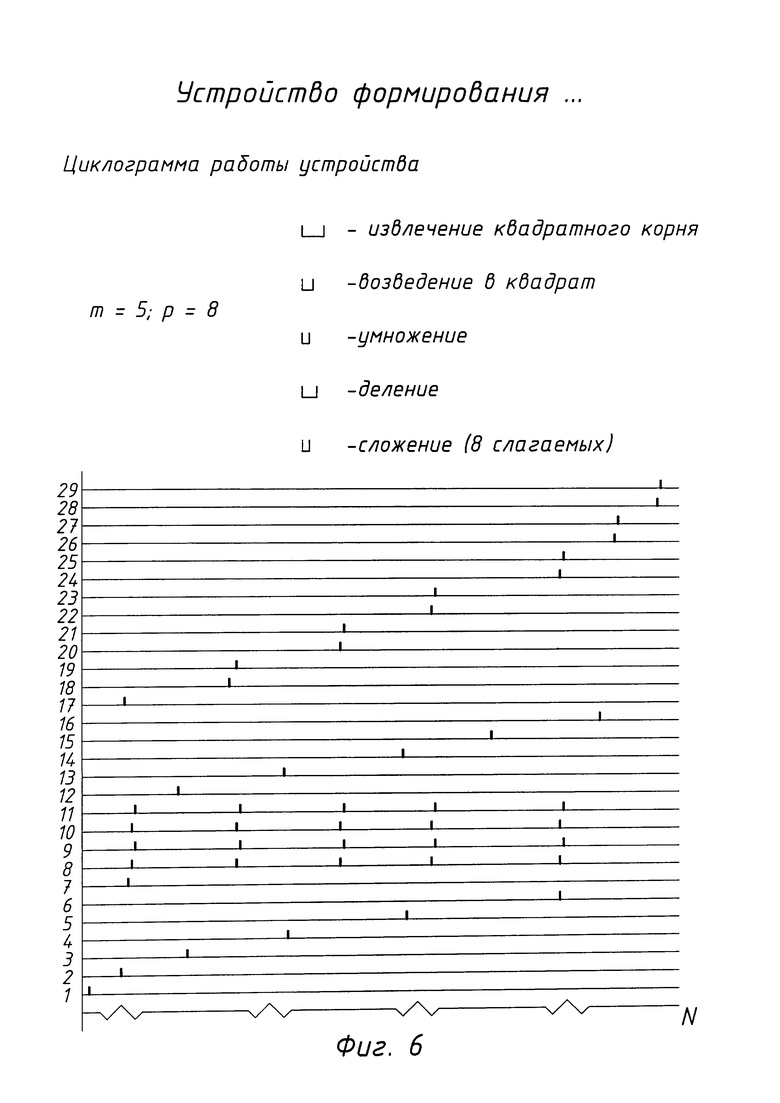

На фиг. 6 представлена циклограмма работы устройства (по оси ординат обозначены номера выходов РИ, а по оси абсцисс - число пакетов), причем длительность различных вычислительных операций (извлечения квадратного корня - двадцать тактов, возведение в квадрат - восемь тактов, умножение - восемь тактов, деление - шестнадцать тактов, сложение восьми слагаемых - семь тактов) в верхней части фиг.6 (для возможности исполнения циклограммы принято m=5, Р=8 хотя величины могут принять произвольные значения). Поскольку длительность выполнения вычислительных операций некоторыми блоками прототипа определить проблематично, на оси абсцисс выполнены "разрывы".

Устройство формирования управляющих воздействий для обеспечения устойчивой работы сложных технических систем (фиг. 1, 2, 3, 4 5) содержит коррелятор 1, анализатор 2 случайного процесса, вычислительный блок 3, блок 4 возведения в степень, блок 5 транспортирования матриц, первый элемент ИЛИ 6, блок 7 произведения, блок 8 управления, первый элемент И 9, блок 10 формирования матриц, блок 11 памяти, блок-12 обращения матриц, второй 13 и первый 14 сумматоры, блок 15 сравнения, регистратор 16, второй элемент ИЛИ 17, второй 18 и третий 19 элементы И, первую 20 и вторую 21 группы входных регистров, первая из которых состоит из m элементов, а вторая из Р элементов, первый входной регистр 22, третий элемент ИЛИ 23, коммутатор 24, блок 25 умножения, первую группу 26 блоков вычитания, первую 27 и второю 28 группы квадраторов, первую 29 и вторую 30 группы блоков умножения, первую группу 31 элементов ИЛИ, каждая из которых состоит из Р элементов, первый 32 и второй 33 накопительные сумматоры, первый 34 и второй 35 блоки извлечения квадратного корня, первый элемент 36 задержки, первый блок 37 деления, первую группу 38 регистров, группу 39 коммутаторов, первую группу 40 блоков индикации, каждая из которых состоит из m×p элементов, блок 41 оценки минимального значения, вторую группу 42 регистров, первую группу 43 блоков сравнения, первую группу 44 ЭЗ, вторую группу 45 блоков индикации, каждая из которых состоит из m элементов, генератор 46 тактовых импульсов, РИ 47, вторую группу 48 блоков вычитания, третью 49 и четвертую 50 группы блоков умножения, каждая из которых состоит из m×p элементов, группу 51 накопительных сумматоров, состоящую из р элементов, вторую группу 52 блоков сравнения, вторую группу 53 ЭЗ, из которых состоит из m×p элементов, вторую группу 54 элементов ИЛИ, группу 55 ключей, каждая из которых состоит из m элементов, третью группу 56 регистров, состоящую из m×p элементов, группу 57 сумматоров, третью группу 58 ЭЗ, каждая из которых состоит из р элементов, третью группу 59 входных регистров, четвертую группу 60 ЭЗ, третью группу 61 квадраторов, пятую группу 62 ЭЗ, каждая из которых состоит из р элементов, третий накопительный сумматор 63, второй ЭЗ 64, второй блок 65 деления, четвертый накопительный сумматор 66, третью 67 и четвертую 68 группы блоков вычитания, группу 69 блоков деления, пятую 70 и шесту 71 группы блоков умножения, каждая из которых состоит из р элементов, шестую 72 и седьмую 73 группы ЭЗ, третью труппу 74 блоков сравнения, каждая из которых состоит из р элементов, четвертый элемент ИЛИ 75, счетчик 76, второй блок 77 сравнения, второй входной регистр 78 и блок 79 индикации.

Следует подчеркнуть, что вновь введенные блоки и элементы являются стандартными.

Информация о блоках и элементах устройства изложена в следующих источниках:

1. Приборы с зарядовой связью. / Под ред. М. Хоувза и Д. Моргана: Пер. с англ. - М.: Энергоиздат, 1981. - 376 с., ил.

2. Руководство пользователя по сигнальным микропроцессорам ADSP-2100. / Пер. с англ. О.В. Луневой; Под ред. А.Д. Викторова; Санкт-Петербургский государственный электротехнический университет. - Санкт-Петербург, 1997. - 520 с.

3. В.Б. Стешенко ПЛИС фирмы "ALTERA": Проектирование устройств обработки сигналов. / М.: "Додека", 2000.

Наличие только одного входа у каждого элемента второй группы 48 блоков вычитания предполагает, что постоянное уменьшаемое, равное единице, заранее «зашито» в каждом элементе этой группы.

Устройство формирования управляющих воздействий для обеспечения устойчивой работы сложных технических систем работает следующим образом. На информационные входы каждого из элементов первой группы 20 входных регистров засылаются коэффициенты стабильности αk для K-го варианта вычислений. На информационные входы каждого из элементов второй группы 21 входных регистров подаются величины эталонного значения

-го сечения функции распределения сопротивляемости исследуемой СТС. На информационный вход первого входного регистра 22 засылается длина Δх интервала разбиения аргумента х функции распределения сопротивляемости. На информационные входы каждого из элементов третьей группы 59 входных регистров направляются значения ηk, характеризующие приращения величины плотности функции распределения сопротивляемости. На информационный вход второго входного регистра 78 засылается величина р, характеризующая значение числа интервалов разбиения плотности функции распределения сопротивляемости. При этом управляющий сигнал на входы записи групп 20, 21 и 59, а также входных регистров 22 и 78 подается с первого выхода распределителя 47 импульсов, темп работы которого задается генератором 46 тактовых импульсов.

-го сечения функции распределения сопротивляемости исследуемой СТС. На информационный вход первого входного регистра 22 засылается длина Δх интервала разбиения аргумента х функции распределения сопротивляемости. На информационные входы каждого из элементов третьей группы 59 входных регистров направляются значения ηk, характеризующие приращения величины плотности функции распределения сопротивляемости. На информационный вход второго входного регистра 78 засылается величина р, характеризующая значение числа интервалов разбиения плотности функции распределения сопротивляемости. При этом управляющий сигнал на входы записи групп 20, 21 и 59, а также входных регистров 22 и 78 подается с первого выхода распределителя 47 импульсов, темп работы которого задается генератором 46 тактовых импульсов.

Следующий этап оценки функции распределения сопротивляемости осуществляется, в основном, с помощью блоков прототипа.

Информация о нагрузках на исследуемую СТС, представленная в виде сигнала U(t), поступает на вход коррелятора 1 и на вход анализатора 2. В корреляторе 1 определяется автокорреляционная функция исследуемого сигнала и по ней вычисляется период его корреляции Δτ. Период корреляции задается анализатору 2, в котором исследуемый сигнал разбивается на промежутки Δτ и затем в каждом из полученных промежутков определяется наибольшее значение. По выбранным значениям максимумов из интервалов разбиения исследуемого сигнала блоком 3 определяется условная вероятность , которая поступает в блок 4, где возводится в степень n. Информация с выхода блока 4 представляет собой матрицу В уравнения (3), которая в блоке 5 преобразуется в матрицу ВT. С выхода блоков 4 и 5 через элементы 6 и 17 матрицы В и ВT поступают в блок 7. Полученная в результате перемножения матрица Ф по сигналу К1 блока через элемент И 19 засылается в блок 10, где преобразуется в две треугольные матрицы А и D.

, которая поступает в блок 4, где возводится в степень n. Информация с выхода блока 4 представляет собой матрицу В уравнения (3), которая в блоке 5 преобразуется в матрицу ВT. С выхода блоков 4 и 5 через элементы 6 и 17 матрицы В и ВT поступают в блок 7. Полученная в результате перемножения матрица Ф по сигналу К1 блока через элемент И 19 засылается в блок 10, где преобразуется в две треугольные матрицы А и D.

Блоки 5 и 10 практически идентичны и выполнены по единой схеме. Они состоят из двух счетчиков (целочисленных сумматоров) для формирования текущих номеров строки i и столбца j матрицы, блока пересылки чисел для выбора чисел из матрицы и записи этих чисел в матрицу по заданным номерам i и j и блока (блоков) памяти для хранения исходной и сформированных матриц. Отличие состоит лишь в том, что в блоке 5 достаточно одного блока памяти для матрицы В, так как транспонирование матрицы сводится к тому, что блок пересылки меняет местами симметричные относительно главной диагонали элементы матрицы В, т.е.  . В блоке 10 требуется два блока памяти, в одном из которых хранится исходная матрица Ф, преобразованная в результате работы блока пересылки в нижнюю треугольную матрицу, а в другом - сформированная с помощью блока пересылки верхняя треугольная матрица А.

. В блоке 10 требуется два блока памяти, в одном из которых хранится исходная матрица Ф, преобразованная в результате работы блока пересылки в нижнюю треугольную матрицу, а в другом - сформированная с помощью блока пересылки верхняя треугольная матрица А.

По команде К2 блока 8 из блока 11 вектор r через элемент ИЛИ 6 пересылается в блок 7, где перемножается с хранимым там значением ВТ. При этом вычисляется вектор С.

На следующем этапе работы устройства по управляющему сигналу К3 блока 8 матрица D через блок 12 и элемент ИЛИ 6 подается в блок 7, где значение D-1 перемножается со значением С -- результатом предыдущей операции. Результатом перемножения является вектор g, который по команде К4 блока 8 через элемент И 9 засылается в блок 11.

В блок 7 по команде К5 блока 8 через элемент ИЛИ 6 засылается матрица А, где она перемножается с матрицей D-1. Полученная в результате перемножения матрица Н по команде К6 блока 8 через элемент И 9 пересылается на второй вход блока 25 умножения, на первый вход которого по управляющему сигналу со второго выхода РИ 47 на вход считывания первого элемента первой группы 20 входных регистров с выхода этого элемента величина α1 (значения коэффициента стабильности для первого варианта вычислений) подается через третий элемент ИЛИ 23. Результат этого умножения направляется с выхода блока 25 на вход блока 11 памяти. На этом подготовленные операции по вычислению неизвестной  методом Зейделя заканчивается.

методом Зейделя заканчивается.

По команде К7 блока 8 с блока 11 через элемент ИЛИ 6 в блок 7 засылается значение Н, а по команде К8 через элемент ИЛИ 6 в блок 7-приближенное ϕ° значение искомой функции ϕ. Если информация о приближенном значении отсутствует, то в качестве первого приближения в блоке 7 записывается значение ϕ°=1.

В блоке 7 матрица Н и вектор ϕ° перемножаются и произведение по команде К 9 через элемент И 18 направляется в сумматор 13, куда по команде К 8 блока 8 из блока 11 поступает вектор g. С выхода сумматора 13 искомое значение первого шага итерации (в дальнейшем n+1 шага) подается на сумматор 14, где определяется разность Δn=ϕn-ϕn+1 и на блок 11, где оно записывается вместо ϕ°. С сумматора 14 значение Δn поступает в блок 15, где значение Δn сопоставляется с заданной ошибкой вычислений Δ. В дальнейшем в этом блоке ошибка (n+1)-го шага итерации сравнивается с Δ. Если в результате сравнения оказывается, что Δn-1≤Δ, то итерационный процесс определения функции ϕ по команде блока 15 в блок 8 прекращается и значение искомой функции ϕ сумматора 13 по этой же команде выдается в регистр 16, а блок 8 приводится в исходное состояние. В противном случае итерационный процесс вычислений функции ϕ с требуемой точностью продолжается, что достигается повторной подачей команд К7-К9 с блока 8.

С выхода второго сумматора 13 значения  первого варианта вычисления функции распределения сопротивляемости засылаются на соответствующие элементы первой группы 38 регистров. Однако, запись будет осуществлена только в первом столбце этой группы потому, что сигнал с 2+m-го выхода РИ 47 будет подаваться на входы записи только с первого по р-ый элементы первого из m столбцов.

первого варианта вычисления функции распределения сопротивляемости засылаются на соответствующие элементы первой группы 38 регистров. Однако, запись будет осуществлена только в первом столбце этой группы потому, что сигнал с 2+m-го выхода РИ 47 будет подаваться на входы записи только с первого по р-ый элементы первого из m столбцов.

По сигналу с 3+m-го выхода РИ 47 на входы считывания второй группы 21 входных регистров значения  с выходов элементов этой группы направляются на входы уменьшаемого соответствующих элементов группы 26 блоков вычитания и на входы первой группы 27 квадраторов. По сигналу с 5+m-го выхода РИ 47 на вход считывания входного регистра 22 величина Δх поступает через коммутатор 24 на вторые входы первой группы 29 блоков умножения и на первые входы второй группы 30 блоков вычитания. По сигналу с 2+3m-го выхода РИ 47 на входы считывания первой группы 38 регистров значения

с выходов элементов этой группы направляются на входы уменьшаемого соответствующих элементов группы 26 блоков вычитания и на входы первой группы 27 квадраторов. По сигналу с 5+m-го выхода РИ 47 на вход считывания входного регистра 22 величина Δх поступает через коммутатор 24 на вторые входы первой группы 29 блоков умножения и на первые входы второй группы 30 блоков вычитания. По сигналу с 2+3m-го выхода РИ 47 на входы считывания первой группы 38 регистров значения  с выходов элементов первого столбца этой группы через соответствующие элементы группы 39 коммутаторов и группы 31 элементов ИЛИ подаются на входы вычитаемого соответствующих элементов группы 26 блоков вычитания.

с выходов элементов первого столбца этой группы через соответствующие элементы группы 39 коммутаторов и группы 31 элементов ИЛИ подаются на входы вычитаемого соответствующих элементов группы 26 блоков вычитания.

Группы элементов 26, 28, 30 и блоки 33, 35 вычисляют числитель формулы (11). Группы элементов 27, 29 и блоки 32, 34 оценивают знаменатель формулы (11). Благодаря наличию ЭЗ 36 значения числителя и знаменателя поступают одновременно на входы делимого и делителя блока 37 деления, с выхода которого величина отклонения ε1 в соответствии с формулой (11), для первого варианта направляется на информационные входы каждого элемента второй группы 42 регистров. Однако, записано это значение будет только в первом элементе группы 42, так как сигнал на вход записи с 7+m-го выхода РИ 47 будет подаваться только на первый элемент этой группы.

В дальнейшем работа устройства проходит по уже указанной схеме, т.е., производятся вычисления при втором вариант α2 коэффициента стабильности. Работа устройства закончится тогда, когда будет произведен расчет при последнем m-ом варианте (αk=αm) и проанализированы результаты всех расчетов.

После записи в элементах второй группы 42 регистров всех m значений отклонений εk по сигналу с 1+5m-го выхода РИ 47 на входы считывания всех элементов этой группы с их выходов величины εk засылаются через соответствующие элементы группы 44 ЭЗ на информационные входы группы 43 блоков сравнения. Кроме того, значения εk подаются также на входы, с первого по m-ый, блока 41 оценки минимального значения, с выхода которого минимальное значение  отклонения направляется на пороговые входы всех элементов группы 43. Каждый элемент этой группы настроен следующим образом: если

отклонения направляется на пороговые входы всех элементов группы 43. Каждый элемент этой группы настроен следующим образом: если  , то на выходе элемента будет сигнал. В случае, когда

, то на выходе элемента будет сигнал. В случае, когда  , сигнал на выходе элемента будет отсутствовать. Следовательно, во второй группе 45 блоков индикации будет высвечиваться номер варианта вычислений, соответствующий минимальной ошибке. Поэтому, в качестве оптимального нужно выбирать тот вариант функции распределения сопротивляемости анализируемой СТС, который обеспечивает минимальную ошибку.

, сигнал на выходе элемента будет отсутствовать. Следовательно, во второй группе 45 блоков индикации будет высвечиваться номер варианта вычислений, соответствующий минимальной ошибке. Поэтому, в качестве оптимального нужно выбирать тот вариант функции распределения сопротивляемости анализируемой СТС, который обеспечивает минимальную ошибку.

В дальнейшем в основном будут работать вновь введенные блоки и элементы. С помощью элементов второй группы 48 вычитания третьей 49 и четвертой 50 групп блоков умножения и группы 51 накопительных сумматоров определяется величина  в соответствии с формулой (18), которая поступает на входы элементов восьмой группы ЭЗ.

в соответствии с формулой (18), которая поступает на входы элементов восьмой группы ЭЗ.

Далее осуществляется сравнение значений  , поступающих из первой группы (38) регистров, и величины εmin, направляемой из блока 41 оценки минимального значения, при участии второй группы 52 блоков сравнения, и второй группы 53 ЭЗ. Элементы группы 52 построены следующим образом: если

, поступающих из первой группы (38) регистров, и величины εmin, направляемой из блока 41 оценки минимального значения, при участии второй группы 52 блоков сравнения, и второй группы 53 ЭЗ. Элементы группы 52 построены следующим образом: если  , то на выходе элемента группы 52 будет сигнал. В противном случае (

, то на выходе элемента группы 52 будет сигнал. В противном случае ( ) сигнал будет отсутствовать согласно условию (21). Следовательно, если

) сигнал будет отсутствовать согласно условию (21). Следовательно, если  , то сигнал с выхода элемента группы 52 будет поступать на вход считывания соответствующего элемента третьей группы 56 регистров, откуда первое меньшее значение

, то сигнал с выхода элемента группы 52 будет поступать на вход считывания соответствующего элемента третьей группы 56 регистров, откуда первое меньшее значение  первой строки направляется на один из m входов первого элемента группы 54 элементов ИЛИ. С выхода этого элемента величина,

первой строки направляется на один из m входов первого элемента группы 54 элементов ИЛИ. С выхода этого элемента величина,  согласно условию (21) через первый элемент группы 55 ключей будет засылаться на входы первых элементов третьей 58 и пятой 62 ЭЗ, третьей группы квадраторов и на первый вход первого элемента группы сумматоров.

согласно условию (21) через первый элемент группы 55 ключей будет засылаться на входы первых элементов третьей 58 и пятой 62 ЭЗ, третьей группы квадраторов и на первый вход первого элемента группы сумматоров.

Каждый элемент группы 55 ключей настроен так, что он может пропускать только один первый сигнал, т.е. одну величину  . Таким образом для дальнейшей работы устройства поступают на уже указанные группы все остальные элементы

. Таким образом для дальнейшей работы устройства поступают на уже указанные группы все остальные элементы  , вплоть до

, вплоть до  .

.

По сигналу с 2+5m-го выхода РИ 47 на входы считывания третьей группы 59 входных регистров значения ηk направляются с выходов этой группы на входы четвертой группы 60 ЭЗ и на вторые группы 57 сумматоров С помощью третьей 58, четвертой 60 и 62 группы ЭЗ, группы 57 сумматоров, третьей группы 67 блоков вычитания и группы 69 блоков деления осуществляется вычисление градиента  в соответствии с формулой (24).

в соответствии с формулой (24).

Группы ЭЗ необходимы для обеспечения одновременного поступления сигналов на разные входы вычислительного блока.

Далее с помощью третьей группы 61 квадраторов, третьего 63 и четвертого 66 накопительных сумматоров, второго ЭЗ 64, второго блока 65 деления и пятой группы 70 блоков умножения определяется значение h1, по формуле (30). Эта величина использется для вычисления градиента  в соответствии с формулой (31). Это осуществляется с помощью шестой 72 и седьмой 73 группы ЭЗ, шестой группы 71 блоков умножения и четвертой группы 68 блоков вычитания. Значения

в соответствии с формулой (31). Это осуществляется с помощью шестой 72 и седьмой 73 группы ЭЗ, шестой группы 71 блоков умножения и четвертой группы 68 блоков вычитания. Значения  , выраженные через формулу (32) величинами П1, ……, Пm на информационные входы третьей группы 74 блоков сравнения, на пороговые входы которой подаются значения

, выраженные через формулу (32) величинами П1, ……, Пm на информационные входы третьей группы 74 блоков сравнения, на пороговые входы которой подаются значения  с выходов восьмой группы 80 ЭЗ. Каждый элемент группы 74 настроен следующим образом. Если

с выходов восьмой группы 80 ЭЗ. Каждый элемент группы 74 настроен следующим образом. Если  , то на выходе этого элемента будет сигнал. В противном случае, когда

, то на выходе этого элемента будет сигнал. В противном случае, когда  сигнал не появится. Следует иметь в виду, что вместо

сигнал не появится. Следует иметь в виду, что вместо  может фигурировать величина, близкая к 0. При наличии сигнала он поступит через девятую группу 81 ЭЗ, на один из входов четвертого элемента ИЛИ 75. Наличие группы 81 необходимо для того, чтобы предотвратить одновременное поступление через элемент 75 нескольких сигналов на информационный вход счетчика 76. Это достигается тем, что с выхода первого элемента третьей группы 74 блоков сравнения сигнал направляется напрямую, без задержек, на первый вход четвертого элемента ИЛИ 75. Начиная со второго элемента группы 74 сигнал будет поступать через соответствующий элемент группы 81 ЭЗ, в данной ситуации через второй. Вход к этому элементу показан условно. Все последующие элементы группы 81 настроены так, чтобы элемент с большим номером обеспечивал более длительную задержку.

может фигурировать величина, близкая к 0. При наличии сигнала он поступит через девятую группу 81 ЭЗ, на один из входов четвертого элемента ИЛИ 75. Наличие группы 81 необходимо для того, чтобы предотвратить одновременное поступление через элемент 75 нескольких сигналов на информационный вход счетчика 76. Это достигается тем, что с выхода первого элемента третьей группы 74 блоков сравнения сигнал направляется напрямую, без задержек, на первый вход четвертого элемента ИЛИ 75. Начиная со второго элемента группы 74 сигнал будет поступать через соответствующий элемент группы 81 ЭЗ, в данной ситуации через второй. Вход к этому элементу показан условно. Все последующие элементы группы 81 настроены так, чтобы элемент с большим номером обеспечивал более длительную задержку.

Таким образом обеспечивается последовательное поступление сигналов с выхода четвертого элемента ИЛИ 75 на информационный вход счетчика 76. При этом управляющий сигнал на вход запуска этого счетчика подается с 3+5m-го выхода РИ 47. После окончания работы счетчика 76 по управляющему сигналу блока 47 с его 4+5m-го выхода на вход считывания с выхода блока 76 результаты его подсчета засылаются на информационный вход второго блока 77 сравнения. На пороговый вход этого блока по сигналу на вход считывания второго входного регистра 78 с 4+5m-го выхода распределителя 47 импульсов направляется значение р.

Второй блок 77 сравнения настроен следующим образом. Если величина р будет равна результатам подсчета счетчиком 76, что свидетельствует о необходимом минимальном значении Пk, на выходе блока 77 появится сигнал, который приведет к загоранию на блоке 79 индикации надписи «конец работы». Когда величина р будет больше итогов подсчета, сигнала на выходе второго блока 77 сравнения не будет и устройство продолжает свою работу для выполнения следующей итерации. Порядок работы устройства представлен на циклограмме (фиг. 6).

Таким образом, технический результат заявленного изобретения достигается не за счет математического аппарата, а при помощи технических средств (блоков и элементов), упомянутых в описании работы устройства.

Описанное устройство позволяет существенно снизить количество итераций при решении задачи оптимального управления надежностью СТС методом ускоренного спуска а также обеспечить устойчивость вычислений при решения данной задачи за счет введения параметров регуляризации.

Промышленная применимость изобретения обосновывается тем, что оно может быть использовано в разных областях (отраслях) производства при получении информации для принятия решений при эксплуатации СТС с целью обеспечения заданных требований к их надежности.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ ДЛЯ ОБЕСПЕЧЕНИЯ УСТОЙЧИВОЙ РАБОТЫ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2011 |

|

RU2475828C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ТЕХНИЧЕСКОГО УРОВНЯ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2012 |

|

RU2475827C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФУНКЦИЙ ЦЕННОСТИ ЕДИНИЧНЫХ ОЦЕНОЧНЫХ ПОКАЗАТЕЛЕЙ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2010 |

|

RU2445687C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ M-МЕРНОГО ВЕКТОРА | 1995 |

|

RU2080650C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ПРЕДПОЧТИТЕЛЬНОГО УРОВНЯ УНИФИКАЦИИ ТЕХНИЧЕСКИХ СИСТЕМ | 2013 |

|

RU2519049C1 |

| ГЕНЕРАТОР СТОХАСТИЧЕСКИХ ОРТОГОНАЛЬНЫХ КОДОВ | 2016 |

|

RU2615322C1 |

| МАТРИЧНЫЙ СПЕЦПРОЦЕССОР | 1994 |

|

RU2079879C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СТОХАСТИЧЕСКИХ ОРТОГОНАЛЬНЫХ КОДОВ | 2021 |

|

RU2773107C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ФУНКЦИИ РАСПРЕДЕЛЕНИЯ СЛУЧАЙНЫХ ВЕЛИЧИН И ЕЕ ТОЛЕРАНТНЫХ ГРАНИЦ ПО МАЛЫМ ВЫБОРКАМ | 2014 |

|

RU2553120C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ КАЧЕСТВА ОБУЧЕНИЯ ОПЕРАТОРОВ АВТОМАТИЗИРОВАННЫХ РАБОЧИХ МЕСТ | 2020 |

|

RU2787329C2 |

Изобретение относится к вычислительной технике. Техническим результатом является снижение количества итераций при решении задачи оптимального управления надежностью методом ускоренного спуска, а также обеспечение устойчивости вычислений решения данной задачи. Предложено устройство, которое содержит коррелятор, анализатор случайного процесса, вычислительный блок, блок возведения в степень, блок транспонирования матриц, элементы ИЛИ, блок умножения, блок управления, элементы И, блок формирования матриц, блок памяти, блок обращения матриц, сумматоры, блоки сравнения, регистратор, группы входных регистров, входные регистры, коммутатор, группы блоков вычитания, группы квадраторов, группы блоков умножения, группы элементов ИЛИ, накопительные сумматоры, блоки извлечения квадратного корня, элементы задержки (ЭЗ), блоки деления, группы регистров, группу коммутаторов, группы блоков индикации, блок оценки минимального значения, группы блоков сравнения, группы ЭЗ, группу накопительных сумматоров, группу ключей, группу блоков деления, счетчик, блок индикации, генератор тактовых импульсов и распределитель импульсов. 6 ил., 2 табл.