Изобретение относится к вычислительной технике и может быть использовано для оценки качества обучения при работе с компьютером операторов автоматизированных рабочих мест (АРМ) с целью выработки рекомендаций по улучшению качества образовательного процесса, а также для сравнения различных методик и предлагаемых алгоритмов обучения.

Известно устройство для оценки качества обучения операторов при работе с компьютером АРМ, содержащее входные регистры, блоки умножения, блоки деления, элементы задержки (ЭЗ), сумматоры, выходной регистр, блок индикации, генератор тактовых импульсов и распределитель импульсов (РИ) Оценка качества обучения оператора при работе с компьютером АРМ, осуществляется следующим образом. Определяют качество Q, через значения для показателя R, величину Ri. Подставляя показатели R, и величину Ri в формулу в выражение определения качества, окончательно получают Q. Оценка качества обучения оператора при работе с компьютером АРМ, используя это устройство, осуществляется следующим образом. Качество Q этого процесса можно определить с помощью следующего соотношения:

где R - успешность отработки проверочных тестов АРМ;

Т - продолжительность обучения.

Значения для показателя R вычисляются по следующей формуле;

где Ri - успешность отработки i-го проверочного теста АРМ;

n - количество проверочных тестов.

Величину Ri можно определить по следующей зависимости:

где Si - весовой коэффициент i-го проверочного теста (заданий)

Ci - количество успешных испытаний в i-м проверочном тесте;

mi - общее число испытаний в i-м проверочном тесте (задании).

Подставляя формулы (2) и (3) в выражение (1), окончательно можно получить:

[Патент РФ №2330323, М. Кл. G06F 17/18, 2008(прототип)].

Недостатком этого устройства является то, что общее время Т продолжительности обучения не выделяет теоретический ТТ и практический ТП этапы обучения как две основные составляющие компоненты от всего процесса обучения при работе с компьютером, т.е.

Т=ТТ+ТП

Кроме того для обеспечения заданного как априори определенного (желаемого теоретического) уровня обучения работе с компьютером, необходимо давать оценку этому процессу на различных этапах обучения.

Технической задачей изобретения является получение более объективной информации на различных этапах обучения работе с компьютером в системе АРМ за счет сравнительного анализа теоретического и практического этапов данного обучения.

Оценку осуществляют следующим образом.

Оценивают желаемое качество QT теоретического этапа процесса обучения в контуре АРМ по формуле;

где RT - успешность обработки проверочных тестов на этапе теоретического обучения.

Величина RТ вычисляется по формуле:

где RTi - успешность обработки i-го проверочного теста на этапе теоретического обучения.

Величину RTi оценивают по зависимости;

где STi - весовой коэффициент i-го проверочного теста на этапе теоретического обучения

где CTi - количество успешных испытаний в i-м проверочном тесте на этапе теоретического обучения;

mTi - общее число испытаний в i-м проверочном тесте на этапе теоретического обучения;

Подставляя формулы (6) и (7) в выражение (5), окончательно получают окончательное выражение:

Далее проводят этап практического обучения работе с компьютером и имея данные по всему периоду обучения (для двух этапов) определяют значение Q качества этого процесса, используя показатели R, и величину Ri. Вклад QП этапа практического обучения оценивают через коэффициент вклада К по формуле (с использованием теоретического этапа обучения):

При этом К<1,0., чем больше К, тем меньше вклад QП. Тогда этап практического обучения мало влияет на Q. Если К=0,5, то теория и практика вносят одинаковый вклад в Q.

Сравнивая значение вкладов теоретического и практического этапов обучения работе с компьютером АРМ выбирают необходимую методику для реализации этого информационного процесса.

Поставленная цель достигается тем, что устройство для оценки качества обучения работе с компьютером АРМ, содержащее первую, вторую и третью группы входных регистров, входной регистр, группу блоков умножения, группу блоков деления, группу элементов задержки (ЭЗ), первый блок деления, первый входной регистр, первый блок индикации, генератор тактовых импульсов и распределитель импульсов (РИ?), тактовый вход которого соединен с выходом генератора тактовых импульсов, первый выход распределителя импульсов - с входами записи первой, второй и третьей групп входных регистров и входного регистра, второй выход - с входами считывания второй и третьей групп входных регистров, третий выход - с входами считывания первой группы входных регистров, четвертый выход - с входом считывания входного регистра, пятый и шестой выходы - с входами соответственно записи и считывания первого выходного регистра, выход каждого элемента первой группы входных регистров подключен к первому входу каждого элемента группы блоков умножения, состоящей из n элементов, выходы каждого элемента второй и третьей группы входных регистров соединены с входами соответственно делимого и делителя каждого элемента группы блоков деления, состоящей из n элементов, вход каждого из которых подключен ко второму входу каждого элемента группы блоков умножения, выходы первого и второго элементов которого соединены соответственно с первым и вторым входами первого элемента группы сумматоров, состоящей из (n-1) элементов, а выходы остальных элементов группы блоков умножения, начиная с третьего подключены к входам соответствующих элементов группы ЭЗ, состоящей из (n-2) элементов, выходы каждого из которых соединены с первыми входами соответствующих элементов группы сумматоров, начиная со второго элемента, выходы каждого из которых, включая первый элемент, и кроме последнего элемента, подключены ко вторым входам последующих элементов группы сумматоров, а выход последнего элемента, т.е. (n-1)-го сумматора, соединен с входом делимого блока деления, вход делителя которого подключен к выходу входного регистра, выход первого входного регистра соединен с входом первого блока индикаций, отличающееся тем, что оно дополнительно содержит первую, вторую и третью группы элементов ИЛИ, элемент ИЛИ, коммутатор, элементы задержки, второй выходной регистр, второй блок деления, второй и третий блоки индикации, информационные входы первой группы элементов ИЛИ, состоящей из n элементов, являются входом задания исходной информации, на первые входы которых поступают значения STi, характеризующие весовые коэффициенты i-го проверочного теста на этапе теоретического обучения, а на вторые входы - величина Si, характеризующие весовые коэффициенты i-го проверочного теста на двух этапах обучения, информационные входы второй группы элементов ИЛИ, состоящей из n элементов, являются входом задания исходной информации, на первые входы которых поступают значения Ci, характеризующие количество успешных испытаний в i-м проверочном тесте на этапе теоретического обучения, а на вторые входы - величины Ci, характеризующие количество успешных испытаний в i-м проверочном тесте на двух этапах обучения, информационные входы третьей группы элементов ИЛИ, состоящей из n элементов, являются входом задания исходной информации, на первые входы которых поступают значения mTi, характеризующие общее число испытаний в i-м проверочном тесте на этапе теоретического обучения, а на вторые входы - величины mi, характеризующие общее число испытаний в i-м проверочном тесте на двух этапах обучения, информационные входы элемента ИЛИ являются входами задания исходной информации, на первый вход которого поступает значение Тт, характеризующее длительность теоретического этапа обучения, а на второй вход величина Т, характеризующая общую длительность процесса обучения, выходы каждого элемента первой, второй и третьей групп элементов ИЛИ соединены с информационными входами соответствующих элементов первой, второй и третьей групп входных регистров, каждая из которых состоит из n элементов, выход элементов ИЛИ подключен к информационному входу входного регистра, выход первого блока деления соединен с информационным выходом коммутатора, первый и второй выходы которого подключены к информационным входам соответственно первого и второго выходных регистров, а управляющий вход - к выходу ЭЗ, вход которого соединен с пятым выходом РИ, выход второго выходного регистра подключен к входу второго блока индикации и к входу делителя второго блока деления, вход делимого которого соединен с выходом первого выходного регистра, в выход - с входом третьего. Блок индикации, входы записи и считывания второго выходного регистра подключены соответственно к пятому и и шестому выходам РИ.

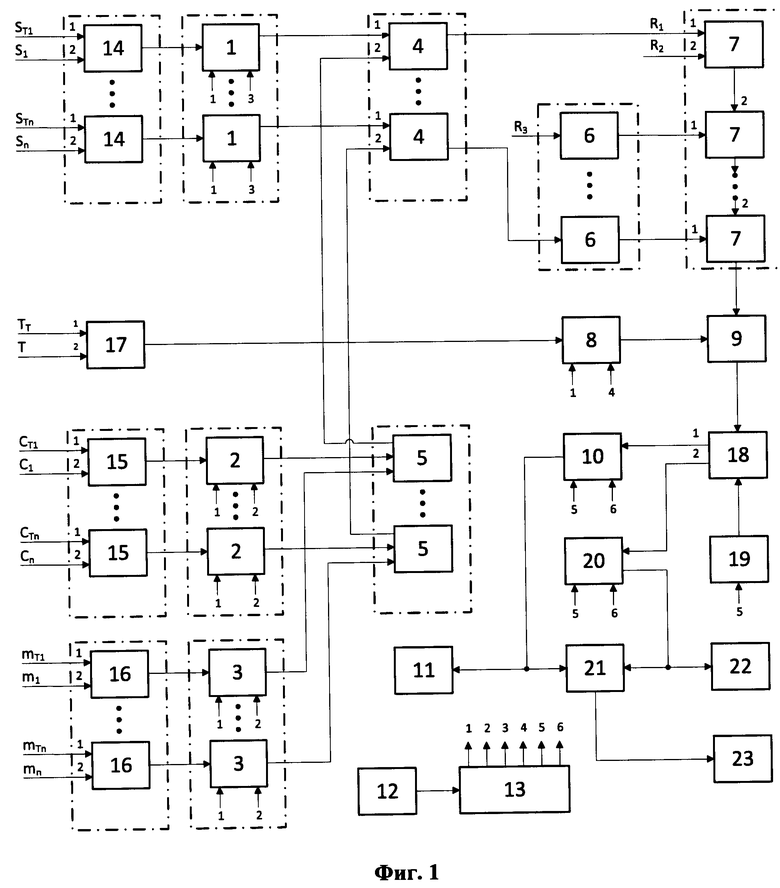

Сущность изобретения поясняется чертежами, где на фиг. 1 представлена функциональная схема устройства для оценки качества обучения работе с компьютером АРМ (для ликвидации громоздкости связи между распределителем импульсов и управляющими входами соответствующих блоков показаны не полностью, а обозначены путем нумерации входов и выходов), на фиг. 2 изображена циклограмма работы заявленного устройства (по оси ординат обозначены номера выходов распределителя импульсов, а по оси абсцисс - число тактов), причем длительность различных вычислительных операций (сложение - один такт, умножение - восемь тактов, деление шестнадцать тактов) - в легенде фиг. 2 (для возможности исполнения циклограммы принято n=10, эта величина может принимать произвольное значение).

Устройство для оценки качества обучения работе с компьютером АРМ (фиг. 1) содержит первую -1, вторую -2 и третью -3 группы входных регистров, каждая из которых состоит из n элементов, группу -4 блоков умножения, состоящую из n элементов, группу -5 блоков деления, состоящую из n элементов, группу элементов задержки (ЭЗ)-6, состоящую из (n-2) элементов, группу сумматоров -7 состоящую из (n-1)элементов, входной регистр -8, первый блок деления -9, первый выходной регистр -10, первый блок индикации -11, генератор тактовых импульсов -12, распределитель импульсов (РИ) -13, первую -14, вторую -75 и третью -16 группы элементов ИЛИ, элемента ИЛИ -17, коммутатор -18, элемент задержки -19, второй выходной регистр -20,второй блок деления -21, второй -22 и третий -23 блоки индикации.

Устройство для оценки качества обучения работе с компьютером работает следующим образом.

Устройство для оценки качества обучения работе с компьютером АРМ, содержащее первую -1, вторую -2 и третью -3 группы входных регистров, входной регистр-8, группу блоков умножения-4, группу блоков деления-5, группу элементов задержки (ЭЗ)-6, первый блок деления-9, первый выходной регистр-10, первый блок индикации-11, генератор тактовых импульсов-12 и распределитель импульсов-13. При этом его тактовый выход соединен с входом генератора тактовых импульсов -12. Первый выход распределителя импульсов-13 соединен с входами записи первой-1, второй-2 и третьей-3 групп входных регистров и входного регистра-'8, второй выход соединен с входами считывания второй-2 и третьей-3 групп входных регистров. Третий выход соединен с входами считывания первой группы входных регистров-1. Четвертый выход соединен с входом считывания входного регистра-8. Пятый и шестой выходы соединен с входами соответственно записи и считывания первого выходного регистра-10. Выход каждого элемента первой группы входных регистров-1 подключен к первому входу каждого элемента группы блоков умножения-4, состоящей из n элементов. Выходы каждого элемента второй-2 и третьей-3 группы входных регистров соединены с входами соответственно делимого и делителя каждого элемента группы блоков деления-5, состоящей из n элементов, выход каждого из которых подключен ко второму входу каждого элемента группы блоков умножения-4, выходы первого и второго элементов которого соединены соответственно с первым и вторым входами первого элемента группы сумматоров-7, состоящей из (n-1) элементов, а выходы остальных элементов группы блоков умножения-4, начиная с третьего подключены к входам соответствующих элементов группы ЭЗ-6, состоящей из (n-2) элементов, выходы каждого из которых соединены с первыми входами соответствующих элементов группы сумматоров -7, начиная со второго элемента, выходы каждого из которых, включая первый элемент, и кроме последнего элемента, подключены ко вторым входам последующих элементов группы сумматоров -7, а выход последнего элемента, т.е. (n-1)-го сумматора -7, соединен с входом делимого блока деления-9, выход делителя которого подключен к входу выходного регистра-10, выход первого-10 выходного регистра соединен с входом первого блока индикаций-11, отличающееся тем, что оно дополнительно содержит первую-14, вторую-15 и третью-16 группы элементов ИЛИ, элемент ИЛИ-17, коммутатор-18, элементы задержки-19, второй выходной регистр-20, второй блок деления-21, второй-22 и третий-23 блоки индикации, информационные входы первой группы элементов ИЛИ-14, состоящей из n элементов, являются входом задания исходной информации, на первые входы которых поступают значения STi, характеризующие весовые коэффициенты i-го проверочного теста на этапе теоретического обучения, а на вторые входы - величина Sj, характеризующие весовые коэффициенты i-го проверочного теста на двух этапах обучения, информационные входы второй группы элементов ИЛИ-15, состоящей из n элементов, являются входом задания исходной информации, на первые входы которых поступают значения Ci, характеризующие количество успешных испытаний в i-м проверочном тесте на этапе теоретического обучения, а на вторые входы - величины Ci, характеризующие количество успешных испытаний в i-м проверочном тесте на двух этапах обучения, информационные входы третьей группы элементов ИЛИ-16, состоящей из n элементов, являются входом задания исходной информации, на первые входы которых поступают значения mTi, характеризующие общее число испытаний в i-м проверочном тесте на этапе теоретического обучения, а на вторые входы - величины mi, характеризующие общее число испытаний в i-м проверочном тесте на двух этапах обучения, информационные входы элемента ИЛИ-17 являются входами задания исходной информации, на первый вход которого поступает значение ТТ, характеризующее длительность теоретического этапа обучения, а на второй вход величина T, характеризующая общую длительность процесса обучения, выходы каждого элемента первой - 14, второй - 15 и третьей- 16 групп элементов ИЛИ соединены с информационными входами соответствующих элементов первой-1, второй-2 и третьей-3 групп входных регистров, каждая из которых состоит из n элементов, выход элементов ИЛИ-17 подключен к информационному входу входного регистра-8, выход первого блока деления-9 соединен с информационным входом коммутатора-18, первый и второй выходы которого подключены к информационным входам соответственно первого-10 и второго - 20 выходных регистров, а управляющий вход - к выходу ЭЗ - 19, вход которого соединен с пятым выходом РИ - 13, выход второго выходного регистра - 20 подключен к входу второго блока индикации - 22 и к входу делителя второго блока деления - 21, вход делимого которого соединен с выходом первого выходного регистра - 10, а выход - с входом третьего- 23 блока индикации, входы записи и считывания второго выходного регистра-20 подключены соответственно к пятому и шестому выходам РИ - 13.

Оценивается качество QT теоретического этапа процесса обучения. Для этого на первые входы первой - 14, второй - 15 и третьей - 16 групп элементов ИЛИ (фиг. 1) засылаются соответственно величины, STi, CTi, mTi, которые направляются на информационные входы соответственно первой-1, второй-2 и третьей - 3 групп входных регистров. На первый вход элемента ИЛИ - 17 подается значение Тт, которое направляется на информационный вход входного регистра - 8. При этом управляющий сигнал на входы записи всех этих регистров направляется с первого выхода РИ - 13, темп работы которого задается генератором тактовых импульсов -12.

По сигналу со второго входа РИ - 13 на входы считывания каждого элемента второй - 2 и третьей - 3 групп входных регистров значения СTi и mTi подаются на входы соответственно делимого и делителя группы - 5 блоков деления С входов каждого элемента этой группы величина CTi/mTi направляется на второй вход каждого элемента группы - 4 блоков умножения. По сигналу с третьего входа РИ - 13 на входы считывания каждого элемента первой группы - 1 входных регистров значение STi подается на первый вход каждого элемента группы - 4 блоков умножения, в которой определяется величина RTi в соответствии с формулой (7).

С входов первых двух элементов группы-4 значения RT1 и RT2 подаются соответственно на первый и второй входы первого сумматора группы сумматоров - 7. С входов остальных элементов группы блоков умножения -4, начиная с третьего, величины RTi направляются на соответствующие элементы группы элементов задержки (ЭЗ) -6 на первые входы соответствующих элементов группы сумматоров -7, начиная со второго. С выхода последнего сумматора группы -7 значение RT определенная по формуле (6) засылается на вход делимого первого блока деления -9. На вход делителя этого блока с четвертого выхода импульсов (РИ) -13 с выхода входного регистра -8 подается величина Тт.

С выхода первого блока деления -9 значение QT качества теоретического этапа процесса обучения работе с компьютером АРМ, вычисленное по формуле (5), направляется на информационный вход коммутатора -18, который настроен следующим образом: если сигнал на управляющем входе отсутствует, то информация появляется на его первом выходе, а в случае наличия управляющего сигнала информация будет исходить со второго выхода коммутатора -18. Поскольку управляющий сигнал у этого блока отсутствует, значение QT с его первого входа подается на информационный вход первого выходного регистра -10. Управляющий сигнал на запись подается при этом на вход записи регистра -10 с пятого выхода распределителя импульсов -13.

Далее осуществляется оценка величины Q качества обучения работе с компьютером с помощью формул (2), (3) и (4). Исходная информация для этого определяется после проведения двух этапов обучения: теоретического и практического. Эта информация в виде величин Si, Ci, mi засылается на вторые входы соответственно первой -14, второй -15 и третьей -16 групп элементов ИЛИ. В дальнейшем работа устройства осуществляется по уже описанной схеме. Единственное отличие заключается в том, что значение Q будет поступать со второго входа коммутатора -18 на информационный вход второго выходного регистра -20, так как на управляющем входе блока -18 появляется сигнал, который поступает с выхода ЭЗ -19. Блок -19 позволяет осуществить подачу управляющего сигнала с пятого выхода РИ -13 при оценке QT. Повторная подача сигнала с пятого выхода РИ -13 обеспечивает запись величины Q в блоке -20.

По сигналу с шестого выхода РИ -13 на входе считывания первого -10 и второго-20 выходных регистров, значения QT и Q засылаются на входы соответственно делимого и делителя второго блока деления -21. Кроме того, эти значения подаются на входы соответственно первого -11 и второго -22 блоков индикации для наглядного отображения. Блок -21 осуществляет оценку вклада QП этапа практического обучения K в соответствии с формулой (9). Величина K засылается на вход третьего блока индикации 23 для наглядного отображения. Порядок функционирования блоков устройства представлен на циклограмме его работы (фиг. 2).

В дальнейшем работа устройства может быть повторена по уже описанной схеме с использованием других исходных данных (применение другой методики обучения) с последующим сравнением новых значений QT и Q.

Таким образом, технический результат достигается не за счет математического аппарата, а за счет технических средств (блоков и элементов), упомянутых в процессе описания работы устройства, осуществляющего ускорение объективного выбора методики обучения работе с компьютером за счет сравнения качества результатов преподавания.

Промышленная применимость изобретения обосновывается тем, что оно может быть использовано в разных областях (отраслях) при расчетах, связанных с оценкой качества обучения работе с компьютером АРМ, для выбора лучшей методики преподавания (обучения).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ КАЧЕСТВА ОБУЧЕНИЯ РАБОТЕ С КОМПЬЮТЕРОМ | 2007 |

|

RU2330323C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ФУНКЦИИ РАСПРЕДЕЛЕНИЯ СЛУЧАЙНЫХ ВЕЛИЧИН И ЕЕ ТОЛЕРАНТНЫХ ГРАНИЦ ПО МАЛЫМ ВЫБОРКАМ | 2014 |

|

RU2553120C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ОЦЕНКИ ФАЗОВОЙ НАПРЯЖЕННОСТИ РЕСПОНДЕНТА | 2012 |

|

RU2492520C1 |

| УСТРОЙСТВО ДЛЯ ТЕХНИКО-ЭКОНОМИЧЕСКОЙ ОЦЕНКИ ВЫПОЛНЕНИЯ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИХ И ОПЫТНО-КОНСТРУКТОРСКИХ РАБОТ | 2011 |

|

RU2470365C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ВЫПОЛНЕНИЯ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИХ И ОПЫТНО-КОНСТРУКТОРСКИХ РАБОТ | 2009 |

|

RU2410750C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ВЫПОЛНЕНИЯ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИХ И ОПЫТНО-КОНСТРУКТОРСКИХ РАБОТ | 2011 |

|

RU2452018C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ ДЛЯ ОБЕСПЕЧЕНИЯ УСТОЙЧИВОЙ РАБОТЫ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2011 |

|

RU2475828C1 |

| Устройство формирования оптимальных управляющих воздействий для обеспечения устойчивой работы сложных технических систем | 2017 |

|

RU2674281C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФУНКЦИЙ ЦЕННОСТИ ЕДИНИЧНЫХ ОЦЕНОЧНЫХ ПОКАЗАТЕЛЕЙ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2010 |

|

RU2445687C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ РЕЗУЛЬТАТИВНОСТИ СИСТЕМЫ МЕНЕДЖМЕНТА КАЧЕСТВА ПРОДУКЦИИ НАУЧНО-ТЕХНИЧЕСКОЙ ОРГАНИЗАЦИИ | 2015 |

|

RU2611964C2 |

Настоящее техническое решение относится к области вычислительной техники. Технический результат заключается в повышении точности обработки информации. Технический результат достигается за счёт того, что устройство содержит первую - 1, вторую - 2 и третью - 3 группы входных регистров, каждая из которых состоит из n элементов, группу - 4 блоков умножения, состоящую из n элементов, группу - 5 блоков деления, состоящую из n элементов, группу элементов задержки (ЭЗ) - 6, состоящую из (n-2) элементов, группу сумматоров - 7 состоящую из (n-1) элементов, входной регистр - 8, первый блок деления - 9, первый выходной регистр - 10, первый блок индикации - 11, генератор тактовых импульсов - 12, распределитель импульсов (РИ) - 13, первую - 14, вторую - 15 и третью - 16 группы элементов ИЛИ, элемента ИЛИ - 17, коммутатор - 18, элемент задержки - 19, второй выходной регистр - 20, второй блок деления - 21, второй - 22 и третий - 23 блоки индикации. 2 ил.

Устройство для оценки качества обучения операторов при работе с компьютером АРМ, содержащее входные регистры, блоки умножения, блоки деления, элементы задержки (ЭЗ), сумматоры, выходной регистр, блок индикации, генератор тактовых импульсов и распределитель импульсов (РИ), отличающееся тем, что содержит первую, вторую и третью группы входных регистров, входной регистр, группу блоков умножения, группу блоков деления, группу элементов задержки (ЭЗ), группу сумматоров, первый блок деления, первый выходной регистр, первый блок индикации, генератор тактовых импульсов и распределитель импульсов (РИ), тактовый вход которого соединен с выходом генератора тактовых импульсов, первый выход распределителя импульсов - с входами записи первой, второй и третьей групп входных регистров и входного регистра, второй выход - с входами считывания второй и третьей групп входных регистров, третий выход - с входами считывания первой группы входных регистров, четвертый выход - с входом считывания входного регистра, пятый и шестой выходы - с входами соответственно записи и считывания первого выходного регистра, выход каждого элемента первой группы входных регистров подключен к первому входу каждого элемента группы блоков умножения, состоящей из n элементов, выходы каждого элемента второй и третьей группы входных регистров соединены с входами соответственно делимого и делителя каждого элемента группы блоков деления, состоящей из n элементов, выход каждого из которых подключен ко второму входу каждого элемента группы блоков умножения, выходы первого и второго элементов которого соединены соответственно с первым и вторым входами первого элемента группы сумматоров, состоящей из (n-1) элементов, а выходы остальных элементов группы блоков умножения, начиная с третьего, подключены к входам соответствующих элементов группы ЭЗ, состоящей из (n-2) элементов, выходы каждого из которых соединены с первыми входами соответствующих элементов группы сумматоров, начиная со второго элемента, выходы каждого из которых, включая первый элемент, и кроме последнего элемента, подключены ко вторым входам последующих элементов группы сумматоров, а выход последнего элемента (n-1)-го сумматора соединен с входом делимого блока деления, вход делителя которого подключен к выходу входного регистра, выход первого входного регистра соединен с входом первого блока индикации, отличающееся тем, что оно дополнительно содержит первую, вторую и третью группы элементов ИЛИ, элемент ИЛИ, коммутатор, элементы задержки, второй выходной регистр, второй блок деления, второй и третий блоки индикации, информационные входы первой группы элементов ИЛИ, состоящей из n элементов, являются входом задания исходной информации, на первые входы которых поступают значения STi, характеризующие весовые коэффициенты i-го проверочного теста на этапе теоретического обучения, а на вторые входы - величины Si, характеризующие весовые коэффициенты i-го проверочного теста на двух этапах обучения, информационные входы второй группы элементов ИЛИ, состоящей из n элементов, являются входом задания исходной информации, на первые входы которых поступают значения CTi, характеризующие количество успешных испытаний в i-м проверочном тесте на этапе теоретического обучения, а на вторые входы - величины Ci, характеризующие количество успешных испытаний в i-м проверочном тесте на двух этапах обучения, информационные входы третьей группы элементов ИЛИ, состоящей из n элементов, являются входом задания исходной информации, на первые входы которых поступают значения mTi, характеризующие общее число испытаний в i-м проверочном тесте на этапе теоретического обучения, а на вторые входы - величины mi, характеризующие общее число испытаний в i-м проверочном тесте на двух этапах обучения, информационные входы элемента ИЛИ являются входами задания исходной информации, на первый вход которого поступает значение ТТ, характеризующее длительность теоретического этапа обучения, а на второй вход величина Т, характеризующая общую длительность процесса обучения, выходы каждого элемента первой, второй и третьей групп элементов ИЛИ соединены с информационными входами соответствующих элементов первой, второй и третьей групп входных регистров, каждая из которых состоит из n элементов, выход элемента ИЛИ подключен к информационному входу входного регистра, выход первого блока деления соединен с информационным выходом коммутатора, первый и второй выходы которого подключены к информационным входам соответственно первого и второго выходных регистров, а управляющий вход - к выходу ЭЗ, вход которого соединен с пятым выходом РИ, выход второго выходного регистра подключен к входу второго блока индикации и к входу делителя второго блока деления, вход делимого которого соединен с выходом первого выходного регистра, в выход - с входом третьего блока индикации, входы записи и считывания второго выходного регистра подключены соответственно к пятому и шестому выходам РИ.

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ КАЧЕСТВА ОБУЧЕНИЯ РАБОТЕ С КОМПЬЮТЕРОМ | 2007 |

|

RU2330323C1 |

| УСТРОЙСТВО ДЛЯ КОЛИЧЕСТВЕННОЙ ОЦЕНКИ КАЧЕСТВЕННОГО ПОКАЗАТЕЛЯ | 2013 |

|

RU2520390C1 |

| US 005552732 A, 03.09.1996 | |||

| Ковш карусельного вакуум-фильтра | 1976 |

|

SU632378A1 |

| KR 20050071691 A, 07.07.2005. | |||

Авторы

Даты

2023-01-09—Публикация

2020-10-05—Подача