Область техники

Технология, которая раскрывается в этом описании, относится к полупроводниковому модулю.

Уровень техники

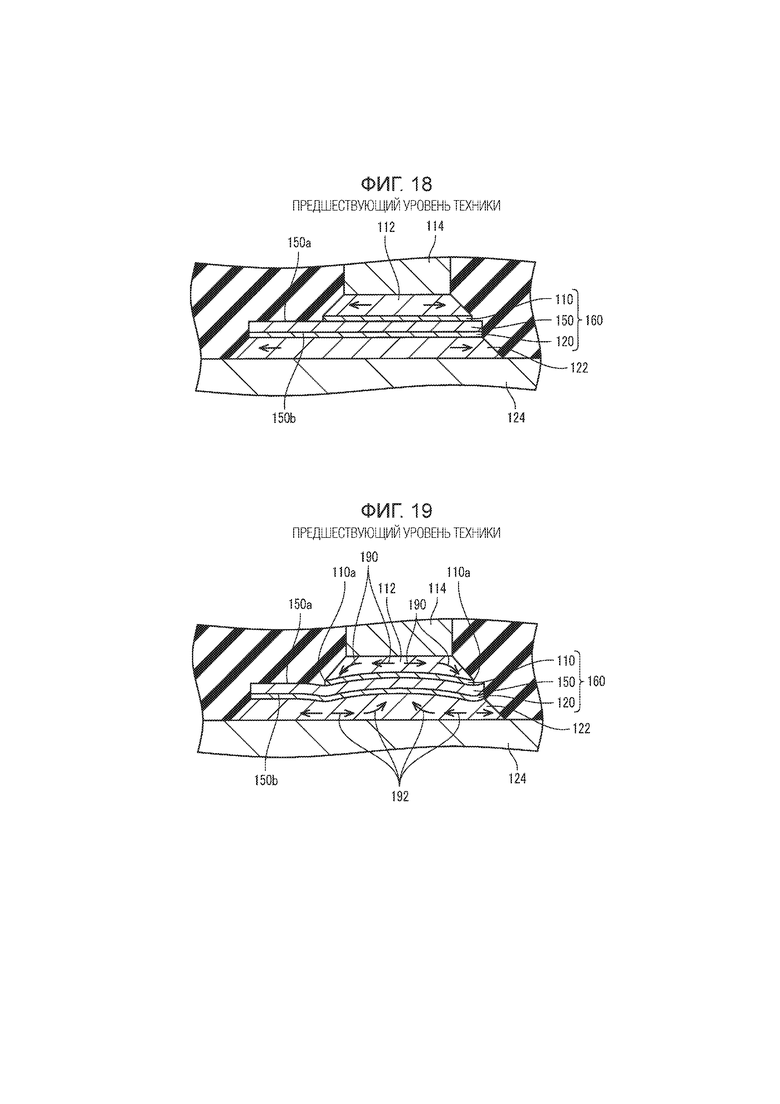

Японская нерассмотренная публикация патентной заявки № 2016-046497 (JP 2016-046497 A) раскрывает полупроводниковый модуль, в котором проводники соединяются припоем с обеими поверхностями полупроводниковой интегральной схемы. Фиг. 18 представляет собой частичный укрупненный вид полупроводникового модуля, раскрытого в JP 2016-046497 A. Как иллюстрировано на фиг. 18, полупроводниковая интегральная схема 160 имеет полупроводниковую подложку 150, первый электрод 110 в контакте с одной поверхностью 150a полупроводниковой подложки 150 и второй электрод 120 в контакте с другой поверхностью 150b полупроводниковой подложки 150. Первый электрод 110 соединяется с первым проводником 114 слоем 112 припоя, а второй электрод 120 соединяется со вторым проводником 124 слоем 122 припоя. Каждый из первого проводника 114 и второго проводника 124 функционирует как теплорассеивающий элемент, высвобождающий тепло из полупроводниковой подложки 150.

Сущность изобретения

Электрод (такой как сигнальный электрод), отличный от первого электрода 110, располагается на поверхности 150a полупроводниковой подложки 150, и, таким образом, первый электрод 110 меньше по размеру, чем второй электрод 120. Каждый из первого проводника 114, второго проводника 124 и полупроводниковой подложки 150 термически расширяется, когда полупроводниковая подложка 150 формирует тепло. В это время величина расширения первого проводника 114 и величина расширения второго проводника 124 превышают величину расширения полупроводниковой подложки 150, поскольку коэффициент линейного расширения первого проводника 114 и коэффициент линейного расширения второго проводника 124 больше коэффициента линейного расширения полупроводниковой подложки 150. Слой 112 припоя тянется к внешней периферийной стороне вследствие теплового расширения первого проводника 114. Слой 122 припоя тянется к внешней периферийной стороне вследствие теплового расширения второго проводника 124. Механическое напряжение многократно прикладывается к слоям 112, 122 припоя, когда полупроводниковая подложка 150 многократно формирует тепло. Затем припой перемещается к внешней периферийной стороне в слое 112 припоя, и припой перемещается к внешней периферийной стороне в слое 122 припоя, как указано стрелками на фиг. 18, вследствие явления сползания припоя. Поскольку явление сползания припоя продолжается, припой, перемещающийся к внешней периферийной стороне в слое 112 припоя, оказывает давление на полупроводниковую подложку 150, направленное вниз, рядом с внешним периферийным краем 110a первого электрода 110, как указано стрелками 190 на фиг. 19. В результате, полупроводниковая подложка 150 деформируется вниз на внешнем периферийном крае 110a первого электрода 110, как иллюстрировано на фиг. 19. В результате оказания давления полупроводниковой подложкой 150, которая деформируется вниз, припой в слое 122 припоя перемещается из находящейся под давлением части по направлению к окружению. В результате, некоторая часть припоя в слое 122 припоя перемещается по направлению к нижнему участку среднего участка первого электрода 110, как указано стрелками 192 на фиг. 19. Соответственно, слой 122 припоя оказывает давление на полупроводниковую подложку 150, направленное вверх, в позиции среднего участка первого электрода 110, и полупроводниковая подложка 150 деформируется вверх. Деградация полупроводниковой подложки 150 получается в результате деформации полупроводниковой подложки 150, иллюстрированной на фиг. 19. Тогда надежность полупроводникового модуля снижается. Хотя полупроводниковая интегральная схема 160 покрыта изоляционной смолой на фиг. 18 и 19, было подтверждено, что деформация как на фиг. 19 возникает даже в случае, когда полупроводниковая интегральная схема не покрыта изоляционной смолой. Следовательно, эта спецификация предлагает технологию для пресечения деформации полупроводниковой подложки, свойственной явлению сползания припоя в полупроводниковом модуле.

Аспект изобретения относится к полупроводниковому модулю, включающему в себя полупроводниковую подложку, первый электрод в контакте с первой поверхностью полупроводниковой подложки в зоне за исключением внешней периферийной области первой поверхности полупроводниковой подложки, второй электрод в контакте со второй поверхностью полупроводниковой подложки, первая поверхность и вторая поверхность являются противоположными поверхностями полупроводниковой подложки, первый проводник, соединенный с первым электродом через первый слой припоя, и второй проводник, соединенный со вторым электродом через второй слой припоя. Второй электрод перекрывает весь первый электрод и шире первого электрода, если смотреть в направлении толщины полупроводниковой подложки. Углубленный участок, расположенный вдоль внешнего периферийного края первого электрода, располагается в соединительной поверхности второго проводника в контакте со вторым слоем припоя, чтобы перекрывать внешний периферийный край первого электрода, если смотреть на полупроводниковую подложку в направлении толщины.

В полупроводниковом модуле углубленный участок, расположенный вдоль внешнего периферийного края первого электрода, располагается в соединительной поверхности второго проводника в контакте со вторым слоем припоя, чтобы перекрывать внешний периферийный край первого электрода, если смотреть на полупроводниковую подложку в направлении толщины. Поскольку второй слой припоя в углубленном участке (т.е., второй слой припоя под внешним периферийным краем первого электрода) является толстым, второй слой припоя в углубленном участке имеет относительно высокую эластичность. Соответственно, даже когда на полупроводниковую подложку оказывается направленное вниз давление под внешним периферийным краем первого электрода вследствие явления сползания первого слоя припоя, явление сползания едва ли должно возникать во втором слое припоя в углубленном участке. Соответственно, давление на полупроводниковую подложку, свойственное явлению сползания второго слоя припоя, едва ли должно создаваться, и деформация полупроводниковой подложки может быть предотвращена. Следовательно, в полупроводниковом модуле согласно аспекту изобретения, деградация со временем полупроводниковой подложки едва ли должна возникать.

Краткое описание чертежей

Признаки, преимущества и техническое и промышленное значение примерных вариантов осуществления изобретения будут описаны ниже со ссылкой на сопровождающие чертежи, на которых аналогичные номера обозначают аналогичные элементы, и на которых:

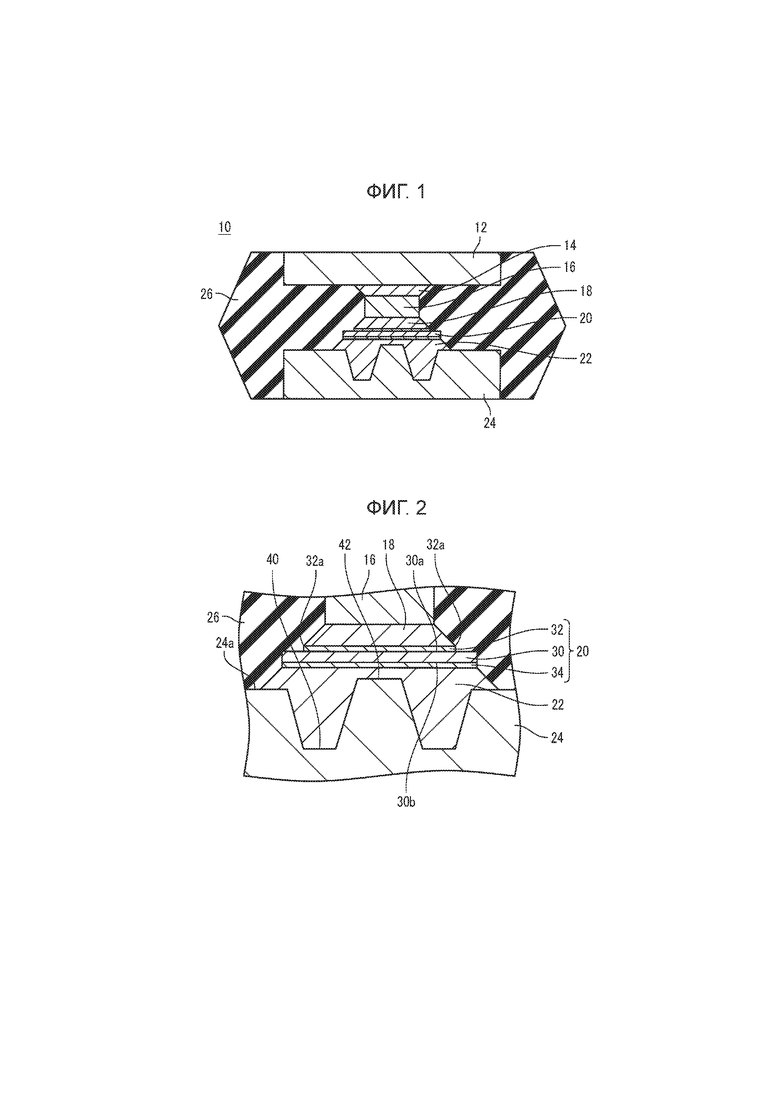

Фиг. 1 - вид в разрезе полупроводникового модуля;

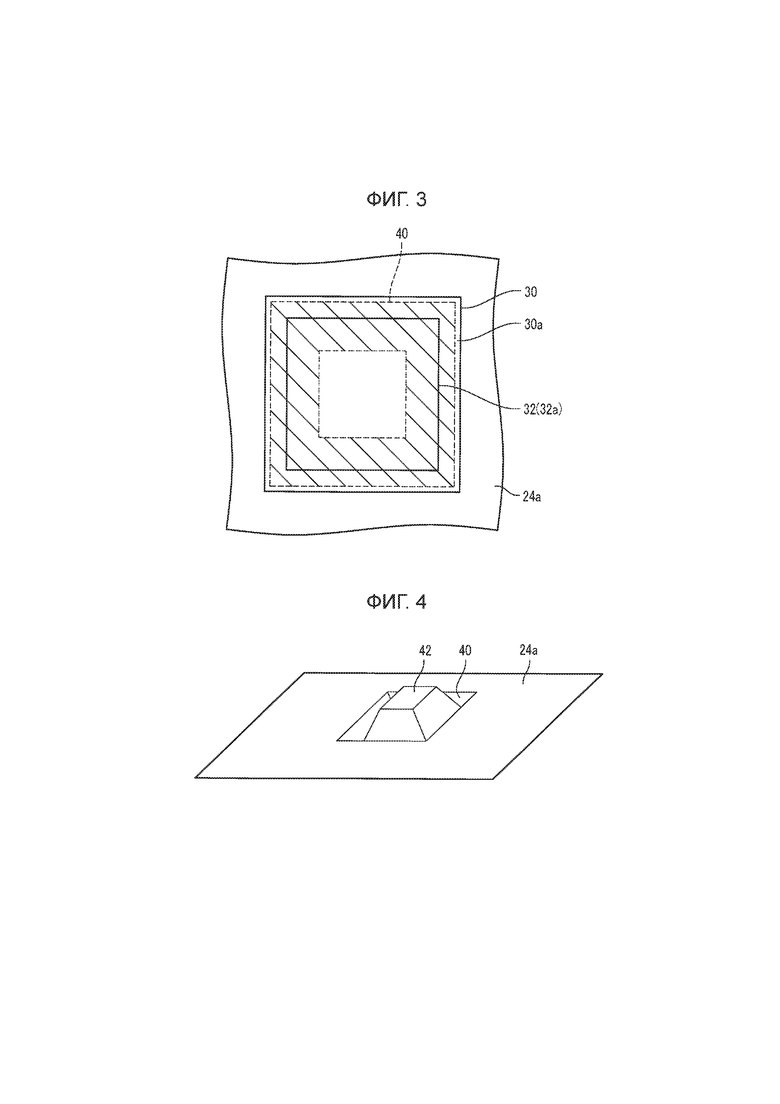

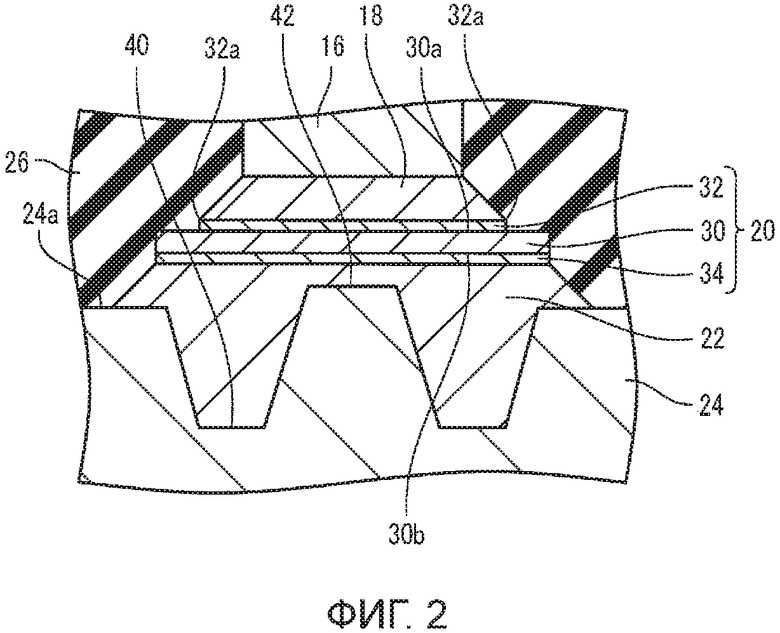

Фиг. 2 - укрупненный вид в разрезе полупроводниковой интегральной схемы и ее окружения;

Фиг. 3 - вид сверху, показывающий полупроводниковую интегральную схему сверху;

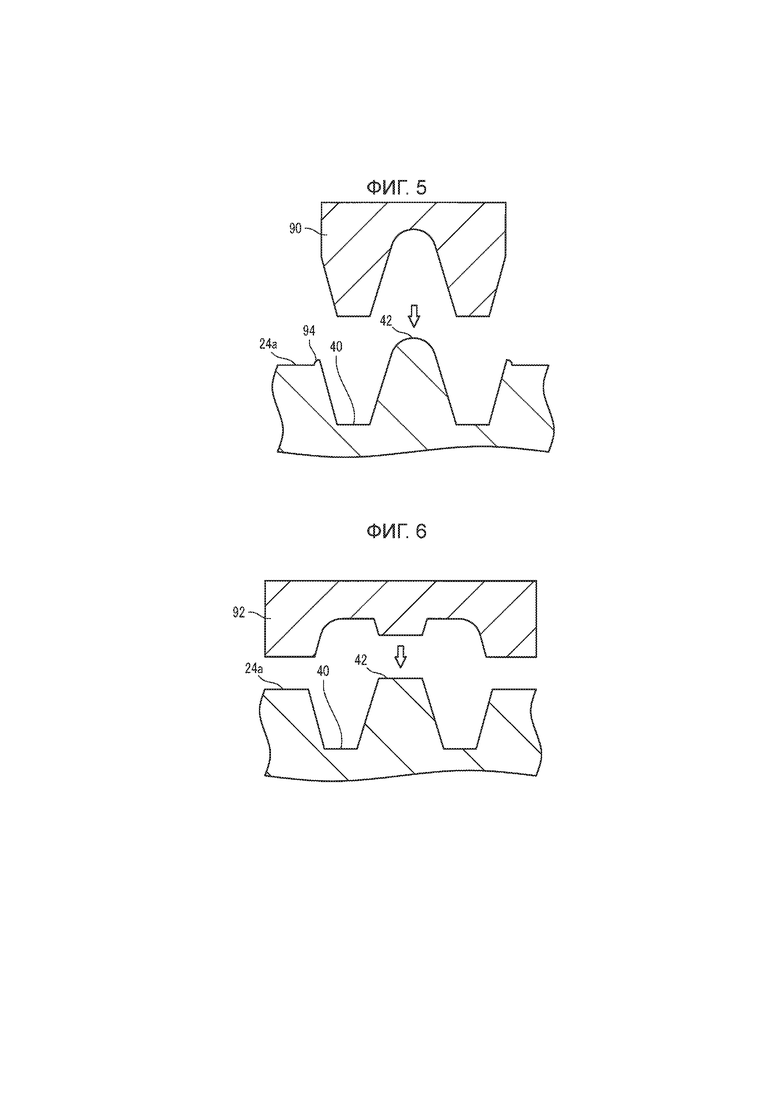

Фиг. 4 - вид в перспективе углубленного участка и выступающего участка;

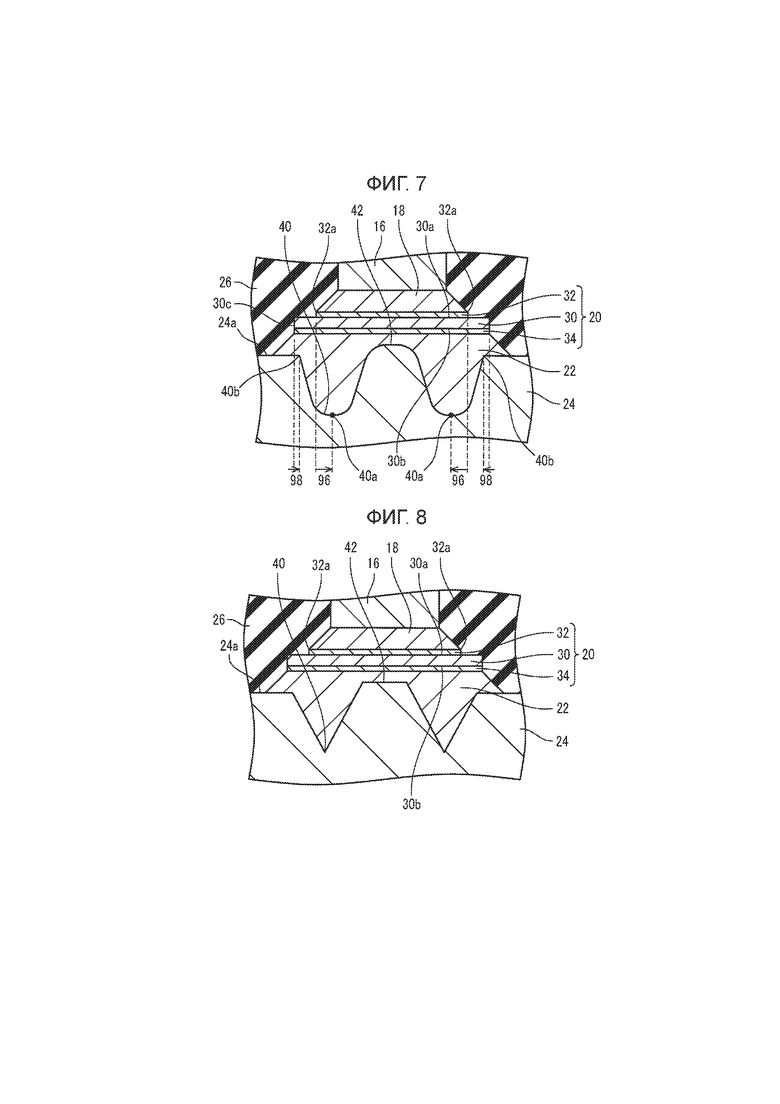

Фиг. 5 - пояснительный чертеж этапа, на котором углубленный участок и выступающий участок формируются;

Фиг. 6 - пояснительный чертеж этапа, на котором углубленный участок и выступающий участок формируются;

Фиг. 7 - укрупненный вид в разрезе полупроводникового модуля согласно примеру модификации, который соответствует фиг. 2;

Фиг. 8 - укрупненный вид в разрезе полупроводникового модуля согласно примеру модификации, который соответствует фиг. 2;

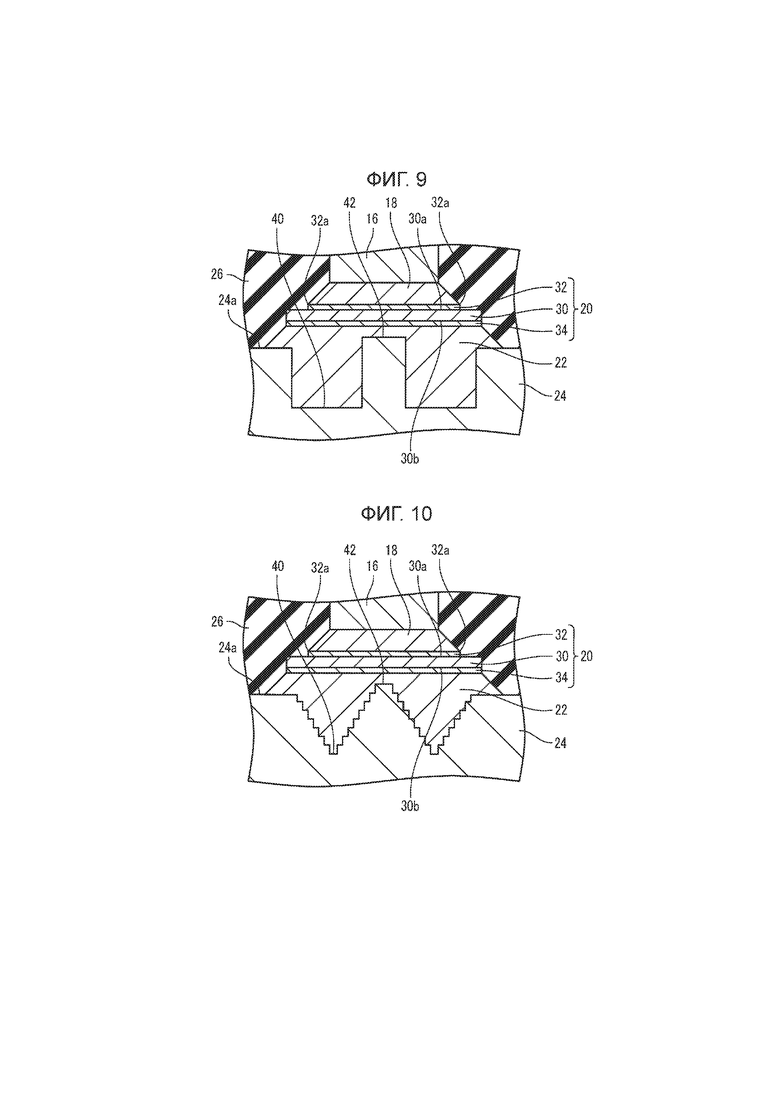

Фиг. 9 - укрупненный вид в разрезе полупроводникового модуля согласно примеру модификации, который соответствует фиг. 2;

Фиг. 10 - укрупненный вид в разрезе полупроводникового модуля согласно примеру модификации, который соответствует фиг. 2;

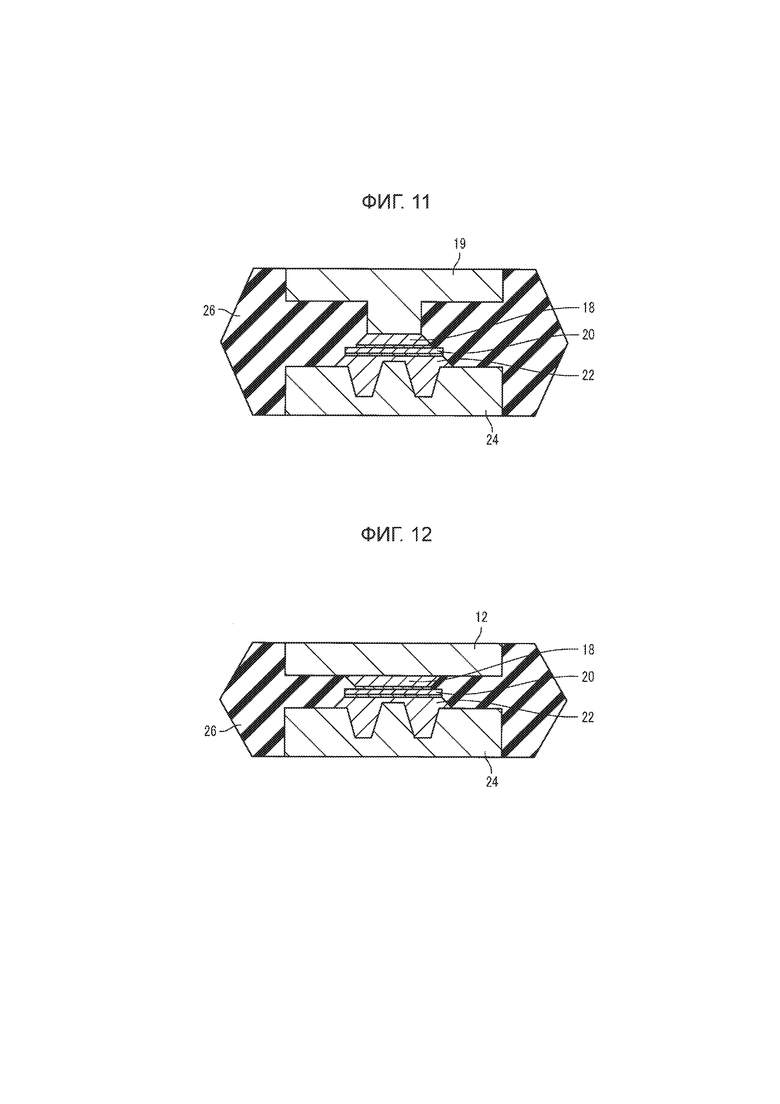

Фиг. 11 - вид в разрезе полупроводникового модуля согласно примеру модификации, который соответствует фиг. 1;

Фиг. 12 - вид в разрезе полупроводникового модуля согласно примеру модификации, который соответствует фиг. 1;

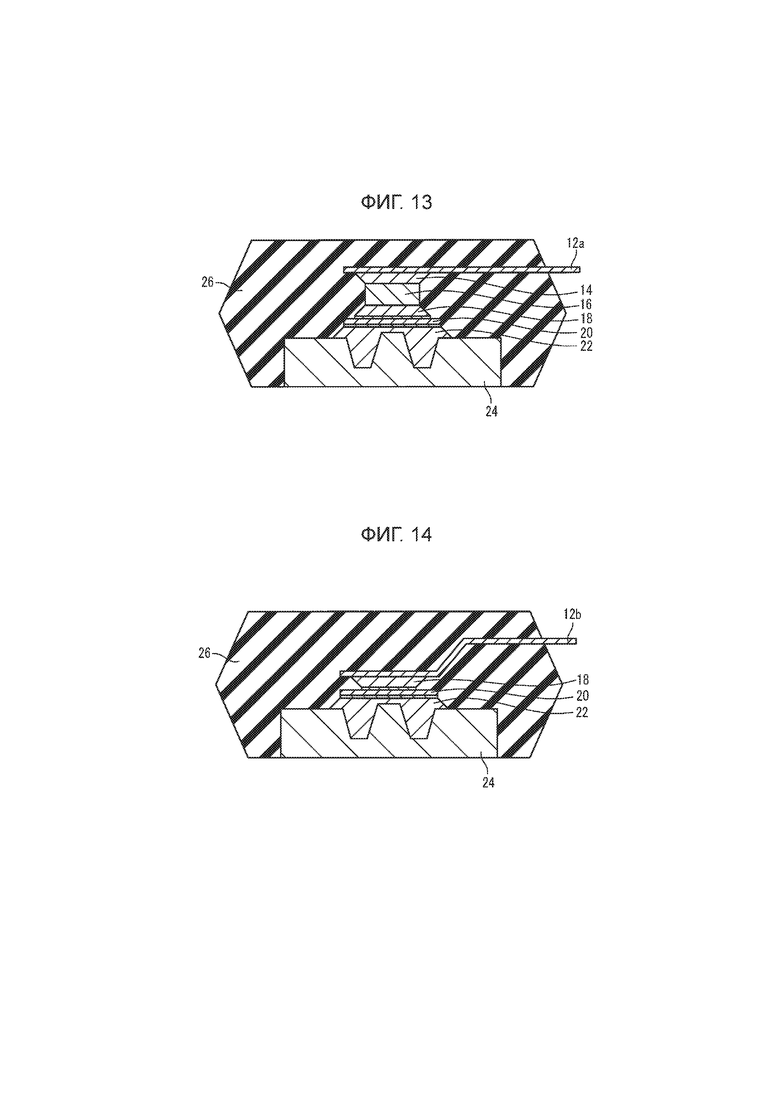

Фиг. 13 - вид в разрезе полупроводникового модуля согласно примеру модификации, который соответствует фиг. 1;

Фиг. 14 - вид в разрезе полупроводникового модуля согласно примеру модификации, который соответствует фиг. 1;

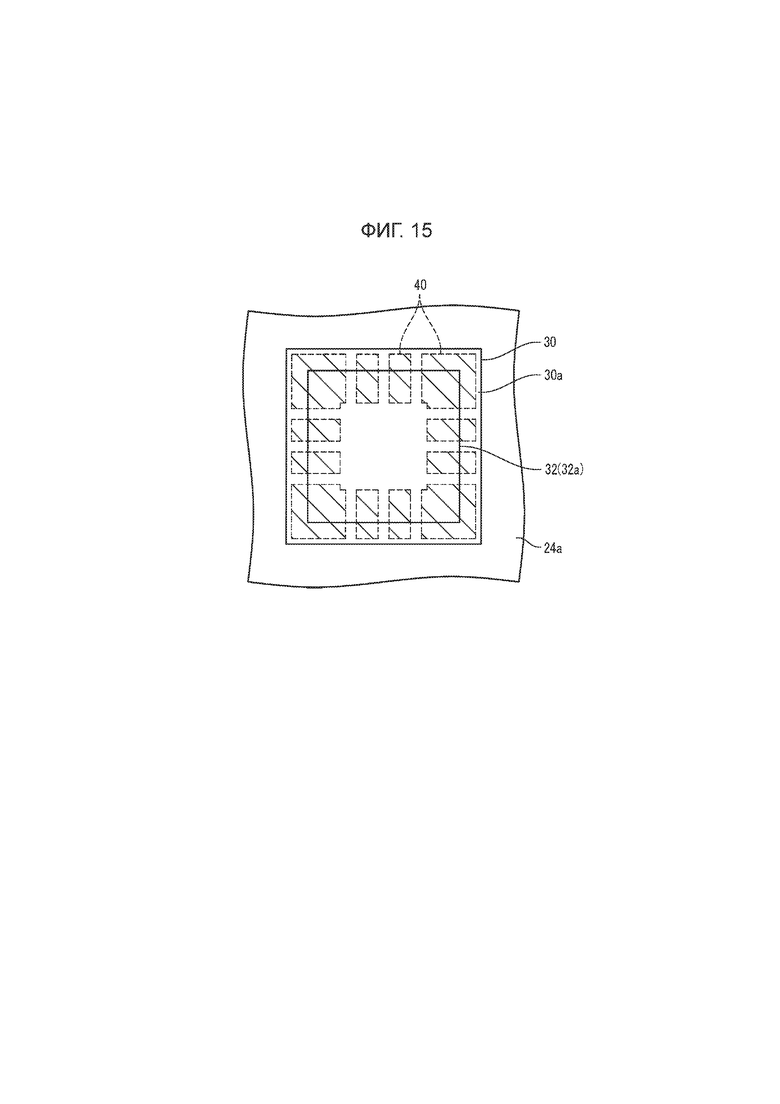

Фиг. 15 - вид сверху полупроводникового модуля согласно примеру модификации, который соответствует фиг. 3;

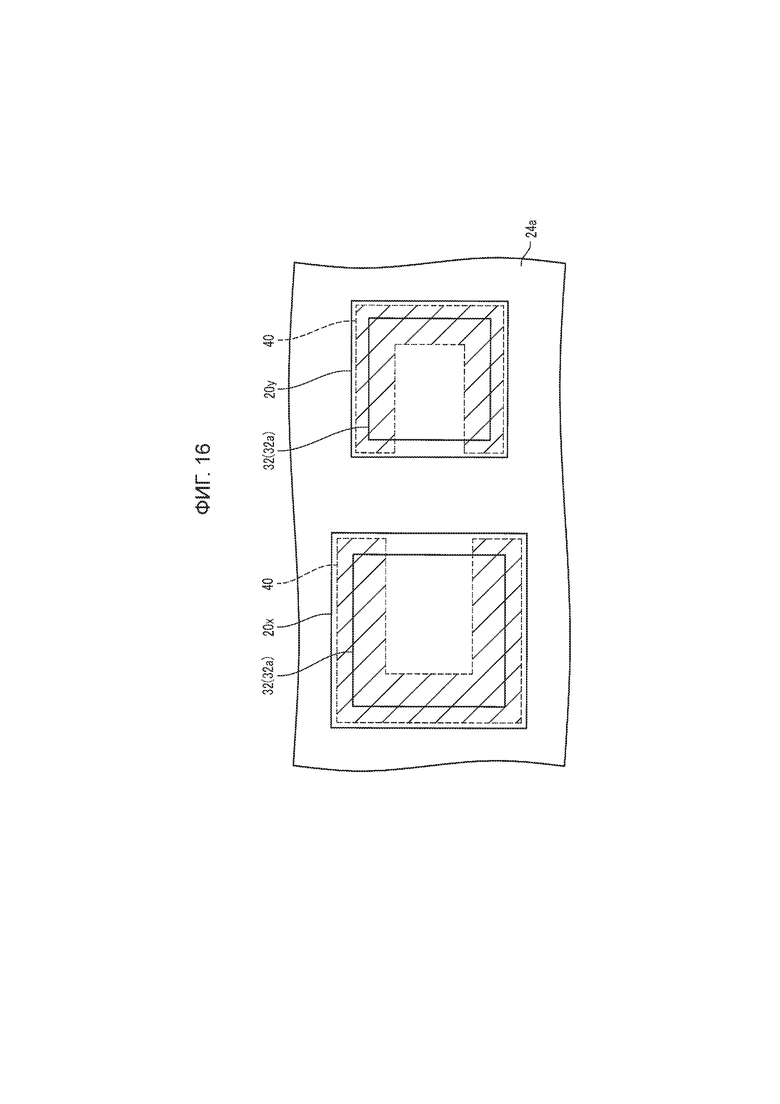

Фиг. 16 - вид в разрезе полупроводникового модуля согласно примеру модификации, который соответствует фиг. 3;

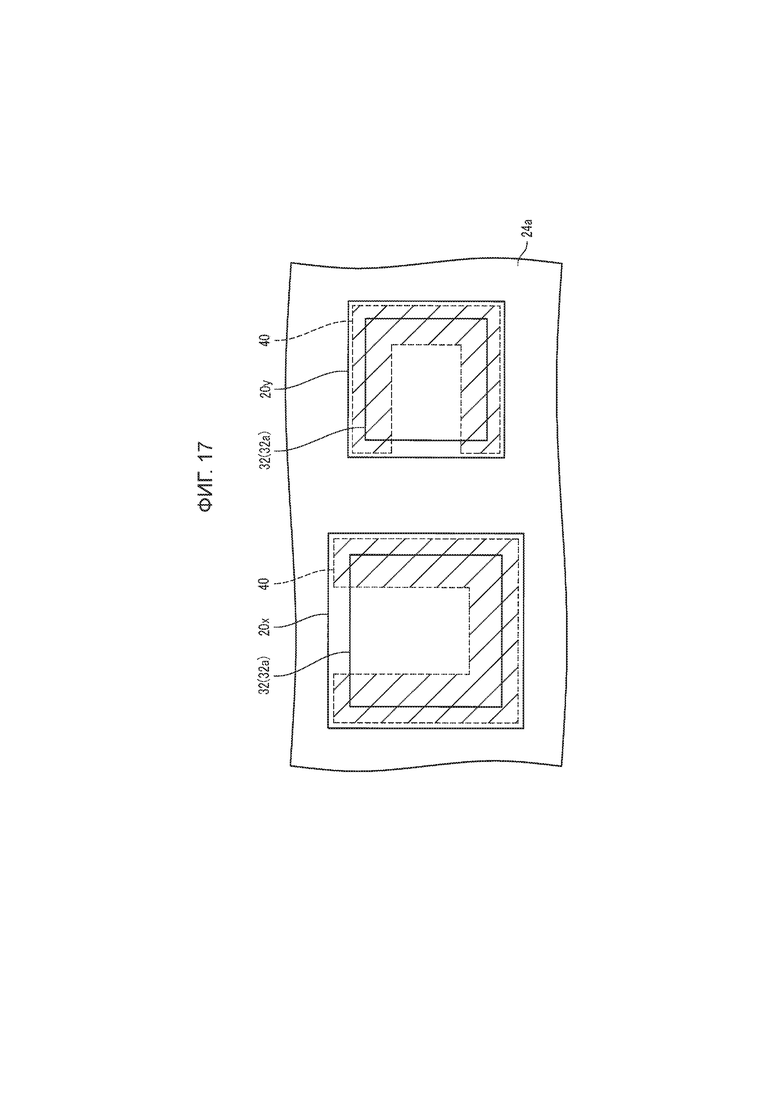

Фиг. 17 - вид в разрезе полупроводникового модуля согласно примеру модификации, который соответствует фиг. 3;

Фиг. 18 - укрупненный вид в разрезе полупроводниковой интегральной схемы полупроводникового модуля согласно предшествующему уровню техники и ее окружения; и

Фиг. 19 - укрупненный вид в разрезе полупроводниковой интегральной схемы полупроводникового модуля согласно предшествующему уровню техники и ее окружения.

Подробное описание вариантов осуществления изобретения

Как иллюстрировано на фиг. 1, полупроводниковый модуль 10 согласно варианту осуществления имеет верхнюю выводную рамку 12, металлический блок 16, полупроводниковую интегральную схему 20, нижнюю выводную рамку 24 и изоляционную смолу 26.

Как иллюстрировано на фиг. 2, полупроводниковая интегральная схема 20 имеет SiC-подложку 30, верхний электрод 32 и нижний электрод 34. Верхний электрод 32 находится в контакте с верхней поверхностью 30a SiC-подложки 30. Фиг. 3 представляет собой вид сверху, показывающий полупроводниковую интегральную схему 20 сверху. Как иллюстрировано на фиг. 3, верхний электрод 32 покрывает средний участок верхней поверхности 30a SiC-подложки 30 и не покрывает внешний периферийный участок верхней поверхности 30a. Сигнальный электрод (не иллюстрирован) располагается в части внешнего периферийного участка верхней поверхности 30a. Сигнальный электрод соединяется с сигнальной клеммой (не иллюстрирована) проводом. Как иллюстрировано на фиг. 2, нижний электрод 34 покрывает всю площадь нижней поверхности 30b SiC-подложки 30. Соответственно, если смотреть в направлении толщины SiC-подложки 30, как на фиг. 3, нижний электрод 34 (т.е., зона, которая имеет тот же размер, что и SiC-подложка 30 на фиг. 3) перекрывает весь верхний электрод 32 и шире верхнего электрода 32. Полупроводниковое устройство, такое как полевой транзистор со структурой металл-оксид-полупроводник (MOSFET) для сильноточного управления и диод, формируется в SiC-подложке 30.

Металлический блок 16 формируется из металла (более конкретно, меди). Как иллюстрировано на фиг. 1 и 2, металлический блок 16 располагается над полупроводниковой интегральной схемой 20. Нижняя поверхность металлического блока 16 соединяется с верхним электродом 32 полупроводниковой интегральной схемы 20 посредством первого слоя 18 припоя.

Верхняя выводная рамка 12 формируется из металла (более конкретно, меди). Как иллюстрировано на фиг. 1, верхняя выводная рамка 12 располагается над металлическим блоком 16. Нижняя поверхность верхней выводной рамки 12 соединяется с верхней поверхностью металлического блока 16 посредством слоя 14 припоя.

Нижняя выводная рамка 24 формируется из металла (более конкретно, меди). Как иллюстрировано на фиг. 1 и 2, нижняя выводная рамка 24 располагается ниже полупроводниковой интегральной схемы 20. Верхняя поверхность 24a нижней выводной рамки 24 соединяется с нижним электродом 34 полупроводниковой интегральной схемы 20 посредством второго слоя 22 припоя. Верхняя поверхность 24a нижней выводной рамки 24 имеет углубленный участок 40 и выступающий участок 42. Как иллюстрировано на фиг. 3 и 4, углубленный участок 40 окружает выступающий участок в верхней поверхности 24a. На фиг. 3 зона, в которой углубленный участок 40 располагается, указывается диагональной линией. Если смотреть в направлении толщины SiC-подложки 30 как на фиг. 3, весь внешний периферийный край 32a верхнего электрода 32 перекрывает углубленный участок 40. Выступающий участок 42 располагается в зоне, окруженной углубленным участком 40. Как иллюстрировано на фиг. 2 и 4, выступающий участок 42 выступает вверх за верхнюю поверхность 24a на внешней периферийной стороне углубленного участка 40. Весь углубленный участок 40 и выступающий участок 42 покрываются вторым слоем 22 припоя. Второй слой 22 припоя соединяется с поверхностью выступающего участка 42, внутренней поверхностью углубленного участка 40 и верхней поверхностью 24a на внешней периферийной стороне углубленного участка 40 (верхней поверхностью 24a рядом с углубленным участком 40).

Как иллюстрировано на фиг. 1, многослойная структура из верхней выводной рамки 12, металлического блока 16, полупроводниковой интегральной схемы 20 и нижней выводной рамки 24 покрывается изоляционной смолой 26. Вся поверхность многослойной структуры за исключением верхней поверхности верхней выводной рамки 12 и нижней поверхности нижней выводной рамки 24 покрывается изоляционной смолой 26. Верхняя поверхность верхней выводной рамки 12 и нижняя поверхность нижней выводной рамки 24 соединяются с охладителем (не иллюстрирован).

Верхняя выводная рамка 12 и нижняя выводная рамка 24 функционируют в качестве проводки полупроводникового модуля 10. Току предоставляется возможность протекать к полупроводниковой интегральной схеме 20 через верхнюю выводную рамку 12 и нижнюю выводную рамку 24. Верхняя выводная рамка 12 и нижняя выводная рамка 24 также функционируют в качестве теплоотвода. Поскольку ток протекает к полупроводниковой интегральной схеме 20, полупроводниковая интегральная схема 20 формирует тепло. Тепло, формируемое полупроводниковой интегральной схемой 20, рассеивается через нижнюю выводную рамку 24 и рассеивается через металлический блок 16 и верхнюю выводную рамку 12. Соответственно, поскольку ток протекает к полупроводниковой интегральной схеме 20, температуры нижней выводной рамки 24, металлического блока 16 и верхней выводной рамки 12 становятся относительно высокими. Коэффициент линейного расширения нижней выводной рамки 24 и коэффициент линейного расширения металлического блока 16 выше коэффициента линейного расширения SiC-подложки 30. Соответственно, величины расширения нижней выводной рамки 24 и металлического блока 16 превышают величину расширения SiC-подложки 30. Поскольку величина расширения SiC-подложки 30 является небольшой, а величина расширения нижней выводной рамки 24 является большой, высокое термическое напряжение прикладывается ко второму слою 22 припоя между SiC-подложкой 30 и нижней выводной рамкой 24. Соответственно, поскольку полупроводниковая интегральная схема 20 многократно активизируется, термическое напряжение многократно прикладывается ко второму слою 22 припоя, и припой во втором слое 22 припоя перемещается к внешней периферийной стороне вследствие явления сползания припоя. Поскольку величина расширения SiC-подложки 30 является небольшой, а величина расширения металлического блока 16 является большой, высокое термическое напряжение прикладывается к первому слою 18 припоя между SiC-подложкой 30 и металлическим блоком 16. Соответственно, поскольку полупроводниковая интегральная схема 20 многократно активизируется, термическое напряжение многократно прикладывается к первому слою 18 припоя, и припой в первом слое 18 припоя перемещается к внешней периферийной стороне вследствие явления сползания припоя. Поскольку припой в первом слое 18 припоя перемещается к внешней периферийной стороне, давление увеличивается на внешнем периферийном крае первого слоя 18 припоя (т.е., рядом с внешним периферийным краем 32a верхнего электрода 32). Соответственно, первый слой 18 припоя оказывает давление на SiC-подложку 30, направленное вниз, рядом с внешним периферийным краем 32a верхнего электрода 32. Давление прикладывается ко второму слою 22 припоя под внешним периферийным краем 32a верхнего электрода 32. Поскольку углубленный участок 40 располагается под внешним периферийным краем 32a верхнего электрода 32, давление прикладывается ко второму слою 22 припоя в углубленном участке 40. Поскольку второй слой 22 припоя в углубленном участке 40 является толстым, второй слой 22 припоя в углубленном участке 40 имеет относительно высокую упругость и едва ли должен пластично деформироваться. Соответственно, даже когда давление многократно прикладывается ко второму слою 22 припоя в углубленном участке 40, перемещение припоя, свойственное давлению, едва ли должно возникать. Поскольку нижняя выводная рамка 24 имеет выступающий участок 42, перемещение припоя во втором слое 22 припоя по направлению к среднему участку затрудняется боковыми поверхностям выступающего участка 42. Соответственно, во втором слое 22 припоя, перемещение припоя по направлению к среднему участку, как указано стрелками 192 на фиг. 19, редко возникает. Соответственно, в полупроводниковом модуле 10 согласно варианту осуществления, давление, с которым второй слой 22 припоя толкает средний участок SiC-подложки 30 вверх, едва ли должно создаваться. Соответственно, в полупроводниковом модуле 10 согласно варианту осуществления, деформация полупроводниковой подложки, как на фиг. 19, пресекается. Следовательно, в полупроводниковом модуле 10, временное ухудшение SiC-подложки 30 может быть пресечено, и может поддерживаться высокая надежность.

Результат моделирования будет описан ниже относительно деформации SiC-подложки 30 во время, когда предварительно определенное число термических циклов было применено. Полупроводниковый модуль (пример 1), в котором нижняя выводная рамка 24 не имеет углубленный участок 40 и выступающий участок 42 (т.е., полупроводниковый модуль, в котором верхняя поверхность 24a нижней выводной рамки 24 является плоской как на предшествующем уровне техники), привел в результате к деформации приблизительно 6,82 × 10-4 мм в SiC-подложке 30. SiC-подложки особенно подвержены деформации, как описано выше, поскольку обычные SiC-подложки являются чрезвычайно тонкими с толщиной 150 мкм или менее. Полупроводниковый модуль (пример 2), в котором нижняя выводная рамка 24 имеет углубленный участок 40 и не имеет выступающий участок 42, привел в результате к деформации приблизительно 3,78 × 10-4 мм в SiC-подложке 30 при тех же условиях, что и пример 1. Сравнение между примерами 1 и 2 ясно показывает, что деформация SiC-подложки 30 может быть эффективно предотвращена посредством предоставления углубленного участка 40. Полупроводниковый модуль (пример 3), в котором нижняя выводная рамка 24 имеет углубленный участок 40 и выступающий участок 42 (т.е., конфигурацию на фиг. 1 и 2), привел в результате к деформации приблизительно 1,74 × 10-4 мм в SiC-подложке 30 при тех же условиях, что и для примера 2. Сравнение между примерами 2 и 3 ясно показывает, что деформация SiC-подложки 30 может быть более эффективно предотвращена посредством предоставления выступающего участка 42.

Этапы, на которых углубленный участок 40 и выступающий участок 42 формируются, иллюстрируются на фиг. 5 и 6. Сначала, плоская верхняя поверхность 24a нижней выводной рамки 24, которая еще должна быть обработана, сдавливается пресс-формой 90, иллюстрированной на фиг. 5. В результате, формируются углубленный участок 40 и выступающий участок 42. На этапе на фиг. 5 верхняя поверхность выступающего участка 42 изгибается и выпячивается. На этапе на фиг. 5 внешний периферийный край углубленного участка 40 имеет задир 94. Верхняя поверхность выступающего участка 42 и задира 94 сдавливается пресс-формой 92, иллюстрированной на фиг. 6. В результате, верхняя поверхность выступающего участка 42 сплющивается, и задир 94 исчезает.

Пример модификации будет описан ниже. Полупроводниковый модуль согласно примеру модификации, который должен быть описан ниже, имеет ту же конфигурацию, что и полупроводниковый модуль 10 согласно вышеописанному варианту осуществления, за исключением отдельно упомянутых частей.

Форма сечения углубленного участка 40 может быть подходящим образом изменена. Фиг. 7 показывает форму сечения углубленного участка 40 согласно примеру модификации. На фиг. 7 углубленный участок 40 имеет U-образное поперечное сечение. Как указано стрелками 96, на фиг. 7, самый глубокий участок 40a углубленного участка 40 располагается на внутренней периферийной стороне внешнего периферийного края 32a верхнего электрода 32 (более конкретно, самый глубокий участок 40a располагается на внутренней периферийной стороне внешнего периферийного края 32a верхнего электрода 32, когда SiC-подложка 30 рассматривается в направлении толщины). Моделирование, аналогичное примеру 1, описанному выше, было выполнено с помощью конфигурации полупроводникового модуля, иллюстрированного на фиг. 7 (пример 4), и моделирование привело в результате к деформации приблизительно 2,35 × 10-4 мм в SiC-подложке 30. Моделирование, аналогичное примеру 4, описанному выше, было выполнено с помощью конфигурации, в которой самый глубокий участок 40a располагается на внешней периферийной стороне внешнего периферийного края 32a верхнего электрода 32 (пример 5), и моделирование привело в результате к деформации приблизительно 2,49 × 10-4 мм в SiC-подложке. Сравнение между примерами 4 и 5 ясно показывает, что деформация SiC-подложки 30 может быть дополнительно предотвращена посредством самого глубокого участка 40a углубленного участка 40, располагаемого на внутренней периферийной стороне внешнего периферийного края 32a верхнего электрода 32.

Как указано стрелками 98, на фиг. 7, внешний периферийный край 40b углубленного участка 40 располагается на внутренней периферийной стороне внешнего периферийного края 30c SiC-подложки 30 (более конкретно, внешний периферийный край 40b располагается на внутренней периферийной стороне внешнего периферийного края 30c, когда SiC-подложка 30 рассматривается в направлении толщины). Деформация SiC-подложки 30 в конфигурации на фиг. 7 (т.е., пример 4) равна 2,35 × 10-4 мм, как описано выше. Моделирование, аналогичное примеру 4, описанному выше, было выполнено с помощью конфигурации, в которой внешний периферийный край 40b углубленного участка 40 располагается на внешней периферийной стороне внешнего периферийного края 30c SiC-подложки 30 (пример 6), и моделирование привело в результате к деформации приблизительно 4,56 × 10-4 мм в SiC-подложке 30. Сравнение между примерами 4 и 6 ясно показывает, что деформация SiC-подложки 30 может быть дополнительно предотвращена посредством внешнего периферийного края 40b углубленного участка 40, располагаемого на внутренней периферийной стороне внешнего периферийного края 30c SiC-подложки 30.

Углубленный участок 40 может иметь V-образную форму сечения как на фиг. 8. Углубленный участок 40 может иметь прямоугольную форму сечения как на фиг. 9. Углубленный участок 40 может иметь ступенчатую форму сечения как на фиг. 10.

На фиг. 1 металлический блок 16 и верхняя выводная планка 12 соединяются слоем 14 припоя. Альтернативно, полупроводниковый модуль может быть сконфигурирован посредством металлической части 19, сформированной так, что металлический блок 16 и верхняя выводная планка 12 объединяются, как иллюстрировано на фиг. 11. Как иллюстрировано на фиг. 12, верхняя выводная рамка 12 может быть соединена с верхним электродом полупроводниковой интегральной схемы 20 через первый слой 18 припоя и без металлического блока 16. Как иллюстрировано на фиг. 13, клемма 12a, более тонкая, чем верхняя выводная рамка 12, может быть соединена с верхней поверхностью металлического блока 16. Как иллюстрировано на фиг. 14, тонкая клемма 12b может быть соединена с верхним электродом полупроводниковой интегральной схемы 20 не через металлический блок 16.

Как иллюстрировано на фиг. 4, в полупроводниковом модуле 10 согласно варианту осуществления, описанному выше, углубленный участок 40 имеет форму рамки, окружающей зону в верхней поверхности 24a нижней выводной рамки 24. Альтернативно, углубленный участок 40 может не иметь форму рамки, поскольку углубленный участок 40 располагается вдоль нижнего участка внешнего периферийного края 32a верхнего электрода 32. Например, как иллюстрировано на фиг. 15, углубленные участки 40 могут быть распределены с промежутками вдоль нижнего участка внешнего периферийного края 32a верхнего электрода 32. Как иллюстрировано на фиг. 16, частично прерывающийся углубленный участок 40 может протягиваться вдоль нижнего участка внешнего периферийного края 32a верхнего электрода 32. В конфигурации, которая иллюстрируется на фиг. 16, две полупроводниковых интегральных схемы 20x, 20y устанавливаются на нижнюю выводную рамку 24. Например, полупроводниковая интегральная схема 20x может составлять MOSFET, а полупроводниковая интегральная схема 20y может составлять диод. В этом случае углубленный участок 40 может не быть предусмотрен на сторонах верхнего электрода 32 полупроводниковой интегральной схемы 20x и верхнего электрода 32 полупроводниковой интегральной схемы 20y, которые обращены друг к другу. Как иллюстрировано на фиг. 17, углубленный участок 40 может быть прерывистым.

Хотя весь углубленный участок 40 покрывается вторым слоем 22 припоя в варианте осуществления, описанном выше, часть углубленного участка 40 может не быть покрыта вторым слоем 22 припоя.

Хотя полупроводниковая интегральная схема 20 покрывается изолирующей смолой 26 в варианте осуществления, описанном выше, полупроводниковая интегральная схема 20 может не быть покрыта изолирующей смолой 26. Полупроводниковая интегральная схема 20 может быть покрыта силиконовым гелем или т.п. вместо изолирующей смолы 26.

Соотношения между компонентами полупроводникового модуля согласно варианту осуществления, описанному выше, и компонентами полупроводникового модуля согласно изобретению будут описаны ниже. Верхний электрод согласно варианту осуществления является примером первого электрода согласно изобретению. Нижний электрод согласно варианту осуществления является примером второго электрода согласно изобретению. Верхняя выводная рамка согласно варианту осуществления является примером первого проводника согласно изобретению. Нижняя выводная рамка согласно варианту осуществления является примером второго проводника согласно изобретению. Выступающий участок согласно варианту осуществления является примером соединительной поверхности в зоне, окруженной углубленным участком согласно изобретению.

Технические элементы, раскрытые в этой спецификации, будут перечислены ниже. Каждый из последующих технических элементов является независимо полезным.

В полупроводниковом модуле согласно примеру, раскрытому в этой спецификации, углубленный участок может иметь форму рамки в соединительной поверхности. Весь внешний периферийный край первого электрода может перекрывать углубленный участок, если смотреть на полупроводниковую подложку в направлении толщины.

Согласно вышеописанной конфигурации, деформация полупроводниковой подложки может быть более надежным образом предотвращена.

В полупроводниковом модуле согласно примеру, раскрытому в этой спецификации, соединительная поверхность в зоне, окруженной углубленным участком, может выступать в сторону полупроводниковой подложки за поверхность второго проводника на внешней периферийной стороне углубленного участка.

Согласно вышеописанной конфигурации, деформация полупроводниковой подложки может быть более надежным образом предотвращена.

В полупроводниковом модуле согласно примеру, раскрытому в этой спецификации, самый глубокий участок углубленного участка может быть расположен на внутренней периферийной стороне внешнего периферийного края первого электрода, если смотреть на полупроводниковую подложку в направлении толщины.

Согласно вышеописанной конфигурации, деформация полупроводниковой подложки может быть более надежным образом предотвращена.

В полупроводниковом модуле согласно примеру, раскрытому в этой спецификации, второй слой припоя может покрывать углубленный участок и поверхность второго проводника на внешней периферийной стороне углубленного участка.

Вариант осуществления, описанный подробно выше, является просто примером и не ограничивает рамки формулы изобретения. Технология, раскрытая в рамках формулы изобретения, включает в себя различные модификации и изменения на основе конкретного примера, описанного выше. Технические элементы, описанные в этой спецификации или на чертежах, демонстрируют техническую полезность независимо или посредством различных сочетаний и не ограничиваются сочетаниями, раскрытыми в предоставленной формуле изобретения. Технология, приведенная в качестве примера в этой спецификации или на чертежах, добивается множества целей в одно и то же время и сохраняет техническую полезность, даже когда просто достигается одна из целей.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 2012 |

|

RU2511054C2 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО | 2018 |

|

RU2695049C1 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО | 1999 |

|

RU2165115C2 |

| КОМПОЗИЦИОННЫЙ МАТЕРИАЛ | 1998 |

|

RU2216602C2 |

| ЭЛЕКТРОННЫЙ КОМПОНЕНТ И ЭЛЕКТРОННОЕ УСТРОЙСТВО | 2014 |

|

RU2575944C2 |

| СВЕТОИЗЛУЧАЮЩИЙ ДИОД БОКОВОГО ИЗЛУЧЕНИЯ С СИЛИКОНОВОЙ ЛИНЗОЙ, ПОДДЕРЖИВАЕМОЙ КРИВОЛИНЕЙНЫМ СИЛИКОНОВЫМ УЧАСТКОМ | 2008 |

|

RU2477546C2 |

| ОСТРОВКОВЫЙ ДЕРЖАТЕЛЬ ДЛЯ СВЕТОИЗЛУЧАЮЩЕГО УСТРОЙСТВА | 2011 |

|

RU2721101C2 |

| ИЗЛУЧАЮЩИЙ УЛЬТРАФИОЛЕТОВЫЙ СВЕТ НИТРИДНЫЙ ПОЛУПРОВОДНИКОВЫЙ ЭЛЕМЕНТ И ИЗЛУЧАЮЩЕЕ УЛЬТРАФИОЛЕТОВЫЙ СВЕТ НИТРИДНОЕ ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО | 2015 |

|

RU2664755C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ГИБРИДНОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ СВЧ-ДИАПАЗОНА | 2009 |

|

RU2417480C1 |

| КОМПОЗИТНЫЙ МАТЕРИАЛ, СПОСОБ ЕГО ПОЛУЧЕНИЯ, ИЗЛУЧАЮЩАЯ ТЕПЛО ПАНЕЛЬ ДЛЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА, ПОЛУПРОВОДНИКОВЫЙ ПРИБОР (ВАРИАНТЫ), ДИЭЛЕКТРИЧЕСКАЯ ПАНЕЛЬ И ЭЛЕКТРОСТАТИЧЕСКОЕ ПОГЛОЩАЮЩЕЕ УСТРОЙСТВО | 2000 |

|

RU2198949C2 |

Полупроводниковый модуль включает в себя полупроводниковую подложку, первый электрод в контакте с первой поверхностью полупроводниковой подложки, второй электрод в контакте со второй поверхностью полупроводниковой подложки, первый проводник, соединенный с первым электродом через первый слой припоя, и второй проводник, соединенный со вторым электродом через второй слой припоя. Второй электрод перекрывает весь первый электрод и шире первого электрода, если смотреть в направлении толщины полупроводниковой подложки. Углубленный участок, расположенный вдоль внешнего периферийного края первого электрода, располагается в соединительной поверхности второго проводника в контакте со вторым слоем припоя, чтобы перекрывать внешний периферийный край первого электрода, если смотреть на полупроводниковую подложку в направлении толщины. Изобретение обеспечивает исключение деградации со временем полупроводниковой подложки. 7 з.п. ф-лы, 19 ил.

1. Полупроводниковый модуль, содержащий:

полупроводниковую подложку;

первый электрод в контакте с первой поверхностью полупроводниковой подложки в зоне за исключением внешней периферийной области первой поверхности полупроводниковой подложки;

второй электрод в контакте со второй поверхностью полупроводниковой подложки, причем первая поверхность и вторая поверхность являются противоположными поверхностями полупроводниковой подложки;

первый проводник, соединенный с первым электродом через первый слой припоя; и

второй проводник, соединенный со вторым электродом через второй слой припоя,

при этом второй электрод перекрывает весь первый электрод и шире первого электрода, если смотреть в направлении толщины полупроводниковой подложки;

причем углубленный участок, расположенный вдоль внешнего периферийного края первого электрода, расположен в соединительной поверхности второго проводника в контакте со вторым слоем припоя, чтобы перекрывать внешний периферийный край первого электрода, если смотреть на полупроводниковую подложку в направлении толщины.

2. Полупроводниковый модуль по п. 1, в котором:

углубленный участок окружает зону в соединительной поверхности и

весь внешний периферийный край первого электрода перекрывает углубленный участок, если смотреть на полупроводниковую подложку в направлении толщины.

3. Полупроводниковый модуль по п. 2, в котором соединительная поверхность в зоне, окруженной углубленным участком, выступает к полупроводниковой подложке за поверхность второго проводника на внешней периферийной стороне углубленного участка.

4. Полупроводниковый модуль по п. 3, в котором самый глубокий участок углубленного участка расположен на внутренней периферийной стороне внешнего периферийного края первого электрода, если смотреть на полупроводниковую подложку в направлении толщины.

5. Полупроводниковый модуль по любому из пп. 2-4, в котором второй слой припоя покрывает углубленный участок и поверхность второго проводника на внешней периферийной стороне углубленного участка.

6. Полупроводниковый модуль по любому из пп. 1-4, в котором внешний периферийный край углубленного участка расположен на внутренней периферийной стороне внешнего периферийного края полупроводниковой подложки, если смотреть на полупроводниковую подложку в направлении толщины.

7. Полупроводниковый модуль по любому из пп. 1-4, в котором полупроводниковая подложка является SiC-подложкой.

8. Полупроводниковый модуль по п. 1, в котором множество углубленных участков, расположенных вдоль внешнего периферийного края первого электрода, расположено в соединительной поверхности второго проводника в контакте со вторым слоем припоя, чтобы перекрывать внешний периферийный край первого электрода, если смотреть на полупроводниковую подложку в направлении толщины.

| US 20140291696 A1, 02.10.2014 | |||

| DE 102014223863 A1, 22.10.2015 | |||

| US 8921989 B2, 30.12.2014 | |||

| СИЛОВОЙ ПОЛУПРОВОДНИКОВЫЙ МОДУЛЬ | 1999 |

|

RU2225660C2 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО И СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО УСТРОЙСТВА | 2015 |

|

RU2612944C1 |

| МОЩНЫЙ ПОЛУПРОВОДНИКОВЫЙ ПРИБОР | 2009 |

|

RU2407106C1 |

Авторы

Даты

2019-04-25—Публикация

2018-06-22—Подача