Область техники, к которой относится изобретение

Изобретение относится к области создания способов контроля и электротермотренировки (ЭТТ) полупроводниковых приборов, сформированных первоначально на полупроводниковых пластинах, а конкретно способу изготовления полупроводникового прибора.

Уровень техники

Традиционный метод изготовления полупроводниковых приборов хорошо изучен и известен по многочисленным публикациям (см., например, А.П.Достанко «Технология интегральных схем», Минск, «Высшая школа», 1982 г.).

В частности, подробно описаны процессы разделения пластин на кристаллы: скрайбирование алмазным резцом, скрайбирование лазерным лучом, резка алмазными дисками, резка металлическими дисками, полотнами и проволоками, ультразвуковая резка, химическое и электрохимическое травление. Описана также технология посадки кристаллов на кристаллодержатели, подсоединение выводов к кристаллам и корпусам. Отмечено, что изготовление круглых или фигурных кристаллов, образование углублений и выступов в полупроводниковых и диэлектрических пластинах осуществляют ультразвуковой резкой с абразивной суспензией. К недостаткам традиционных методов сборки, контроля и ЭТТ следует отнести их высокую трудоемкость (стоимость), связанную с тем, что операции ЭТТ и окончательного контроля проводятся после окончательного изготовления ИС (дорогостоящие операции: посадка кристаллов на рамку, приварка выводов на кристалл и рамку, изготовление корпусов и процесс корпусирования). Данное изобретение позволяет не проводить этих операций над бракованными кристаллами.

Известна конструкция этажерочной сборки носителей кремниевых кристаллов по патенту США 5434745, H01L 21/18 от 18.07.95 г. В патенте показана этажерочная сборка носителей кристаллов и метод упаковки и соединения кремниевых чипов таких, как чипы памяти. Носитель сконструирован как металлическая подложка, внутри которой закреплен чип. Чип проволочными выводами связан с токопроводящей разводкой на подложке. Каждый проводник, когда связь идет к кромке подложки, соединяется полукруглым отверстием. Основание находится на верхней части подложки. Это основание имеет также разводку к металлизированным отверстиям полукруглой формы через отверстия, которые находятся в основании подложки. Комбинация основания подложки с кремниевым компонентом и с верхним основанием формируют этажерочную единицу. Несколько таких единиц могут быть собраны в этажерку и расположены один над другим. Поверхность единицы может быть окончательно накрыта керамической крышкой, которая также имеет множество полукруглых металлизированных отверстий, образованных на ее краях. Чтобы электрически соединить этажерочную сборку, может быть использован проводящий полимер, расположенный в выемках после выравнивания полукруглых отверстий с помощью основания.

Преимуществом данной конструкции является формирование по периметру носителей кристаллов полукруглых металлизированных отверстий для соединения носителей между собой. Но использование кристаллов в нишах носителей, их соединение с разводкой носителя проволокой делает конструкцию малонадежной с низкой плотностью компоновки.

Известно также техническое решение по патенту GB 2127217 A, H01L 23/12 от 09.08.83 г. «Корпус и держатель полупроводниковой ИС». Кристаллодержатель, который может устанавливаться в корпусе, включает в себя тонкий прямоугольник изолирующего материала с контактными площадками, расположенными близко друг от друга по четырем краям обеих основных поверхностей. Кристалл прикреплен главным образом к центру изолирующего материала, а соединения с контактами проложены на основных поверхностях. В одном из вариантов, держатель имеет изоляционную прокладку с дополнительными контактами. Электрические соединения подсоединены к контактам. Тогда изоляционное покрытие накрывает полую внутреннюю часть. Таким образом, контакты обеспечивают контактирование верхней поверхности законченной конструкции. Двусторонние кристаллодержатели позволяют максимально использовать контакты обеих основных поверхностей. Недостатки - аналогичны решению по патенту США 5434745.

Известны конструкция трехмерного электронного блока и способ его изготовления по международной заявке PCT/SU90/00022, H01L 25/04 от 24.01.90 г.

Способ изготовления заключается в том, что при использовании в блоке бескорпусных электронных компонентов, их предварительно группируют по принципу наименьшего количества выводных контактов у носителя, электронные компоненты ориентируют относительно друг друга и предварительно фиксируют, изготавливают носители с окончательным закреплением в них электронных компонентов, электрически изолируют незащищенные токопроводящие зоны электронных компонентов, кроме контактных площадок, контактные площадки электронных компонентов и выводные контакты носителей очищают от органических загрязнений и окисных пленок, наносят на поверхности электронных компонентов и носителей проводники, производят электрическое соединение выводных контактов носителей по поверхностям блока, осуществляют герметизацию собранного блока.

Положительными факторами данной заявки являются решения по групповому нанесению изоляционного слоя на электрически незащищенные области электронных компонентов и последующее нанесение всех коммутирующих проводников высоконадежным способом - вакуумным напылением с применением «свободных» масок. К недостаткам следует отнести предварительное, без проведения ЭТТ и функционального контроля, расчленение полупроводниковой пластины на кристаллы с последующей их ориентацией между собой и относительно внешних выводов, а наличие полимерного носителя уменьшает общую плотность компоновки.

Известно техническое решение по патенту США 5831445, G01R 1/06 от 03.11.98 г. «Аппаратура и процесс ЭТТ полупроводниковых пластин».

Пластины соединяются с печатной платой, которая электрически контактирует с площадками на каждом кристалле, используя маленькие проводящие контактные столбики. Точное совмещение целой пластины внутри устройства позволяет тестировать все кристаллы на пластине одновременно, исключая необходимость исследования каждого кристалла в отдельности. Устройство оснащается тепловыми элементами и охлаждающими каналами для получения необходимой температуры пластины при ЭТТ и тестировании. Способ исключает использование дефектных кристаллов после ЭТТ и тестирования, повышая, таким образом, эффективность сборки. Достоинством данного технического решения является попытка проведения групповой ЭТТ и контроля в составе пластины, а также наличие теплоотвода. К недостаткам следует отнести контактирование пластины с контактными столбиками путем их пластической деформации, что вызывает необходимость больших усилий при сочленении платы с пластиной и делает невозможным вторичное применение данной конструкции контактирующего устройства.

Известно также техническое решение по патенту США 5399505, H01L 21/66 от 21.03.95 г. «Метод и аппаратура для осуществления на уровне пластин тестирования кристаллов интегральных схем».Данное решение является наиболее близким к предлагаемому способу изготовления полупроводниковых приборов.

Полупроводниковые пластины включают кристаллы интегральных схем, проводники на пластине и контактные площадки пластины, сформированные на ней. Проводники на пластине используются для передачи электрических сигналов к кристаллам интегральных схем и от них так, что может быть проведено на уровне пластины тестирование и ЭТТ кристаллов интегральных схем. В соответствии с одним из вариантов воплощения, каждый проводник на пластине электрически соединен с одной и той же площадкой на каждом кристалле интегральных схем. Каждый проводник на пластине включает, по меньшей мере, свою часть проводника, которая проходит сверху поверхности, по меньшей мере, одного кристалла интегральной схемы.

К преимуществам данного решения следует отнести попытку группового контроля и ЭТТ кристаллов в составе пластины. К недостаткам - параллельное соединение одноименных контактных площадок всех кристаллов, что делает весьма затруднительным определение вышедшего из строя кристалла; использование только лицевой поверхности пластины для разводки делает ее очень сложной и требует огромного количества внешних контактных площадок на пластине.

Основной задачей данного изобретения является обеспечение групповой ЭТТ и полного функционального контроля кристаллов в составе полупроводниковой пластины, что значительно удешевляет производство полупроводниковых приборов.

Раскрытие изобретения

Поставленная задача решается тем, что способ изготовления полупроводникового прибора, включающий изготовление структур на полупроводниковой пластине, покрытие пластины изоляционным слоем со вскрытием контактных площадок, предварительный контроль кристаллов, разделение полупроводниковой пластины на отдельные кристаллы, их корпусирование, ЭТТ и окончательный контроль, согласно изобретению предусматривает проектирование разводки проводников для проведения ЭТТ и предварительного (функционального) контроля кристаллов по лицевой и обратной поверхностям полупроводниковой пластины. При этом целесообразно использовать стандартное математическое обеспечение для разводки двусторонних и многослойных печатных плат.

В полупроводниковой пластине в зонах последующей резки пластины и других зонах, не занятых структурами и/или проводниками, их соединяющими, по результатам проектирования, прошивают переходные сквозные отверстия, которые могут быть любой формы. В случае дальнейшего использования кристаллов, вычлененных из полупроводниковой пластины, в многокристальных сборках или в трехмерных модулях, при помощи отверстий формируют внешние контакты микроплат.

Поверхности сквозных отверстий, образовавшиеся сколы, лицевую и обратную поверхность полупроводниковой пластины селективно покрывают изоляционным слоем. Это необходимо для обеспечения дальнейшей разводки проводников по обеим поверхностям полупроводниковой пластины. В соответствии с результатами проектирования поверх нанесенного вторичного изоляционного слоя на лицевую, обратную поверхности полупроводниковой пластины и в отверстия наносят преимущественно методом вакуумного осаждения металлические проводники, необходимые для ЭТТ и полного контроля всех кристаллов, входящих в состав полупроводниковой пластины. При этом необходимо использовать магнетронное напыление или любое другое с планетарным вращением объекта напыления. Это обеспечит хорошее нанесение проводников в отверстиях. Возможна также многослойная разводка на поверхностях пластины. При расположении проводников на лицевой поверхности пластины следует учитывать возможность паразитной емкостной связи между структурой и нанесенным проводником.

Во избежание нежелательных воздействий бракованных зон полупроводниковой пластины на потенциально годные кристаллы, разрывают проводники, идущие от забракованных при предварительном контроле кристаллов от общей разводки, нанесенной на полупроводниковую пластину.

Далее проводят групповую ЭТТ и полный контроль всех годных после предварительного контроля кристаллов в соответствии с техническими условиями на них. При необходимости во время ЭТТ и контроля обеспечивают тепловой контакт полупроводниковой пластины со средствами теплоотвода. Далее полупроводниковую пластину разделяют на кристаллы сквозной резкой, после чего направляют годные кристаллы на корпусирование.

И далее используют их в многокристальных сборках в трехмерных модулях в качестве гарантированно годных компонентов.

При прошивке отверстий в полупроводниковой пластине лазерным методом применяют многоступенчатый метод прошивки или другие средства предотвращения разбрызгивания и выброса материала подложки полупроводниковой пластины на кромки отверстий и на поверхности пластины. Выполнение этого условия необходимо ввиду того, что при последующем нанесении изоляционного и проводящего слоев возможно возникновение дефектных областей в зонах выброса материала и недопустимо вкрапление материала подложки в полупроводниковую структуру.

При прошивке отверстий в полупроводниковой пластине ультразвуковым методом, обработку ведут с обратной поверхности пластины. Это необходимо, чтобы защитить поверхность полупроводниковой пластины со структурами от воздействия абразивного материала и отходов обработки. При прошивке отверстий в полупроводниковой пластине методом химического травления, обработку ведут одновременно с противоположных поверхностей пластины с предварительным вскрытием зон травления, например, фотолитографией. Это необходимо для уменьшения бокового подтрава во время обработки.

Неорганический изоляционный слой на поверхности отверстий, на лицевую и обратную поверхности пластины наносят преимущественно методами пиролитического осаждения или магнетронным напылением кремния в кислородной среде. Последний вариант предпочтительней, так как обеспечивает более высокое качество покрытия в отверстиях.

Органический изоляционный слой на поверхности отверстий, на лицевую и обратную поверхности полупроводниковой пластины наносят преимущественно методом распыления органического диэлектрика с применением вакуумного отсоса, что обеспечивает хорошее качество изоляционного покрытия в отверстиях.

После нанесения изоляционного слоя, в случае необходимости, на обратной поверхности полупроводниковой пластины производят формирование электронных компонентов, выполненных по тонкопленочной и/или толстопленочной технологии и необходимых для обеспечения ЭТТ и контроля.

Одновременно с нанесением проводников образуют внешнюю контактную зону для присоединения внешнего кабеля, состоящую из множества выводных контактов, расположенных по периферийной зоне полупроводниковой пластины на одной или двух ее поверхностях. При этом полезно, в первую очередь, использовать зону базового среза на пластине, так как в этом месте легче обеспечить внешнее контактирование. Удаление проводников, идущих от забракованных кристаллов, осуществляют преимущественно пережиганием лазерным методом или механическим методом преимущественно с помощью САПР.

В случае дальнейшего использования кристаллов в многокристальных сборках или в трехмерных модулях, при сквозной резке полупроводниковой пластины на торцах кристаллов оставляют металлизированные впадины, соединенные проводниками между собой и/или с контактными площадками кристаллов; изолируют полученные после разделения полупроводниковой пластины оголенные участки кристаллов; производят селективное горячее лужение проводников, расположенных во впадинах и частично - на поверхностях кристаллов. Таким образом, получают кристалл-микроплату, полностью пригодную для сборки трехмерного модуля.

Краткое описание чертежей

Изобретение поясняется конкретными примерами его выполнения, на которых:

на фиг.1 изображена полупроводниковая пластина со сквозными отверстиями;

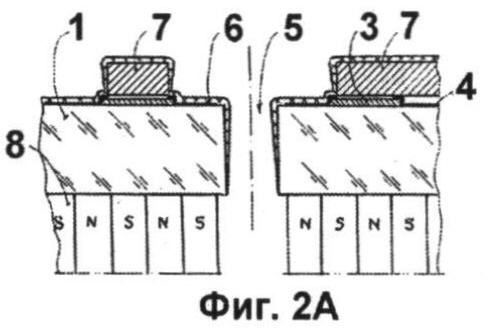

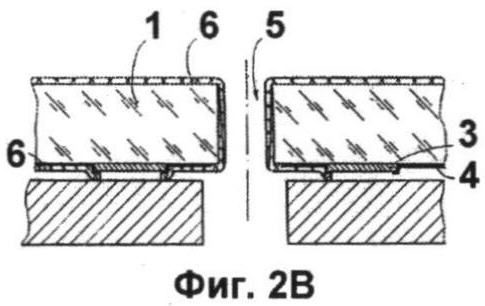

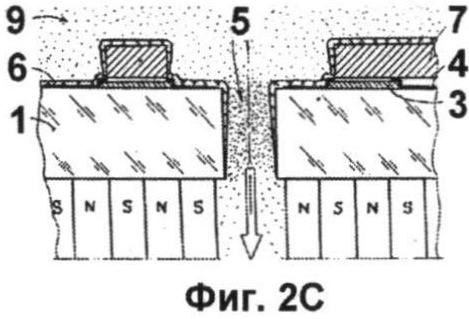

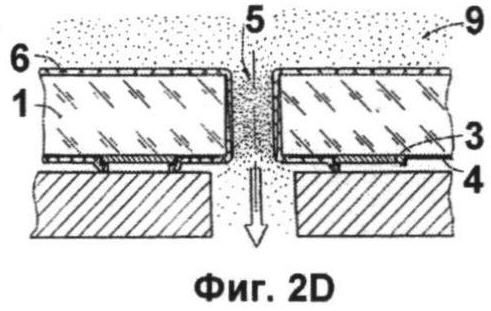

на фиг.2A, 2B, 2C и 2D изображены варианты нанесения изоляционного слоя на поверхности полупроводниковой пластины и в отверстия;

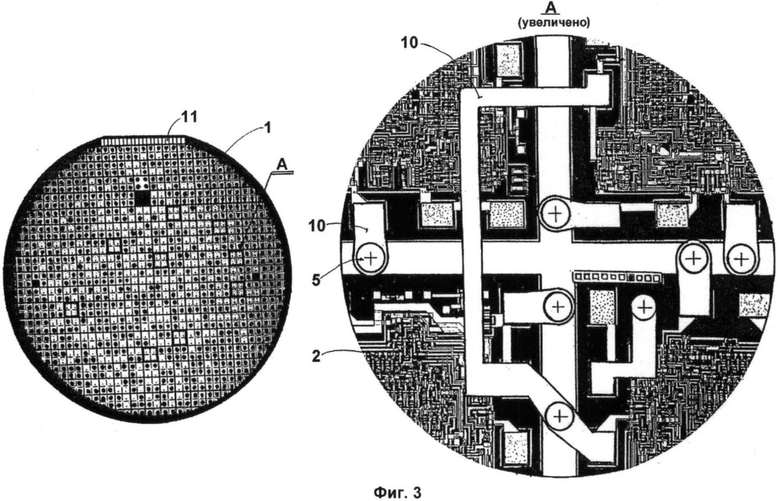

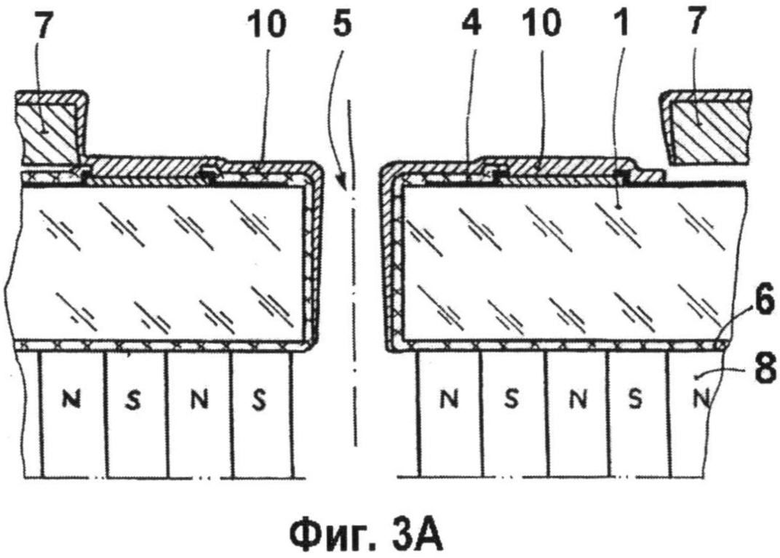

на фиг.3, 3A и 3B изображены полупроводниковая пластина с нанесенными проводниками и процесс нанесения проводников;

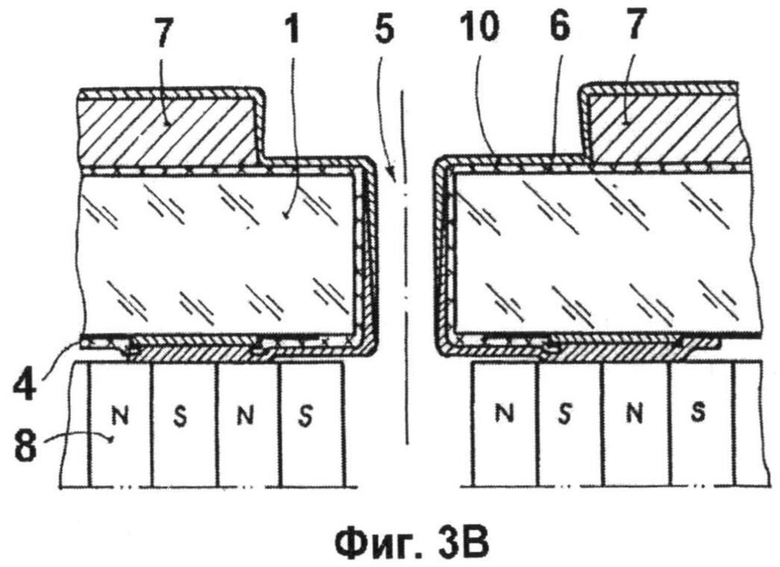

на фиг.4 изображена схема расположения полупроводниковой пластины для осуществления ЭТТ и контроля;

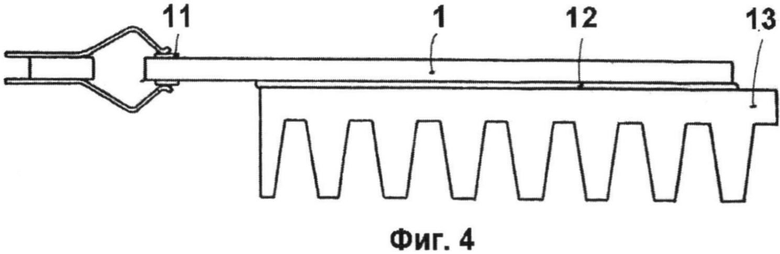

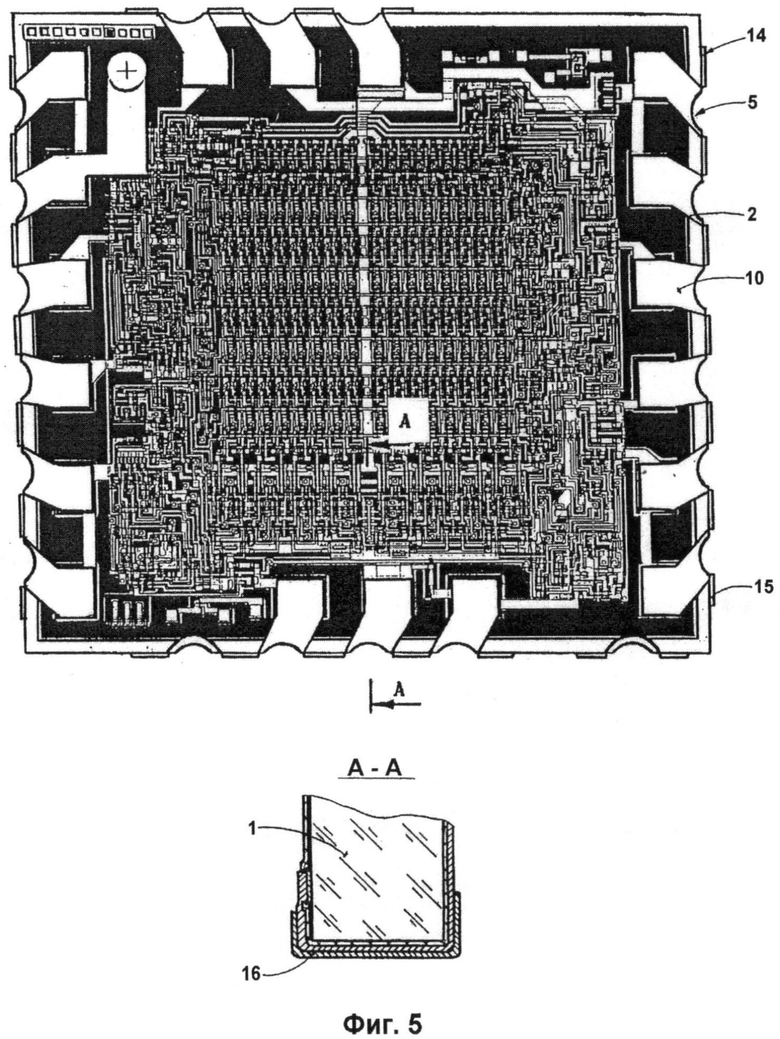

на фиг.5 изображен вариант кристалла-микроплаты для трехмерного модуля после вычленения из полупроводниковой пластины.

Осуществление изобретения

Полупроводниковая пластина 1 (фиг.1) со сформированными структурами 2 изготавливается традиционными методами. Каждый кристалл на полупроводниковой пластине 1 имеет контактные площадки 3. Полупроводниковая пластина 1 при изготовлении покрыта первичным изоляционным слоем 4, который вскрыт в местах расположения контактных площадок 3 и, как правило, в зонах будущего скрайбирования пластины 1 на кристаллы. В этих зонах, а также в других местах, где отсутствуют структуры 2 и проводники, их соединяющие, прошивают сквозные отверстия 5, которые впоследствии используют в качестве переходных отверстий при соединении проводников, находящихся на поверхностях полупроводниковой пластины 1, а также в качестве зон для внешних выводов при использовании кристаллов в качестве микроплат для трехмерных модулей.

Для электрической защиты вскрытых при прошивке сквозных отверстий 5 и возможных при этом сколов наносят вторичный изоляционный слой 6. На фиг.2A показан вариант нанесения неорганического изоляционного слоя 6 на лицевую поверхность полупроводниковой пластины 1 с одновременным покрытием сквозных отверстий 5 методом, например, пиролитического осаждения или магнетронного напыления через «свободную» маску 7, удерживаемую постоянными магнитами 8. На фиг.2B показан аналогичный вариант нанесения неорганического изоляционного слоя 6 на обратную поверхность полупроводниковой пластины 1 с одновременным вторичным покрытием сквозных отверстий 5. На фиг.2C показан вариант нанесения органического изоляционного слоя 6 на лицевую поверхность полупроводниковой пластины 1. При этом распыленный диэлектрик 9 под воздействием вакуума, приложенный с противоположной стороны, всасывается через сквозные отверстия 5, покрывая их сплошным слоем. Одновременно, благодаря завихрениям, частично покрывают изоляционным слоем 6 и обратную поверхность полупроводниковой пластины 1. При перевороте полупроводниковой пластины 1 (фиг.2D) полностью покрывается изоляционным слоем 6 обратная поверхность пластины 1 и вторично - сквозные отверстия 5.

Далее наносят на защищенные изоляционным слоем 6 поверхности полупроводниковой пластины 1, в соответствии с результатами проектирования, проводники 10 (фиг.3). В показанном на фиг.3A варианте, проводники 10 наносят методом вакуумного напыления через «свободные» маски 7, удерживаемые постоянными магнитами 8. При использовании магнетронного напыления или любого другого (при условии планетарного вращения полупроводниковой пластины 1 во время напыления), обеспечивается нанесение проводников не только на поверхности пластины 1, но и в сквозные отверстия 5. При перевороте пластины 1 (фиг.3B) и вторичном напылении покрываются сквозные отверстия 5 вторично. Одновременно на одну или обе поверхности полупроводниковой пластины 1 наносят выводные контакты 11 для внешнего электрического соединения полупроводниковой пластины 1 с приборами контроля и ЭТТ.

После этого полупроводниковая пластина 1 с нанесенными на нее проводниками 10 поступает на ЭТТ и полный контроль. При необходимости, обеспечивается теплоотвод от пластины 1 (фиг.4) путем нанесения на обратную поверхность пластины 1 теплопроводного состава 12 и использования средств теплоотвода 13. Далее полупроводниковая пластина 1 со структурами 2 разрезается на отдельные кристаллы, которые поступают на сборку ИС. Если предусматривается использование кристаллов в качестве кристаллов-микроплат 14 (фиг.5) для сборки трехмерных модулей, то сквозная разрезка ведется таким образом, чтобы сохранить проводник 10 в секторе отверстия 5. После этого на вскрытые зоны торцевых частей кристалла наносят локально изоляционный слой 15 и торцевую часть проводника совместно с частью проводников, выходящих на поверхности полупроводниковой пластины 1, обслуживают припоем 16. В таком виде кристалл-микроплата 14 поступает на сборку трехмерного модуля.

Данное изобретение может быть широко использовано в микроэлектронике при производстве любых электронных приборов. При этом обеспечивается сокращение производственных и материальных затрат и повышение надежности применяемых комплектующих электронных компонентов. Особенно применение данного изобретения будет эффективно при производстве многокристальных сборок и трехмерных модулей.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ ТРЕХМЕРНОГО МОДУЛЯ | 2012 |

|

RU2498454C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ЭЛЕКТРОННОГО ПРИБОРА | 2012 |

|

RU2498453C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2011 |

|

RU2475885C1 |

| КОНТАКТИРУЮЩЕЕ УСТРОЙСТВО | 2012 |

|

RU2498449C1 |

| СПОСОБ КОРПУСИРОВАНИЯ ЭЛЕКТРОННЫХ КОМПОНЕНТОВ | 2012 |

|

RU2503086C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОКОМПОНЕНТНОГО ТРЕХМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2001 |

|

RU2193260C1 |

| СПОСОБ СБОРКИ ТРЕХМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2012 |

|

RU2492549C1 |

| СПОСОБ ИСПЫТАНИЙ И КОНТРОЛЯ ЭЛЕКТРОННЫХ КОМПОНЕНТОВ | 2003 |

|

RU2272335C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ПОЛИМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2001 |

|

RU2193259C1 |

| ТРЕХМЕРНОЕ ЭЛЕКТРОННОЕ УСТРОЙСТВО | 2011 |

|

RU2488913C1 |

Изобретение относится к микроэлектронике и может быть использовано при производстве электронных приборов. В способе изготовления полупроводникового прибора в полупроводниковой пластине прошивают переходные сквозные отверстия, поверхности отверстий, образовавшиеся сколы, лицевую и обратную поверхности полупроводниковой пластины селективно покрывают изоляционным слоем, поверх изоляционного слоя наносят металлические проводники, необходимые для проведения электротермотренировки и полного контроля всех кристаллов, после электротермотренировки и полного контроля пластину разрезают на кристаллы, годные из которых используют для корпусирования. Изобретение обеспечивает групповую электротермотренировку и полный контроль кристаллов в составе полупроводниковой пластины, что значительно удешевляет производство полупроводниковых приборов. 8 з.п. ф-лы, 5ил.

1. Способ изготовления полупроводникового прибора, включающий формирование структур на полупроводниковой пластине, покрытие пластины изоляционным слоем со вскрытием контактных площадок, предварительный контроль кристаллов, разделение полупроводниковой пластины на отдельные кристаллы, их корпусирование, электротермотренировку и окончательный контроль, отличающийся тем, что проектируют разводку проводников для проведения электротермотренировки и предварительного контроля кристаллов по лицевой и обратной поверхностям полупроводниковой пластины, в результате чего в полупроводниковой пластине в зонах последующей резки пластины и других зонах, не занятых структурами и/или проводниками их соединяющими, прошивают переходные сквозные отверстия; поверхности сквозных отверстий, образовавшиеся сколы, лицевую и обратную поверхности полупроводниковой пластины селективно покрывают вторым изоляционным слоем; в соответствии с результатами проектирования, поверх нанесенного изоляционного слоя на лицевую, обратную поверхности полупроводниковой пластины и в отверстия наносят преимущественно методом вакуумного осаждения металлические проводники, необходимые для ЭТТ и полного контроля всех кристаллов, входящих в состав полупроводниковой пластины; удаляют проводники, идущие от забракованных при предварительном контроле кристаллов от общей разводки, нанесенной на полупроводниковую пластину; проводят групповую ЭТТ и полный контроль всех годных после предварительного контроля кристаллов в соответствии с техническими условиями на них; полупроводниковую пластину разделяют на отдельные кристаллы сквозной резкой, после чего направляют годные кристаллы на корпусирование.

2. Способ изготовления полупроводникового прибора по п.1, отличающийся тем, что при прошивке отверстий в полупроводниковой пластине лазерным методом применяют многоступенчатый метод прошивки или другие средства предотвращения разбрызгивания и выброса материала подложки полупроводниковой пластины на кромки отверстий и на поверхности пластины.

3. Способ изготовления полупроводникового прибора по п.1, отличающийся тем, что при прошивке отверстий в полупроводниковой пластине ультразвуковым методом, обработку ведут со стороны поверхности пластины, не содержащей структур.

4. Способ изготовления полупроводникового прибора по п.1, отличающийся тем, что при прошивке отверстий в полупроводниковой пластине методом химического травления, обработку ведут одновременно с противоположных поверхностей пластины с предварительным вскрытием зон травления.

5. Способ изготовления полупроводникового прибора по п.1, отличающийся тем, что второй неорганический изоляционный слой на поверхности отверстий, на лицевую и обратную поверхности пластины наносят преимущественно методом пиролитического осаждения или магнетронным напылением кремния в кислородной среде.

6. Способ изготовления полупроводникового прибора по п.1, отличающийся тем, что второй изоляционный слой выполняют из органического материала и наносят на поверхности отверстий, на лицевую и обратную поверхности пластины наносят преимущественно методом распыления органического диэлектрика с применением вакуумного отсоса.

7. Способ изготовления полупроводникового прибора по п.1, отличающийся тем, что после нанесения второго изоляционного слоя на обратной стороне полупроводниковой пластины производят формирование электронных компонентов, выполненных по тонкопленочной и/или толстопленочной технологии и необходимых для обеспечения ЭТТ и контроля.

8. Способ изготовления полупроводникового прибора по п.1, отличающийся тем, что одновременно с нанесением проводников формируют внешнюю контактную зону для присоединения внешнего кабеля, состоящую из множества выводных контактов, расположенных по периферийной зоне полупроводниковой пластины на одной или двух ее поверхностях.

9. Способ изготовления полупроводникового прибора по п.1, отличающийся тем, что в случае дальнейшего использования кристаллов в многокристальных сборках или в трехмерных модулях, при сквозной резке пластины на торцах кристаллов оставляют металлизированные впадины, соединенные проводниками между собой и/или с контактными площадками кристаллов; изолируют оголенные участки кристаллов; производят селективное горячее лужение проводников, расположенных во впадинах и частично - на поверхностях кристаллов.

| СПОСОБ ИЗГОТОВЛЕНИЯ И КОНТРОЛЯ ЭЛЕКТРОННЫХ КОМПОНЕНТОВ | 1997 |

|

RU2133522C1 |

| US 5504369 A, 02.04.1996 | |||

| US 5831445 A, 03.11.1998 | |||

| Шланговое соединение | 0 |

|

SU88A1 |

| Способ восстановления поврежденного ахиллова сухожилия | 1974 |

|

SU631149A1 |

Авторы

Даты

2014-04-10—Публикация

2012-07-27—Подача