Область техники, к которой относится изобретение

Изобретение связано, но не ограничено реализацией и использованием так называемых блоков защиты памяти, блоков управления памяти, кэшей инструкций, кэшей данных и кэшей в виде буферов ассоциативной трансляции, используемых в блоках управления памятью. Различные варианты выполнения данного изобретения подходят для использования во многих 32- и 64-битовых процессорных средах. Это включает в себя, но не ограниченно киберфизическими вычислительными средами, которые работают в реальном времени с особыми требованиями к защите и безопасности, а также вычислительными средами с сильно ограниченными ресурсами.

Уровень техники

Ссылка в данном описании на опубликованный документ не должна рассматриваться, как признание, что содержание того документа является частью общедоступных сведений опытного адресата данного описания. Примеры архитектуры управления памятью приведены в [1], [2] и [3]. Технические термины, используемые для описания архитектуры различных технологий блоков защиты памяти (БЗП) и блоков управления памятью (БУП), иногда имеют противоречащие определения. В данном описании, включая формулу изобретения:

- «Включает в себя» и «включающий в себя» используются для указания на наличие заявленных функций, систем, этапов или компонентов, но не исключают наличие или добавление одной или нескольких других функций, систем, этапов, компонентов.

- Запоминающее устройство (например, 118 на Фиг. 1), объединенное с контроллером памяти (например, 115 на Фиг. 1), можно описать на более высоком уровне генерализации, как запоминающее устройство.

- Периферийное устройство может иметь (например, сетевой контроллер 105 на Фиг. 1) или не иметь (например, блок криптоускорителя) контакты внешних вводов-выводов. Периферийное устройство включает в себя не менее одного соединительного интерфейса, при этом каждый соединительный интерфейс является либо главным соединительным портом, либо соединительным портом назначения.

- Шина является одним из видов соединителя. Коммутатор является одним из видов соединителя.

- Блок прямого доступа к памяти память-память (ПДП ПП) (например, 140 на Фиг. 1) является программируемой аппаратной цепью, специально оптимизированной для выдачи запросов на передачу данных памяти через один или несколько главных соединительных портов (например, 143 и 144 на Фиг. 1) с целью считывания значения из памяти, хранящегося по одному адресу, и записи этого значения в другой адрес памяти. ПДП ПП является подчиненным устройством под контролем другого, главного устройства (например, 110 или 194 на Фиг. 1). Хорошо известным пример такого контроллера ПДП ПП является Intel 8237А. Блок ПДП ПП может иметь и дополнительные возможности, связанные с перемещением данных памяти, такие как считывание непрерывных областей памяти из запоминающего устройства и запись каждого слова данных на тот же адрес периферийного устройства с распределением памяти. Блок ПДП ПП можно описать, как программируемый блок прямого доступа к памяти (ППДП).

- Блок защиты памяти (БЗП) получает запрос передачи данных памяти, связанный с вводным адресным пространством, и генерирует запросы передачи данных памяти, связанные с выводным адресным пространством. БЗП характеризуется тем, что (а) разрешает управлять доступом к одному или нескольким регионам вводного адресного пространства, и (b) БЗП всегда применяет тождественное преобразование между адресом запроса передачи данных памяти в вводном адресном пространстве и адресом соответствующего запроса передачи данных памяти в выводном адресном пространстве. Архитектура некоторых БЗП специально спроектирована для поддержки отображения двух или более описателей региона в одном и том же непрерывном регионе вводного адресного пространства во время выполнения.

- Блок управления памяти (БУП) получает запрос передачи данных памяти, связанный с вводным адресным пространством, и в ответ генерирует соответствующий запрос передачи данных памяти, связанный с выводным адресным пространством. БУП характеризуется тем, что (а) разрешает управлять доступом к одному или нескольким регионам вводного адресного пространства, и (b) БУП адаптирован для трансляции адреса запроса передачи данных памяти, ассоциированного с вводным адресным пространством, и адреса соответствующего запроса передачи данных памяти в выводном адресном пространстве.

- Правильно сформированный запрос передачи данных памяти - это любой запрос передачи данных памяти, который правильно выполняет требования ассоциированного протокола связи для запроса передачи данных памяти. Прием правильно сформированного запроса передачи данных памяти подразумевает, что запрос не был неправильно сформирован при выдаче, и что запрос не был поврежден в процессе передачи.

Во многих публикациях, описывающих технологии управления памятью, «виртуальное адресное пространство» отображается на «физическое адресное пространство». Данная терминология является однозначной при одном уровне средств трансляции адресов для программного обеспечения, выполняющегося на процессоре общего назначения, используемом в заданной архитектуре ЭВМ. В данном описании мы используем терминологию - «вводное адресное пространство» отображается на «транслированное адресное пространство». Последняя терминология может последовательно использоваться для каждого уровня средств трансляции адресов памяти в архитектуре ЭВМ, имеющей два или более уровней средств трансляции адресов. Последняя терминология также может последовательно использоваться для средств трансляции адресов памяти, адаптированных для приема запросов передачи данных памяти от процессоров общего назначения, графических процессоров и других видов главных соединительных периферийных устройств.

В тексте данного описания, включая формулу изобретения, термины страница, дескриптор страницы, фрейм, сегмент, дескриптор сегмента и дескриптор диапазона имеют следующие значения:

- «Фрейм» размером N байт определяет непрерывный регион памяти транслированного адресного пространства длиной N байт и начинающийся с границы байта N.

- «Страница» размером N байт определяет непрерывный регион памяти вводного адресного пространства длиной N байт и начинающийся с границы байта N. «Дескриптор страницы» описывает страницу памяти, ассоциированную с вводным адресным пространством. Страница памяти вводного адресного пространства может отображаться на фрейм памяти транслированного адресного пространства.

- «Сегмент» размером N байт определяет непрерывный регион памяти вводного адресного пространства длиной N байт, начинающийся с границы байта О. Выделенная часть сегмента может иметь размер менее N байт и начинаться с относительного адреса, расположенного внутри этого сегмента. Терминология «сегмент переменной длины» подразумевает, что длина выделенной части сегмента может быть разной. Выделенная часть сегмента может быть отображена на непрерывный регион памяти на границе байта Р в транслированном адресном пространстве. Значения О и Р также могут быть разными. Отношение между значениями N, О и Р изменяется в зависимости от параметров реализованной схемы сегментирования. На практике, некоторые архитектуры ЭВМ предназначены для использования средств, реализованных в оборудовании, для предотвращения перекрытия выделенных частей двух программируемых сегментов в вводном адресном пространстве. Правильная работа других архитектур ЭВМ может потребовать управляющего ПО, чтобы убедиться, что выделенные части двух программируемых сегментов не перекрываются в вводном адресном пространстве во время выполнения. «Дескриптор сегмента» описывает сегмент памяти, ассоциированный с вводным адресным пространством.

- «Дескриптор диапазона» размером N байт определяет непрерывный регион памяти вводного адресного пространства длиной N байт. Диапазон может быть задан нижней границей адресов и верхней границей адресов, или нижней границей адресов и длиной диапазона. Если в заданном дескрипторе диапазона не активирована программируемая трансляция адресов, диапазон в вводном адресном пространстве отображается при помощи тождественного преобразования на непрерывный регион памяти в выводном адресном пространстве. Дескриптор диапазона может начинаться и заканчиваться на мелкоструктурных границах (например, 64-битовая структурированность) в вводном адресном пространстве. В качестве альтернативы, дескриптор диапазона может начинаться и заканчиваться на крупноструктурных границах в вводном адресном пространстве (например, кибибайтовая структурированность). В коммерческих массовых реализациях БЗП распространено явное разрешение двум или более дескрипторам диапазона, где эти дескрипторы диапазона не имеют способностей программируемой трансляции адресов, ассоциироваться с перекрывающимися регионами памяти в вводном адресном пространстве.

В тексте данного описания, включая заявки, строка кэша, блок кэша, субблок кэша и тэг кэша имеют следующие определения:

- «Строка кэша» - это непрерывный регион памяти. Традиционно, в архитектурах ЭВМ общего назначения, строка кэша имеет длину от 8 до 32 байт. В принципе, строка кэша может иметь ту же длину, что и максимальная длина страницы или сегмента. Каждая строка кэша ассоциируется с тэгом кэша. В контексте строк кэша, «тэг кэша» хранит метаданные о строке кэша. Метаданные могут включать в себя, но не ограничивается, их адрес в вводном адресном пространстве и/или их адрес в транслированном адресном пространстве, а также статус данного кэша.

- «Блок кэша» - это непрерывный регион памяти, разделенный на субблоки кэша. Традиционно, в архитектурах ЭВМ общего назначения, блок кэша включает в себя от 2 до 4 субблоков кэша. Традиционно, в архитектурах ЭВМ общего назначения, субблок кэша имеет длину от 8 до 32 байт. Каждый блок кэша ассоциируется с тэгом кэша. В контексте блоков кэша, тэг кэша хранит метаданные о блоке кэша. Метаданные могут включать в себя, но не ограничивается, их адрес в вводном адресном пространстве и/или их адрес в транслированном адресном пространстве, а также статус данных субблоков кэша.

В тексте данного описания, включая формулу изобретения, «программируемый блок обработки запросов передачи данных памяти» (ПОЗПДП) м «дескриптор региона» имеют следующие определения:

- Блок ПОЗПДП адаптирован для приема и обработки запросов передачи данных памяти в соответствии с различными политика, при это каждый запрос передачи данных памяти ассоциируется с конкретным адресным пространством, а каждое адресное пространство ассоциируется с определенными правилами, применяемыми этим блоком ПОЗПДП. «Дескриптор региона» используется для ассоциации различных правил с конкретным регионом конкретного адресного пространства, ассоциированного с конкретными случаями блока ПОЗПДП. Например:

дескриптор региона может быть или не быть адаптирован с одним или несколькими полями контроля доступа;

дескриптор региона может быть или не быть адаптирован с одним или несколькими полями контроля доступа;

дескриптор региона может быть или не быть адаптирован с одним или несколькими полями трансляции адреса; и

дескриптор региона может быть или не быть адаптирован с одним или несколькими полями трансляции адреса; и

дескриптор региона может быть или не быть адаптирован с полями, которые модифицируют поведение по умолчанию подсистемы памяти, которая получает запросы передачи данных памяти, отправленные блоком ПОЗПДП (например, посредством поправки политики записи кэша и/или политики запроса памяти).

дескриптор региона может быть или не быть адаптирован с полями, которые модифицируют поведение по умолчанию подсистемы памяти, которая получает запросы передачи данных памяти, отправленные блоком ПОЗПДП (например, посредством поправки политики записи кэша и/или политики запроса памяти).

- Регион адресного пространства, ассоциированный с дескриптором региона:

может быть или не быть ограничен в отношении конкретного субнабора всех возможных базовых относительных адресов в рамках адресного пространства; и

может быть или не быть ограничен в отношении конкретного субнабора всех возможных базовых относительных адресов в рамках адресного пространства; и

может быть или не быть ограничен в отношении конкретного субнабора всех возможных длин региона.

может быть или не быть ограничен в отношении конкретного субнабора всех возможных длин региона.

В свою очередь поля «дескриптора региона» могут быть адаптированы для реализации различных дескрипторов. Это включает в себя, но не ограничивается: дескрипторы страниц; дескрипторы сегментов; дескрипторы буфера динамической трансляции; дескрипторы диапазона без программируемой трансляции адресов; дескрипторы диапазона с программируемой трансляцией адресов; и тэги кэша.

Очевидно, что конкретные поля заданного дескриптора региона определяются специально для данного случая дескриптора региона.

Блок ПОЗПДП определяется независимо одного или нескольких главных соединителей, которые адаптированы для выдачи запросов передачи данных памяти на один или несколько целевых соединительных портов данного блока ПОЗПДП. Посредством неограничивающего примера, блок ПОЗПДП, реализующий функциональность БУП, может быть адаптирован для использования в качестве частного блока управления памятью для операций ввода-вывода (БУПВВ) для одного главного соединительного периферийного устройства без потери универсальности. Более того, блок ПОЗПДПЮ реализующий функции БУП, может быть адаптирован для использования общего БУПВВ, совместного используемого через множественные главные соединительные периферийные устройства без потери универсальности.

В тексте данного описания, включая формулу изобретения, «программируемый дескриптор региона» определяется как дескриптор региона, где одно или несколько полей этого дескриптора региона может быть настроено программно.

Ранние схемы БУП для управления оперативной памятью компьютерных архитектур типично адаптировались для использования с оперативными запоминающими устройствами малой емкости.

По мере увеличения емкости физической памяти использовались схемы БУП, основанные на разных принципах, для преодоления различных воспринимаемых или фактических ограничений [1], [2] этих более ранних схем БУП, предназначенных для малых объемов хранения.

Насколько известно автору, все опубликованные схемы БУП, поддерживающие большие вводные адресные пространства с возможностью мелкоструктурного выделения памяти, используют (управляемые программно или аппаратно) буферы динамической трансляции (БДТ). Эти БДТ используются для кэширования относительно малого числа из потенциально очень большого количества дескрипторов регионов, которые могут быть ассоциированы с вводным адресным пространством. Рассмотрим архитектуру VAX-11/780 [3]. Схема БУП VAX-11/780 требует 8388608 дескрипторов региона для выделения всего 32-битового вводного адресного пространства [2]. Некоторые реализации VAX-11/780 использовали унифицированные БДТ для кэширования до 128 из максимально возможных 8388608 дескрипторов региона [2]) быстродействующей памяти, и хранили разрешенные дескрипторы регионов в одной или нескольких таблицах в относительно более медленном основном запоминающем устройстве. Впоследствии, насколько известно автору, отрасль фокусировалась преимущественно на применении двух (или более) уровней косвенной адресации (индексированные схемы, хэш-схемы, хэши списков указателей) для поиска дескрипторов региона с целью улучшения схемы управления потенциально очень большим числом разрешенных дескрипторов региона. Отраслевая тенденция применения двух или более уровней косвенной адресации направлена на преодоления различных технических сложностей, выявленных в одноуровневых трансляционных архитектурах, таких как архитектура VAX-11/780 [2]. Насколько известно автору, все опубликованные реализации схем БУП, поддерживающие два или более уровней косвенной адресации для получения доступа к листовому дескриптору региона в 32- или 64-битовом адресном пространстве, используют (программно или аппаратно управляемые) БДТ для ускорения своей работы. Хорошо известно, что использование БДТ для кэширования дескрипторов региона в комбинации с кэшем данных значительно повышает сложность выполнения анализа статической синхронизации программного обеспечения, выполняемого в ядре процессора, имеющего разрешенный кэш данных и разрешенные возможности БДТ.

Существует длительная потребность в архитектуре БУП, имеющей низкое значение задержки, высокую пропускную способность, работу с постоянным временем с поддержкой относительно мелкоструктурного выделения памяти в 32- и 64-битовом вводном адресном пространстве. На рынке микроконтроллеров также существует потребность в блоке ПОЗПДП, который может работать, как блок защиты памяти (БЗП) и как БУП для запуска операционных систем реального времени (ОСРВ) с высоким уровнем безопасности и доступности. Это обусловлено тем, что многие ОСРВ с высоким уровнем безопасности и доступности полагаются на доступность аппаратного БУП с возможностью трансляции адресов.

Также имеется давно ощущаемая потребность в средствах для экономически эффективного ускорения перепрограммирования дескрипторов региона с более низким уровнем безопасности и доступности для поддержки ускоренного обмена процессов и повышенной производительности системы.

Также имеется давно ощущаемая потребность в поддержке двух уровней трансляции адресов, при которой каждый уровень трансляции адресов контролируется разным программным обеспечением (например, гипервизор контролирует первый уровень схемы БУП, а операционная система, управляемая гипервизором, контролирует второй уровень схемы БУП), что подходит для использования в системах реального времени с возможностью статистического анализа времени.

В средах с ограниченными ресурсами (таких как «Интернет вещей»), которые должны выполнять основанные на страницах схемы БУП для поддержки операционных систем общего назначения, таких как Linux, также существует рыночная потребность в инновационной архитектуре БУП, требующей для реализации меньший объем аппаратных цепей, чем традиционная основанная на страницах БУП, а также поддерживающая более быстрое выполнение программного обеспечения после обмена содержимого пользовательского адресного пространства.

Предпочтительный вариант выполнения данного изобретения предусматривает новые и инновационные решения для удовлетворения рыночных потребностей, описанных выше.

Раскрытие изобретения

Имеется давно ощущаемая потребность в средствах для экономически эффективного ускорения перепрограммирования дескрипторов региона с более низким уровнем безопасности и доступности для поддержки ускоренного обмена процессов и повышенной производительности системы.

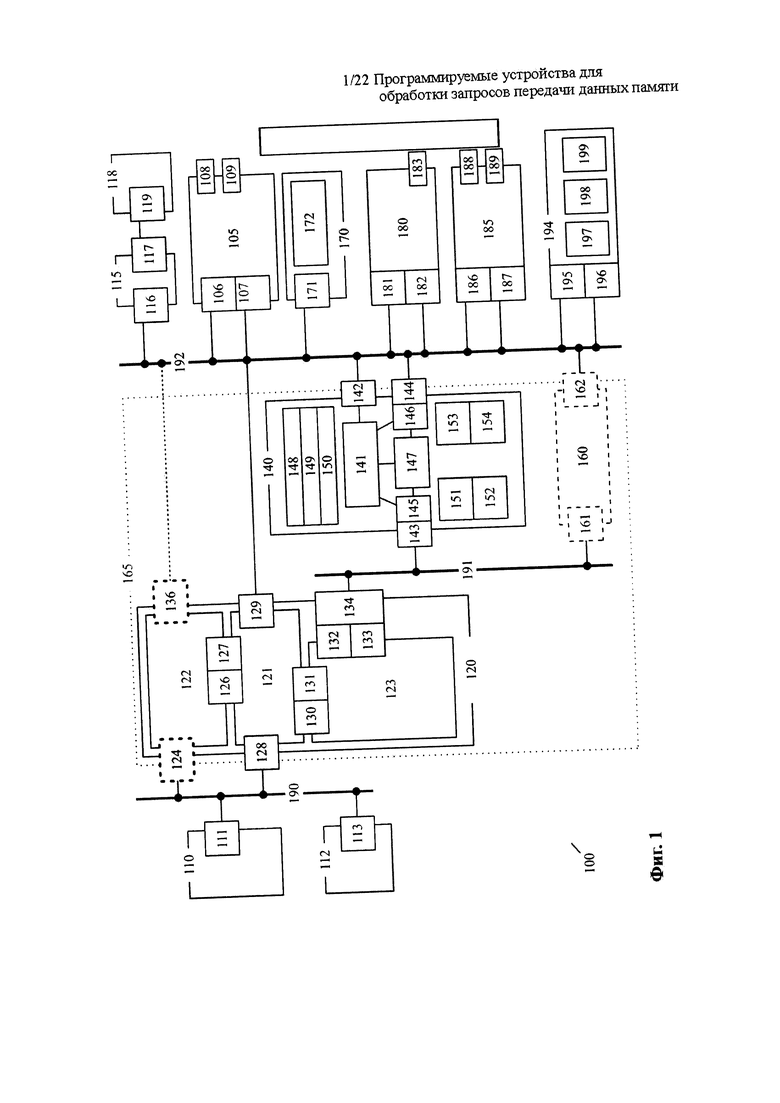

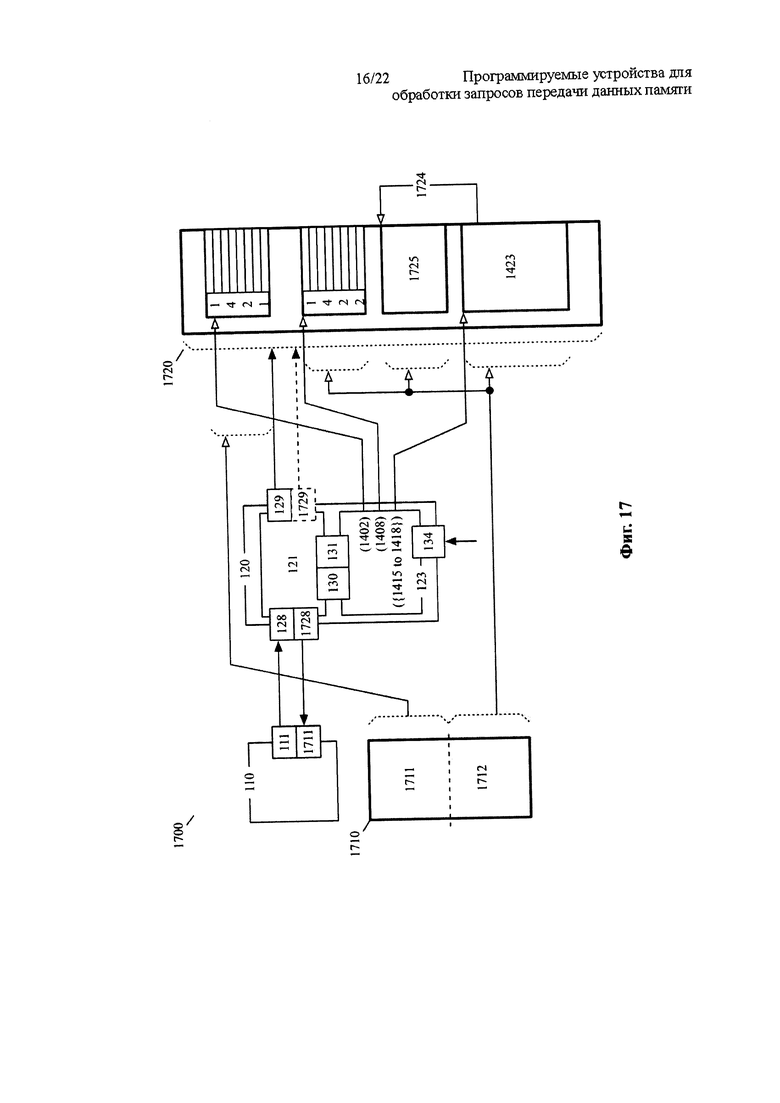

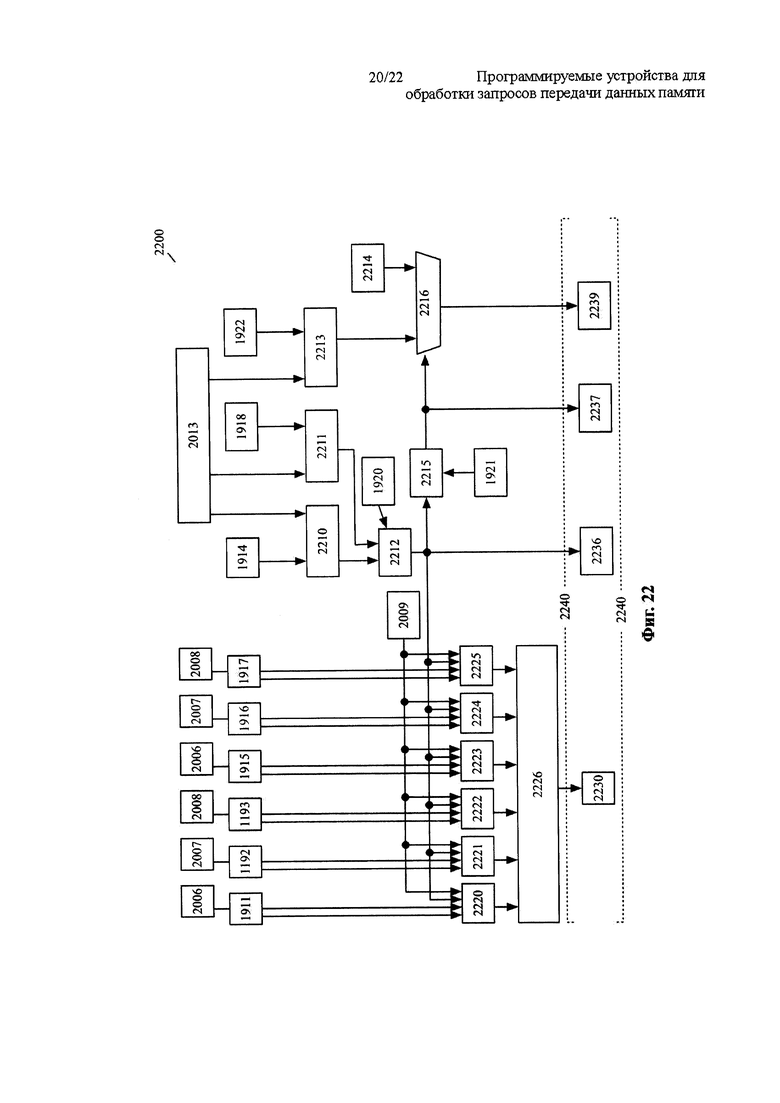

На Фиг. 1 представлена блок-схема, иллюстрирующая части аппарата (100) для обработки данных для предпочтительного варианта выполнения данного изобретения. Аппарат (100) включает в себя процессорный модуль (110). Этот процессорный модуль (110) оснащен главным соединительным портом (111), подключенным к интерконнекту (190). Пример процессорного модуля включает в себя, но не ограничивается: 16-б 32- или 64-битовое ядро процессора общего назначения; модуль графического процессора; или специализированный процессорный модуль. В принципе, главное соединительное периферийное устройство может использоваться вместо процессорного модуля (110).

Аппарат (100) также включает в себя энергонезависимое запоминающее устройство (112). Энергонезависимое запоминающее устройство (112) подключено через свой целевой соединительный порт (113) к межкомпонентному соединению (190).

Аппарат (100) также включает в себя программируемый блок обработки запросов передачи данных памяти (ПОЗПДП) (120). Примеры функций, которые может реализовать ПОЗПДП, включают в себя, но не ограничивается основанный на страницах блок управления памятью (БУП); основанный на страницах БУП с буфером динамической трансляции для кэширования дескрипторов страниц, к которым недавно осуществлялся доступ; основанный на сегментах БУП; основанный на сегментах БУП с буфером динамической трансляции для кэширования дескрипторов сегментов, к которым недавно осуществлялся доступ; блок защиты памяти (БЗП); и кэш, в котором тэги кэша и данные кэша хранятся в данных программируемой конфигурации запоминающего устройства (123) ПОЗПДП (120).

Тэг кэша может включает в себя, но не ограничивается, разные из следующих полей: однобитовое поле наличия строки кэша; (32-битовое/64-битовое) вводное адресное поле; (32-битовое/64-битовое) транслированное адресное поле; многобитовые поля кодировки правил контроля доступа для задач, выполняемых пользовательским программным обеспечением; многобитовые поля кодировки правил контроля доступа для задач, выполняемых системным программным обеспечением; многобитовые поля кодировки правил контроля доступа для главных соединительных периферийных устройств; однобитовый флаг «наличия строки кэша»; поле текущей маски с 8-, 16- и/или 32-битовым структурированием; флаг «недавно считанной строки кэша»; однобитовый флаг «строки кэша, ожидающей записи»; поле маски изменения с 8-, 16- и/или 32-битовым структурированием; многобитовое поле режима хэширования (например, сквозная запись, обратная запись и т.д.); многобитовое поле запроса памяти для задачи требований к непрерывности памяти много-шинных мастер-сред.

Аппарат (100) также включает в себя:

- Программируемый блок прямого доступа к памяти (ППДП) (140).

- Дополнительный односторонний соединительный мост (160). Главный соединительный порт (161) этого моста (160) подключен к межкомпонентному соединению (191). Целевой соединительный порт (162) этого моста (160) подключен к межкомпонентному соединению (192).

- Контроллер SDRAM (115). Целевой соединительный порт (116) этого контроллера SDRAM (115) подключен к межкомпонентному соединению (192).

- Запоминающее устройство SDRAM (118). Целевой порт (119) этого запоминающего устройства SDRAM (118) подключен к главному порту контроллера SDRAM (115).

- Встроенное в чип запоминающее устройство SDRAM (170) с целевым соединительным портом (171) и средствами хранения (172).

- Периферийное устройство с сетевым интерфейсом (105). Оба, целевой соединительный порт (106) и главный соединительный порт (107) этого периферийного устройства с сетевым интерфейсом (105) подключены к межкомпонентному соединению (192).

- Периферийный мультимедийный интерфейс высокой четкости (HDMI) (180). Оба, целевой соединительный порт (181) и главный соединительный порт (182) этого периферийного устройства HDMI (180) подключены к межкомпонентному соединению (192).

- Периферийный двойной порт (188, 189) стандарта USB (универсальная последовательная шина) (185). Оба, целевой соединительный порт (186) и главный соединительный порт (187) этого периферийного устройства USB (185) подключены к межкомпонентному соединению (192).

- Процессор общего назначения (194) с встроенным ядром (199), подсистемой БУП (197) и подсистемой кэша (199). Этот процессор общего назначения (194) подключен к межкомпонентному соединению (292) через главный соединительный порт (195) и целевой соединительный порт (196).

Совместно программируемый блок обработки запросов передачи данных памяти (ПОЗПДП) (120), программируемый блок прямого доступа к памяти (ППДП), дополнительный мост (160) и межкомпонентное соединение (191) можно описать, как составной программируемый блок обработки запросов передачи данных памяти (165).

В данном педагогическом описании процессорный модуль (110) адаптирован для выдачи запросов передачи данных памяти и/или запросов передачи данных кода с главного соединения (111) на межкомпонентное соединение (190).

Программируемый блок обработки запросов передачи данных памяти (ПОЗПДП) (120) оснащен контроллером (121), который адаптирован для получения доступа к блоку динамического контроля (122) через порт записи (126) и порт считывания (127). Блоку динамического контроля (122) содержит набор одного или нескольких управляющих регистров (не показано на иллюстрации). Блок ПОЗПДП (120) адаптирован для получения доступа к запоминающему устройству (123). Запоминающее устройство (123) адаптировано для хранения программируемых данных конфигурации для блока ПОЗПДП (120). Эти программируемые данные конфигурации адаптированы для хранения не менее двух элементов программируемых дескрипторов региона. Блок управления (121) также адаптирован для получения запросов передачи данных памяти через целевое соединение (128), подключенное к межкомпонентному соединению (190). Блок управления (121) также адаптирован для отправки запросов передачи данных памяти через главное соединение (129), подключенное к межкомпонентному соединению (192). Блок управления (121) также адаптирован для обработки запросов передачи данных памяти, ассоциированных к первым адресным пространством, полученным через целевой соединительный порт (128) в соответствии с, как минимум, одним правилом, ассоциированным с этим первым адресным пространством, которые закодированы в как минимум двух или более элементах программируемого дескриптора региона, хранящихся в программируемых данных конфигурации запоминающего устройства (123) на момент обработки.

Программируемый блок обработки запросов передачи данных памяти (ПОЗПДП) (120) оборудован целевым соединительным портом (134), который адаптирован для получения запросов передачи данных памяти для получения доступа к части элементов дескриптора региона, хранящихся в программируемых данных конфигурации в запоминающем устройстве (123). Это включает в себя средства считывания (132) и средства записи (133) для разрешения и обработки правильно сформированных запросов передачи данных памяти, адресованных на действительный адрес памяти в этом запоминающем устройстве (123) главным соединением (143) блока ППДП (140).

В предпочтительном варианте выполнения данного изобретения целевой соединительный порт (134) программируемого блока обработки запросов передачи данных памяти (ПОЗПДП) (120) также адаптирован для приема запросов передачи данных памяти для получения доступа к части программируемых данных конфигурации, хранящихся в запоминающем устройстве (123), не являющихся дескриптором региона.

Блок ПОЗПДП (120) оснащен целевым соединительным портом (124), адаптированным для приема запросов передачи данных памяти на запись и считывание для блока динамического управления (122). Этот целевой соединительный порт (124) подключен к межкомпонентному соединению (190). В качестве альтернативы, блок ПОЗПДП (120) оснащен целевым соединительным портом (136), адаптированным для приема запросов передачи данных памяти на запись и считывание для блока динамического управления (122). Этот целевой соединительный порт (136) подключен к межкомпонентному соединению (192).

Программируемый блок прямого доступа к памяти (ППДП) (140) оборудован главным соединительным портом (143), который подключен к межкомпонентному соединению (191), вторым главным соединительным портом (144), который подключен к межкомпонентному соединению (192), и целевым соединительным портом (142), который подключен к межкомпонентному соединению (192). Блок ППДП (140) адаптирован для использования двунаправленного модуля FIFO (первый пришел-первый ушел) (147). Первый порт этого модуля FIFO (147) подключен к первой вспомогательной цепи управления (145). Второй порт этого модуля FIFO (147) подключен ко второму вспомогательному блоку управления (146). Первая вспомогательная цепь управления (145) адаптирована для выдачи запросов передачи данных памяти на главное соединение (143) и использует счетчик (151) и текущий индекс адресов памяти (152). Вторая вспомогательная цепь управления (146) адаптирована для выдачи запросов передачи данных памяти на главное соединение (144) и использует счетчик (153) и текущий индекс адресов (154).

Блок ППДП (140) адаптирован для программирования одним или несколькими запросами передачи данных памяти, полученными через целевой соединительный порт (142). На данной педагогической иллюстрации блок ППДП (140) имеет один программируемый дескриптор передачи память-память (148, 149, 150). Дескриптор передачи память-память (148, 149, 150) имеет три поля: Поле адреса исходной памяти (148), поле адреса целевой памяти (149) и поле длины передачи памяти (150). Дескриптор передачи память-память программируется посредством записи в поля (148), затем (149) и затем (150), именно в такой последовательности.

Блок ППДП (140) операции передачи память-память начинается после того, как все три поля (148, 149, 150) дескриптор передачи память-память были записаны. Операция выполняется следующим образом. Значение исходного адреса (148) загружается в текущий указатель адреса (151, 153) одной из двух вспомогательных цепей управления (145, 146). Целевой адрес (149) загружается в текущий указатель адреса (151, 153) второй из двух вспомогательных цепей управления (145, 146). Например, старший бит исходного адреса (148) может быть использован для указания, с каким главным портом (143, 144) блока ППДП (140) ассоциирован исходный адрес. В качестве альтернативы, блок ППДП (140) адаптирован для сравнения исходного адреса с разными диапазонами адресов памяти, ассоциированными с каждым из его главных портов (143, 144), чтобы определить, с каким главным портом ассоциирован этот исходный адрес. Затем значение поля длины передачи памяти (150) копируется в оба поля счетчика (151, 153). Модуль FIFO (147) обнуляется, чтобы убедиться, что в очереди данного модуля FIFO отсутствуют какие-либо элементы данных. Две вспомогательные цепи управления (145, 156) затем получают инструкции от блока управления (141) начать считывание или запись, необходимые для успешного выполнения запрошенной операции передачи память-память. Слова памяти, считанные с исходного адреса, добавляются в модуль FIFO (147). Слова памяти, предназначенные для записи по целевому адресу, выталкиваются из модуля FIFO (147). 3начение счетчиков (251) и (253) уменьшается в соответствии с объемом считанных или записанных данных, соответственно. Процесс вспомогательного блока управления (145) завершается, когда значение его поля счетчика (151) равно нулю. Процесс вспомогательного блока управления (146) завершится, когда значение его поля счетчика (153) будет равно нулю.

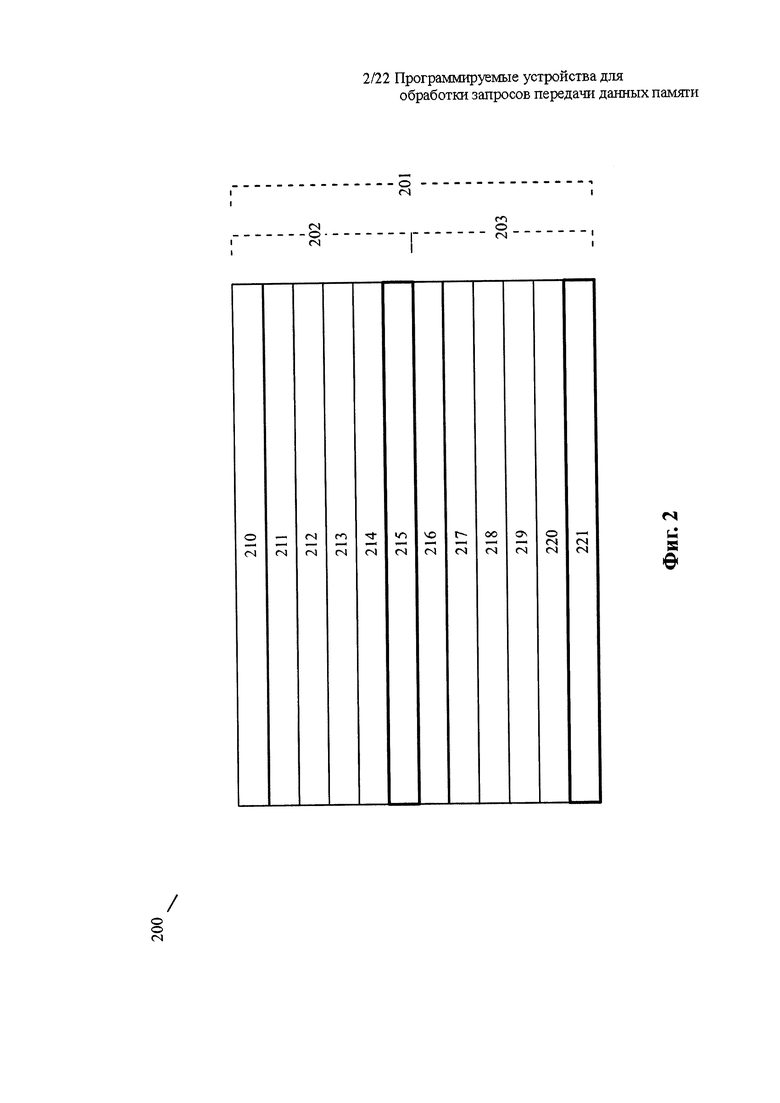

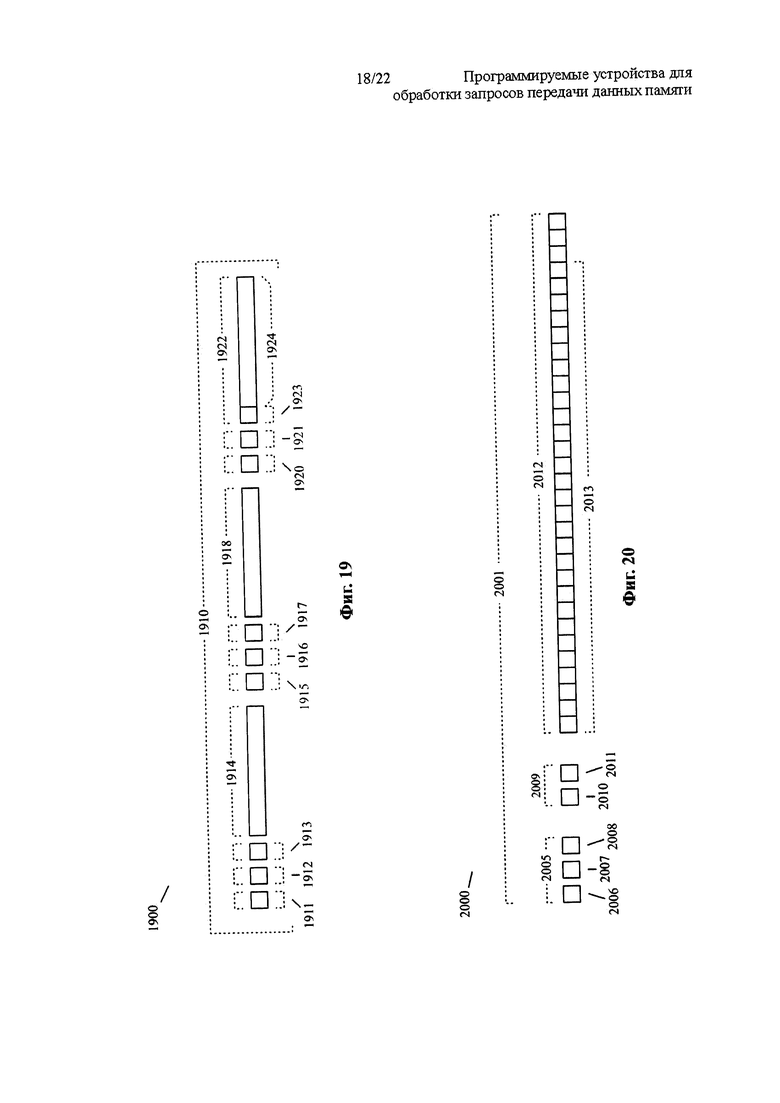

На Фиг. 2 представлена блок-схема (200), иллюстрирующая разбивку адресного пространства (201) для получения доступа к программируемым данным конфигурации, хранящимся в запоминающем устройстве (123) блока ПОЗПДП (120), показанного на Фиг. 1 в соответствии с предпочтительным вариантом осуществления данного изобретения. Это адресное пространство памяти (201) разделено на 12 полей (210-221). Длина каждого поля (210-221) составляет 32 бита. Это адресное пространство (201) логически разделено на:

- первый непрерывный набор (202) 6 полей (210-215), ассоциированных с конфигурацией системной части адресного пространства целевого порта (128) блока ПОЗПДП (120); и

- второй непрерывный набор (203) 6 полей (216-221), ассоциированных с конфигурацией пользовательской части адресного пространства целевого порта (128) блока ПОЗПДП (120).

Поле (210) хранит конфигурацию и/или информацию о состоянии, ассоциированную с системным адресным пространством (202). Поля (211)-(214) адаптированы для хранения как минимум одного дескриптора региона, ассоциированного с системным адресным пространством. Блок ПОЗПДП (120) адаптирован так, чтобы при записи любого значения в поля (210)-(214) блок управления ПОЗПДП (121) уведомляется, что данные конфигурации для системной части (202) адресного пространства на данный момент перепрограммируются. Блок ПОЗПДП адаптирован так, чтобы при записи любого значения в поле (215) блок управления ПОЗПДП (121) уведомляется, что перепрограммирование данных конфигурации для системной части адресного пространства завершилось.

Поле (216) хранит конфигурацию и/или информацию о состоянии, ассоциированную с пользовательским адресным пространством (203). Поля (216)-(221) адаптированы для хранения как минимум одного дескриптора региона, ассоциированного с пользовательским адресным пространством. Блок ПОЗПДП (120) адаптирован так, чтобы при записи любого значения в поля (216)-(221) блок управления ПОЗПДП (121) уведомляется, что данные конфигурации для пользовательской части (203) адресного пространства на данный момент перепрограммируются. Блок ПОЗПДП (120) адаптирован так, чтобы при записи любого значения в поле (221) блок управления ПОЗПДП (121) уведомляется, что перепрограммирование данных конфигурации для пользовательской части адресного пространства завершилось.

Эта новая конфигурация адресного пространства (201) программируемых данных конфигурации, хранящихся в запоминающем устройстве (123) блока ПОЗПДП (120), разрешает: обновлять все системные данные при помощи операции непрерывной передачи память-память (через поля 210-215); обновлять все пользовательские данные при помощи операции непрерывной передачи память-память (через поля 216-221); и обновлять системные и пользовательские данные при помощи операции непрерывной передачи память-память (через поля 210-221).

Как преимущество, это позволяет очень быстро перепрограммировать данные конфигурации блока ПОЗПДП (120) блоком ППДП (140) новым способом.

В дальнейшем предпочтительном варианте выполнения данного изобретения, когда аппарат (100) был обнулен, блок ПОЗПДП (120) сбрасывает состояние своего блока динамического контроля (122) и сбрасывает состояние своих программируемых данных конфигурации (123). Более того, режим работы блока ПОЗПДП (120) по умолчанию заключается в ретрансляции запросов передачи данных памяти, полученных на целевой порт (128), без изменения главного порта (129) и ретрансляции ответов на запросы передачи памяти, полученных на главный порт (129), без изменения целевого порта (128). После этого блок ПОЗПДП будет готов к приему запросов передачи данных памяти на порт (124), (136) и (134) для конфигурации своей работы.

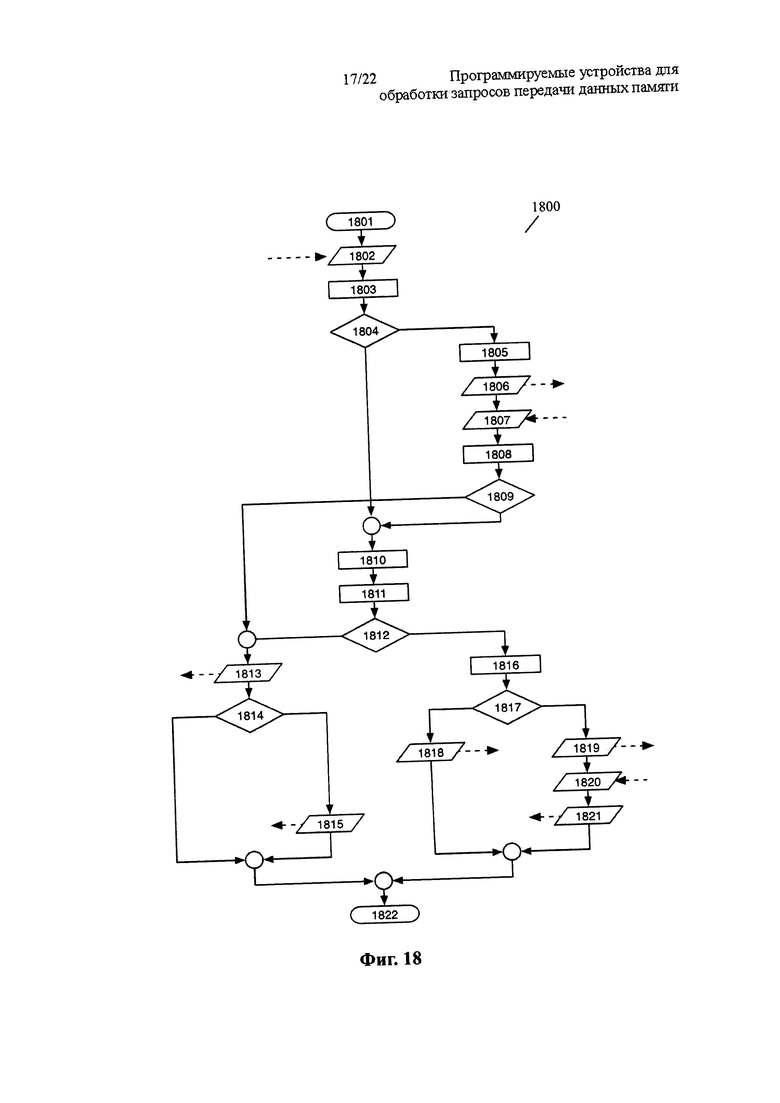

На Фиг. 3 приведена блок-схема (300), иллюстрирующая операцию передачи память-память, выполненную блоком ППДП (140 на Фиг. 1) для программирования всех программируемых данных конфигурации, хранящихся в запоминающем устройстве (123 на Фиг. 1) блока ПОЗПДП (120 на Фиг. 1), в рамках одной операции передачи память-память (148, 149, 150 на Фиг. 1). В данном примере процессорный модуль (110 на Фиг. 1) является ядром процессора. Блок ПОЗПДП (120 на Фиг. 1) реализует функции блока управления памятью. На данной блок-схеме блок ПОЗПДП (120) и ядро процессора (110) уже инициализированы.

Ярлык (301) иллюстрирует последовательность шагов (301, 305, 308, 311, 314, 330, 331, 334), выполняемых ядром процессора (110). Ярлык (302) иллюстрирует последовательность шагов (302, 306, 309, 312, 315, 321, 323, 327, 328, 329, 332, 335), выполняемых блоком ПОЗПДП (110). Ярлык (303) иллюстрирует последовательность шагов (303, 307, 310, 313, 316, 317, 320, 322, 326, 336), выполняемых блоком ППДП (140). Ярлык (304) иллюстрирует последовательность шагов (304, 318, 319, 324, 325, 337), выполняемых блоком памяти SDRAM (115, 118).

Блок-схема (300) начинается с шагов (301), (302), (303) и (304).

На шаге (305) ядро процессора (110) выдает 32-битовый запрос передачи данных памяти для записи в поле исходного адреса памяти (148) блока ППДП (140). Этот запрос передачи данных памяти принимается на целевом порту (128) блока ПОЗПДП (120) в шаге (306). Блок ПОЗПДП (120) обрабатывает этот запрос передачи данных памяти в соответствии с правилами адресации трансляции памяти, ассоциированными с целевым портом (128) и хранящимися в программируемых данных конфигурации в запоминающем устройстве (123). Блок ПОЗПДП (120) передает этот обработанный запрос передачи данных памяти в блок ППДП (140) через главный порт (129), а затем через межкомпонентное соединение (192). 3атем блок ППДП (140) получает этот запрос передачи данных памяти через свой целевой порт (142) в шаге (307). Блок ППДП (140) записывает поел данных этого запроса передачи данных памяти в свое поле «адреса исходной памяти» (148).

На шаге (308) ядро процессора (110) выдает 32-битовый запрос передачи данных памяти для записи в поле «адреса целевой памяти» (149) целевого порта (142) блока ППДП (140). Этот запрос передачи данных памяти обрабатывается и перенаправляется этим блоком ПОЗПДП (120) в блок ППДП (140) в шаге (309). В шаге (310) этот блок ППДП (140) получает этот запрос передачи данных памяти и записывает данные этого запроса передачи данных памяти в свое поле «целевого адреса памяти» (149).

На шаге (311) ядро процессора (110) выдает 32-битовый запрос передачи данных памяти для записи в поле «длины передачи памяти» (150) блока ППДП (140). Этот запрос передачи данных памяти обрабатывается и перенаправляется блоком ПОЗПДП (120) в блок ППДП (140) в шаге (312). В шаге (313) этот блок ППДП (140) получает этот запрос передачи данных памяти и записывает данные этого запроса передачи данных памяти в свое поле «длины адреса памяти» (150). Операция передачи память-память инициируется, когда данные записываются в поле длины передачи памяти (250).

В шаге (314) ядро процессора (110) выдает запрос передачи данных памяти для считывания на адрес памяти внутри адресного пространства целевого порта (124) блока ПОЗПДП (120), и в результате, после того, как системная и пользовательская части программируемых данных конфигурации этого ПОЗПДП были полностью обновлены, блок ПОЗПДП (120) выпускает ответ на считывание. Этот запрос передачи данных памяти принимается и обрабатывается на шаге (315). Соответствующий запрос передачи данных памяти будет выпущен в шаге (329) ниже.

В шаге (316) значение «исходного адреса памяти» (148) загружается, как значение текущего указателя адреса (153). 3начение «целевого адреса памяти» (149) загружается, как значение текущего указателя адреса (151). 3начение «длины передачи памяти» (150) загружается, как значение поля счетчика (151) и значение поля счетчика (153). Модуль FIFO (147) обнуляется, чтобы убедиться, что в очереди данного модуля FIFO отсутствуют какие-либо элементы данных. Вспомогательная цепь управления (145) получает инструкцию начать процесс считывания данных из исходной памяти. Вспомогательная цепь управления (146) получает инструкцию начать процесс записи данных в целевую память.

В шаге (317) вспомогательная цепь управления (146) выдает запрос передачи данных памяти, считанных из пакетной памяти, через порт (144) для прочтения первой половины длины запрошенного сообщения (150). 3апрос передачи данных пакетной памяти - это запрос передачи данных памяти, адаптированный для работы с двумя или более словами данных. Этот запрос передачи считанных данных пакетной памяти использует значение «текущего указателя адреса» (151). Этот запрос передачи считанных данных пакетной памяти принимается и обрабатывается памятью SDRAM на шаге (318). Запрошенные данные отправляются памятью SDRAM обратно на главный порт (144) блока ППДП (140) в виде ответа с передачей данных пакетной памяти в шаге (319).

В шаге (320) блок ППДП (140) получает ответ на считывание данных пакетной памяти, содержащий запрошенные данные, на главный порт (144). Эти данные передаются в модуль FIFO (147). Значение «текущего указателя адреса» (154) увеличивается, а значение счетчика (153) уменьшается в соответствии с объемом принятых данных.

В шаге (320) вспомогательный блок управления (145) выталкивает эти данные из модуля FIFO (147) и выдает запрос передачи данных пакетной памяти для записи на целевой порт (134) блока ПОЗПДП (120), используя значение «текущего указателя адреса» (152). 3начение «текущего указателя адреса» (151) увеличивается, а значение счетчика (152) уменьшается в соответствии с объемом записанных данных.

В шаге (321) блок ПОЗПДП (120) получает этот запрос передачи данных пакетной памяти для записи на целевой порт (134) и записывает данные, которые он принял, в программируемые данные конфигурации, хранящиеся в запоминающем устройстве (123). Блок управления ПОЗПДП (121) активно отслеживает, когда системная и пользовательская части программируемых данных конфигурации, хранящихся в запоминающем устройстве (123), обновляются, и активно отслеживает, когда конфигурация системной и пользовательской частей программируемых данных конфигурации завершена, как описано в текстовом описании Фиг. 2.

В шаге (322) блок ППДП (140) получил все данные, запрошенные в его запросе передачи считанных данных пакетной памяти, выпущенном в шаге (317). Вспомогательная цепь управления (146) выдает запрос передачи данных памяти, считанных из пакетной памяти, через порт (144) для прочтения второй половины длины запрошенных данных памяти (150). Этот запрос передачи считанных данных пакетной памяти использует значение «текущего указателя адреса» (151).

В шаге (322) вспомогательный блок управления (145) блока ППДП (140) продолжает передавать любые оставшиеся данные, хранящиеся в модуле FIFO (147), в блок ПОЗПДП (120). Это может потребовать или не потребовать выдачу дополнительных запросов передачи данных памяти для записи, если необходимо.

В шаге (324) запрос передачи считанных данных пакетной памяти, выпущенный в шаге (322), принимается и обрабатывается хранилищем SDRAM. B шаге (325) запрошенные данные отправляются памятью SDRAM обратно на главный порт (144) блока ППДП (140), как ответ с передачей данных пакетной памяти.

В шаге (326) блок ППДП (140) продолжает передавать данные в блок ПОЗПДП (120). Вспомогательная цепь управления (146) блока ППДП (140) останавливается, когда значение ее счетчика (153) становится равным нулю. Вспомогательная цепь управления (145) блока ППДП (140) останавливается, когда значение ее счетчика (151) становится равным нулю. Когда обе вспомогательные цепи управления, (146) и (145), останавливаются, операция передачи память-память блока ППДП (140) завершается (по крайней мере, насколько это относится к блоку ППДП).

В шаге (327) блок ПОЗПДП (120) продолжает принимать и обрабатывать переданные данные записи памяти, отправленные через главный порт (143) блока ППДП (140).

В шаге (328) блок ПОЗПДП (120) был успешно перепрограммирован. Блок ПОЗПДП (120) теперь будет обслуживать запросы передачи данных памяти, полученные через целевой порт (128) блока ПОЗПДП (120) в соответствии с правилами, которые теперь закодированы в программируемых данных конфигурации в запоминающем устройстве (123) этого блока ПОЗПДП.

В шаге (329) блок динамического контроля (122) блока ПОЗПДП (120) отправляет запрос передачи считанных данных памяти со значением 1 в поле считанных данных обратно в ядро процессора (110). Это сообщает ядру процессора, что блок ПОЗПДП (120) был полностью перепрограммирован. В шаге (330) ядро процессора (110) получает этот ответ передачи данных памяти.

На шаге (331) ядро процессора (110) выдает запрос передачи данных памяти для записи в вводное адресное пространство целевого порта (128) блока ПОЗПДП (120). В шаге (332) этот запрос передачи данных памяти для записи принимается через целевой порт (128) блока ПОЗПДП (120) и обрабатывается его блоком управления (121) в соответствии с правилами, которые теперь хранятся в программируемых данных конфигурации в запоминающем устройстве (123) этого блока ПОЗПДП.

Блок-схема заканчивается ярлыками (334), (335), (336) и (337).

В альтернативном предпочтительном варианте выполнения данного изобретения: Блок ПОЗПДП (120) на Фиг. 1 сильно связан с ядром процессора (110) на Фиг. 1; запоминающее устройство (112) на Фиг. 1 отключается от межкомпонентного соединения (190) на Фиг. 1 и подключается к межкомпонентному соединению (192) на Фиг. 1; целевая шина (124) блока ПОЗПДП (120) на Фиг. 1 не используется; а целевая шина (136) блока ПОЗПДП (120) на Фиг. 1 используется.

Существует длительная потребность в архитектуре БУП, имеющей низкое значение задержки, высокую пропускную способность, работу с постоянным временем с поддержкой относительно мелкоструктурного выделения памяти в 32- и 64-битовом вводном адресном пространстве.

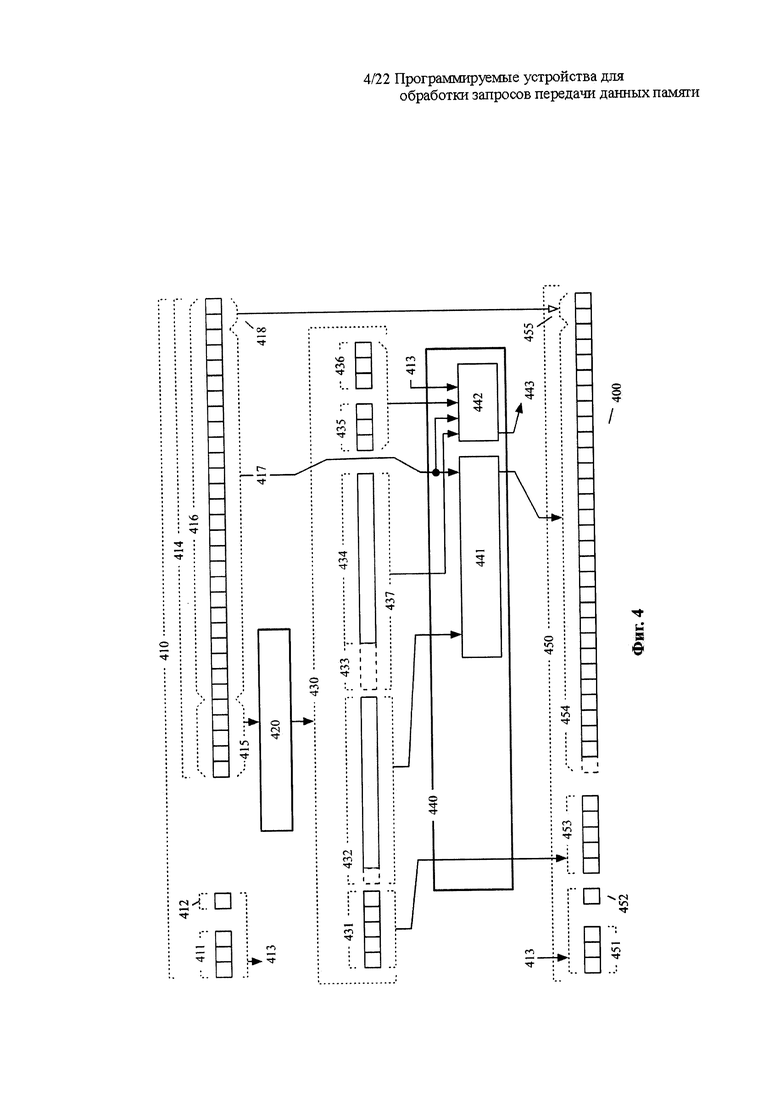

Фиг. 4 представляет собой гибридную принципиальную блок-схему и диаграмму потоков данных, частично иллюстрирующую предпочтительный вариант выполнения данного изобретения, где блок ПОЗПДП (120) на Фиг. 1 адаптирован для реализации функционала блока управления памятью (БУП).

Этот БУП (120) использует инновационную одноуровневую схему прямой индексированной посегментной трансляции адресов памяти, адаптированную для использования с большими вводными адресными пространствами (например, в данном случае, 31-битовое вводное адресное пространство (414)), в которых имеется небольшое число дескрипторов сегментов, ассоциированных с вводным адресным пространством (414), и каждый дескриптор сегмента поддерживает мелкоструктурное выделение памяти (533) внутри этого сегмента. Эта инновационная схема трансляции адресов памяти предназначена для использования с широким диапазоном схем организации памяти, включая, но не ограничивается, описанные с ссылкой на Фиг. 6 и Фиг. 8. В частности, данная инновационная схема организации памяти, описанная с ссылкой на Фиг. 8, синергетически использует комбинацию (а) большого вводного адресного пространства и (b) малого числа дескрипторов региона, которая обеспечивает возможность мелкоструктурного выделения памяти и предлагает неожиданное решение для проблемы масштабирования размера адресного пространства с другими одноуровневыми схемами прямой трансляции индексированных адресов памяти [1], [2]. Как преимущество, одна аппаратная реализация блока ПОЗПДП (120) может поддерживать обе схемы организации памяти, описанные на Фиг. 6 и Фиг. 8.

Эта схема может быть легко адаптирована для использования с большими вводными адресными пространствами, которые больше, равны или меньше, чем выводное адресное пространство.

Дескрипторы региона блока ПОЗПДП (120) адаптированы для кодирования дескрипторов сегмента с полями, как показано для дескриптора сегмента (430).

Ярлык 410 иллюстрирует поля запроса передачи данных памяти, полученного через целевой соединительный порт (128) блока ПОЗПДП (120). Этот запрос передачи данных памяти (410) показан с полями (411), (412) и (414). Поле (411) кодирует 3-битовое управляющее поле для данного запроса передачи данных памяти (410). Эти три бита кодируют операции «считывание данных», «запись» и «считывание для выполнения», соответственно. Поле (412) кодирует 1-битовое значение привилегии, указывающее на привилегию уровня системы или привилегию уровня пользователя для данного запроса передачи данных памяти (410). Поле (414) кодирует значение 31-битового вводного адреса в вводном адресном пространстве. 5 старших битов (415) 31-битового вводного адреса (414) используется в качестве селектора индекса сегмента. Оставшиеся 26 битов (416) 31-битового вводного адреса (414) используются в качестве сдвига внутри этого сегмента (415).

Модуль поиска одноуровневого дескриптора сегмента с прямой индексацией (420) хранит таблицу 32 дескрипторов сегмента, которые могут быть запрограммированы во время выполнения. Дескрипторы сегмента этой таблицы индексируются во время выполнения 5 верхними битами (615) вводного адреса (614) запроса передачи данных памяти, полученного через целевой соединительный порт (128) блока ПОЗПДП (120).

Каждый дескриптор сегмента, иллюстрированный дескриптором сегмента (430), включает в себя 5 полей (431), (432), (434), (435) и (436). Общая длина дескриптора сегмента (430) составляет 64 бита. В этом варианте выполнения данного изобретения этот дескриптор сегмента (430) поддерживает 31-битовое вводное адресное пространство, допускающее адресацию 2^31 байт памяти. Этот дескриптор сегмента (430) также поддерживает 31-битовое выводное адресное пространство, допускающее адресацию 2^31 байт памяти. Поля (431-436) дескриптора сегмента (430) имеют следующее назначение. Поле (431) кодирует 6 бит метаданных, ассоциированных с этим дескриптором сегмента. Поле (432) кодирует 29-битовый сдвиг внутри транслированного адресного пространства. Уменьшение числа бит поля (432) уменьшает размер физического адресного пространства, на котором может отображаться вводное адресное пространство. Это, в свою очередь, уменьшает объем аппаратных ресурсов, необходимых для хранения дескрипторов сегмента. Поле (434) кодирует длину 24-битового выделенного сегмента с 8-байтовой структурированностью. Поле (433) логически расширяет длину 24-битового выделенного сегмента до значения 29-битового выделенного сегмента (437). В частности, нулевое бинарное значение хранится в каждом из 5 старших битов (433) этого значения 29-битового выделенного сегмента (437). Поле (435) кодирует 3-битовое разрешающее поле для привилегированного пользовательского доступа. Эти три бита кодируют разрешения на «считывание данных», «запись» и «считывание для выполнения», соответственно. Поле (436) кодирует 3-битовое разрешающее поле для привилегированного системного доступа. Эти три бита кодируют разрешения на «считывание данных», «запись» и «считывание для выполнения», соответственно.

Вывод модуля поиска дескрипторов сегмента (420) подается, как ввод в модуль сборки запроса передачи данных памяти и проверки разрешений (440). Модуль (440) включает в себя арифметическую операцию сложения шириной 29 бит, которая: получает в качестве ввода 29 старших битов (417) 31-битового поля смещения (416) запрос передачи данных памяти (410); получает в качестве ввода 29-битовый сдвиг (432) в рамках транслированного адресного пространства для данного дескриптора сегмента (430) и генерирует 29-битовое значение в качестве вывода, которое используется, как старшие 29 битов (454) 31-битового адреса (454, 454) транслированного запроса передачи данных памяти (413).

Модуль сборки запроса передачи данных памяти и проверки разрешений (440) также включает в себя модуль проверки разрешений (442), который:

- Проверяет, чтобы значение смещения (416) запроса передачи данных памяти (410) меньше или равно длине 29-битового сегмента (437) дескриптора сегмента (430), который ассоциирован с данным запросом передачи данных памяти (410); и

- Проверяет, чтобы 3-битовое управляющее поле (411) и 1-битовое поле привилегий (412) запроса передачи данных памяти (410) разрешается политикой разрешений, закодированной в полях (435) и (436) дескриптора сегмента (430), ассоциированного с данным запросом передачи данных памяти (410). Если эта проверка разрешений дает отрицательный результат, подается сигнал ошибки (443). В предпочтительном варианте выполнения данного изобретения этот сигнал ошибки может привести к отправке сигнала прерывания в ядро процессора (110).

Значение поля метаданных (431) этого дескриптора сегмента (430) используется в качестве поля метаданных (453) транслированного запроса передачи данных памяти (413). В предпочтительном варианте выполнения данного изобретения поле метаданных (431) адаптировано для кодирования:

- 1-битовое каскадное поле для условного включения дополнительного уровня трансляции адресов памяти дополнительными средствами трансляции адресов памяти;

- 4 битов для контроля подсистемы памяти, включая: выбор режима кэширования (например, сквозная запись, обратная запись) и требований к запросу памяти для поддержания когерентности памяти.

Значение (413) 3-битовой операции (411) и 1-битового поля привилегий (412) запроса передачи данных памяти (410) передается, как значение 3-битовой операции (451) и 1-битового поля привилегий (452) транслированного запроса передачи данных памяти (413), соответственно.

Значение 2 младших битов (418) адреса (416) входящего запроса передачи данных памяти (410) предоставляется, как значение 2 младших битов (454) транслированного запроса памяти (450).

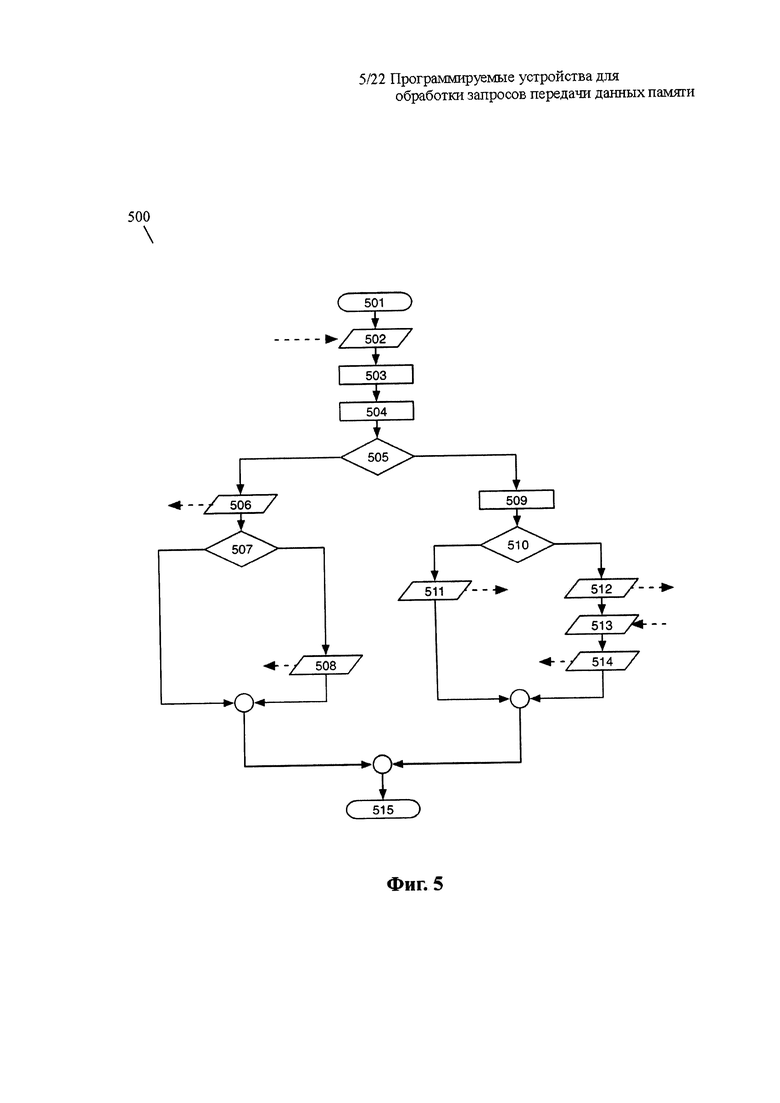

Фиг. 5 представляет собой блок-схему (500), иллюстрирующую шаги операции трансляции адреса памяти, выполняемой блоком управления (121) блока ПОЗПДП (120) в соответствии с предпочтительным вариантом выполнения данного изобретения.

Блок схема начинается с шага (501).

В шаге (502) этот запрос передачи данных памяти принимается блоком управления (121) блока ПОЗПДП (120) через порт (128).

В шаге (503) пять старших битов (415) адреса (414) этого запроса передачи данных памяти (410) предоставляются, как индекс для модуля поиска дескриптора сегмента (420). Модуль поиска дескриптора сегмента (420) выпускается, как вывод значения дескриптора сегмента (430), ассоциированного с данным значением индекса. Вывод модуля поиска дескрипторов сегмента (420) принимается модулем сборки и проверки разрешений (440).

В шаге (504) модуль проверки разрешений (442) выполняет проверку согласованности запроса передачи данных памяти (414), принятого в шаге (502), и соответствующего дескриптора сегмента, выпущенного в шаге (503).

В шаге (505), если проверка согласованности (504) дает отрицательный результат, осуществляется переход к шагу (506), в противном случае к шагу (509).

В шаге (506) генерируется сигнал события ошибки проверки разрешения на порт (443).

В шаге (507), если запрос передачи данных памяти (410), полученный в шаге (502), является запросом передачи данных памяти для записи, осуществляется переход к шагу (515), в противном случае к шагу (508).

В шаге (508) выдается ответ на запрос передачи памяти для считывания. В поле данных этого ответа на запрос передачи данных памяти хранится нулевое значение. Если протокол связи предусматривает такую возможность, для данного запроса передачи данных памяти возвращается состояние ошибки. Перейти к шагу (515).

В шаге (509) выполняется операция сложения шириной 29 бит (441) и сборка полей транслированного запроса передачи данных памяти (450), как описано в тексте под Фиг. 4.

В шаге (510), если запрос передачи данных памяти, полученный в шаге (502), является запросом передачи данных памяти для записи, осуществляется переход к шагу (511), в противном случае к шагу (512).

В шаге (511) выпускается запрос передачи данных памяти для записи на главный порт (129) блока ПОЗПДП (120). Перейти к шагу (515).

В шаге (512) выпускается запрос передачи данных памяти для считывания на главный порт (129) блока ПОЗПДП (120).

В шаге (513) принимается соответствующий ответ на запрос передачи данных памяти для считывания на главный порт (129) блока ПОЗПДП (120).

В шаге (514) передается результат этого ответа на запрос передачи данных памяти для считывания, полученный в шаге (513), на целевой порт (128) блока ПОЗПДП (120).

Блок-схема останавливается на шаге (515).

Фиг. 6 представляет собой блок-схему (600), показывающую пример отображения схемы трансляции адресов на основании сегмента между вводным адресным пространством (610) и транслированным адресным пространством (630) в соответствии с предпочтительным вариантом выполнения данного изобретения. На данной схеме (600) вводное адресное пространство (610) начинается с нуля в верхнем левом углу прямоугольника (610) и заканчивается в нижнем правом углу этого прямоугольника (610). На данной схеме (600) целевое адресное пространство (630) начинается с нуля в верхнем левом углу прямоугольника (630) и заканчивается в нижнем правом углу этого прямоугольника (630). Линейное вводное адресное пространство (610) разделено на N=8 разделов равной длины (611-618). На данной иллюстрации смещение сегмента в разделе вводного адресного пространства можно отобразить в любом месте выводного адресного пространства с 8-байтовой структурированностью (например, ярлык 632). Выделенная длина сегмента также имеет 8-байтовую структурированность (например, ярлыки 634, 837, 838).

Дескриптор сегмента для раздела (611) показан, как выделяющий всю длину этого раздела (611) и транслирующий его базовое смещение на более старший адрес (631) целевого адресного пространства (630). Дескриптор сегмента для раздела (612) выделяет верхнюю часть этого раздела (612) и транслирует его базовое смещение на более старший адрес (632) целевого адресного пространства (630). Выделенные части первого сегмента (611) и второго сегмента (612) непрерывны в вводном адресном пространстве. Дескриптор сегмента для раздела (613) не выделяет никаких частей этого раздела. Дескриптор сегмента для (614) выделяет верхнюю часть этого раздела (614) и транслирует его базовое смещение на тот же адрес (634) целевого адресного пространства (630).

Дескриптор сегмента для раздела (615) не выделяет никаких частей памяти этого раздела. Дескриптор сегмента для раздела (616) не выделяет никаких частей памяти этого раздела.

Дескриптор сегмента для (617) выделяет небольшой регион в верхней части этого раздела (617) и транслирует его базовое смещение на более младший адрес (637) целевого адресного пространства (630). Дескриптор сегмента для (618) выделяет больший регион в верхней части этого раздела (618) и транслирует его базовое смещение на более младший адрес (638) целевого адресного пространства. На данной иллюстрации дескриптор сегмента для раздела (617) адаптируется с правилом разрешения доступа, позволяющим пользователю производить запись в этот выделенный регион памяти, а дескриптор сегмента для раздела (618) адаптируется с правилом разрешения доступа, позволяющим некэшированному пользователю считывать ту же часть транслированного адресного пространства.

Так можно увидеть, что все сегменты переменной длины в вводном адресном пространстве начинаются с границы раздела, что разрешает аппаратно-эффективную индексацию этого дескриптора сегмента с низким значением задержки (в сравнении с таблицей дескрипторов диапазона, как показано ярлыком 123 на Фиг. 21). 8-байтовая структурированность выделенной длины сегмента и 8-байтовая структурированность относительного сдвига разрешает более эффективную компоновку вводного адресного пространства на транслированное адресное пространство памяти, чем возможно со страницами длиной 4 кибибайт, наблюдаемыми во многих традиционных БУП. Эта мелкая структурированность отображения на транслированное адресное пространство особенно полезна во встроенных микроприложениях с сильно ограниченной емкостью хранения.

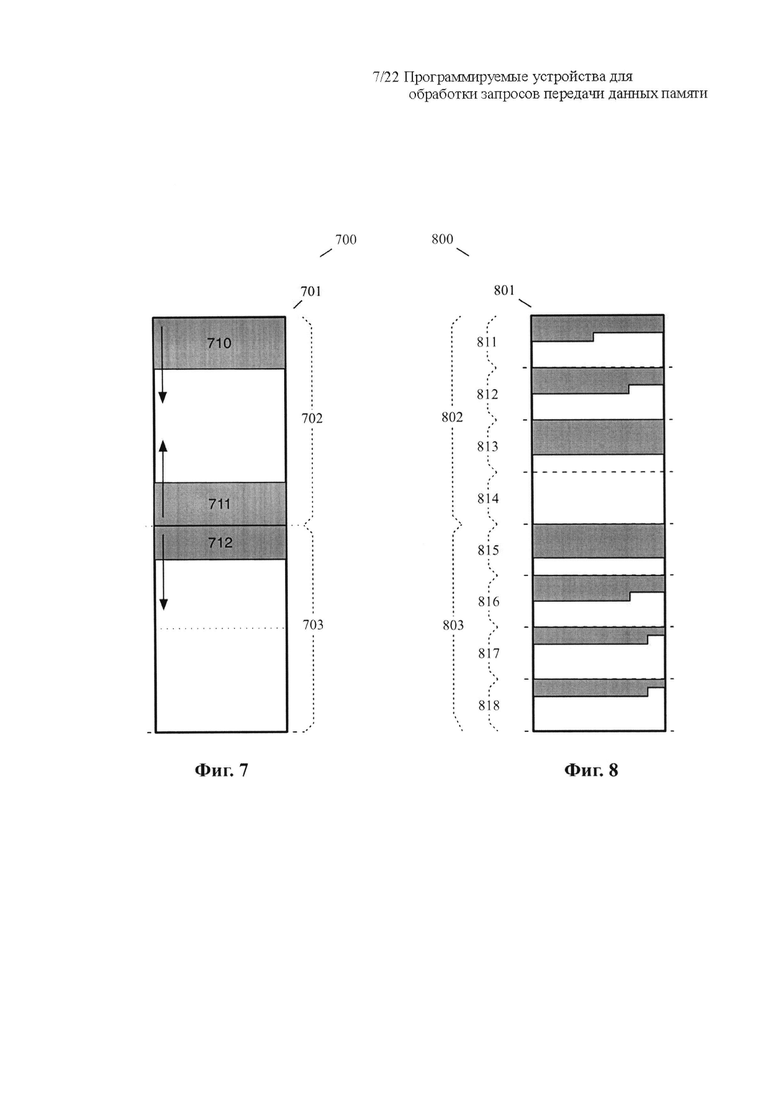

Фиг. 7 представляет собой блок-схему (670), иллюстрирующую организацию вводного адресного пространства (701) одноуровневой напрямую отображаемой схемы, основанной на страницах, для архитектуры DEC VAX-11/760, как описано на Фиг. 6-1 [3]. Каждый дескриптор страницы отображается на 512-байтовый непрерывный регион 32- битового вводного адресного пространства. Вводное адресное пространство (701) равномерно разделено на адресное пространство процесса (702) и адресное пространство системы (702). Пользовательское пространство (702) динамически делится на первый регион (710), называемый «Р0», и второй регион (711), называемый «Р1». Регион Р0 начинается вверху пользовательского пространства и простирается вниз. Регион Р1 начинается внизу пользовательского пространства и простирается вверх. Системное пространство (703) динамически делится на первый регион (712), называемый «системный регион», и «зарезервированный регион». Системный регион (712) начинается вверху адресного пространства системы и простирается вниз. DEC выбрала такую организацию памяти для ограничения размера одноуровневых таблиц с прямой индексацией, в которых хранятся дескрипторы страниц для трех регионов (Р0, Р1, системный регион), поддерживающих трансляции адресов памяти [3].

Фиг. 8 представляет собой блок-схему (670), иллюстрирующую инновационную организацию вводного адресного пространства (701) для одноуровневой схемы прямого отображения, основанной на сегментах, для предпочтительного варианта выполнения данного изобретения. В данном примере рассматривается М-битовое вводное адресное пространство (801), равномерно разделенное на N=8 сегментов (811-818). Верхние 4 сегмента (811, 812, 813, 814) ассоциированы с адресным пространством системы (803), а нижние 4 сегмента (815, 816, 817, 818) ассоциированы с адресным пространство пользователя (802).

Если размер вводного адресного пространства составляет М=32 бита, один дескриптор региона может отображать 512 мебибайт транслированного адресного пространства. Подавляющее большинство встроенных систем реального времени имеют менее 512 мебибайт физической памяти. В данном случае эти встроенные системы могли бы отобразить всю емкость хранения физической памяти на один дескриптор региона. Это предотвращает необходимость отображения 2 или более дескрипторов сегмента для получения доступа к любому непрерывному региону физической памяти. Многие операционные системы реального времени с особыми требованиями к безопасности статически выделяют память, доступную для каждого приложения, выполняемого на этом ОСРВ при включении питания. Это означает, что многие дескрипторы региона для адресного пространства системы и адресного пространства каждого приложения данного ОСРВ можно создать статически до включения питания данного устройства. Например: исполняемый код ОСРВ можно отобразить в разделе (811) с разрешенным системным привилегированным доступом только для чтения. ВЗБ, стеки и неупорядоченный массив этого ОСРВ можно отобразить в разделе (812) с разрешенным системным привилегированным доступом для чтения/записи. Сегмент (813) может отображать всю оперативную память в непрерывном регионе памяти в вводном адресном пространстве для поддержки функций копирования память-память, выполняемых ядром процессора. Сегмент (814) при включении питания можно оставить неотображенным. Исполняемый код первого приложения можно отобразить в разделе (815) с разрешенным пользовательским привилегированным доступом только для чтения. BSS, стек и неупорядоченный массив этого первого приложения можно отобразить в разделе (816) с разрешенным пользовательским привилегированным доступом для чтения/записи. Первый регион памяти, используемый совместно первым приложением и вторым приложением, можно отобразить в сегменте (817) с разрешенным пользовательским привилегированным доступом для чтения/записи. Второй регион памяти, используемый совместно первым приложением и вторым приложением, можно отобразить в сегменте (818) с разрешенным пользовательским привилегированным доступом только для чтения. Это статичное отображение не исключает возможность также и динамического отображения во время выполнения.

Увеличение количества дескрипторов региона с N=8 до N=16 позволяет поддерживать значительно более сложную организацию памяти, сохраняя при этом очень малую таблицу дескрипторов региона как для адресного пространства системы (802), так и для адресного пространства пользователя (803). Полное содержимое таблицы дескрипторов региона легко можно хранить в памяти SRAM на микрочипе для доступа с малой задержкой и высокой пропускной способностью. Увеличение размера вводного адресного пространства с 32 до 64 битов при одновременном сохранении постоянного размера целевого адресного пространства не увеличивает потребность таблицы дескрипторов региона в памяти.

Это инновационная схема организации памяти (800), разработанная совместно с блоком ПОЗПДП, применяющая инновационную схему сегментации для больших вводных адресных пространств, позволяет проводить трансляцию адресов памяти с постоянным временем с очень низкими перегрузками цепей, что делает ее идеально подходящей для киберфизических приложений с особыми требованиями к обеспечению безопасности при ограниченных ресурсах.

В предпочтительном варианте выполнения данного изобретения схема БУП, основанная на 4-кибибайтовых фиксированных страницах, используется в качестве второго уровня условно активированных средств трансляции адресов памяти.

Имеется давно ощущаемая потребность в поддержке двух уровней трансляции адресов, при которой каждый уровень трансляции адресов контролируется разным программным обеспечением (например, гипервизор контролирует первый уровень схемы БУП, а операционная система, управляемая гипервизором, контролирует второй уровень схемы БУП), что подходит для использования в системах реального времени с возможностью статистического анализа времени.

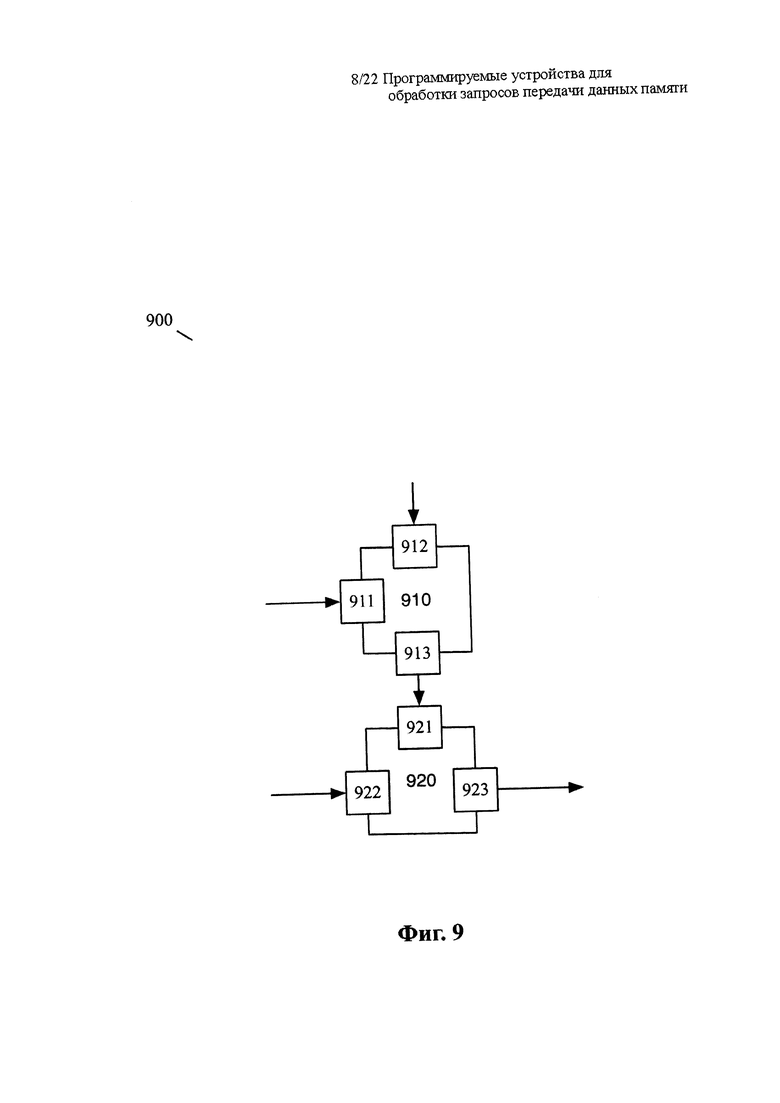

Фиг. 9 представляет собой блок-схему (900), иллюстрирующую два уровня средств управления памятью в соответствии с предпочтительным вариантом выполнения данного изобретения. Схема (900) показывает блок ПОЗПДП (910) и БУП (920).

В предпочтительном варианте выполнения данного изобретения содержание программируемых данных конфигурации блока ПОЗПДП (910) контролируется программным гипервизором, выполняемым в ядре процессора. Это ядро процессора выдает один или несколько запросов передачи данных памяти на целевой порт (911) блока ПОЗПДП (910) для конфигурации программируемых данных конфигурации этого блока ПОЗПДП (910).

Содержимое Программируемых данных конфигурации блока БУП (920) контролируется совместно операционной системой, работающей на гипервизоре в виртуальной машине, и исполнительным ПО этого гипервизора. Операционная система, работающая на этом программном гипервизоре, определяет правила, необходимые операционной системе для ее внутренних операций. Эти правила кодируются и записываются через целевой порт (912) блока ПОЗПДП (910). 3атем эти правила преобразуются правилами, хранящимися в блоке ПОЗПДП (910), контролируемыми исполнительным ПО гипервизора. Затем эти преобразованные правила записываются блоком ПОЗПДП (910) в программируемые данные конфигурации этого блока БУП (920).

В частности, блок ПОЗПДП (910) адаптирован для приема и обработки запросов передачи данных памяти, полученных через его целевой порт (912), в соответствии с правилами, закодированными в программируемых данных конфигурации блока ПОЗПДП (910). Эти правила в программируемых данных конфигурации блока ПОЗПДП (910) кодируют инструкции, как выполнять трансляцию адресов памяти одного или нескольких дескрипторов региона, полученных на целевой порт (912) и предназначенных для записи в программируемые данные конфигурации БУП (910) через его целевой порт (921). 3атем эти преобразованные правила записываются блоком ПОЗПДП (910) в программируемые данные конфигурации этого блока БУП (920), используя целевой порт (921).

Например, правила, закодированные в блоке ПОЗПДП (910), могут задавать непрерывный регион вводного адресного пространства целевого порта (922), доступ к которому могут получать запросы передачи данных памяти, полученные на целевом порту (922), вместе с относительным смещением для трансляции всех этих адресов в транслированное адресное пространство главного порта (923).

БУП (920) адаптирован для приема запросов передачи данных памяти на его целевой порт (922) и трансляции их адресов в соответствии с правилами, закодированными в программируемых данных конфигурации этого БУП (920).

Таким образом, схема трансляции адресов памяти, записанная в программируемые данные конфигурации БУП (920), логически эквивалентна последовательному выполнению двух уровней трансляции адреса памяти (трансляция адреса памяти на уровне операционной системы, затем трансляция адреса памяти на уровне программного гипервизора). В качестве преимущества, на два уровня трансляции адресного пространства при выполнении может повлиять БУП (920), с задержкой выполнения одного уровня трансляции адресного пространства.

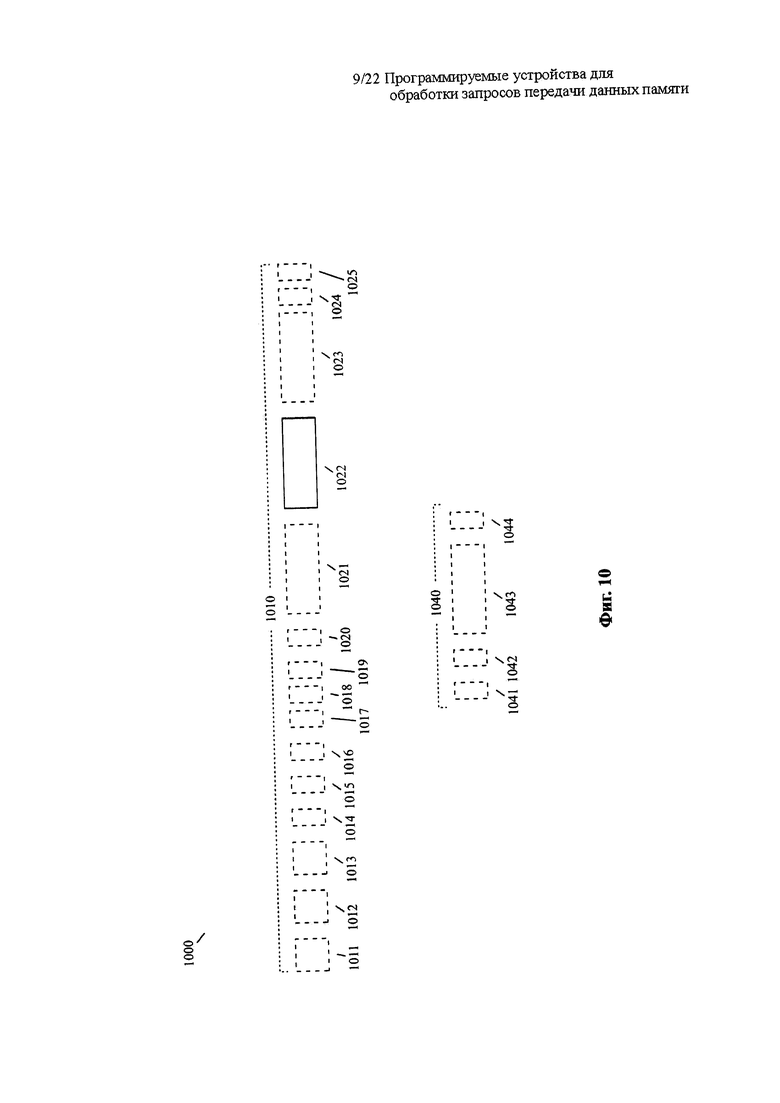

Фиг. 10 представляет собой блок-схему (1000), иллюстрирующую различные поля, которые могут присутствовать в запросе передачи данных памяти (1010) и ответе на запрос передачи данных памяти (1040) в соответствии с предпочтительным вариантом выполнения данного изобретения.

Что касается запроса передачи данных памяти (1010), необязательное поле (1011) содержит идентификатор группы устройств, который идентифицирует группу главных соединительных устройств. Необязательное поле (1012) содержит код типа устройства (например, сетевой интерфейс, графический процессор и т.д.). Необязательное поле (1013) содержит идентификатор устройства. Необязательное поле (1014) определяет правила согласования (такие как «без кэша», правила кэширования по умолчанию, кэш только для записи, кэш с обратной записью и т.д.) данного запроса передачи данных памяти. Необязательное поле (1015) содержит правила запроса памяти (запрос полного хранения, свободный доступ к памяти, запрос частичного хранения и т.д.). Необязательное поле (1016) содержит флаг запроса блокировки межкомпонентного соединения. Необязательное поле (1017) содержит операцию «считывание для получения данных». Необязательное поле (1018) содержит операцию «запись». Необязательное поле (1019) содержит операцию «считывание для исполнения». Необязательное поле (1020) содержит длину этого запроса передачи данных памяти. Необязательное поле (1021) содержит идентификатор адресного пространства, ассоциированный с данным запросом передачи данных памяти. Поле (1022) содержит адрес памяти, к которому требуется доступ. Необязательное поле (1023) содержит данные для записи, как часть запроса передачи данных памяти для записи. Необязательное поле (1024) содержит маску разрешения байта для запроса передачи данных памяти для записи. Необязательное поле (1025) содержит уровень привилегий этого запроса передачи данных памяти.

Что касается ответа на запрос передачи данных памяти (1040), необязательное поле (1041) содержит код результата для ассоциированного запроса передачи данных памяти (1010). Необязательное поле (1042) содержит 1-битовое значение, указывающее, действительны ли считанные данные, ассоциированные с этим ответом. Необязательное поле (1043) содержит считанные данные, ассоциированные с запросом передачи данных памяти (1010). Необязательное поле (1044) содержит маску активации считывания байта.

В предпочтительном варианте выполнения данного изобретения блок ПОЗПДП (120) адаптирован средствами идентификации главного соединения-источника, выдавшего запрос передачи данных памяти, полученные на его целевой порт (128), используя одно или несколько полей (1012) запроса передачи данных памяти (1010). В предпочтительном варианте выполнения данного изобретения блок ПОЗПДП (120) адаптирован средствами идентификации группы устройства главного соединения - источника, выдавшего запрос передачи данных памяти, полученные на его целевой порт (128), используя одно или несколько полей (1011) этого запроса передачи данных памяти (1010). В предпочтительном варианте выполнения данного изобретения блок ПОЗПДП (120) адаптирован средствами идентификации типа главного соединения-источника, выдавшего запрос передачи данных памяти, полученные на его целевой порт (128), используя одно или несколько полей (1012) этого запроса передачи данных памяти (1010). В предпочтительном варианте выполнения данного изобретения блок ПОЗПДП (120) адаптирован средствами ассоциации идентификатора адресного пространства с запросом передачи данных памяти, полученные на его целевой порт (128), используя одно или несколько полей (1011, 1012, 1013, 1021) этого запроса передачи данных памяти. В предпочтительном варианте выполнения данного изобретения правила закодированы в, как минимум, одном дескрипторе региона программируемых данных конфигурации блока ПОЗПДП (120) и ассоциированы с одним или несколькими полями (1011, 1012, 1013, 1016, 1021) запроса передачи данных памяти, полученного на целевой порт (128).

Существует длительная потребность в архитектуре БУП, имеющей низкое значение задержки, высокую пропускную способность, работу с постоянным временем с поддержкой относительно мелкоструктурного выделения памяти в 32- и 64-битовом вводном адресном пространстве. Также имеется давно ощущаемая потребность в средствах для экономически эффективного ускорения перепрограммирования дескрипторов региона с более низким уровнем безопасности и доступности для поддержки ускоренного обмена процессов и повышенной производительности системы. Теперь представим описание предпочтительного выполнения Фиг. 1, где блок ПОЗПДП (120) адаптирован схемой БУП, основанной на страницах.

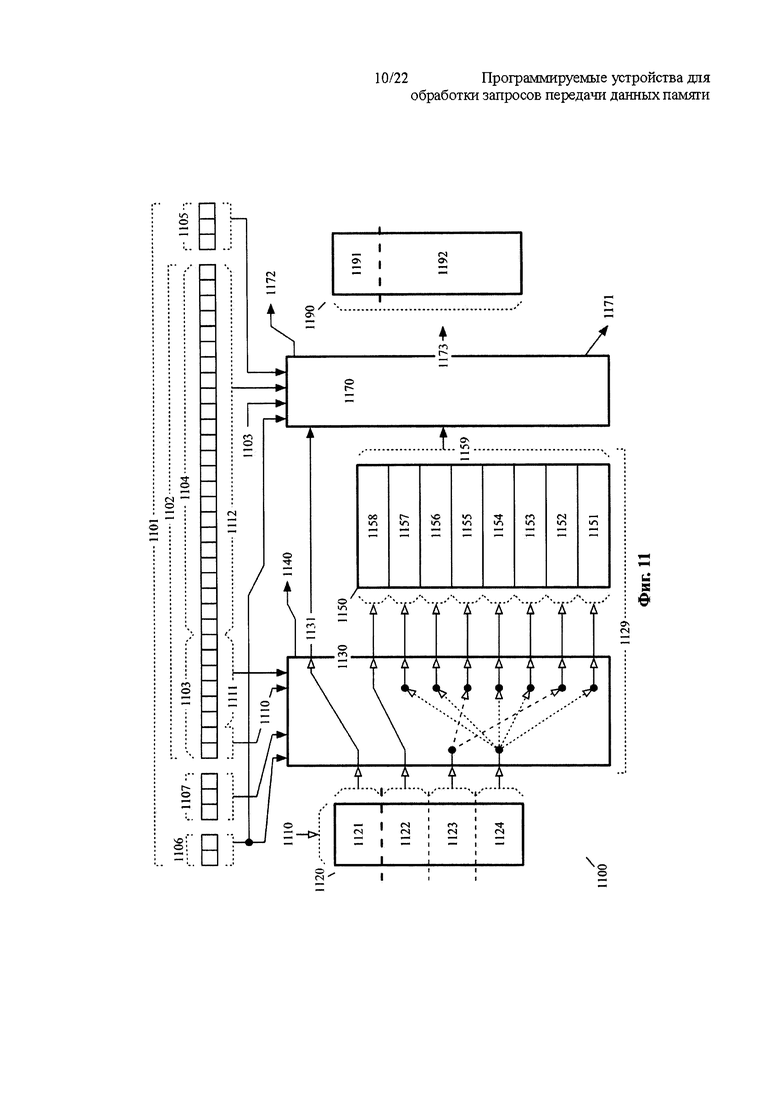

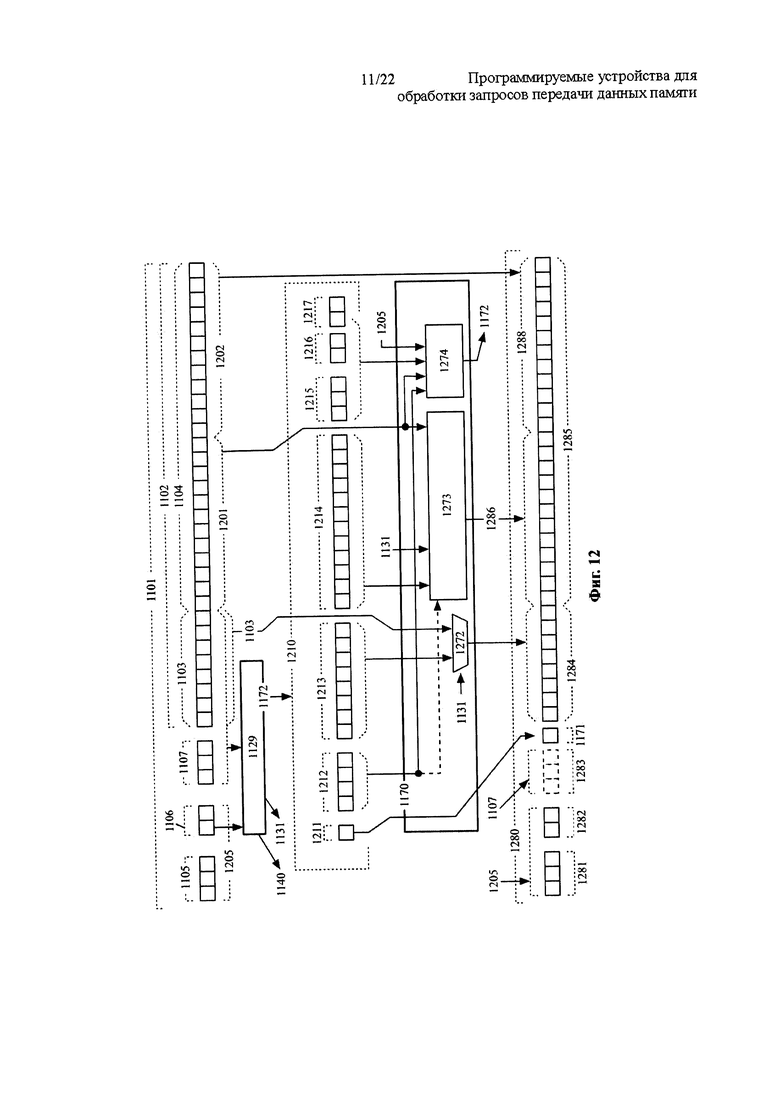

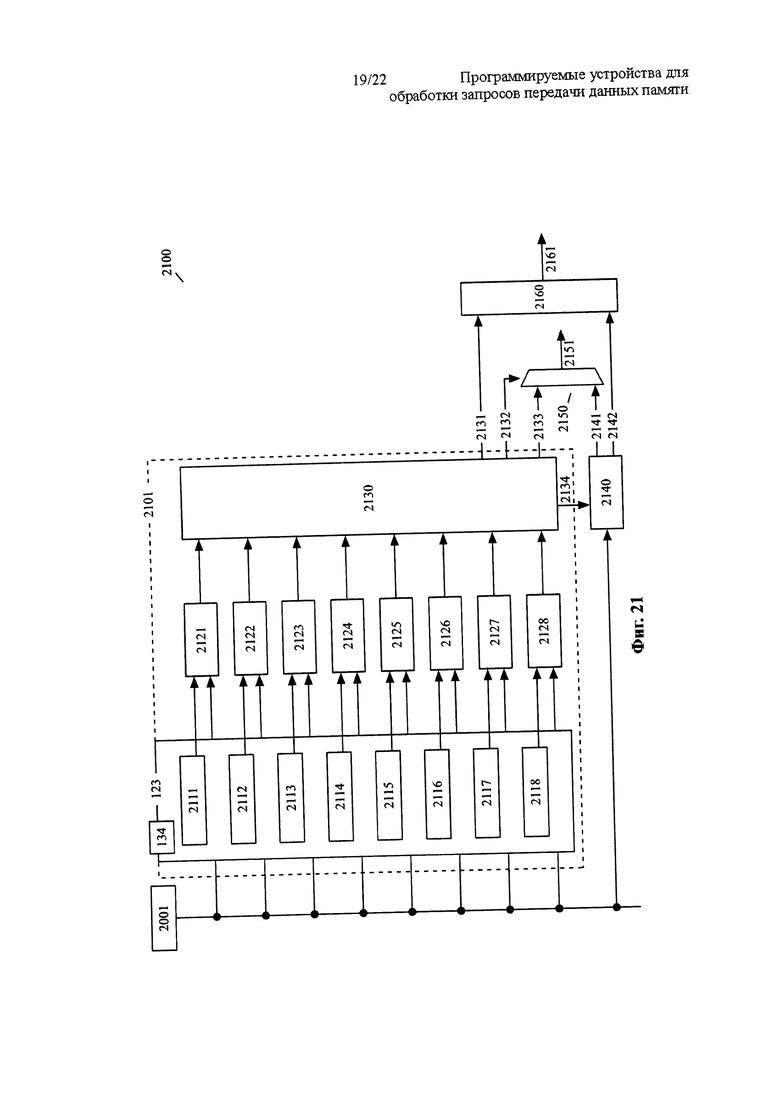

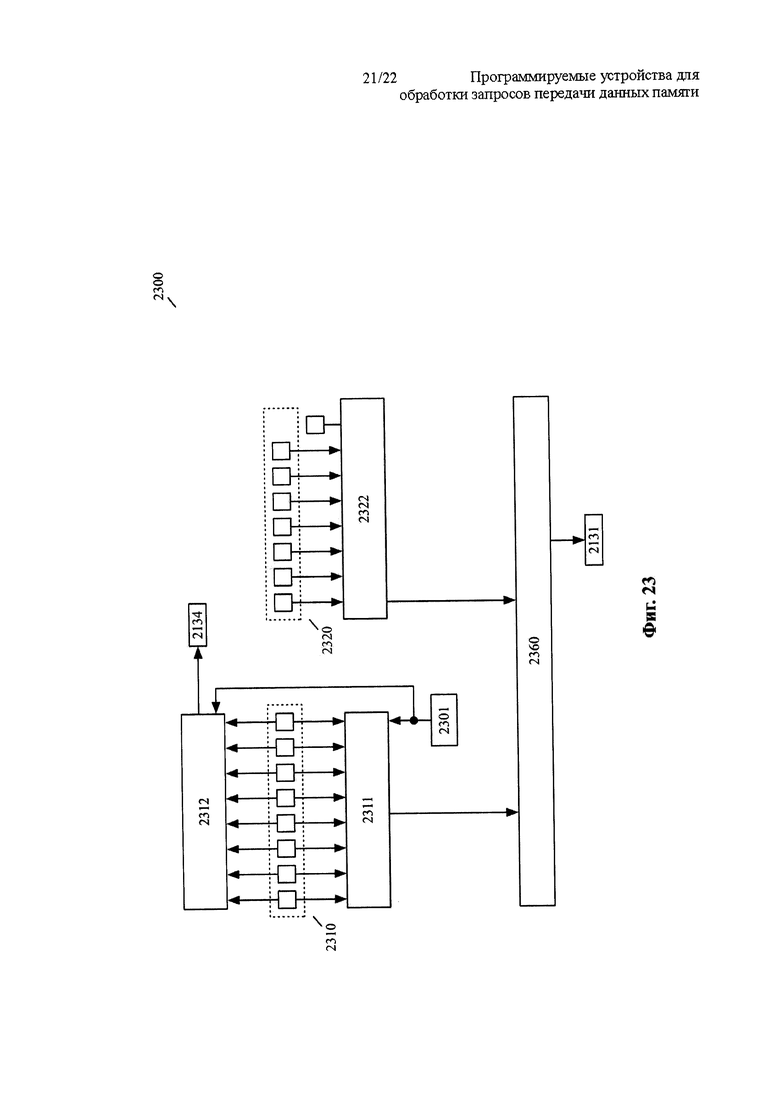

Фиг. 11 представляет собой гибридную принципиальную блок-схему и диаграмму потоков данных, частично иллюстрирующую предпочтительный вариант выполнения (1100) данного изобретения, где блок ПОЗПДП (120) на Фиг. 1 адаптирован для реализации функционала разбитого на разделы одноуровневого блока управления памятью (БУП) с прямой индексацией, основанного на страницах. На данной иллюстрации блок ПОЗПДП (120) использует 8 разделов (1151-1158). Эти 8 разделов (1151-1158) можно описать, как 8 независимых регионов обработки запросов передачи данных памяти. Каждый из этих разделов поддерживается одноуровневой таблицей прямой индексации, содержащей 64 дескриптора региона. Каждый из этих 512 дескрипторов региона является дескриптором страницы переменной длины с мелкоструктурным выделением памяти. Каждый из этих 512 дескрипторов региона можно хранить в одном физическом запоминающем устройстве.

Ярлык 1101 иллюстрирует поля, которые запрос передачи данных памяти получил через целевой соединительный порт (128) блока ПОЗПДП (120).

Этот запрос передачи данных памяти (410) показан с полями (1106), (1107), (1102) и (1105). Поле (1106) содержит 2-битовое поле привилегий со следующими 3 привилегиями пользовательская привилегия для программного обеспечения, привилегии старшего оператора для программного обеспечения и привилегии доступа для главных соединительных периферийных устройств.

Поле (1107) содержит выбор одного из 5 пространств в 3 битах.

Поле (1102) содержит 32-битовый вводной адрес. 2 старших битов (1110) 32-битового вводного адреса (1102) подразделяют это адресное пространство (1120) на 4 пространства: главное соединительное частное пространство (1211), адресное пространство системы (1122), адресное пространство пользователя с высоким приоритетом (1123) и адресное пространство пользователя с низким приоритетом (1124). Следующие 6 старших битов (1111) 32-битового вводного адреса (1102) подразделяют каждое адресное пространство (1121, 1122, 1123, 1124) на 64 пространства. Оставшиеся 24 бита (1112) 32-битового вводного адреса (1102) обеспечивают смещение старших 8 битов (1103) 32-битового вводного адреса (1102).

Поле (1105) кодирует 3-битовое управляющее поле для данного запроса передачи данных памяти (410). Эти 3 бита кодируют операции «считывание данных», «запись» и «считывание для выполнения», соответственно.

Модуль выбора раздела (1130) в качестве ввода получает значение полей (1106), (1107), (1110) и (1111). Модуль выбора раздела (1130) адаптирован для:

- Освобождения вывода (1140), указывающего на ошибку во время выбора раздела.

- Освобождения вывода (1131), указывающего, что трансляция адреса памяти не требуется. Этот вывод (1131) подается, как ввод на модуль сборки и проверки разрешений (1170).

- Освобождения вывода, указывающего, какой из 8 разделов (1151-1158) следует использовать для трансляции 32-битового адреса (1102) запроса передачи данных памяти (1101). Этот вывод подается, как ввод на модуль поиска разбитого на разделы одноуровневого прямого индексированного дескриптора страницы (1150).

Модуль поиска разбитого на разделы одноуровневого прямого индексированного дескриптора страницы (1150) имеет 8 разделов (8 независимых регионов обработки запросов передачи данных памяти). Каждый из этих 8 разделов имеет таблицу из 64 дескрипторов страницы, которые можно программировать во время выполнения. Выбор разделов для использования при выполнении трансляции адресов памяти осуществляется во время выполнения модулем выбора раздела (1130) для каждого запроса передачи данных памяти (1101), поступившего на целевой порт (128).

В предпочтительных вариантах выполнения данного изобретения отображение 5 адресных пространств (1107) запроса передачи данных памяти (1101) на 8 разделов (1151, 1152, 1153, 1154, 1155, 1156, 1157, 1158) модуля поиска разбитого на разделы одноуровневого прямого индексированного дескриптора страницы (1150) статически отображается посредством реализации модуля выбора раздела (1130). Простое статистическое отображение можно легко реализовать при помощи комбинационной логики с очень малыми аппаратными ресурсами и с очень высокой скоростью во время выполнения.

Стрелки, нарисованные внутри модуля выбора раздела (1130) на Фиг. 11, иллюстрируют следующее педагогическое отображение вводных пространств и разделов:

- Частное адресное пространство главного соединения (1121) не отображается на любом из 8 разделов (1151-1158).

- Адресное пространство уровня системы (1122) всегда отображается на разделы (1158). В предпочтительных вариантах выполнения данного изобретения ошибка (1140) выдается, если уровень привилегии (1106) этого запроса передачи данных памяти (1101) не соответствует привилегии уровня системы.

- Если значение поля выбора пространства (1107) запроса передачи данных памяти (1101) равно 0, адресное пространство пользователя с низким приоритетом (1124) отображается в раздел (1151), а адресное пространство пользователя с высоким приоритетом (1123) отображается в раздел (1152). Таким образом можно выделить все адресное пространство пользователя (1123, 1124).

- Если значение поля выбора пространства (1107) запроса передачи данных памяти (1101) равно 1, адресное пространство пользователя с низким приоритетом (1124) отображается в раздел (1153), а адресное пространство пользователя с высоким приоритетом (1123) отображается в раздел (1154). Таким образом можно выделить все адресное пространство пользователя.

- Если значение поля выбора пространства (1107) запроса передачи данных памяти (1101) равно 2, адресное пространство пользователя с низким приоритетом (1124) отображается в раздел (1155), а адресное пространство пользователя с высоким приоритетом (1123) не отображается ни в один раздел.

- Если значение поля выбора пространства (1107) запроса передачи данных памяти (1101) равно 3, адресное пространство пользователя с низким приоритетом (1124) отображается в раздел (1156), а адресное пространство пользователя с высоким приоритетом (1123) не отображается ни в один раздел.

- Если значение поля выбора пространства (1107) запроса передачи данных памяти (1101) равно 4, адресное пространство пользователя с низким приоритетом (1124) отображается в раздел (1157), а адресное пространство пользователя с высоким приоритетом (1123) не отображается ни в один раздел.

Программное обеспечение, выполняемое ядром процессора, отвечает за:

- отображение адресных пространств, контролируемых системой управления, на 5 пространств (1107) запроса передачи данных памяти (1107), контролируемого модулем выбора раздела (1130);

- программирование дескрипторов страниц модуля поиска разбитого на разделы одноуровневого прямого индексированного дескриптора страниц (1150); и

- изменение значения, переданного в поля выбора пространства (1107) запроса передачи данных памяти (1107) во время обмена контекста адресных пространств этой управляющей системы.

5 последних запланированных пользовательских приложений с низкими требованиями к емкости памяти, выполняемых в управляющей системе, могут быть отображены на любое из 5 пространств модуля выбора раздела (1130).

Обмен процессов между этими 5 пространствами с очень низкой задержкой может быть достигнут в управляющей системе посредством простого изменения значения, переданного в поле выбора пространства (1107) запроса передачи данных памяти (1107). Например, ядро процессора (110) может быть адаптировано регистром конфигурации, который определяет значение поля выбора пространства (1107), которое будет использовано этим ядром процессора при выдаче запросов передачи данных памяти.

2 последних запланированных пользовательских приложения с высокими требованиями к емкости памяти, выполняемых в управляющей системе, могут быть отображены на 2 адресных пространства модуля выбора раздела (1130), которые отображены на два раздела модуля поиска дескриптора страницы (1150).

Модуль поиска дескрипторов страниц (1150) адаптирован для передачи значения выбранного дескриптора страницы в качестве ввода для модуля сборки и проверки разрешений (1170).