Родственные заявки

Данная заявка испрашивает приоритет предварительной заявки США № 60/793016, поданной 19 апреля 2006 года, и предварительной заявки США № 60/793015, поданной 19 апреля 2006 года, которые полностью включены в данный документ посредством ссылки.

Область техники

Настоящее раскрытие изобретения в целом относится к системам обработки, а точнее говоря, к системам виртуально маркированного кэша команд.

Предшествующий уровень (техники)

Распространенные процессорные системы используют понятие трансляции адресов в процессорном конвейере для изменения адреса страницы данных или команд с их адреса в виртуальной памяти на их настоящий адрес в физической памяти. Один способ трансляции адресов использует буфер быстрого преобразования адреса (TLB), который обычно сохраняет много записей, где каждая запись включает в себя идентификатор пространства приложения (ASID), также называемый идентификатором процесса (PID), метку (ТЭГ) виртуального адреса (VT) и номер физической страницы (PPN). Таким образом, буфер быстрого преобразования адреса содержит соответствие между виртуальным адресом и физическим адресом. В его простейшей форме процессорный конвейер принимает в качестве входных данных виртуальный адрес команды, сравнивает часть виртуального адреса с записями в TLB, чтобы найти подходящую запись, и заменяет часть виртуального адреса номером физической страницы, ассоциированным с подходящей записью, чтобы сформировать физический адрес. Заданное преобразование физического адреса в виртуальный адрес, как правило, охватывает диапазон виртуального и физического адресного пространства, причем этот диапазон называется "страницей" с размером страницы, как правило, большим размера строки кэша в кэше команд, так что несколько строк кэша могут быть ассоциированы с одинаковой страницей виртуального или физического адресного пространства.

Общепринятые процессорные системы также включают в себя один или более кэшей команд, которые хранят недавно использованные команды в быстрой внутрикристальной памяти, чтобы минимизировать задержку, возникающую в результате выборки команд из более медленной памяти вне кристалла. Кэш команд может быть индексирован для эффективного поиска записи. Термин "индексированный", который использован относительно кэшей команд, означает множество битов либо в виртуальном адресе, либо в физическом адресе, которые используются для задания множества в кэше команд с множественной ассоциацией или строки в кэше команд прямого отображения. Кэш команд, индексированный битами в виртуальном адресе, известен как виртуально индексированный кэш. Кэш команд, индексированный битами в физическом адресе, известен как физически индексированный кэш.

Записи в кэше команд могут маркироваться тэгами с помощью ключа, который сравнивается либо с частью физического адреса, либо с частью виртуального адреса. Кэш команд, маркированный в качестве тэгов частью физического адреса, известен как кэш команд, физически маркированный тэгами. Кэш команд, маркированный в качестве тэгов частью виртуального адреса, известен как кэш команд, виртуально маркированный тэгами. Разработчик процессора выбирает, как кэш команд индексируется и маркируется. Традиционные кэши команд могут быть либо виртуально индексированными и виртуально маркированными (VIVT), виртуально индексированными и физически маркированными (VIPT), либо физически индексированными и физически маркированными (PIPT). Посредством трансляции адресов виртуальный адрес преобразуется в физический адрес, который может быть использован для поиска записи в физически маркированном кэше команд или для обращения к физической памяти в случае промаха кэша команд.

В дополнение к метке (тэгу) виртуального адреса традиционные виртуально маркированные кэши команд обычно включают в себя метку ASID или PID. Данная метка позволяет процессорной системе различать, действительна ли адресная запись для активного программного процесса. Например, если процессорная система исполняет команды, ассоциированные с программным процессом, имеющим ASID "х", то успешное совпадение кэша потребовало бы совпадения как метки ASID, так и метки виртуального адреса команды. Из-за различных сценариев, таких как свопинг активного ASID, то есть замена одного процесса, имеющего заданное значение ASID, новым процессом, используя то же значение ASID, виртуально маркированные кэши команд могут иметь одну или несколько записей, которые становятся устаревшими и уже недействительными. Поскольку попадания в кэш ограждают процессорное время от выборки команд из памяти, разработчики процессорной системы хотят когерентности кэша, то есть кэша, чье содержимое отражает действительные, неустаревшие команды. Для поддержания когерентности кэша записи в кэше обычно делаются недействительными в ответ на команды о недействительности кэша команд, выданные программным приложением. Объем управления кэшем команд, требуемый программным приложением, зависит от того, является ли кэш команд виртуально маркированным или физически маркированным. Так как один или более виртуальных адресов могут отображаться на заданный физический адрес, в традиционном виртуально маркированном кэше команд могут возникать проблемы псевдонимов и синонимов.

Проблема псевдонимов возникает, когда две или более записей I-кэша, содержащие разные сочетания виртуального адреса / ASID, соответствуют одному и тому же физическому адресу. Эти разные сочетания могут возникать вследствие любой из трех следующих причин. Во-первых, виртуальный адрес двух или более записей I-кэша может буквально отличаться, но быть частью одного и того же программного процесса, имеющего одинаковое значение поля ASID. Во-вторых, виртуальные адреса двух или более записей I-кэша могут быть одинаковыми, но ассоциированными с разными программными процессами и, таким образом, ассоциированными с разными значениями поля ASID. В-третьих, виртуальные адреса двух или более записей I-кэша могут различаться и ассоциироваться с разными программными процессами, таким образом, быть ассоциированными с разными значениями ASID. В любом из этих случаев разные сочетания могут соответствовать одному и тому же физическому адресу. В результате этой проблемы псевдонимов традиционные виртуально маркированные кэши команд перекладывают нагрузку на программное приложение для выдачи команд о недействительности I-кэша для большего количества сценариев, чем нужно физически маркированному кэшу команд. Например, программному приложению, написанному для виртуально маркированного кэша команд, потребовалось бы выдавать команды о недействительности кэша команд для выполнения недействительности каждого виртуального адреса в кэше команд, который может быть ассоциирован с физическим адресом, который сам стал недействительным или изменился.

Проблема синонимов относится к двум или более записям I-кэша, которые располагаются в разных виртуальных индексах I-кэша, но которые ассоциированы с одним и тем же физическим адресом. Проблема синонимов может возникать в традиционных виртуально индексированных I-кэшах независимо от того, являются ли I-кэши виртуально или физически маркированными.

Виртуально маркированные кэши команд также перекладывают другую дополнительную нагрузку на программное обеспечение для того, чтобы сделать недействительными записи I-кэша, по сравнению с физически маркированными кэшами команд. В частности, когда соответствие для сочетания заданного ASID и страницы виртуального адресного пространства меняется с одного физического адреса на другой, все записи I-кэша в виртуально маркированном I-кэше, которые ассоциированы с этим сочетанием ASID и страницы виртуального адресного пространства, уже не являются действительными, так как I-кэш может кэшировать содержимое старых адресов физической памяти, ассоциированных со старым соответствием, а не содержимое новых адресов физической памяти, ассоциированных с новым соответствием. Это справедливо, даже если фактическое содержимое базовых старого и нового адресов физической памяти могло не измениться. Следовательно, программное обеспечение, написанное для управления виртуально маркированным кэшем команд, обязано выполнять действия, чтобы сделать недействительным кэш команд, чтобы сделать недействительными все записи кэша команд, которые могли быть ассоциированы с сочетанием ASID и страницы виртуального адресного пространства, для которого менялось соответствие.

В процессоре с виртуально маркированным кэшем команд трансляция адресов может выполняться в конвейере параллельно с поиском команд в виртуально маркированном кэше команд. Таким образом, этот параллелизм обеспечивает выгодную мощность, частоту и пропускную способность команд, когда используются виртуально маркированные кэши команд. Следовательно, имеется потребность в системе и способах для кэша команд, которые обеспечивают преимущества традиционного виртуально маркированного кэша команд наряду с устранением дополнительной нагрузки, возложенной традиционными виртуально маркированными кэшами команд на программные приложения, в отношении управления записями, и не возлагают дополнительные требования на программные приложения.

Сущность изобретения

Один аспект раскрытия изобретения раскрывает систему кэша команд, имеющую преимущества как виртуально маркированного кэша команд, так и физически маркированного кэша команд. Этот аспект настоящего изобретения использует виртуально маркированный кэш команд, который с позиции компьютерной программы действует как физически маркированный кэш команд.

Другой аспект раскрытия изобретения раскрывает, что виртуальные адреса или их части используются в качестве меток как в средстве трансляции адресов, так и в виртуально маркированном кэше команд. С этим пониманием команды о недействительности, направленные средству трансляции адресов, могут дополнительно использоваться, чтобы сделать недействительными записи в виртуально маркированном кэше команд.

В другом аспекте раскрытия изобретения система кэша команд включает в себя виртуально маркированный кэш команд, средство для трансляции адресов и схему управляющей логики. Средство для трансляции адресов отвечает за команду о недействительности трансляции адресов. Схема управляющей логики конфигурируется, чтобы сделать недействительными записи в виртуально маркированном кэше команд в ответ на команду о недействительности трансляции адресов.

В еще одном аспекте раскрывается способ работы виртуально маркированного кэша команд так, как если бы он был физически маркированным кэшем команд с точки зрения компьютерной программы. Способ включает в себя прием команды о недействительности трансляции адресов и для признания недействительности записи в виртуально маркированном кэше команд в ответ на команду о недействительности трансляции адресов.

В дополнительном аспекте раскрывается схема управляющей логики для управления виртуально маркированным кэшем команд так, чтобы он действовал, как если бы он был физически маркированным кэшем команд. Схема управляющей логики включает в себя первый вход для приема команды о недействительности трансляции адресов и средство для формирования управляющих сигналов, чтобы сделать недействительной запись в виртуально маркированном кэше команд в ответ на команду о недействительности трансляции адресов.

Разумеется, другие варианты осуществления настоящего изобретения станут очевидными специалистам в данной области техники из последующего подробного описания, в котором различные варианты осуществления изобретения показаны и описаны в качестве иллюстрации. Как будет признано, изобретение допускает другие и отличные варианты осуществления, и его некоторые детали допускают модификацию в различных других отношениях, все без отклонения от настоящего изобретения. Соответственно, чертежи и подробное описание должны рассматриваться как пояснительные по характеру, а не как ограничивающие.

Краткое описание чертежей

Фиг.1 - функциональная блок-схема одного варианта осуществления процессора.

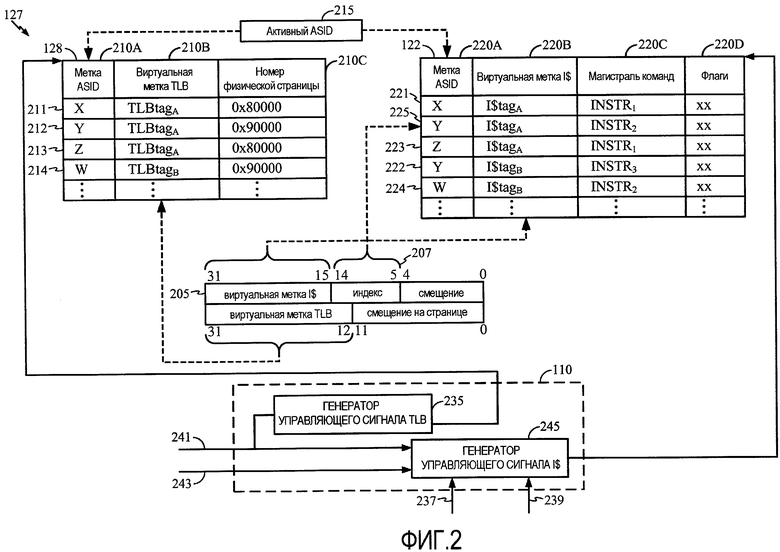

Фиг.2 - более подробное изображение системы кэша команд из фиг.1.

Фиг.3 - блок-схема, иллюстрирующая выборочное объявление недействительными множества записей виртуально маркированного I-кэша, которые могли быть ассоциированы с физическим адресом в I-кэше прямого отображения.

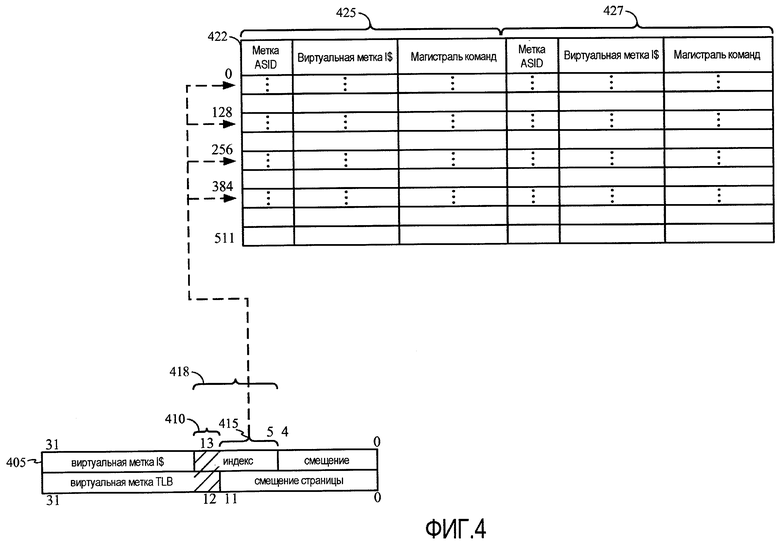

Фиг.4 - блок-схема, иллюстрирующая выборочное объявление недействительными множества записей виртуально маркированного I-кэша, которые могут быть ассоциированы с физическим адресом в двухвходовом I-кэше с множественным доступом.

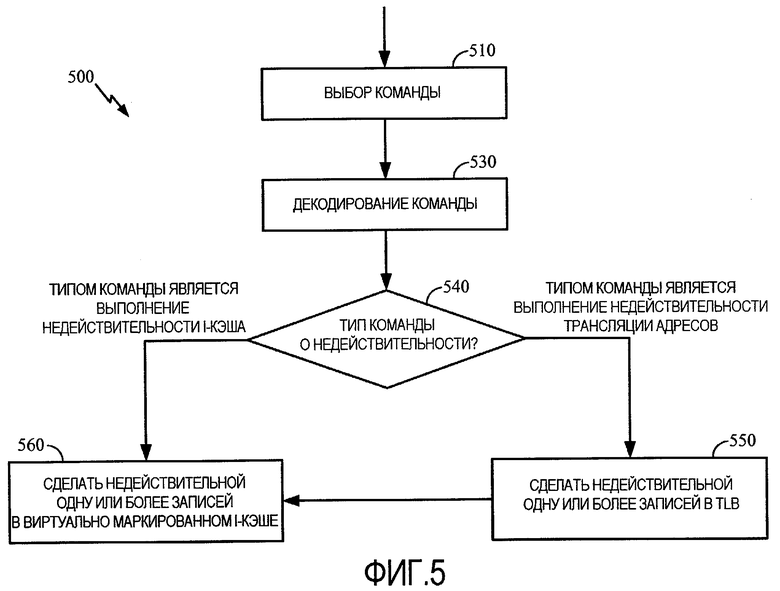

Фиг.5 - блок-схема последовательности операций, иллюстрирующая способ для виртуально маркированного кэша команд, чтобы действовать, как если бы он был физически маркированным кэшем команд с точки зрения компьютерной программы.

Подробное описание

Изложенное ниже подробное описание со ссылками на прилагаемые чертежи предназначено в качестве описания различных вариантов осуществления настоящего изобретения и не предназначено, чтобы представлять единственные варианты осуществления, в которых настоящее изобретение может быть осуществлено на практике. Подобное описание включает в себя конкретные детали с целью обеспечения всестороннего понимания настоящего изобретения. Тем не менее, специалистам в данной области техники будет очевидно, что настоящее изобретение может быть осуществлено на практике без этих конкретных деталей. В некоторых случаях широко известные структуры и компоненты показаны в форме блок-схемы, чтобы избежать запутывания идеи настоящего изобретения.

Фиг.1 изображает функциональную схему процессора 100. Процессор 100 исполняет команды в конвейере 120 исполнения команд согласно схеме 110 управляющей логики. Процессор 100 может быть любым типом компонента конвейерного процессора, включая, в качестве примера, микропроцессор, цифровой процессор сигналов (DSP), программируемую логику, схему на дискретных вентилях, или транзисторную логику, или любой другой компонент обработки информации. В некоторых вариантах осуществления конвейер 120 может быть суперскалярной конструкцией с множеством параллельных конвейеров. Конвейер 120 включает в себя различные регистры или защелки 160A-D, организованные в каскаде конвейера, и один или более модулей 180 исполнения. Хотя на фиг.1 изображены пять каскадов конвейера, специалисты в данной области техники признают, что каскады конвейера, большие или меньшие проиллюстрированных каскадов конвейера, могут включаться в процессор 100. Файл 130 регистра общего назначения (GPR) предоставляет регистры, составляющие вершину иерархии памяти. Процессор 100 включает в себя систему 127 кэша команд, которая включает в себя виртуально маркированный кэш 122 команд (I-кэш), буфер 128 быстрого преобразования адреса (TLB) и схему 110 управления.

Конвейер 120 выбирает команды из I-кэша 122 путем подачи виртуального адреса в I-кэш 122. Трансляция адресов памяти управляется при помощи TLB 128. Параллельно с подачей виртуального адреса I-кэшу 122 конвейер 120 выдает на TLB 128 виртуальный адрес команды, чтобы определить соответствующий физический адрес, который может использоваться для доступа к запоминающему устройству 150 через интерфейс 140 запоминающего устройства, если виртуальный адрес не найден в I-кэше 122 (промах кэша). Схема 110 управляющей логики принимает команды о недействительности от конвейера 120 и управляет обеспечением недействительности одной или нескольких записей в I-кэше 122 и TLB 128. Структура и работа системы 127 кэша команд полнее описываются применительно к описанию фиг.2.

К данным обращаются из кэша 126 данных (D-кэш) с помощью трансляции адресов памяти и разрешений, управляемых буфером 128 быстрого преобразования адреса (TLB). Хотя фиг.1 изображает TLB 128 как интегральный TLB, в различных вариантах осуществления TLB 128 может разделяться на множество TLB, где один выделен для трансляции обращений в D-кэш 126, а другие выделены для трансляции обращений в I-кэш 122. Промахи в I-кэше 122 и/или в D-кэше 126 служат причиной обращения к основной памяти 150 (вне кристалла) под управлением интерфейса 140 запоминающего устройства. Такое обращение к основной памяти использует физический адрес, извлеченный из TLB 128.

Процессор 100 может включать в себя интерфейс 134 ввода/вывода (I/O), управляющий доступом к различным периферийным устройствам 136 и 138. Специалисты в данной области техники признают, что возможны многочисленные вариации процессора 100. Например, процессор 100 может включать в себя кэш второго уровня (L2) для любого или двух вместе из I-кэша 122 и D-кэша 126. К тому же один или несколько функциональных блоков, изображенных в процессоре 100, могут быть опущены из конкретного варианта осуществления.

Фиг.2 - более подробное изображение системы 127 кэша команд из фиг.1. В этом типовом варианте осуществления TLB 128 конфигурируется имеющим три столбца 210A-210C. Столбец 210A содержит идентификаторы пространства приложения (ASID), ассоциированные с программными процессами. Регистр 215 содержит ASID исполняемого в настоящее время программного процесса, который может храниться в выделенном регистре или в файле 130 GPR. Столбец 210В содержит виртуальные метки TLB. Виртуальная метка TLB является частью виртуального адреса. Например, виртуальный адрес 205 является 32-разрядным адресом, сохраненным в регистре, таком как регистр счетчика команд (РС). В этом примере позиции разрядов 31-12 определяют часть виртуального адреса, определяющего виртуальную метку TLB.

Столбец 210С содержит 20-разрядные номера физических страниц (PPN), соответствующие сочетанию ASID / виртуальная метка TLB. Номер физической страницы возвращается из TLB 128, когда активный ASID (ассоциированный с исполнением программного процесса) и виртуальная метка TLB из виртуального адреса 205 соответствуют сочетанию (комбинации) метки ASID и виртуальной метки TLB, сохраненному в строке TLB 128. Возвращенный PPN конкатенируется со смещением страницы для определения соответствующего физического адреса. В частности, во время конкатенации возвращенный PPN помещается в позиции битов 31-12, тогда как часть смещения страницы в виртуальном адресе продолжает занимать позиции битов 11-0.

В этом типовом варианте осуществления виртуально маркированный I-кэш 122 является 32-килобайтным кэшем прямого отображения с 1024 "наборами из 1 строки" и 32-байтными строками. В данном варианте осуществления виртуально маркированный I-кэш 122 конфигурируется имеющим четыре столбца 220A-220D. Столбец 220A содержит идентификаторы пространства приложения (ASID), ассоциированные с программными процессами. Столбец 220В содержит виртуальные метки I-кэша (I$). Столбец 220С содержит 32-байтную магистраль команд, ассоциированную с конкретной комбинацией виртуальной метки I-кэша и ASID. Необязательно, столбец 220D содержит флаги, указывающие, при каком условии ассоциированная запись была сохранена в I-кэше, чтобы ограничить объем последующего задания недействительности записей.

Виртуальный адрес 205 изображается показывающим два наложенных значения для их битовых позиций. Когда виртуальный адрес 205 используется виртуально маркированным I-кэшем 122, битовые позиции 31-15 определяют виртуальную метку I-кэша (I$), битовые позиции 14-5 определяют индекс 207 для выбора одной строки или множества из 1024 "наборов из 1 строки" в I-кэше 122 и битовые позиции 4-0 определяют смещение в столбце 220С магистрали команд. Строка в I-кэше 122 прямого отображения также называется "набором из 1 строки". Хотя восемь 32-битовых команд, например, могут размещаться в одной магистрали команд, для простоты иллюстрируется одна команда на виртуальную метку I$. Следует отметить, что этим раскрытием изобретения предусматриваются другие размеры команд. Когда виртуальный адрес 205 используется в TLB 128 для трансляции адресов, битовые позиции 31-12 определяют виртуальную метку TLB, а позиции битов 11-0 определяют смещение страницы.

Во время поиска указанного виртуального адреса в I-кэше индекс 207 из виртуального адреса выбирает соответствующую строку в I-кэше 122. Активный ASID 215 и позиции битов 31-15 указанного виртуального адреса затем сравниваются с меткой ASID и виртуальной меткой I$, сохраненными в выбранной строке кэша.

Аналогичным образом, во время трансляции TLB для указанного виртуального адреса активный ASID 215 и позиции битов 31-12 указанного виртуального адреса сравниваются с метками ASID и виртуальными метками TLB, сохраненными в TLB 128, чтобы найти совпадение и, таким образом, соответствующий PPN.

Хотя и не проиллюстрировано здесь, в некоторых вариантах осуществления часть виртуального адреса, содержащая виртуальную метку TLB, может быть одной и той же частью виртуального адреса, содержащей виртуальную метку I-кэша. Специалисты в данной области техники признают, что несмотря на то, что виртуально маркированный I-кэш 122 иллюстрируется как кэш прямого отображения, I-кэш 122 может также быть реализован в качестве кэша с множественным доступом, чтобы обращаться к группам записей в виде наборов из нескольких строк.

Возвращаясь к TLB 128, изображаются как связь (отношение) псевдонимов, так и связь различения. Связь псевдонимов возникает, когда один и тот же номер физической страницы (PPN) располагается в двух или более записях в TLB 128. Например, обе записи 211 и 213 ссылаются на PPN 0x80000. В этом примере записи 211 и 213 имеют одинаковую виртуальную метку TLB, но ассоциированы с разными программными процессами, чтобы сделать уникальным сочетание (комбинацию) метки ASID / виртуальной метки TLB. Записи 212 и 214 также являются псевдонимами друг друга, поскольку обе ссылаются на PPN 0x90000. По отношению друг к другу записи 212 и 214 имеют уникальные виртуальные метки TLB и уникальные метки ASID, чтобы определить уникальное сочетание ASID / виртуальной метки TLB. Связь различения возникает, когда одна и та же виртуальная метка TLB соответствует двум или более разным номерам физических страниц. Записи 211 и 212 изображают связь различения, так как одна и та же виртуальная метка TLB (TLBtagA) соответствует двум разным номерам физических страниц, 0x80000 и 0x90000 соответственно.

Признавая, что виртуальные метки TLB и виртуальные метки I$ компонуются из позиций битов в виртуальном адресе (некоторые из них являются общими битовыми позициями), записи в TLB 128 относятся к записям в I-кэше 122. Поэтому ради условных обозначений использование нижнего индекса при ссылке на конкретную виртуальную метку I$ (например, I$tagA) указывает, что значение конкретной виртуальной метки I$ находится в связи со значением виртуальной метки TLB, имеющей тот же нижний индекс (например, TLBtagA). В примерном варианте осуществления на фиг.2 виртуальные метки TLB содержат больше битов, чем виртуальная метка I$. Следовательно, одна виртуальная метка TLB может соответствовать одной или более виртуальным меткам I$. Таким образом, одна запись TLB, имеющая номер физической страницы, может соответствовать одной или более записям I-кэша, означая, что команда или команды в I-кэше 122 также могут физически располагаться по номеру физической страницы соответствующей записи TLB. Для простоты следует отметить, что не иллюстрируются все записи I-кэша, относящиеся к конкретной записи TLB. Принимая во внимание описанную выше связь "один ко многим" между записями TLB и записями I-кэша, если заданная строка I-кэша ассоциируется с одной и той же меткой ASID и значением метки виртуального адреса в заданной строке TLB, то команда или команды в заданной строке I-кэша могут дополнительно располагаться на странице физического адресного пространства, соответствующей странице виртуального адресного пространства, ассоциированной с заданной строкой TLB.

Со временем записи в TLB 128 и в I-кэше 122 могут стать устаревшими. Например, если ASID повторно используется следующей неотносящейся компьютерной программой и преобразования виртуального [адреса] в физический у следующей программы иные, чем у предыдущей программы, то записи в TLB и I-кэше, содержащие повторно используемый ASID, уже не будут верными, так как они будут преобразованы в физические адреса, ассоциированные с предыдущей компьютерной программой. Для поддержания когерентности TLB и кэша используется схема 110 управляющей логики для управления устаревшими записями как в TLB 128, так и в I-кэше 122. Вообще компьютерные программы, написанные для физически маркированного I-кэша, могут быть проще, чем написанные для виртуально маркированного I-кэша в отношении управления устаревшими записями в I-кэше по разным причинам, включая то, что проблема псевдонимов не существует в физически маркированном I-кэше, и то, что простая замена преобразований виртуального адреса в физический не требует недействительности I-кэша в физически маркированном I-кэше. Однако компьютерные программы, написанные как для физически маркированных I-кэшей, так и написанные для виртуально маркированных I-кэшей, должны включать в себя явные команды о недействительности TLB при изменении соответствия заданного виртуального адреса для заданного идентификатора процесса с одного физического адреса на другой.

Существуют два основных класса сценариев, где записи I-кэша должны быть сделаны недействительными с помощью виртуально маркированного кэша команд. Первый класс сценариев касается изменений в преобразовании адресов, где, например, виртуальный адрес становится преобразованным в другой физический адрес. В традиционных реализациях виртуально маркированного I-кэша команды о недействительности I-кэша используются, чтобы сделать недействительными I-кэш по этому классу сценариев. Кроме того, в первом классе сценариев команды о недействительности TLB используются, чтобы сделать недействительным TLB в традиционных реализациях виртуально маркированного I-кэша и физически маркированного I-кэша. Второй класс сценариев затрагивает ситуацию, где меняется содержимое физической памяти. Во втором классе сценариев команды о недействительности I-кэша используются, чтобы сделать недействительным I-кэш в традиционных реализациях виртуально маркированного I-кэша и физически маркированного I-кэша. Однако в традиционных реализациях физически маркированного I-кэша команда о недействительности I-кэша должна лишь идентифицировать физический адрес измененной памяти, чтобы сделать (ее) недействительной, в отличие от всех возможных виртуальных адресов, которые могут принадлежать этому физическому адресу в традиционной реализации виртуально маркированного I-кэша.

Схема 110 управляющей логики конфигурируется для распознавания, что первый класс сценариев, который традиционно требовал бы от компьютерной программы запускать явную недействительность I-кэша для виртуально маркированного I-кэша, также требует от компьютерной программы вызывать недействительность TLB даже для физически маркированного I-кэша. Например, один сценарий включает в себя ситуацию, когда комбинация ASID / виртуальной метки TLB преобразуется в новый номер физической страницы. В этом сценарии схема 110 управляющей логики в ответ на явную команду о недействительности TLB делает недействительными записи в TLB 128, касающиеся комбинации ASID / виртуальной метки TLB, и также делает недействительными записи в виртуально маркированном I-кэше 122, касающиеся комбинации ASID / виртуальной метки I-кэша. В некоторых вариантах осуществления явная команда о недействительности TLB вызывает мгновенную недействительность всех записей в I-кэше 122 независимо от заданной комбинации ASID / виртуальной метки TLB.

Что касается второго класса сценариев, направленного на модификации, сделанные в содержимом заданного физического адреса, компьютерная программа выдает явную команду о недействительности I-кэша, чтобы вызвать обновление I-кэша 122. Содержимое явной команды о недействительности I-кэша может указывать или не указывать виртуальный адрес, ассоциированный с измененным физическим адресом, или измененный физический адрес.

В одном варианте осуществления схема 110 управляющей логики в ответ на эту явную команду о недействительности I-кэша конфигурируется для мгновенной недействительности всех записей в виртуально маркированном I-кэше 122. В этом варианте осуществления виртуальный адрес, ассоциированный с заданным физическим адресом, или, в качестве альтернативы, заданный физический адрес может быть указан в явной команде о недействительности I-кэша. Однако, поскольку все записи I-кэша мгновенно становятся недействительными, указанный виртуальный или физический адрес у явной команды недействительности I-кэша просто игнорируется.

В альтернативном варианте осуществления схема 110 управляющей логики в ответ на явную команду о недействительности I-кэша конфигурируется для выборочной недействительности записей в виртуально маркированном I-кэше 122. Так как записи I-кэша, как правило, имеют виртуальные метки, которые соответствуют физическому адресу, записи I-кэша, которые могут соответствовать указанному физическому адресу, нужно будет сделать недействительными. Обратимся к записям в строках 212 и 214 в TLB 128 для примера идентификационной информации множества виртуальных адресов, для которых соответствующие записи виртуально маркированного I-кэша нужно будет сделать недействительными в результате изменения содержимого физического адреса. Эти записи являются записями-псевдонимами и преобразуются в один и тот же номер 0x90000 физической страницы.

Аналогичным образом, записи 225 и 224 I-кэша содержат команды, которые также находятся по физическому адресу, определенному первыми 17 битами номера физической страницы, потому что значение виртуальных меток I$ (I$tagA и I$tagB) относятся к значению виртуальных меток TLB (TLBtagA и TLBtagB) соответственно, как проиллюстрировано двойным наложенным значением позиций битов в виртуальном адресе 205, рассмотренным выше. Следовательно, если, например, содержимое физического адреса 0x9000_0000 изменяется, то записи 225 и 224 вместе с любыми другими непроиллюстрированными записями, чьи команды также находятся по физическому адресу 0x9000_0000, будут выборочно сделаны недействительными схемой 110 управляющей логики. Конкретнее, в этом варианте осуществления выполнения выборочной недействительности записей в виртуально маркированном I-кэше 122 схема 110 управляющей логики конфигурируется, чтобы сделать недействительными все записи, ассоциированные с конкретными виртуальными индексами I-кэша, на которых указанный физический адрес мог бы располагаться, например все записи в выбранных множествах I-кэша.

Фиг.3 - блок-схема, иллюстрирующая выполнение выборочной недействительности множества записей виртуально маркированного I-кэша, которые могли быть ассоциированы с физическим адресом в I-кэше 122 прямого отображения. Как изображено в виртуальном адресе 205, позиции битов 14-12, или ссылка 305, являются частью битов индекса, также называемых битами индекса I-кэша, когда виртуальный адрес 205 используется виртуально маркированным I-кэшем 122. Позиции битов 14-12 также являются частью виртуальной метки TLB. Однако, поскольку позиции битов 14-12 являются транслированными битами во время трансляции адресов, эти же биты являются частью номера физической страницы, соответствующего виртуальному адресу 205. Так как позиции битов 14-12 не используются виртуальной меткой I$ и номер физической страницы может указываться для выполнения недействительности, каждая комбинация битов 14-12 определяет границы 0, 128, 256,... 896 в виртуально маркированном I-кэше 122, где могла бы располагаться ассоциированная запись I-кэша, соответствующая номеру физической страницы. Оставшиеся биты индекса, биты 11-5 или ссылка 315, не транслируются во время трансляции адресов и, таким образом, являются общими между виртуальным адресом 205 и его транслированным физическим адресом. Следовательно, биты 11-5 указывают смещение от определенных границ, чтобы обнаружить соответствующие записи I-кэша, возможно, относящиеся к физической странице. Так как ссылка 305 содержит три бита, схема 110 управляющей логики в ответ на физический адрес, который должен быть сделан недействительным, может конфигурироваться для одновременного осуществления недействительности восьми записей в виртуально маркированном I-кэше 122 путем объединения каждой комбинации битов 14-12 с битами 11-5 физического адреса.

Как правило, поскольку биты 11-0 не становятся транслированными с помощью трансляции адресов, они не отличаются между указанным физическим адресом и любыми виртуальными адресами, которые могли бы транслировать в этот физический адрес. Другими словами, все виртуальные адреса, которые могут соответствовать указанному физическому адресу, обязаны совпадать с физическим адресом в битах 11-0. Следовательно, любые биты из этих в позициях 11-0, которые используются как часть индекса I-кэша, чтобы выбрать набор I-кэша, который может содержать записи, соответствующие указанному физическому адресу, должны иметь то же значение, что и соответствующие биты из физического адреса. Это только те биты индекса I-кэша в позициях 14-12, например, которые могут принять другое значение, чем соответствующие биты из физического адреса, все еще идентифицирующие набор записей, возможно, содержащих записи, соответствующие указанному физическому адресу.

В ответ на явную команду о недействительности I-кэша, идентифицирующую физический адрес, который нужно сделать недействительным из I-кэша из-за того, что содержимое этого физического адреса изменилось, схема 110 управляющей логики использует позиции битов 11-5 для определения смещений от границ, определенных битами 14-12, чтобы сделать недействительными все записи в транслированном наборе подходящих записей в I-кэше, позволяя сделать недействительным I-кэш на основе набора, а не на основе всего I-кэша. С помощью одной команды, указывающей физический адрес, который необходимо сделать недействительным, или, в качестве альтернативы, виртуальный адрес, ассоциированный с недействительным физическим адресом, этот вариант осуществления дает возможность программному обеспечению, написанному для модели физически маркированного I-кэша, автоматически запускать операцию выполнения недействительности I-кэша на виртуально маркированном I-кэше, чтобы гарантировать, что все возможные псевдонимы виртуальных адресов для указанного физического адреса становятся удаленными из кэша. Как описано, такое удаление может быть на основе строки, набора или всего кэша. Таким образом, виртуально маркированный I-кэш должным образом управляется без какой-либо дополнительной нагрузки на программное обеспечение, которое было написано для модели физически маркированного I-кэша.

Количество одновременных индексов в виртуально маркированном I-кэше 122 с помощью схемы 110 управляющей логики зависит от множественной ассоциативности виртуально маркированного I-кэша. Фиг.4 - блок-схема, иллюстрирующая выборочное выполнение недействительности набора записей виртуально маркированного I-кэша, которые могли быть ассоциированы с физическим адресом в двухвходовом I-кэше 422 с множественным доступом. Помимо его ассоциативности, двухвходовый I-кэш 422 с множественным доступом является 32-килобайтным виртуально маркированным I-кэшем с 32-байтными строками и, соответственно, может быть аналогичен I-кэшу 222. Виртуальный адрес 405 является 32-разрядным (битовым) адресом, сохраненным в регистре, например в счетчике команд (РС), и аналогично виртуальному адресу 205 изображается показывающим два перекрывающихся значения для его битовых позиций. I-кэш 422 имеет индекс 418, имеющий размер девять битов, и, соответственно, виртуальную метку I$, имеющую размер 18 битов. Для этого варианта осуществления позиции битов 13-12 или транслированные битовые позиции 410 определят четыре границы, получив в результате четыре одновременных индекса, и позиции битов 11-5 или нетранслированные битовые позиции 415 определили бы смещение от каждой из четырех границ, чтобы выборочно сделать недействительными строки в виртуально маркированном I-кэше. В двухвходовом кэше с множественным доступом каждая строка включает в себя две строки кэша. Следовательно, схема 110 управляющей логики одновременно индексирует четыре строки кэша и, таким образом, делает недействительными восемь записей виртуально маркированного I-кэша.

Следует отметить, что различные размеры и конфигурации виртуально маркированных I-кэшей рассматриваются в качестве дополнительных вариантов осуществления. В качестве примера, 4-входовый вариант осуществления с множественным доступом 32-килобайтного виртуально маркированного I-кэша с 32-байтными строками дают в результате индекс, имеющий размер в восемь битов, и, соответственно, виртуальную метку I$, имеющую размер 19 битов. Для 4-входового I-кэша с множественным доступом позиция битов 12 определила бы две границы, и позиции битов 11-5 определят смещение от двух границ, чтобы выборочно сделать недействительными записи в 4-входовом I-кэше.

В качестве другого примера, 8-входовый вариант осуществления с множественным доступом 32-килобайтного виртуально маркированного I-кэша с 32-байтными строками дает в результате индекс, имеющий размер в семь битов, и, соответственно, виртуальную метку I$, имеющую размер 20 битов, тот же размер виртуальной метки TLB и фактически номер физической страницы. Для 8-входового I-кэша с множественным доступом нет определенных границ, и позиции битов 11-5 индексируют в 8-входовый кэш. Отметим, однако, что каждая строка в 8-входовом кэше содержит 8 строк кэша, восемь строк кэша выборочно становятся недействительными. Кроме того, поскольку в этом примере размер виртуальной метки TLB равен размеру виртуальной метки I$, любые записи в I-кэше, которые могут быть ассоциированы с указанным физическим адресом, гарантированно располагаются на входе I-кэша, выбранном одним индексом I-кэша, который, в свою очередь, аналогичен позициям битов индекса из указанного физического адреса, так как эти позиции битов не транслируются. Другими словами, когда все биты индекса I-кэша находятся в битовых позициях в смещении на странице, соответственно, биты индекса I-кэша не становятся транслированными с помощью механизма трансляции адресов, любые записи в I-кэше, которые могут быть ассоциированы с указанным физическим адресом, гарантированно располагаются во входе I-кэша, выбранном этим одним индексом I-кэша.

Эти предыдущие примеры демонстрируют, как виртуально индексированный и виртуально маркированный I-кэш с множественным доступом в соответствии с идеями этого раскрытия изобретения влияет на выборочное выполнение недействительности. В частности, чем выше множественный доступ виртуально индексированного и виртуально маркированного кэша, тем меньше количество битов, которые транслируются процессом трансляции адресов, но которые используются в их нетранслированной форме в индексе I-кэша, приводя к меньшему количеству выборочно недействительных строк I-кэша. Аналогичным образом размер физической страницы влияет на количество разрядов адреса, которые становятся транслированными. Так как размер страницы увеличивается, транслируется меньше битов верхнего порядка в виртуальном адресе. Следовательно, чем больше размер страницы, тем меньше количество битов, которые транслируются процессом трансляции адресов, но которые используются в их нетранслированной форме для индекса I-кэша, снова приводя к меньшему количеству выборочно недействительных строк/множеств I-кэша.

В случае где количество битов в номере физической страницы то же, что и количество битов в виртуальной метке I-кэша, отсутствуют биты 305 в индексе I-кэша, которые, в конечном счете, подвергаются трансляции с помощью процесса трансляции адресов. Таким образом, множество возможных входов I-кэша уменьшается на один гарантированный вход. Вообще увеличение размера страницы приводит к меньшей трансляции битов, и, таким образом, уменьшается размер возможных записей I-кэша, ассоциированных с физическим адресом.

Возвращаясь к фиг.2, схема 110 управляющей логики принимает в качестве входных данных команды о недействительности, например Команды о недействительности TLB и Команды о недействительности I-кэша от компьютерной программы, независимо от того, написана компьютерная программа с физически маркированным I-кэшем либо виртуально маркированным I-кэшем. Эти команды о недействительности могут предоставляться от каскада декодирования в конвейере 120, такого как каскад 160В конвейера, например Схема 110 управляющей логики реагирует на множество Команд о недействительности TLB, чтобы сделать недействительной одну или более записей в I-кэше 122, используя известные механизмы, такие как формирование управляющих сигналов I-кэша, чтобы сделать недействительной одну или более записей I-кэша в ответ на известные команды о недействительности I-кэша. С помощью реагирования на множество Команд о недействительности TLB для дополнительного управления I-кэша и реагирования на команду о недействительности I-кэша для сценария, указывающего, что содержимое физического адреса изменилось, схема 110 управляющей логики освобождает компьютерную программу от необходимости выдавать команды о недействительности I-кэша отдельно для каждого сценария, что требует традиционный виртуально маркированный I-кэш. Следовательно, компьютерные программы, которые написаны для управления физически маркированным I-кэшем, можно теперь успешно исполнять на процессоре 100, управляющем виртуально индексированным, виртуально маркированным I-кэшем, так что он ведет себя, как если бы он был физически индексированным и физически маркированным с позиции программного обеспечения.

Схема 110 управляющей логики также реагирует на известные команды о недействительности I-кэша, чтобы сделать недействительной одну или более записей в виртуально маркированном I-кэше 122, для существующих компьютерных программ, которые написаны для управления виртуально маркированным I-кэшем. Дополнительно в некоторых вариантах осуществления схема 110 управляющей логики может принимать необязательный разрешающий сигнал 237 от процессора 100, который может использоваться, если исполняются компьютерные программы, специально написанные для виртуально маркированного I-кэша. Разрешающий сигнал 237 может вызываться как результат разряда состояния процессора, разряда конфигурации и т.п. Когда вызывается разрешающий сигнал 237, схема 110 управляющей логики работает, как описано выше. Когда разрешающий сигнал 237 не вызывается (запрещен), схема 110 управляющей логики будет реагировать на Команды о недействительности TLB, чтобы сделать недействительной одну или более записей из TLB 128, и будет реагировать на Команды о недействительности I-кэша, чтобы сделать недействительной одну или более записей в виртуально маркированном I-кэше 122. Когда разрешающий сигнал 237 не вызывается (запрещен), схема 110 управляющей логики не будет делать недействительными записи в виртуально маркированном I-кэше 122 в ответ на Команды о недействительности TLB и не будет обязательно делать недействительными больше записей I-кэша, чем те специально ассоциированные с указанным виртуальным адресом, в ответ на Команды о недействительности I-кэша.

В некоторых вариантах осуществления схема 110 управляющей логики может включать в себя генератор 235 управляющего сигнала TLB и генератор 245 управляющего сигнала I-кэша. Входы 241 и 243 в генератор 245 управляющего сигнала I-кэша соответственно подают Команды о недействительности TLB и Команды о недействительности I-кэша в генератор 245 управляющего сигнала I-кэша. Генератор 245 управляющего сигнала I-кэша конфигурируется для формирования управляющих сигналов, чтобы сделать недействительной одну или более записей в виртуально маркированном I-кэше 122 на основе принятой команды о недействительности. Генератор 235 управляющего сигнала TLB формирует управляющие сигналы известным образом, чтобы сделать недействительной одну или более записей в TLB 128 на основе конкретного типа принятой команды о недействительности TLB. Когда вход в генератор 245 управляющего сигнала I-кэша является результатом команды о недействительности I-кэша, генератор 245 управляющего сигнала I-кэша формирует управляющие сигналы известным образом, чтобы сделать недействительной одну или более записей в виртуально маркированном I-кэше 122. Дополнительно генератор 245 управляющего сигнала I-кэша формирует управляющие сигналы, чтобы сделать недействительной одну или более записей в виртуально маркированном I-кэше 122 в ответ на Команды о недействительности TLB. Следующая таблица описывает функциональное поведение генератора 245 управляющего сигнала I-кэша, обусловленное приемом следующих Команд о недействительности TLB.

Столбец 220D является одним вариантом осуществления, чтобы убедиться, что отсутствует ошибочное "совпадение" с записью в I-кэше 122 на основе сравнения виртуальной метки, когда запись была установлена во время, когда механизм трансляции был в одном состоянии разблокирования (разрешения), но совпадение возникает в более позднее время, когда механизм трансляции находится другом состоянии разблокирования (разрешения). Например, в ситуации, где механизм трансляции, такой как TLB 128, обладает функцией разрешения, которая позволяет TLB 128 находиться в разрешенном или запрещенном состоянии, сохраненные в I-кэше 122 записи могут содержать флаговое значение, указывающее, работало ли TLB в то время, когда была сохранена запись. Когда запись сохраняется в I-кэше во время неработающего TLB 128, сохраненная запись ассоциируется с физическим адресом, который является тем же самым, что и нетранслированный виртуальный адрес.

В случае переключений TLB из запрещения в разрешение записи I-кэша, которые были сохранены во время неработающего TLB, делаются недействительными схемой 110 управляющей логики в ответ на сигнал 239 переключения (перехода) TLB. Также в случае переключений TLB из разрешения в запрещение записи I-кэша, которые были сохранены во время работающего TLB, делаются недействительными схемой 110 управляющей логики в ответ на сигнал 239 переключения TLB. Сигнал 239 перехода TLB обычно формируется при переходах TLB 128 из запрещения в разрешение и наоборот. В частности, генератор 245 управляющего сигнала I-кэша в ответ на сигнал 239 перехода TLB формирует управляющие сигналы, чтобы сделать недействительными записи в I-кэше 122, которые совпадают с флаговым полем, указывающим записи, которые были вначале сохранены, пока TLB 128 находился в состоянии, из которого он только что переключился. В альтернативном варианте осуществления могут устанавливаться флаги столбца 220D, когда состояние адресной таблицы является разрешенным. В данном варианте осуществления, когда выполняется поиск в I-кэше, рассматриваются флаги, чтобы определить, есть ли совпадение с текущим состоянием адресной таблицы.

В другом альтернативном варианте осуществления проблема обеспечения того, что не возникает ошибочного "совпадения" с записью I-кэша, установленной в предыдущем противоречивом состоянии, устраняется без необязательного столбца 220D. В данном варианте осуществления схема 110 управляющей логики мгновенно делает недействительным весь кэш 122, когда сигнал 239 перехода разрешения TLB указывает, что было переключение в механизме разрешения TLB.

Специалистам в данной области техники следует признать, что размер виртуального адреса 205 и размерности TLB 128 и I-кэша 122 могут применяться к другим вариантам осуществления без отклонения от идей изобретения.

Фиг.5 - блок-схема операций, иллюстрирующая способ 500, чтобы заставить виртуально маркированный кэш команд действовать, как если бы он был физически маркированным кэшем команд с точки зрения компьютерной программы. На функциональном этапе 510 способ выбирает команду.

Выбранная команда направляется к декодеру 530 команд, где выбранная команда декодируется. На этапе 540 способ определяет тип команды. Если типом команды является команда о недействительности трансляции адресов, способ переходит к этапу 550, который делает недействительной одну или более записей в TLB, например TLB 128, в соответствии с командой о недействительности трансляции адресов. Далее способ переходит к этапу 560. На этапе 560 способ также делает недействительной одну или более записей в I-кэше 122 в соответствии с преобразованием команд о недействительности трансляции адресов, например, как определено в Таблице 1. Специалисты в данной области техники примут во внимание, что порядок этапа 550 и этапа 560 может быть изменен без затрагивания процесса выполнения недействительности. Возвращаясь к этапу 540, если типом команды является команда о недействительности I-кэша, то способ переходит к этапу 560, чтобы сделать недействительной одну или более записей в I-кэше 122 в соответствии с командой о недействительности I-кэша. Возвращаясь к этапу 540, если типом команды не является команда о недействительности какого-либо типа, то возвращаются к этапу 510 для выбора следующей команды.

Различные пояснительные логические блоки, модули, схемы, элементы и/или компоненты, описанные применительно к вариантам осуществления, раскрытым в этом документе, могут быть реализованы или выполнены с помощью процессора общего назначения, цифрового процессора сигналов (DSP), специализированной интегральной схемы (ASIC), программируемой пользователем вентильной матрицы (FPGA) или другого программируемого логического компонента, схемы на дискретных компонентах или транзисторной логики, дискретных аппаратных компонентов или любого их сочетания, спроектированных для выполнения функций, описанных в этом документе. Процессором общего назначения может быть микропроцессор, но в альтернативном варианте процессором может быть любой типовой процессор, контроллер, микроконтроллер или конечный автомат. Процессор также может быть реализован в виде комбинации вычислительных компонентов, например сочетания DSP и микропроцессора, множества микропроцессоров, одного или более микропроцессоров совместно с ядром DSP или любой другой подобной конфигурации.

Способы или алгоритмы, описанные применительно к раскрытым в этом документе вариантам осуществления, могут быть реализованы непосредственно в аппаратных средствах, в программном модуле, исполняемом процессором, или в их сочетании. Модуль программного обеспечения может находиться в памяти ОЗУ, флэш-памяти, памяти ПЗУ, памяти EPROM (электрически программируемого ПЗУ), памяти EEPROM (электрически стираемого и программируемого ПЗУ), регистрах, на жестком диске, съемном диске, компакт-диске или любом другом виде носителя информации, известного в данной области техники. Носитель информации может быть соединен с процессором так, что процессор может считывать информацию и записывать информацию на носитель информации. В альтернативном варианте носитель информации может составлять единое целое с процессором.

Хотя изобретение раскрывается в контексте вариантов осуществления, нельзя не отметить, что обычными специалистами в данной области может применяться широкий спектр реализаций с учетом вышеприведенного обсуждения и формулы изобретения, которая следует ниже.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ТРАНСЛЯЦИИ АДРЕСА | 2008 |

|

RU2461870C2 |

| СПОСОБ МОДИФИКАЦИИ РАЗРЕШЕНИЙ НА ДОСТУП К ПАМЯТИ В ЗАЩИЩЕННОЙ ПРОЦЕССОРНОЙ СРЕДЕ | 2014 |

|

RU2602793C2 |

| СРАВНЕНИЕ И ЗАМЕНА ПОЗИЦИИ ТАБЛИЦЫ ДИНАМИЧЕСКОЙ ТРАНСЛЯЦИИ АДРЕСА | 2012 |

|

RU2550558C2 |

| СПОСОБЫ И УСТРОЙСТВА ДЛЯ СОКРАЩЕНИЯ ПОИСКОВ В КЭШЕ ЦЕЛЕВЫХ АДРЕСОВ ВЕТВЛЕНИЙ | 2007 |

|

RU2419835C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ УМЕНЬШЕНИЯ ПОТРЕБЛЯЕМОЙ МОЩНОСТИ В АССОЦИАТИВНОЙ ПАМЯТИ | 2007 |

|

RU2414014C2 |

| ЭФФЕКТИВНОЕ УПРАВЛЕНИЕ ИЕРАРХИЕЙ ПАМЯТИ | 2007 |

|

RU2397534C2 |

| Связанное с выбранными архитектурными функциями администрирование обработки | 2015 |

|

RU2665243C2 |

| ИСПОЛЬЗОВАНИЕ АУТЕНТИФИЦИРОВАННЫХ МАНИФЕСТОВ ДЛЯ ОБЕСПЕЧЕНИЯ ВНЕШНЕЙ СЕРТИФИКАЦИИ МНОГОПРОЦЕССОРНЫХ ПЛАТФОРМ | 2014 |

|

RU2599340C2 |

| УСТРОЙСТВО, СПОСОБ И СИСТЕМА УПРАВЛЕНИЯ МАТРИЦАМИ | 2010 |

|

RU2491616C2 |

| ИНДИКАТОР ИЗМЕНЕНИЙ ДЛЯ УМЕНЬШЕНИЯ ПОТРЕБЛЕНИЯ ЭНЕРГИИ ПРИ НЕУДАЧНЫХ ОБРАЩЕНИЯХ К КЭШ-ПАМЯТИ | 2006 |

|

RU2390855C2 |

Изобретение относится к системам обработки, точнее, к системам виртуально маркированного кэша команд. Техническим результатом является обеспечение полезной мощности, частоты и пропускной способности команд при использовании виртуально маркированного кэша команд. Система содержит: виртуально маркированный кэш команд, средство для трансляции адресов, причем упомянутое средство реагирует на команду о недействительности трансляции адресов, и схему управляющей логики, сконфигурированную, чтобы сделать недействительными менее чем все записи в виртуально маркированном кэше команд в ответ на команду о недействительности трансляции адресов. 3 н. и 17 з.п. ф-лы, 5 ил., 1 табл.

1. Система кэширования команд, содержащая:

виртуально маркированный кэш команд;

средство для трансляции адресов, причем упомянутое средство реагирует на команду о недействительности трансляции адресов; и

схему управляющей логики, сконфигурированную, чтобы сделать недействительными менее чем все записи в виртуально маркированном кэше команд в ответ на команду о недействительности трансляции адресов.

2. Система по п.1, в которой средством для трансляции адресов является буфер быстрого преобразования адреса (TLB).

3. Система по п.1, в которой схема управляющей логики конфигурируется для выполнения мгновенной недействительности виртуально маркированного кэша команд в ответ на команду о недействительности трансляции адресов.

4. Система по п.1, в которой схема управляющей логики конфигурируется, чтобы сделать недействительной одну или более записей в виртуально маркированном кэше команд, соответствующих идентификатору службы приложения (ASID), указанному командой о недействительности трансляции адресов.

5. Система по п.1, в которой схема управляющей логики конфигурируется, чтобы сделать недействительным выборочный набор записей в виртуально маркированном кэше команд, соответствующий индексу, указанному в команде недействительности трансляции адресов.

6. Система по п.1, в которой схема управляющей логики конфигурируется для выполнения мгновенной недействительности виртуально маркированного кэша команд в ответ на изменение состояния средства для трансляции адресов.

7. Система по п.1, в которой схема управляющей логики содержит вход для приема сигнала разрешения, причем схема управляющей логики конфигурируется, только чтобы сделать недействительной запись в виртуально маркированном кэше команд в ответ на команду о недействительности трансляции адресов после приема сигнала разрешения.

8. Система по п.1, в которой схема управляющей логики конфигурируется для выполнения мгновенной недействительности виртуально маркированного кэша команд в ответ на команду о недействительности кэша команд, указывающую о недействительности указанного физического адреса.

9. Система по п.5, в которой индекс содержит транслированные битовые позиции и нетранслированные битовые позиции,

где каждая комбинация значений транслированных битовых позиций определяет границы в виртуально маркированном кэше команд,

причем схема управляющей логики дополнительно конфигурируется для выполнения выборочной недействительности записей при смещении от определенных границ, причем смещение указано значением нетранслированных битовых позиций.

10. Система по п.1, которая расположена в процессоре.

11. Способ работы виртуально маркированного кэша команд, как если бы он был физически маркированным кэшем команд с точки зрения компьютерной программы, содержащий этапы, на которых:

принимают команду о недействительности трансляции адресов; и делают недействительными менее чем все записи в виртуально маркированном кэше команд в ответ на команду о недействительности трансляции адресов.

12. Способ по п.11, в котором этап, на котором делают недействительной запись в виртуально маркированном кэше команд, дополнительно содержит этап, на котором:

мгновенно делают недействительным виртуально маркированный кэш команд.

13. Способ по п.11, в котором этап, на котором делают недействительной запись в виртуально маркированном кэше команд, дополнительно содержит этап, на котором:

делают недействительной одну или более записей, соответствующих идентификатору службы приложения (ASID), указанному командой о недействительности трансляции адресов.

14. Способ по п.11, в котором этап, на котором делают недействительной запись в виртуально маркированном кэше команд, дополнительно содержит этап, на котором:

делают недействительным набор выборочных записей, соответствующий адресу, указанному командой о недействительности трансляции адресов.

15. Способ по п.11, в котором этап, на котором делают недействительной запись в виртуально маркированном кэше команд, дополнительно содержит этап, на котором:

мгновенно делают недействительным виртуально маркированный кэш команд в ответ на изменение состояния средства для трансляции адресов.

16. Способ по п.11, в котором этап, на котором делают недействительной запись в виртуально маркированном кэше команд, дополнительно содержит этап, на котором:

принимают сигнал разрешения; и

делают недействительной запись в виртуально маркированном кэше команд после приема сигнала разрешения.

17. Способ по п.11, в котором этап, на котором делают недействительной запись в виртуально маркированном кэше команд, дополнительно содержит этап, на котором:

принимают команду о недействительности кэша команд, указывающую недействительность указанного физического адреса; и

мгновенно делают недействительным виртуально маркированный кэш команд в ответ на команду о недействительности кэша команд.

18. Схема управляющей логики для инструктирования виртуально маркированному кэшу команд действовать, как если бы он был физически маркированным кэшем команд, с точки зрения компьютерной программы, содержащая:

первый вход для приема команды о недействительности трансляции адресов; и

средство для формирования управляющих сигналов, чтобы сделать недействительными менее чем все записи в виртуально маркированном кэше команд в ответ на команду о недействительности трансляции адресов.

19. Схема управляющей логики по п.18, дополнительно содержащая: второй вход для приема команды о недействительности кэша команд, причем упомянутое средство для формирования управляющих сигналов также реагирует на команду о недействительности кэша команд.

20. Схема управляющей логики по п.19, дополнительно содержащая:

третий вход для запрещения средству для формирования управляющих сигналов делать недействительными записи в виртуально маркированном кэше команд в ответ на команду о недействительности трансляции адресов.

| НОВЫЙ РЕЖИМ ПРОЦЕССОРА ДЛЯ ОГРАНИЧЕНИЯ ФУНКЦИОНИРОВАНИЯ ГОСТЕВОГО ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ, ВЫПОЛНЯЮЩЕГОСЯ НА ВИРТУАЛЬНОЙ МАШИНЕ, ПОДДЕРЖИВАЕМОЙ МОНИТОРОМ ВИРТУАЛЬНОЙ МАШИНЫ | 2001 |

|

RU2265880C2 |

| US 6412043 B1, 25.06.2002 | |||

| US 6338128 B1, 08.01.2002 | |||

| US 6079005, 20.06.2000 | |||

| US 5003459, 26.03.1991. | |||

Авторы

Даты

2011-11-10—Публикация

2007-04-17—Подача