Область техники, к которой относится изобретение

Настоящее изобретение, в общем, относится к вычислительной системе и, в частности (но не исключительно), к периодам времени возобновления работы для корневых портов и конечных точек, интегрированных в корневые порты.

Уровень техники

Так как электронные устройства становятся все более сложными и повсеместно используются в повседневной жизни пользователей, к ним предъявляется все больше и больше разнообразных требований. Чтобы удовлетворить большинство из этих требований, ряд электронных устройств содержит многочисленные электронные устройства, таких как центральное процессорное устройство (ЦПУ), устройство связи, графический ускоритель и т.д. Во многих случаях между этими устройствами можно устанавливать связь с большим объемом передаваемых данных. Кроме того, многие пользователи испытывают большие надежды, связанные с техническими характеристиками устройство. Пользователи становятся все менее терпимыми к большому времени ожидания операций, выполняемых их устройствами. В дополнение к этому, многие устройства выполняют все более сложные и тяжелые задачи, которые могут приводить к большим объемам передачи данных между устройствами. Поэтому между этими устройствами можно поддерживать связь, которая будет преимущественной от быстрого времени срабатывания.

Краткое описание чертежей

Варианты осуществления проиллюстрированы посредством примера, а не посредством ограничения, на фигурах сопроводительных чертежей одинаковые ссылочные позиции показывают аналогичные элементы, при этом:

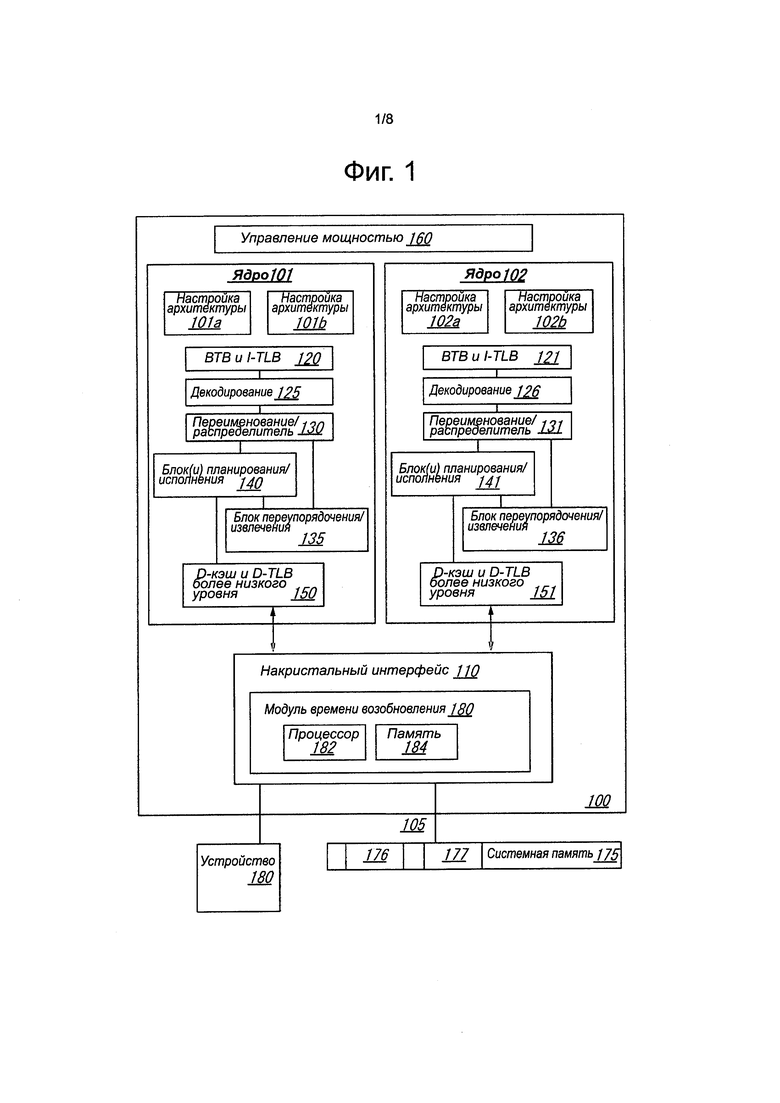

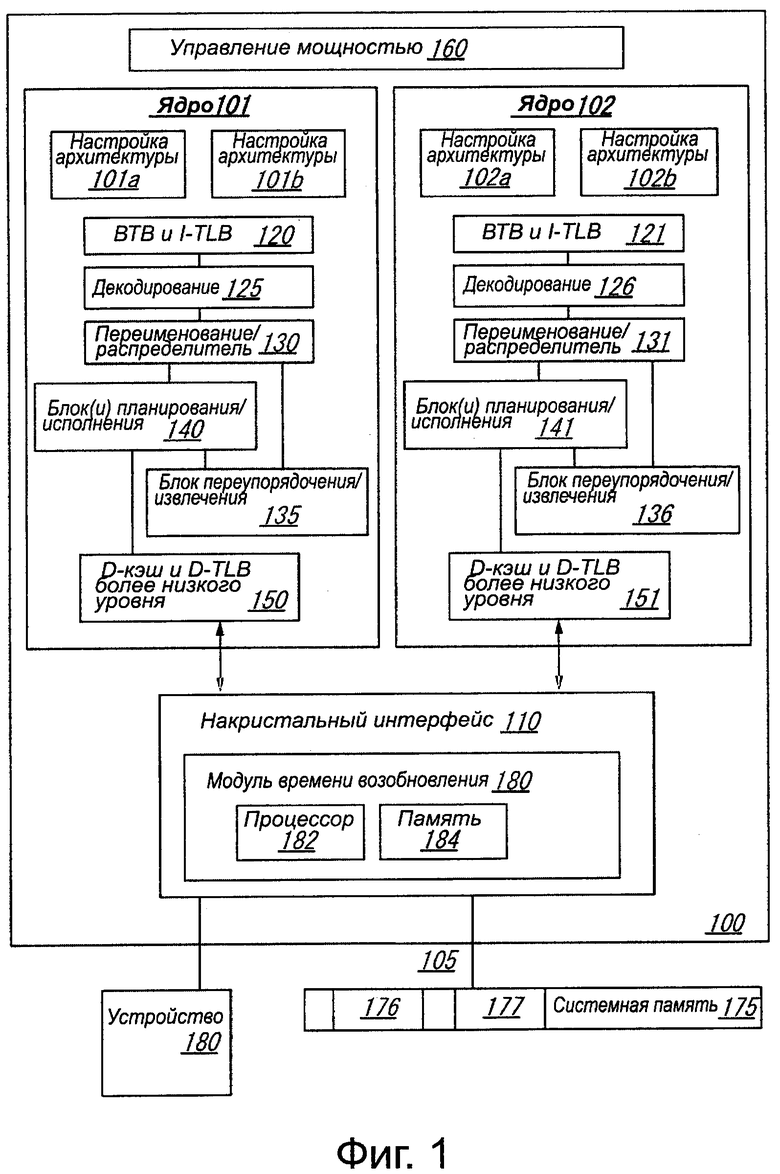

фиг. 1 иллюстрирует варианты осуществления блок-схемы вычислительной системы, включающие в себя многоядерный процессор, согласно по меньшей мере одному примерному варианту осуществления;

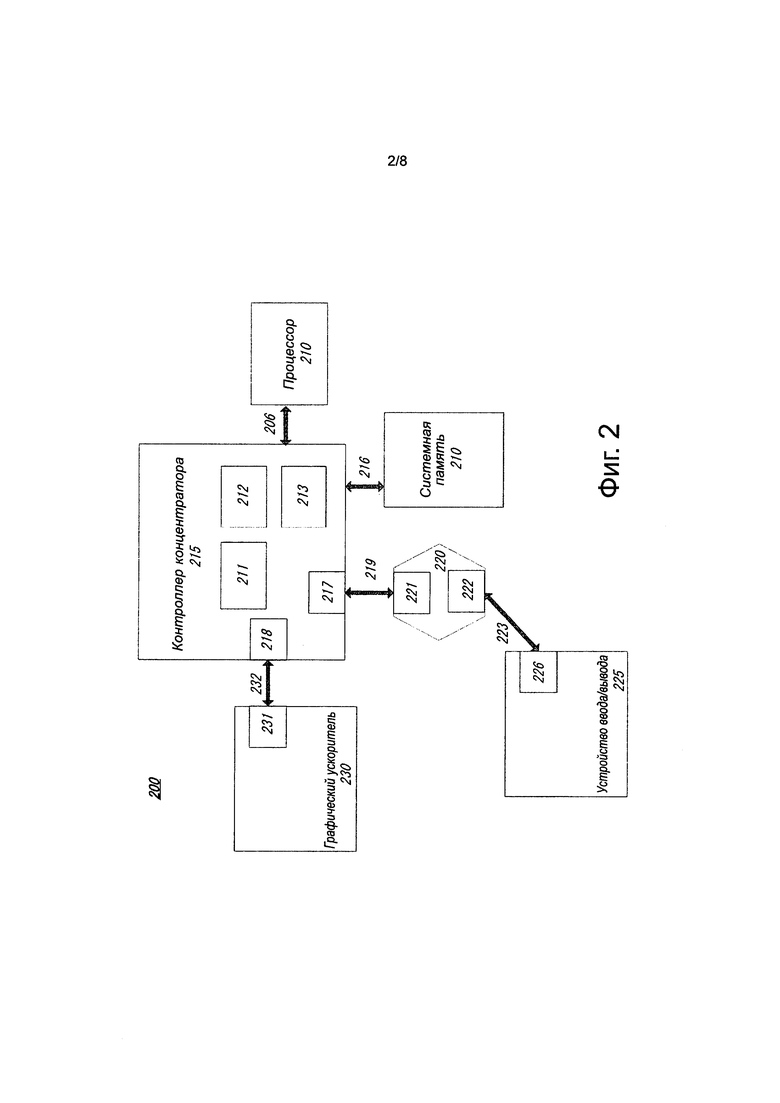

фиг. 2 иллюстрирует вариант осуществления вычислительной системы, включающей в себя архитектуру межсоединений согласно по меньшей мере одному примерному варианту осуществления;

фиг. 3 иллюстрирует вариант осуществления архитектуры межсоединений, включающей в себя многоуровневый стек согласно по меньшей мере одному примерному варианту осуществления;

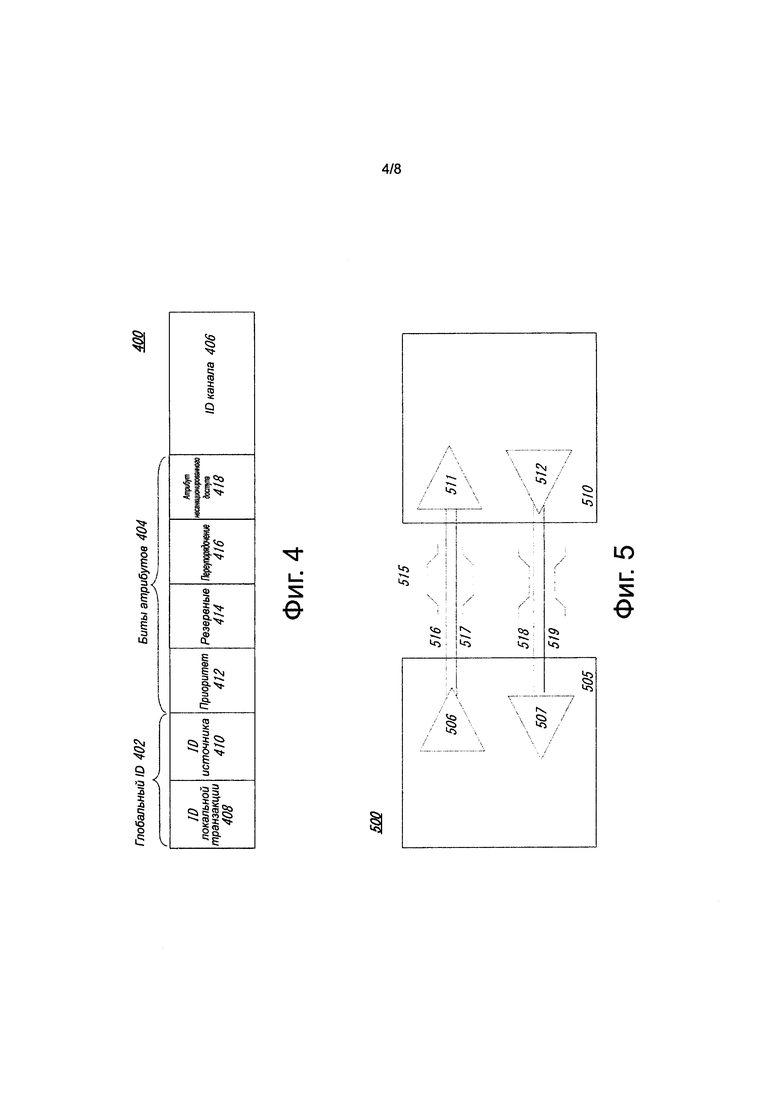

фиг. 4 иллюстрирует вариант осуществления запроса или пакета, который будет генерироваться или приниматься в рамках архитектуры межсоединений согласно по меньшей мере одному примерному варианту осуществления;

фиг. 5 иллюстрирует вариант осуществления пары передатчика и приемника для архитектуры межсоединений согласно по меньшей мере одному примерному варианту осуществления;

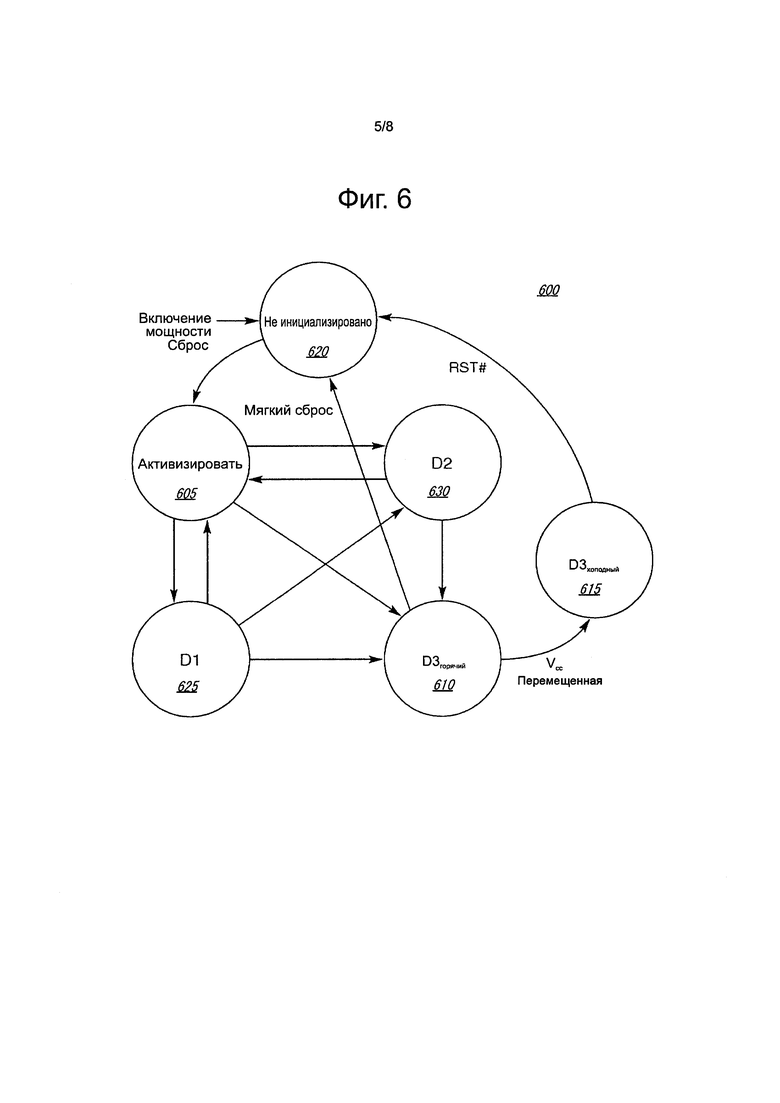

фиг. 6 иллюстрирует примерную диаграмму переходов состояний управления мощностью;

фиг. 7 - блок-схема последовательности операций согласно по меньшей мере одному варианту осуществления;

фиг. 8 - блок-схема последовательности операций согласно по меньшей мере одному варианту осуществления;

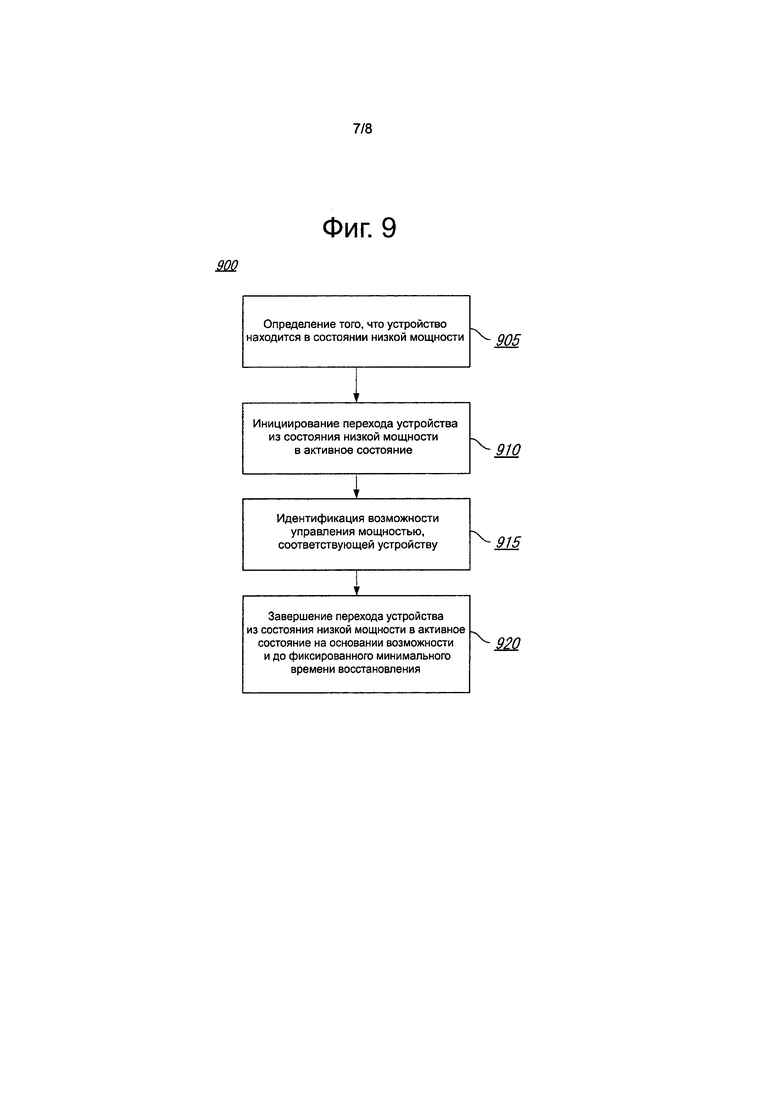

фиг. 9 - блок-схема последовательности операций согласно по меньшей мере одному примерному варианту осуществления;

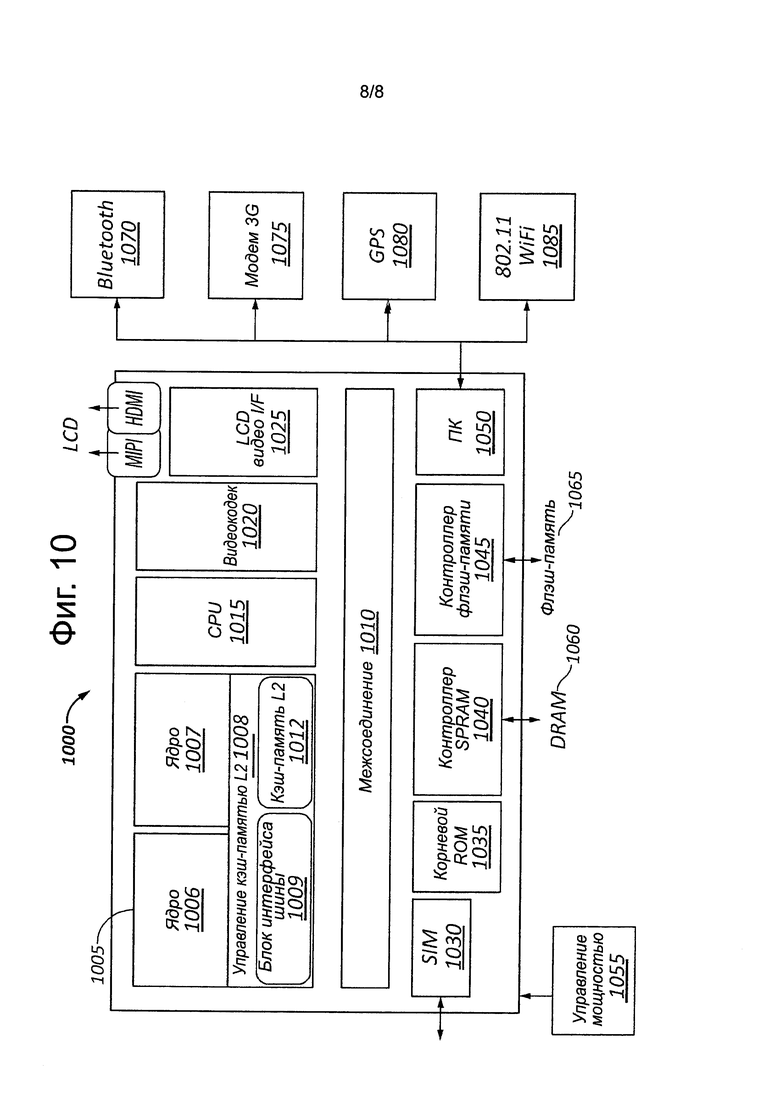

фиг. 10 иллюстрирует вариант осуществления блок-схемы для вычислительной системы.

Осуществление изобретения

В последующем описании изложены многочисленные конкретные детали, такие как примеры конкретных типов процессоров и конфигураций систем, конкретные структуры аппаратных средств, конкретные архитектурные и микроархитектурные подробности, конкретные конфигурации регистров, конкретные типы инструкций, конкретные компоненты систем, конкретные измерения/вершины, конкретные стадии и работа процессорного конвейера и т.д., чтобы обеспечить полное понимание настоящего изобретения. Однако специалистам в данной области техники будет очевидно, что эти конкретные детали не обязательно должны применяться при практическом осуществлении настоящего изобретения. В других случаях хорошо известные компоненты или способы, такие как конкретные и альтернативные процессорные архитектуры, конкретные логические схемы/код для описанных алгоритмов, конкретный код аппаратных средств, конкретная операция межсоединения, конкретные логические конфигурации, конкретные технологии изготовления и материалы, конкретные реализации компилятора, конкретное выражение алгоритмов в коде, конкретное выключение питания и вентильная технология/логика и другие конкретные подробности работы компьютерной системы подробно не описаны во избежание излишнего усложнения настоящего изобретения.

Хотя следующие варианты осуществления можно описать со ссылкой на уменьшение времени возобновления работы для корневых портов и конечных точек, составляющих единое целое с корневыми портами, таких как в вычислительных платформах или микропроцессорах, другие варианты осуществления применимы к другим типам интегральных схем и логических устройств. Аналогичные технологии и идеи вариантов осуществления, описанных здесь, можно применить к другим типам и схемам полупроводниковых устройств, которые могут также получить выигрыш от уменьшения времени возобновления работы. Например, раскрытые варианты осуществления не ограничиваются настольными компьютерными системами или Ultrabooks™. К тому же, их можно также использовать и в других устройствах, таких как портативные карманные устройства, планшетные компьютеры, другие тонкие ноутбуки, устройства "системы на микросхеме" (SOC) и встроенные приложения. Некоторые примеры портативных устройств включают в себя сотовые телефоны, устройства на основе Интернет-протокола, цифровые камеры, персональные цифровые помощники (PDA) и портативные персональные компьютеры (ПК). Встроенные приложения типично включают в себя микроконтроллер, процессор цифровой обработки сигналов (DSP), систему на микросхеме, сетевые компьютеры (NetPC), телевизионные приставки, сетевые концентраторы, коммутаторы глобальной сети (WAN) или любую другую систему, которая позволяет выполнять функции и операции, указанные ниже. Более того, устройства, способы и системы, описанные здесь, не ограничиваются физическими вычислительными устройствами, но могут также относиться к оптимизациям программного вычисления для уменьшения периодов возобновления работы.

На фиг. 1 изображена блок-схема, иллюстрирующая компоненты, связанная с уменьшением времени возобновлением работы для корневых портов и конечных точек, составляющих единое целое с корневыми портами, согласно по меньшей мере одному примерному варианту осуществления. Примеры фиг. 1 представляют собой только примеры компонентов, связанных с уменьшением времени возобновления работы для корневых портов и конечных точек, составляющих единое целое с корневыми портами, и не ограничивают объем формулы изобретения. Например, могут изменяться операции, относящиеся к компоненту, может изменяться число компонентов, может изменяться состав компонента и/или т.п. Например, в некоторых вариантах осуществления операции, относящиеся к одному компоненту примера, показанного на фиг. 1, можно выделить одному или более другим компонентам.

Процессор 100 включает в себя любой процессор или процессорное устройство, такое как микропроцессор, встроенный процессор, процессор цифровой обработки сигналов (DSP), сетевой процессор, портативный процессор, процессор приложений, сопроцессор, система на кристалле (SOC) или другое устройство для исполнения кода. Процессор 100 в одном варианте осуществления включает в себя по меньшей мере два ядра - ядро 101 и 102, которые могут включать в себя ассиметричные ядра и симметричные ядра (иллюстрированные варианты осуществления). Однако процессор 100 может включать в себя любое число процессорных элементов обработки, которые могут быть симметричными или ассиметричными.

В одном варианте осуществления процессорный элемент относится к аппаратным средствам или к логике для поддержки программного потока. Примеры аппаратных процессорных элементов включают в себя: блок потоков, слот потоков, поток, блок обработки, контекст, блок контекста, логический процессор, аппаратный поток, ядро и/или любой другой элемент, который может поддерживать состояние для процессора, такое как состояние исполнения или архитектурное состояние. Другими словами, процессорный элемент в одном варианте осуществления относится к любому аппаратному средству, которое может независимым образом ассоциироваться с кодом, таким как программный поток, операционная система, приложение или другой код. Физический процессор (или разъем для установки процессора) типично относится к интегральной схеме, которая потенциально включает в себя любое число других процессорных элементов, таких как ядра или аппаратные потоки.

Ядро часто относится к логике, расположенной на интегральной схеме, с возможностью поддержания независимого архитектурного состояния, в котором каждое архитектурное состояние, поддерживаемое независимым образом, ассоциируется по меньшей мере с некоторыми выделенными ресурсами исполнения. В отличие от ядер аппаратный поток типично относится к любой логике, расположенной на интегральной схеме, с возможностью поддержания независимого архитектурного состояния, в котором архитектурные состояния, поддерживаемые независимым образом, совместно используют доступ к ресурсам исполнения. Как можно увидеть, когда совместно используются определенные ресурсы, и другие ресурсы выделяются архитектурному состоянию, линия между номенклатурой аппаратного потока и ядром перекрывается. Тем не менее, часто ядро и аппаратный поток рассматриваются операционной системой как отдельные логические процессоры, где операционная система может отдельно планировать операции, исполняемые в каждом логическом процессоре.

Физический процессор 100, как иллюстрировано на фиг. 1, включает в себя два ядра - 101 и 102. В данном случае, ядро 101 и 102 рассматриваются как симметричные ядра, то есть ядра с одинаковыми конфигурациями, функциональными блоками и/или логикой. В другом варианте осуществления ядро 101 включает в себя процессорное ядро неупорядоченного исполнения, тогда как ядро 102 включает в себя процессорное ядро упорядоченного исполнения. Однако ядра 101 и 102 можно по отдельности выбрать из любого типа ядра, такого как родное ядро, ядро, управляемое с помощью, программного обеспечения, ядро, адаптированное к исполнению родной архитектуры набора команд (ISA), ядро, адаптированное для исполнения транслированной архитектуры набора команда (ISA), ядро комплексного проектирования или другое известное ядро. В неоднородной среде ядра (то есть ассиметричные ядра), некоторую форму трансляции, такую как двоичная трансляция, можно использовать для планирования или исполнения кода в одном или обоих ядрах. Тем не менее, в дальнейшем обсуждении функциональные блоки, иллюстрированные в виде ядра 101, описаны более подробно ниже, так как блоки в ядре 102 работают аналогичным образом в изображенном варианте осуществления.

Как изображено, ядро 101 включает в себя два аппаратных потока 101а и 101b, которые можно также называть как слоты 101а и 101b аппаратных потоков. Поэтому программные объекты, такие как операционные системы, в одном варианте осуществления, потенциально рассматривают процессор 100 как четыре отдельных процессора, четыре логических процессора или процессорные элементы с возможностью одновременного исполнения четырех программных потоков. Как упоминалось выше, первый поток ассоциируется с регистрами 101а состояния архитектуры, второй поток ассоциируется с регистрами 101b состояния архитектуры, третий поток может ассоциироваться с регистрами 102а состояния архитектуры и четвертый поток может ассоциироваться с регистрами 102b состояния архитектуры. В данном случае, каждый из регистров (101а, 101b, 102а и 102b) состояния архитектуры можно называть как процессорные элементы, потоковые слоты или потоковые блоки, как описано выше. Как это иллюстрировано, регистры 101а состояния архитектуры тиражируются в регистрах 101b состояния архитектуры, поэтому отдельные состояния, контексты архитектуры могут сохраняться для логического процессора 101а и 101b. В ядре 101 другие меньшие ресурсы, такие как указатели инструкций и логика переименования в распределителе, и блок 130 переименования и распределения можно также дублировать для потоков 101а и 101b. Некоторые ресурсы, такие как буферы переупорядочения в блоке 135 переупорядочения/извлечения, целевой буфер ветвления (ВТВ) и буфер 120 трансляции инструкций (I-TLB), буферы нагрузки/хранения и очереди можно совместно использовать посредством разбиения. Другие ресурсы, такие как внутренние регистры общего назначения, регистр(ы) базовой страницы-таблицы, данные кэш-памяти низкого уровня и данные TLB 150, блок(и) 140 исполнения и части блок 135 неупорядоченного исполнения потенциально и полностью используются совместно.

Процессор 100 часто включает в себя другие ресурсы, которые можно в полное мере совместно использовать, совместно использовать путем разбиения или выделения с помощью/в процессорных элементах. На фиг. 1 проиллюстрирован вариант осуществления только примерного процессора с иллюстративными логическими блоками/ресурсами процессора. Следует отметить, что процессор может включать в себя или не включать в себя или не включать в себя любой из этих функциональных блоков, а также включать в себя любые другие известные функциональные блоки, логику или непоказанные аппаратные средства. Как показано, ядро 101 включает в себя упрощенное, типичное процессорное ядро с неупорядоченным исполнением (101). Но процессор с упорядоченным исполнением можно использовать в различных вариантах осуществления. Ядро 101 включает в себя а ВТВ и I-TLB 120 для предсказания ветвей, которые будут исполняться/получать и ВТВ и I-TLB 120 для хранения вводов трансляции адресов для инструкций.

Ядро 101 дополнительно включает в себя модуль 125 декодирования, соединенный с ВТВ и I-TLB 120 для декодирования выбранных элементов. Логика выборки в одном варианте осуществления включает в себя отдельные секвенсеры, ассоциированные с потоковыми слотами 101а, 101b, соответственно. Обычно ядро 101 ассоциируется с первой ISA, которая определяет/специфицирует инструкции, исполняемые в процессоре 100. Часто инструкции машинного кода, которые представляют собой часть первой ISA, включают в себя часть инструкций, которые называются кодом операции, которая обращается к/специфицирует инструкцию или операцию, которая будет выполняться. Логика 125 декодирования включает в себя схему, которая распознает эти инструкции из своих кодов операций и передает декодированные инструкции по конвейеру для обработки, так как это определено первой ISA. Например, как будет более подробно описано ниже, декодеры 121 в одном варианте осуществления включают в себя логику, назначенную или адаптированную для распознавания конкретных инструкций, таких как транзакционная инструкция. В результате распознавания с помощью декодеров 125, архитектура или ядро 101 принимает конкретные, предварительно определенные действия для выполнения задач, связанных с соответствующей инструкцией. Важно отметить, что любую из задач, блоков, операций и способов, описанных здесь, можно выполнить в ответ на одну или нескольких инструкций, некоторые из которых могут быть новыми или старыми инструкциями. Следует отметить, что декодеры 125 в одном варианте осуществления распознают ту же самую ISA (или ее поднабор). Альтернативно, в неоднородной среде ядра декодеры 125 распознают вторую ISA (либо поднабор первой ISA или особый ISA).

В одном примере блок 130 переименования и распределения включает в себя распределитель для резервирования ресурсов, таких как регистровые файлы для хранения результатов обработки инструкций. Однако потоки 101а и 101b имеют возможность неупорядоченного исполнения, где блок 130 переименования и распределения также резервирует другие ресурсы, такие как буферы переупорядочения, чтобы отследить результаты инструкций. Блок 130 переименования и распределения может также включать в себя средство переименования регистров для переименования регистров со ссылкой на программы/инструкции для других регистров, внутренних к процессору 100. Блок 135 переупорядочения/извлечения включает в себя компоненты, такие как буферы переупорядочения, упомянутые выше, буферы загрузки и буферы хранения для поддержания неупорядоченного исполнения и впоследствии упорядоченного извлечения инструкций, исполняемых вне очереди.

Блок 140 модуля(ей) планирования и исполнения в одном варианте осуществления включает в себя модуль планировщика для планирования инструкций/операции по отношению к исполнительным блокам. Например, инструкция операции с плавающей точкой планируется в порту блока исполнения, который имеет доступный блок исполнения операций с плавающей точкой. Файлы регистров, ассоциированные с блоками исполнения, также включены для хранения информационных результатов обработки инструкций. Примерные блоки исполнения включают в себя блок исполнения операций с плавающей точкой, блок исполнения целочисленных операций, блок исполнения переходов, блок исполнения загрузки, блок исполнения сохранения и другие известные блоки.

Кэш данных нижнего уровня и буфер 150 трансляции данных (D-TLB) соединены с блоком(ами) 140 исполнения. Кэш данных предназначен для хранения недавно используемых, выполняемых операций над элементами, такими как операнды данных, которые потенциально удерживаются в состояниях когерентности памяти. D-TLB предназначен для хранения последних, виртуальных/линейных и физических адресных трансляций. В качестве конкретного примера, процессор может включать в себя структуру таблицы страниц для разбиения физической памяти на множество виртуальных страниц.

В данном случае, ядра 101 и 102 совместно используют доступ к кэш более высокого уровня или еще выше, такому как кэш второго уровня, ассоциированный с интерфейсом 810, расположенным на кристалле. Следует отметить, что более высокий уровень или еще выше относится к уровням кэш, которые увеличиваются или становятся дальше от блока(ов) исполнения. В одном варианте осуществления кэш более высокого уровня представляет собой кэш данных самого последнего уровня (последний кэш в иерархии памяти в процессоре 100), таком как кэш данных второго или третьего уровня. Однако кэш более высокого уровня не является ограниченным, так как он может ассоциироваться с или включать в себя кэш инструкций. Трассовый кэш (тип кэша инструкций) вместо этого может быть связан после декодера 125 для хранения недавно декодированных трасс. В данном случае, инструкция потенциально относится к макроинструкции (то есть к общей инструкции, распознанной декодерами), которая может быть закодирована в ряде микроинструкций (микроопераций).

В изображенной конфигурации процессор также включает в себя накристальный модуль 110 интерфейса. Исторически контроллер памяти, который будет более подробно описан ниже, был включен в вычислительную систему (внешнюю) к процессору 100. В этом сценарии накристальный модуль 110 интерфейса должен поддерживать связь с устройствами, внешними к процессору 100, такими как системная память 175, микропроцессорный набор (часто включающий в себя концентратор контроллера памяти для подсоединения к памяти 175 и концентратор контроллера ввода/вывода для подсоединения периферийных устройств), концентратор контроллера памяти, северный мост или другую интегральную схему. И в этом сценарии шина 105 может включать в себя любое известное межсоединение, такое как многоточечная шина, двухточечное межсоединение, последовательное межсоединение, параллельная шина, когерентная (например, когерентная кэш-память) шина, архитектура многоуровневого протокола, дифференциальная шина и шина приемопередатчиков (GTL).

Память 175 можно выделить процессору 100 или совместно использовать с другими устройствами в системе. Общие примеры типов памяти 175 включают в себя DRAM, SRAM, энергонезависимую память (NV память) и другие известные запоминающие устройства. Следует отметить, что устройство 180 может включать в себя графический процессор и плату, подсоединенную к концентратору контроллера памяти, запоминающее устройство для данных, подсоединенное к концентратору контроллера ввода/вывода, беспроводный приемопередатчик, устройство флэш-памяти, аудиоконтроллер, сетевой контроллер, или другое известное устройство.

Однако в последнее время, так как большое количество логических схем и устройств выполняется как единое целое на одном кристалле, таком как система на кристалле (SOC), каждое из этих устройств можно встроить в процессор 100. Например, в одном варианте осуществления концентратор контроллера памяти находится в одном и том же корпусе и кристалле с процессором 100. В данном случае, часть ядра (часть на ядре) 110 включает в себя один или более контроллеров для сопряжения с другими устройствами, такими как память 175 или устройство 180. Конфигурация, включающая в себя межсоединение и контроллеры для сопряжения с такими устройствами часто называется как наядерной (или неядерной конфигурацией). В качестве примера накристальный интерфейс 110 включает в себя кольцевое межсоединение для накристальной связи и высокоскоростную последовательную двухточечную линии 105 связи для внекристальной связи. Кроме того, в среде SOC даже большее количество устройств, таких как сетевой интерфейс, сопроцессоры, память 175, устройство 180 и любые другие известные компьютерные устройства/интерфейсы можно выполнить как единое целое на одном кристалле или интегральной схемы для обеспечения маленького форм-фактора с высокими функциональными возможностями и низкой потребляемой мощностью.

В одном варианте осуществления процессор 100 выполнен с возможностью исполнения компилятора оптимизации и/или кода 177 транслятора для компиляции, трансляции и/или оптимизации кода 176 приложения для поддержки устройства и способов, описанных в данном документе или для сопряжения с ними. Компилятор часто включает в себя программу или набор программ для трансляции исходного текста/кода в целевой текст/код. Обычно компиляция кода программы/приложения с помощью компилятора выполняется в несколько фаз и передается для преобразования кода языка программирования высокого уровня в машинный код низкого уровня или код на языке Ассемблера. Кроме того, однопроходные компиляторы можно по-прежнему использовать для простой компиляции. Компилятор может использовать любые известные технологии компиляции и выполнять любые известные операции компилятора, такие как лексический анализ, предобработка, синтаксический анализ, семантический анализ, генерацию кода, преобразование кода и оптимизацию кода.

Более крупные компиляторы часто включают в себя несколько фаз, но чаще всего эти фазы включены в две общие фазы: (1) препроцессор, то есть обычно там, где может иметь место синтаксическая обработка, семантическая обработка и некоторые преобразования/оптимизация, и (2) постпроцессор, то есть обычно там, где имеет место анализ, преобразования, оптимизации и генерация кода. Некоторые компиляторы оказываются посередине, что иллюстрирует размывание разграничение между препроцессором и постпроцессором компилятора. В результате, ссылка на вставку, ассоциацию, генерацию и другую операцию компилятора может иметь место в любой из вышеупомянутых фаз или проходов, а также в любых других известных фазах или проходах компилятора. В качестве иллюстративного примера, компилятор потенциально вставляет операции, вызовы, функции и т.д. в одну или более фаз компиляции, такие как вставка вызовов/операций на фазе предварительной обработки компиляции и затем преобразования вызовов/операций в код более низкого уровня во время фазы преобразования. Следует отметить, что во время динамической компиляции, код компилятора или код динамической оптимизации позволяет вставлять такие операции/вызовы, а также оптимизировать код для исполнения во время прогона. В качестве конкретного иллюстративного примера, двоичный код (уже компилированный код) можно динамическим образом оптимизировать во время прогона. В данном случае, программный код может включать в себя код динамической оптимизации, двоичный код или их комбинацию.

Аналогично компилятору, транслятор, такой как двоичный транслятор, транслирует код либо статическим, либо динамическим образом для оптимизации и/или трансляции кода. После этого ссылка на исполнение кода, кода приложения, кода программы или другой программной среды может относиться к: (1) исполнение программ(ы) компилятора, оптимизатора кода оптимизации или транслятора динамическим или статистическим образом для компиляции программного кода, для поддержания программных структур, для выполнения других операций, для оптимизации кода или для трансляции кода; (2) исполнение главного программного кода, включающего в себя операции/вызовы, такие как код прикладной программы, который был оптимизирован/компилирован; (3) исполнение другого программного кода, такого как библиотеки, ассоциированные с главным программным кодом для поддержания программных структур, для выполнения других операций, которые относятся к программному обеспечению или для оптимизации кода; или (4) их комбинации.

В некоторых реализациях контроллер 160 управления мощностью можно также выполнить и реализовать в виде аппаратных средств и программного обеспечения. Система и устройства, подсоединенные к системе, могут поддерживать многочисленные состояния мощности, включая полную мощность, низкую мощность и состояние без мощности, среди прочих (например, промежуточных) состояний или условий. Контроллер 160 управления мощностью может выполнять функции и выполнять задачи для оказания содействия при минимизации потребления мощности системой, тепловых ограничений системы управления и максимизации срока службы аккумулятора системы среди прочих функциональных возможностей. Управление мощностью может включать в себя управление другими функциональными возможностями и характеристиками системы, в том числе быстродействием системы, шумом, сроком службы аккумулятора и потреблением мощности переменного тока среди прочих примеров.

Накристальный интерфейс может включать в себя модуль 104 времени возобновления. Модуль 104 времени возобновления может включать в себя процессор 182 и память 184. Накристальный интерфейс 110 и устройство 180 могут поддерживать связь через высокоскоростную шину последовательного ввода-вывода (PCIe) совместимое или другое соединение. В некоторых протоколах межсоединений, таких как межсоединения периферийных компонентов (PCI) и (PCIe), можно предусмотреть архитектурные механизмы для задержки входов устройств в состояние полной мощности (например, в связи с определенными политиками и возможностями управления мощностью). Например, программное обеспечение, такое как логика управления мощностью операционной системы устройства позволяет по меньшей мере частично, управлять входами и выходами в различных состояниях мощности. В некоторых примерах, политики платформ могут обеспечить минимальные периоды восстановления (задержки), прежде разрешить программному обеспечению выдавать запросы на конфигурацию в устройства, например, в связи с инициированием состояния мощности. Например, чтобы улучшить использование мощности в режиме ожидания, политики функциональной возможности управления мощностью могут попытаться разместить устройство, включающее в себя дискретные присоединенные устройства, корневые порты (RP) и корневые комплексные интегральные конечные точки (RCIE) и т.д., а также внешние устройства, соединенные поверх межсоединения, в состояниях с управлением мощностью, где мощность в этих устройствах можно выключить, устройства могут работать в состоянии с пониженной мощностью, или эти устройства могут работать в условиях резервной мощности. После возобновления работы из этих состояний мощности, программное обеспечение ожидает в течение конкретного периода времени (например, 10 мс, 100 мс и т.д.), прежде чем оно будет выдавать запросы на конфигурацию. Это может иметь значительное влияние на время возобновления. Такие определенные минимальные периоды времени восстановления, несмотря на то, что они являются преимущественными в некоторых контекстах и в связи с некоторыми устройствами, тем не менее, могут быть нежелательными в других контекстах и в связи с другими устройствами.

В некоторых реализациях накристальный интерфейс может включать в себя модуль 104 времени возобновления. Модуль 104 времени возобновления может включать в себя процессор 182 и память 184. Модуль 104 времени возобновления можно сконфигурировать таким образом, чтобы разрешить внутреннему устройству, такому как корневой порт, назначенный порт (DP) или RCIE информировать о времени восстановления, специфическом для устройства, показывая то, как скоро после перехода в состояние мощности (например, первоначальная подача мощности, переход из D3 в D0 и т.д.) устройство будет готово для первой конфигурации (например, в связи с программным обеспечением). В варианте осуществления модуль 104 времени возобновления может дополнительно включать в себя механизм прерывания (например, описание производительности, механизм управления для разрешения прерываний) для внутренних устройств, чтобы запускать прерывание в том случае, когда оно завершается или готово для завершения перехода между состояниями мощности (например, первоначальная подача мощности, переход D3-D0 и т.д.), чтобы дополнительно усилить окончание в предварительно установленном периоде времени восстановления или в противном случае инициировать задачи конфигурации, которые будут выполняться программным обеспечением.

В некоторых реализациях возможности периода времени возобновления, конкретного для устройства, можно определить в одном или более регистров возможностей, и они могут быть доступны одному или более инструментам управления мощностью, в том числе инструментам на основе программного обеспечения. В одном примере во время подсчета устройств (например, одного или более устройств 180, в том числе внешних или внутренних устройств) модуль 104 времени возобновления может осуществлять доступ к возможностям времени возобновления устройства и может сохранять их в памяти 184 для дальнейшего использования. Модуль 104 времени возобновления может также считывать возможности прерывания устройства и реализовывать механизм прерывания вместо механизма опроса с возможностью запуска и распознавания прерывания в том случае, когда внутреннее устройство готово для доступа к конфигурации. Например, в некоторой точке внутреннее устройство может переходить в состояние низкой мощности. В варианте осуществления модуль 104 времени возобновления может определить, что внутреннее устройство должно переходить из состояния низкой мощности в состояние полной мощности. Кроме того, модуль 104 времени возобновления может извлекать объявленное значение времени возобновления для устройства 180 из памяти 184 и затем выдавать первый запрос на конфигурацию после ожидания периода времени в памяти 184, который был объявлен внутренним устройством в соответствующей структуре возможностей среди прочих примеров.

В другом варианте осуществления модуль 104 времени возобновления может определить, что он собирается применить мощность к подсистеме, которая управляла устройством 180. Если устройство 180 выполнено с возможностью передачи прерывания в случае, когда устройство 180 вышло из состояния с низкой мощностью, модуль 104 времени возобновления может ожидать прерывания, которое будет получено из устройства 180, показывать, что оно готово для первого доступа к конфигурации. В обоих случаях модуль времени возобновления может удалить фиксированное архитектурное время ожидания 100 мс перед осуществлением доступа к устройству с помощью первого доступа к конфигурации. Модуль 104 времени возобновления может также удалить фиксированное архитектурное время ожидания для программного обеспечения перед доступом к устройству с помощью первого доступа к конфигурации после записи в регистре статуса и управления мощностью (PMCSR). Чтобы поддержать совместимость с предыдущими версиями, архитектурные периоды времени восстановления (например, унаследованную задержку 100 мс или 10 мс (для доступа после записи (PMCSR)) не следует увеличивать с помощью модуля 104 времени возобновления и можно поддержать в качестве режима по умолчанию для устройств, которые не используют обычные возможности времени возобновления. Как изложено выше, накристальный интерфейс 110 и устройство 180 могут поддерживать связь через соединение по линии связи, такое как PCIe, MIPI, QPI или другие линии межсоединений, совместимые с протоколом.

Основная цель PCIe состоит в том, чтобы обеспечить возможность компонентам и устройствам от разных производителей совместно функционировать в открытой архитектуре, охватывающей многочисленные сегменты рынка; клиенты (настольные компьютерные и мобильные устройства), серверы (стандартные и промышленные), и встроенные и коммуникационные устройства. PCIe имеет высокую производительность межсоединения ввода/вывода общего назначения, определенное для большого разнообразия будущих вычислительных и коммуникационных платформ. Некоторые атрибуты PCI, такие как ее модель применения, архитектура нагрузки-хранения и программные интерфейсы, поддерживались через их поправки, тогда как предыдущие реализации параллельной шины были заменены на высоко масштабируемый, полностью последовательный интерфейс. Более поздние версии PCIe являются преимущественными благодаря достижениям в двухточечных межсоединениях, технологии на основе переключения и пакетированию протокола для доставки новых уровней производительности и особенностей. Управление мощностью, качество обслуживания (QoS), поддержка активного соединения/замена непосредственно в процессе работы, целостность данных и устранение ошибок представляют собой одни из расширенных функциональных возможностей, поддерживаемых PCIe.

Со ссылкой на фиг. 2 иллюстрирован вариант осуществления структур, состоящих из двухточечных линий связи, которые обеспечивают межсоединение набора компонентов. Система 200 включает в себя процессор 205 и системную память 210, подсоединенную к концентратору 215 контроллера. Процессор 205 включает в себя любой процессорный элемент, такой как микропроцессор, хост-процессор, встроенный процессор, сопроцессор или другой процессор. Процессор 205 соединен с концентратором 215 контроллера через управляющую шину (FSB) 206. В одном варианте осуществления, FSB 206 представляет собой последовательное двухточечное межсоединение, как описано ниже. В другом варианте осуществления линия 206 связи включает в себя последовательную дифференциальную архитектуру межсоединений, которая совместима с различными стандартами межсоединений.

Системная память 210 включает в себя устройство памяти, такое как оперативное запоминающее устройство (RAM), энергонезависимую (NV) память или другую память, доступ к которым осуществляется с помощью устройств в системе 200. Системная память 210 соединена с концентратором 215 контроллера через интерфейс 216 памяти. Примеры интерфейса памяти включают в себя интерфейс памяти с удвоенной скоростью передачи данных (DDR), интерфейс памяти с двухканальной DDR и интерфейс памяти с динамическим RAM (DRAM).

В одном варианте осуществления концентратор 215 контроллера представляет собой корневой концентратор, корневой комплекс или корневой контроллер в иерархии межсоединений PCIe. Примеры концентратора 215 контроллера включают в себя микропроцессорный набор, концентратор контроллера памяти (MCH), северный мост, концентратор контроллера межсоединений (ICH), южный мост и корневой контроллер/концентратор. Часто термин "микропроцессорный" набор относится к двум физически отдельным концентраторам контроллера, то есть к концентратору контроллера памяти (MCH), соединенному с концентратором контроллера межсоединений (ICH). Следует отметить, что данные системы часто включают в себя MCH, выполненные как единое целое с процессором 205, тогда как контроллер 215 должен поддерживать связь с устройствами ввода/вывода аналогичным образом, как описано ниже. В некоторых вариантах осуществления одноранговая маршрутизация дополнительно поддерживается через корневой комплекс 215.

В данном случае, концентратор 215 контроллера соединен с коммутатором/мостом 220 через последовательную линию 219 связи. Модули 217 и 221 ввода/вывода, которые можно также назвать как интерфейсы/порты 217 и 221, включают в себя, реализуют стек многоуровневых протоколов для обеспечения связи между концентратором 215 контроллера и коммутатором 220. В одном варианте осуществления многочисленные устройства выполнены с возможностью подсоединения к коммутатору 220.

Коммутатор/мост 220 обеспечивает маршрутизацию пакетов/сообщений из устройства 225 выше по потоку, то есть выше иерархии по направлению к корневому комплексу, в концентратор 215 контроллера, и ниже по потоку, то есть ниже иерархии от корневого контроллера, из процессора 205 или системной памяти 210 в устройство 225. Коммутатор 220 в одном варианте осуществления называется логическим узлом многочисленных виртуальных устройств с мостом типа PCI-PCI. Устройство 225 включает в себя любое внутреннее или внешнее устройство или компонент, который будет подсоединяться к электронной системе, такой как устройство ввода/вывода, контроллер сетевого интерфейса (NIC), плата для расширения, аудиопроцессор, сетевой процессор, накопитель на жестких дисках, запоминающее устройство, ПЗУ на основе CD/DVD, монитор, принтер, мышь, клавиатура, портативное запоминающее устройство, устройство шины Firewire, устройство универсальной последовательной шины (USB), сканер и другие устройства ввода/вывода. Часто такое устройство на профессиональном жаргоне PCIe называется конечной точкой. Хотя это специально не показано, устройство 225 может включать в себя мост PCIe - PCI/PCI-X для поддержки унаследованных устройств или устройств PCI других версий. Устройства конечной точки в PCIe часто классифицируются как унаследованные, PCIe или конечные точки, выполненные как одно целое с корневым комплексом.

Графический ускоритель 230 также соединен с концентратором 215 контроллера через последовательную линию 232 связи. В одном варианте осуществления графический ускоритель 230 соединен с MCH, который соединен с ICH. Коммутатор 220 и, соответственно, устройство 225 ввода/вывода соединено далее с ICH. Модули 231 и 218 ввода/вывода должны также реализовывать стек многоуровневых протоколов для поддержания связи между графическим ускорителем 230 и концентратором 215 контроллера. Аналогично MCH, обсужденным выше, графический контроллер или непосредственно графический ускоритель можно выполнить как единое целое в процессоре 205. Кроме того, в некоторых реализациях одно или более внутренних устройств, например, 211, 212, 213 можно выполнить, например, на микропроцессорном наборе, концентраторе контроллера, корневом комплексе и т.д. Например, можно выполнить конечные точки, выполненные как единое целое с корневым комплексом (RCIE), порт, расположенный ниже по ходу, или корневой порт (например, 217), внутреннее устройство PCI и другие внутренние устройства. Функциональные возможности, описанные в данном документе можно применять к внутренним устройствам, а также к внешним устройствам.

Со ссылкой на фиг. 3 иллюстрирован вариант осуществления многоуровневого стека протокола. Многоуровневый стек 300 протокола включает в себя любую форму многоуровневого стека связи, такого как стек межсоединений Quick Path Interconnect (QPI), стек PCIe, стек межсоединений для высокопроизводительных вычислений следующего поколения или другой многоуровневый стек. Хотя обсуждение, приведенное ниже со ссылкой на фиг. 2-5, приведено в отношении стека PCIe, те же самые концепции можно применить к другим стекам межсоединений. В одном варианте осуществления стек 300 протокола представляет собой стек протокола PCIe, включающий в себя уровень 305 транзакций, уровень 310 линий связи и физический уровень 320. Интерфейс, такой как интерфейсы 217, 218, 221, 222, 226 и 231, показанные на фиг. 2, можно представить в виде стека 300 протокола связи. Представление в виде стека протокола связи можно также назвать как модуль или интерфейс, реализующий/включающий в себя стек протокола.

PCIe использует пакеты для обеспечения обмена информацией между компонентами. Пакеты формируются на уровне 305 транзакций и канальном уровне 310 для переноса информации из компонента передачи в компонент приема. Так как переданные пакеты передаются через другие уровни, они увеличиваются за счет дополнительной информации, необходимой для обработки пакетов на этих уровнях. На приемной стороне имеет место обратный процесс, и пакеты преобразуются из своего представления физического уровня 320 в представление канального уровня 310 и окончательно (для пакетов уровня транзакций) в форму, которую можно обработать с помощью уровня 305 транзакций приемного устройства.

Уровень транзакций

В одном варианте осуществления уровень 305 транзакций должен обеспечить сопряжение между ядром обработки устройства и архитектурой межсоединений, таких как канальный уровень 310 и физический уровень 320. В связи с этим главной обязанностью уровня 305 транзакций является ассемблирование и дизассемблирование пакетов (то есть пакетов уровня транзакций или TLP). Уровень 305 трансляции обычно осуществляет управление передачей на основе кредита для TLP. PCIe реализует разделенные транзакции, то есть транзакции с запросом и ответом разделенным во времени, что позволяет линии связи переносить другой трафик, тогда как целевое устройство производит сбор данных для ответа.

Кроме этого, PCIe использует управление передачей на основе кредита. В этой схеме устройство извещает о начальной сумме кредита для каждого приемного буфера на уровне 305 транзакций. Внешнее устройство на противоположном конце линии связи, такое концентратор 115 контроллера на фиг. 2, подсчитывает количество кредитов, потребляемых каждой TLP. Транзакция может передаваться в случае, если транзакция не превышает кредита лимита. После получения ответа восстанавливается сумма кредита. Преимущество схемы кредита состоит в том, что время ожидания возврата кредита не влияет на производительность при условии, что не возникают трудности с лимитом кредита.

В одном варианте осуществления четыре адресных пространства транзакций включают в себя адресное пространство конфигураций, адресное пространство памяти, адресное пространство ввода/вывода и адресное пространство сообщений. Транзакции пространства памяти включают в себя один или более из запросов считывания и запросов записи для передачи данных в/из местоположения с отображением памяти. В одном варианте осуществления транзакции пространства памяти позволяют использовать два различных форматов адресов, например, например, короткий формат адреса, такой как 32-битовый адрес, или длинный формат адреса, такой как 64-битовый адрес. Транзакции пространства конфигураций используются для обеспечения доступа пространства конфигураций устройств PCIe. Транзакции в пространстве конфигураций включают в себя запросы считывания и запросы записи. Транзакции пространства сообщений (или просто сообщений) определяются для поддержки внутриполосной связи между агентами PCIe. Поэтому в одном варианте осуществления уровень 305 транзакций ассемблирует заголовок/полезную нагрузку 306 пакета. Формат для текущих заголовок, полезных нагрузок пакетов можно найти в спецификации PCIe на веб-сайте спецификации PCIe.

Вкратце, на фиг. 4 иллюстрирован вариант осуществления дескриптора транзакций PCIe. В одном варианте осуществления дескриптор 400 транзакций представляет собой механизм для переноса информации о транзакциях. В связи с этим дескриптор 400 транзакций поддерживает идентификацию транзакций в схеме. Другие возможные применения включают в себя модификации отслеживания упорядочения транзакций по умолчанию и ассоциации транзакции с каналами.

Дескриптор 400 транзакций включает в себя поле 402 глобального идентификатора, поле 404 атрибутов и поле 406 идентификатора канала. В иллюстрированном примере поле 402 глобального идентификатора изображено как включающее в себя поле 408 идентификатора локальной транзакции и поле 410 идентификатора источника. В одном варианте осуществления идентификатор 402 глобальной транзакции является уникальным для всех ожидающих выполнения запросов.

Согласно одной реализации поле 408 идентификатора локальной транзакции представляет собой поле, выработанное с помощью агента запроса, и оно является уникальным для всех запросов, ожидающих выполнения, которые требуют завершения для этого агента, выполняющего запрос. Кроме того, в этом примере идентификатор 410 источника уникальным образом идентифицирует агент инициатора запроса в пределах иерархии PCIe. Соответственно, вместе с источником ID 410 поле 408 идентификатора локальной транзакции обеспечивает глобальную идентификацию транзакции в пределах домена иерархии.

Поле 404 атрибутов точно определяет характеристики и взаимосвязи транзакции. В связи с этим поле 404 атрибутов потенциально используется для предоставления дополнительной информации, которая позволяет осуществить модификацию обработки по умолчанию транзакций. В одном варианте осуществления поле 404 атрибутов включает в себя поле 412 приоритета, резервное поле 414, поле 416 упорядочения и поле 408 санкционированного доступа. В данном случае подполе 412 приоритета можно модифицировать с помощью инициатора для присвоения приоритета транзакции. Резервное поле 414 атрибута остается зарезервированным для будущего использования или использования, определяемого продавцом. Возможные модели применения, использующие приоритет или атрибуты безопасности, можно реализовать с использованием резервного поля атрибута.

В этом примере поле 416 атрибута упорядочения используется для предоставления дополнительной информации, передающий тип упорядочения, который позволяет модифицировать правила упорядочения по умолчанию. Согласно одной примерной реализации атрибут упорядочения "0" обозначает правила упорядочения по умолчанию, которые следует применять, при этом атрибут упорядочения "1" обозначает релаксированное упорядочение, в котором записи могут передавать записи в том же самом направлении, и завершения считываний могут передавать записи в том же самом направлении. Поле 418 атрибута несанкционированного доступа используется для определения того, осуществляется ли несанкционированный доступ к транзакции. Как показано поле 406 ID канала идентифицирует канал, с которым ассоциируется транзакция.

Канальный уровень

Уровень 310 нисходящей линии связи, который также называется канальным уровнем 310, действует как промежуточная стадия между уровнем 305 транзакции и физическим уровнем 320. В одном варианте осуществления обязанность канального уровня 310 заключается в обеспечении надежного механизма обмена пакетами на уровне транзакций (TLP) между двумя компонентами линии связи. Одна сторона канального уровня 310 принимает TLP, ассемблированные с помощью уровня 35 транзакций, применяет идентификатор 311 последовательностей пакетов, то есть идентификационный номер или номер пакета, вычисляет и применяет код с обнаружением ошибок, то есть CRC 312, и передает модифицированный TLP на физический уровень 320 для передачи по физическому каналу во внешнее устройство.

Физический уровень

В одном варианте осуществления физический уровень 320 включает в себя логический подблок 321 и электрический подблок 322 для физической передачи пакета во внешнее устройство. В данном случае, логический подблок 321 отвечает за "цифровые" функции физического уровня 321. В связи с этим, логический подблок включает в себя передающую часть для подготовки исходящей информации для передачи с помощью физического подблока 322, и приемную часть для идентификации и подготовки принятой информации перед передачей ее на канальный уровень 310.

Физический блок 322 включает в себя передатчик и приемник. Передатчик снабжается логическим подблоком 321 символами, которые передатчик преобразует в последовательную форму и передает во внешнее устройство. Приемник снабжается преобразованными в последовательную форму символами из внешнего устройства и преобразует принятые сигналы в битовый поток. Битовый поток преобразуется в форму, обратную последовательной, и подается в логический подблок 321. В одном варианте осуществления применяется код передачи 8b/10b, где передаются/принимаются 10-битовые символы. В данном случае для кадрирования пакета кадрами 323 используются специальные символы. Кроме этого, в одном примере приемник также обеспечивает подачу тактового символа, восстановленного из входящего последовательного потока.

Как изложено выше, хотя уровень 305 транзакций, канальный уровень 310 и физический уровень 320 обсуждены со ссылкой на конкретный вариант осуществления стека на основе протокола PCIe, таким образом, стек многоуровневых протоколов не является ограниченным. Фактически, можно включить/реализовать любой многоуровневый протокол. В качестве примера, порт/интерфейс, который представлен в виде многоуровневого протокола, включает в себя: (1) первый уровень для ассемблирования пакетов, то есть уровень транзакций; второй уровень для последовательных пакетов, то есть канальный уровень; и третий уровень для передачи пакетов, то есть физический уровень. В качестве конкретного примера, используются многоуровневый протокол общего стандартного интерфейса (CSI).

Далее со ссылкой на фиг. 5 иллюстрирован вариант осуществления последовательной двухточечной связной архитектуры PCIe. Хотя иллюстрирован вариант осуществления последовательной двухточечной линии связи PCIe, последовательная двухточечная линия связи таким образом не ограничивается, так как она включает в себя любой канал передачи для передачи последовательных данных. В показанном варианте осуществления основная линия связи PCIe включает в себя две с низким напряжением, дифференциально возбуждаемые сигнальные пары: передающая пара 506/511 и приемная пара 512/507. Соответственно, устройство 505 включает в себя передающую логическую схему 506 для передачи данных в устройство 510 и приемную логическую схему 507 для приема данных из устройства 510. Другими словами, два канала передачи, то есть канала 516 и 517, и два приемных канала, то есть канала 518 и 519, включены в линию связи PCIe.

Канал передачи относится к любому каналу для передачи данных, такому как линия передачи, медная линия, оптическая линия, беспроводный канал связи, инфракрасная линия связи и другие каналы связи. Соединение между двумя устройствами, такими как устройство 505 и устройство 510, называется линией связи, такая как линия связи 415 связи. Линия связи может поддерживать один тракт, причем каждый тракт представляет собой набор различных сигнальных трактов (одна пара для передачи, одна пара для приема). Чтобы масштабировать полосу пропускания, линия связи может объединять многочисленные тракты, обозначенные как xN, где N - любая поддерживаемая ширина полосы пропускания линии связи, такая как 1, 2, 4, 8, 12, 16, 32, 64 или шире.

Дифференциальная пара относится к двум каналам передачи, таким как линии 416 и 417, для передачи дифференциальных сигналов. В качестве примера, когда линия 416 переключается с уровня низкого напряжения на уровень высокого напряжения, то есть передний фронт, линия 417 переходит с уровня высокого напряжения на уровень низкого напряжения, то есть задний фронт. Дифференциальные сигналы потенциально демонстрируют более высокие электрические характеристики, такие как более высокую целостность сигнала, то есть взаимную связь, выброс/провал по напряжению, "звон" и т.д. Это создает возможность для лучшей временной синхронизации окна, которая обеспечивает более высокие частоты передачи.

Как отмечено выше, различные платформы, как PCIe, могут поддерживать многочисленные состояния управления мощностью. На фиг. 6 показана примерная диаграмма 600 переходов состояний, иллюстрирующая примерное состояние управления мощностью (например, 605, 610, 615, 620, 625, 630) и переходы между состояниями. В примере, показанном на фиг. 6, поддерживаются четыре главных состояния мощности. Например, состояние D0 (например, 605, 620) может представлять собой состояние максимальной мощности или активное состояние, и состояние в одном экстремуме, и состояние D3 (например, 610, 615) обеспечивает состояние "Выкл." мощности. Состояния D1 (например, 625) и D2 (например, 630) могут обеспечивать промежуточное состояние мощности, представляющее собой, например, состояние в режиме ожидания или в режиме пониженного энергопотребления устройства. В одном примере возбужденное состояние D3 (например, 610) можно обеспечить в случае, где Vcc по-прежнему прикладывается к устройству, чтобы отличить от невозбужденного состояния D3 (например, 615), где Vcc понижено до полного отключения мощности устройства.

Как представлено на фиг. 6, переходы можно определить между различными состояниями (например, 605, 610, 615, 620, 625, 630). Например, в одной реализации устройства в возбужденном состоянии D3 можно возвратить в D0 путем первоначального ввода устройства, после включения питания, в неинициированное состояние 620 D0, например, путем записи состояния команды состояния D0 в соответствующем регистре состояния управления мощностью. В другом примере, в невозбужденном состоянии D3 устройства функционирование может вернуться обратно в D0 из невозбужденного состояния D3 (только переход в незапрещенное состояние из невозбужденного состояния D3). В некоторых примерах, программное обеспечение можно использовать в связи с переходом в состояние управления мощности, например, для выполнения полного или частичного повторного инициирования функции, включающей в себя свое соответствующее пространство конфигураций. Кроме того, как установлено выше, требование к минимальному времени можно определить в некоторых случаях (например, усиленных системным программным обеспечением) между тем, когда функционирование запрограммировано с D3 до D0, и тем, когда функционирование доступно (включая доступы к конфигурациям). Это позволяет обеспечить время для функционирования, чтобы сбросить себя и ввести себя в состояние включения питания. Однако как отмечено выше, такие минимальные периоды времени восстановления по умолчанию может внести нежелательные задержки в значение времени возобновления для конкретных устройств. Соответственно, в некоторых реализациях можно обеспечить возможность времени возобновления, чтобы разрешить устройству извещать о времени восстановлении, специфическом для устройства, например, короче (или продолжительнее), чем архитектурное минимальное время восстановления. Дополнительно, можно обеспечить возможности, которые позволят устройству инициировать прерывание для запуска доступов к конфигурациям перед заключением относительно архитектурного (или даже в некоторых реализациях извещаемого устройством) минимального времени восстановления среди других возможных примеров.

На фиг. 7 показана упрощенная блок-схема 700 последовательности операций. Контроллер программного обеспечения, такой как инструмент управления мощностью операционной системы, может быть готов к переходу конкретного устройства, такого как внутреннее устройство микропроцессорного набора или система на кристалле, к полной мощности и к побуждению устройства включить мощность 710 и начать переход из низкого состояния или состояния без мощности в активное состояние (например, в связи с конкретной функцией, которая будет выполняться с использованием устройства). Опрос (например 710) может иметь место на основании возможностей, определенных для устройства в соответствующем регистре управления мощностью, в структуре расширенных возможностей или другой структуре или регистре. Например, контроллер может идентифицировать время возобновления для устройства (например, архитектурное время или объявленная задержка по времени) и выдавать запись конфигурации для завершения триггера 725 перехода состояний мощности после идентификации того, что истекло время возобновления. Альтернативно, устройство может иметь возможность прерывания, определенную, например, в структуре возможностей или регистре, и контроллер может идентифицировать возможность или ожидать прерывание 720 из устройства, показывая, что устройство готово для ввода активного состояния и получения доступов к конфигурациям.

Как показано на фиг. 8, процесс 805 подсчета устройств можно выполнять в некоторых реализациях для того, чтобы определить, поддерживает ли устройство, такое как RCIE, корневой порт, порт, расположенный дальше по ходу, или другое поддерживает ли устройство одну или более возможностей времени возобновления. В конкретном примере, показанном на фиг. 8, процесс подсчета может подготовить 810 структуру возможностей, соответствующую устройству, и определить 815, извещается ли о и поддерживается ли время возобновления или восстановления, настроенное под пользователя. Процесс 805 подсчета позволяет в некоторых случаях также определить то, определены ли также для устройства возможности прерывания для того, чтобы оказать содействие в ускорении восстановления устройства. Если определено, что время возобновления поддерживается, например, этап 820, объявленное значение восстановления позволяет идентифицировать 825 то, что является конкретным для устройства (например, и точно определено в структуре возможностей). Объявленное значение восстановления может затем последовать за контроллером программного обеспечения при начале доступа к конфигурации в связи с переходом состояний мощности устройства. Альтернативно, если определено, что специальное время возобновления не поддерживается с помощью устройства (например, этап 830), контроллер программного обеспечения может принимать значение по умолчанию в архитектурных протоколах, включая стандартные минимальные периоды времени восстановления, определенные через архитектуру (например, фиксированное, минимальное время восстановления 10 мс, 100 мс и т.д.).

На фиг. 9 изображена блок-схема последовательности операций, показывающая набор операций 90 согласно по меньшей мере одному примерному варианту осуществления. Устройство, например, модуль 104 времени возобновления (фиг. 1) или часть его, может использовать набор операций 900. Устройство может содержать средство для выполнения операций, показанных на фиг. 9. В примерном варианте осуществления устройство преобразуется путем наличия памяти, например, памяти 184 и/или памяти 175 (фиг. 1), содержащей компьютерный код, выполненный с возможностью побуждать, при работе с процессором, устройство выполнять набор операций 900.

На этапе 905 устройство может определить (например, из соответствующего регистра) то, что оно находится в состоянии низкой мощности. Переход устройства из состояния низкой мощности в активное состояние можно инициировать на этапе 910, например, с помощью по меньшей мере частично контроллера на основе программных средств. Фиксированное минимальное время возобновления можно определить для переходов из состояния низкой мощности в активное состояние в пределах системы, например, время архитектурного восстановления в соответствии с протоколом межсоединений. Возможность устройства можно идентифицировать на этапе 915 согласно управлению мощностью устройства. Возможность может включать в себя механизм прерывания, поддерживаемый для устройства, и объявленное, альтернативное время восстановления, которое было применено к устройству вместо фиксированного минимального времени восстановления. В некоторых случаях для устройства могут быть разрешены обе возможности. Переход устройства в активное состояние можно завершить на этапе 920, например, через конфигурацию устройства, инициированную с помощью триггера, соответствующего идентифицированной возможности. Например, можно применить объявленное время восстановления или можно получить прерывание для запуска завершения перехода устройства в активное состояние перед истечением фиксированного минимального времени восстановления среди других потенциальных примеров и реализаций.

Принципы, описанные выше, можно применить к любому множеству различных архитектур, включающих в себя различные платформы межсоединений. Кроме того, вышеприведенные принципы можно применить во множестве различных устройств, включающих в себя мультипроцессорные серверы, персональные компьютеры, мобильные вычислительные устройства (например, смартфоны, планшетные компьютеры и т.д.) среди других примеров, в качестве только одного примера на фиг. 10 изображен вариант осуществления конфигурации "система на кристалле" (SOC). В качестве конкретного иллюстративного примера, SOC 1000 может быть включена в компьютер, содержащий пользовательское оборудование (UE). В одном варианте осуществления UE относится к любому устройству, которое будет использоваться конечным пользователем для обеспечения связи, такому как переносной телефон, смартфон, планшетный компьютер, сверхтонкий ноутбук, ноутбук с широкополосным адаптером или любое другое подобное коммуникационное устройство. Часто UE подсоединяется к базовой станции или узлу, который потенциально соответствует по своей природе мобильной станции (MS) в сети GSM.

В данном случае, SOC 1000 включает в себя два ядра 1006 и 1007. Аналогично обсуждению, приведенному выше, ядра 1006 и 1007 могут соответствовать архитектуре набора инструкций, такой как процессор на основе Core™ архитектуры Intel®, усовершенствованные микроустройства, процессор Inc. (AMD), процессор на основе MIPS, конфигурация процессора на основе ARM или их потребитель, а также их лицензии или последователи. Ядра 1006 и 1007 подсоединены к управлению 1008 кэш-памятью, которая связана с блоком 1009 интерфейса шины и кэш 1012 L2 для поддержания связи с другими частями системы 1000. Межсоединение 1010 включает в себя накристальное межсоединение, такое как IOSF, AMBA или другое межсоединение, обсужденное выше, которое потенциально реализует один или более аспектов описанного изобретения.

Интерфейс 1010 обеспечивает каналы связи с другими компонентами, такими как модуль 1030 идентификации абонента (SIM) для сопряжения с SIM-картой, загрузочное ПЗУ 1035 для сохранения загрузочного кода для исполнения ядрами 1006 и 1007, чтобы инициировать и загрузить SOC 1000, контроллер 1040 SDRAM для сопряжения с внешней памятью (например, DRAM 1060), контроллер флэш-памяти 1045 для сопряжения с энергонезависимой памятью (например, флэш-памятью 1065), управление 1050 периферийными устройствами (например, последовательный синхронный периферийный интерфейс) для сопряжения с периферийными устройствами, видеокодеки 1020 и видеоинтерфейс 1025 для отображения и приема входного сигнала (например, входного сигнала, инициированного касанием), GPU (графический процессор) 1015 для выполнения графических операций, которые относятся к вычислениям и т.д. Любой из этих интерфейсов может включать в себя аспекты изобретения, описанные в данном документе.

Кроме этого, система иллюстрирует периферийное устройство для связи, такое как модуль 1070 Bluetooth, модем 1075 3G, GPS 1085 и WiFi 1085. Следует отметить, как изложено выше, UE включает в себя радио для обеспечения связи. В результате, эти периферийные модули связи совсем не требуются. Однако в UE необходимо включить некоторую форму радиосвязи для внешней связи.

Следует отметить, что "устройство", "способ" и "система", описанные выше, можно реализовать в виде любого электронного устройства или системы, как было упомянуто выше. В качестве конкретных иллюстраций, фигуры, приведенные ниже, предусматривают примерные системы для применения изобретения, как описано в данном документе. Так как системы, приведенных ниже, описаны более конкретно, ряд различных межсоединений раскрыты, описаны и заново пересмотрены из обсуждения, приведенного выше. И, как уже очевидно, преимущества, описанные выше, можно применить к любому из этих межсоединений связных архитектур или архитектур.

Хотя настоящее изобретение было описано по отношению к ограниченному числу вариантов осуществления, специалистам в данной области техники будут понятны его многочисленные модификации и изменения, которые можно выполнить в нем. Предполагается, что прилагаемая формула изобретения охватывает все такие модификации и изменения, подпадающие под истинную сущность и объем данного настоящего изобретения.

Проектирование может проходить через различные этапы от создания до моделирования и изготовления. Данные, представляющие проектирование, могут представлять собой проектирование в ряде способов. Во-первых, как это полезно при моделировании, аппаратные средства можно представить, используя язык описания аппаратных средств или другой функциональный язык описания. Дополнительно, модель уровня схемы с логическими и/или транзисторными вентилями можно произвести на некоторых стадиях процесса проектирования. Кроме того, большая часть проектирования на некоторой стадии достигает уровня данных, представляющих физическое размещение различных устройств в модели аппаратных средств. В случае, где используются традиционные технологии изготовления полупроводников, данные, представляющие модель аппаратных средств, могут представлять собой данные, точно определяющие наличие или отсутствие различных особенностей на различных уровнях маски для масок, которые используются для производства интегральной схемы. В любом представлении проектирования данные можно сохранять в любой форме машиночитаемого носителя. Память, или магнитные или оптические запоминающие устройства, такие как диск, может представлять собой машиночитаемый носитель для хранения информации, которая передается посредством оптической или электрической волны, модулированной или иным образом выработанной для передачи такой информации. Когда электрическая несущая волна, показывающая или несущая код или конфигурацию, передается до такой степени, что выполняется копирование, буферизация или повторная передача электрического сигнала, делается новая копия. Таким образом, провайдер связи или провайдер сети может сохранить на материальном машиночитаемом носителе по меньшей мере временно, товар, такой как информация, закодированная в несущей волне, осуществляющая технологии вариантов осуществления настоящего изобретения.

Модуль, который используется в данном документе, относится к любой комбинации из аппаратных средств, программного обеспечения и/или программно-аппаратных средств. В качестве примера, модуль включает в себя аппаратные средства, такие как микроконтроллер, ассоциированный с энергонезависимым носителем для хранения кода, адаптированного для дальнейшего исполнения микроконтроллером. Поэтому ссылка на модуль в одном варианте осуществления относится к аппаратным средствам, которые конкретным образом сконфигурированы для распознавания и/или исполнения кода, который будет храниться на энергонезависимом носителе. Кроме того, в другом варианте осуществления применение модуля относится к энергонезависимому носителю, включающему в себя код, который конкретным образом адаптирован для дальнейшего исполнения микроконтроллером для выполнения предопределенных операций. И, как можно сделать вывод, в еще одном варианте осуществления термин "модуль" (в этом примере) может относиться к комбинации из микроконтроллера и энергонезависимого носителя. Часто границы модуля, которые иллюстрированы как отдельные, обычно изменяются и, возможно, перекрываются. Например, первый и второй модуль может совместно использовать аппаратные средства, программное обеспечение, программно-аппаратные средства или их комбинацию, в то же время, по возможности, удерживая некоторые независимые аппаратные средства, программное обеспечение или программно-аппаратные средства. В одном варианте осуществления использование термина "логика" включает в себя аппаратные средства, такие как транзисторы, регистры или другие аппаратные средства, такие как программируемые логические устройства.

Использование фразы "для" или "сконфигурированный для" в одном варианте осуществления относятся к размещению, компоновке, изготовлению, предложению к продаже, импорту и/или проектированию устройства, аппаратных средств, логических устройств или элемента для выполнения проектной или определенной задачи. В данном примере устройство или его элемент, который не находится в рабочем состоянии, по-прежнему "сконфигурирован для" выполнения назначенной задачи, если она спроектирована, связана и/или взаимосвязана с выполнением упомянутой назначенной задачи. В чисто иллюстративном примере логический вентиль может выдавать логические 0 или 1 во время операции. Но логический вентиль, "сконфигурированный для" подачи разрешающего сигнала с тактовыми импульсами не включает в себя возможный логический вентиль, который может выдавать логическую 1 или 0. Вместо этого, логический вентиль представляет собой логический вентиль, подсоединенный некоторым образом, который во время операции вывода 1 или 0 должен разрешать тактовый импульс. Следует еще раз отметить, что использование термина "сконфигурированный для" не требует операции, но вместо этого указывает на скрытое состояние устройства, аппаратных средств и/или элемента, где в скрытом состоянии устройство, аппаратные средства и/или элемент предназначены для выполнения конкретной задачи при работе устройства, аппаратных средств и/или элемента.

Кроме того, использование фраз "допускающий/способный" и/или "выполненный с возможностью" в одном варианте осуществления относится к некоторому устройству, логическому устройству, аппаратным средствам и/или элементу, выполненному таким образом, чтобы обеспечить использование устройство, логического устройства, аппаратных средств и/или элемента конкретным образом. Как было отмечено выше, "использование для", "способный" или "выполненный с возможностью" в одном варианте осуществления относятся к скрытому состоянию устройства, логическому устройству, аппаратных средств и/или элемента где устройство, логическое устройство, аппаратные средства и/или элемент не работает, но предназначен таким образом обеспечить использование устройства конкретным образом.

Значение, которое используются в данном документе, включает в себя любое известное представление числа, состояния, логического состояния или двоичного логического состояния. Часто использование логических уровней, значений логического устройства или логических значений также относится к единицам (1) или нулям (0), которые просто представляют двоичные логические состояния. Например, 1 относится к высокому логическому уровню, и 0 относится к низкому логическому уровню. В одном варианте осуществления ячейка памяти, такая как транзистор или ячейка флэш-памяти, позволяет сохранять одно логическое значение или многочисленные логические значения. Однако были использованы и другие представления значений в компьютерных системах. Например, десятичное число десять можно также представить в виде двоичного значения 1010 и шестнадцатеричной буквы A. Поэтому значение включает в себя любое представление информации, которое может храниться в компьютерной системе.

Более того, состояние можно представить с помощью значений или частей значений. В качестве примера, первое значение, такое как логическая единица, может представлять собой значение по умолчанию или исходное состояние, тогда как второе значение, логический ноль, может представлять собой состояние не по умолчанию. В дополнение к этому, термины "сброс" и "установка" в одном варианте осуществления относятся к значению по умолчанию и обновленному значению или состоянию, соответственно. Например, значение по умолчанию потенциально включает в себя высокое логическое значение, то есть сброс, тогда как обновленное значение потенциально включает в себя низкое логическое значение, то есть установку. Следует отметить, что любую комбинацию значений можно использовать для представления любого числа состояний.

Варианты осуществления способов, аппаратных средств, программного обеспечения, программно-аппаратных средств или кода, изложенные выше, можно реализовать посредством инструкций или кода, который хранится на машинодоступном, машиночитаемом, компьютернодоступном или компьютерночитаемом носителе, которые исполняются процессорным элементом. Невременный машинодостуный/машиночитаемый носитель включает в себя любой механизм, который обеспечивает (то есть сохраняет и/или передает) информацию в виде, читаемом машиной, такой как компьютер или электронной системой. Например, невременный машинодоступный носитель включает в себя оперативное запоминающее устройство (RAM), такое как статическое RAM (SRAM) или динамическое RAM (DRAM); постоянное запоминающее устройство (ROM); магнитный или оптический носитель информации; устройство на основе флэш-памяти; электрические запоминающие устройства; оптические запоминающие устройства; акустические запоминающие устройства; другие виды запоминающих устройств для хранения информации, получаемой из переходных (временных) сигналов (например, несущие волны, инфракрасные сигналы, цифровые сигналы); и т.д., которые следует отличать от невременных носителей, которые могут получать из них информацию.

Инструкции, используемые в логике программы для выполнения вариантов осуществления настоящего изобретения можно хранить в пределах памяти в системе, такой как DRAM, кэш-память, флэш-память или другое запоминающее устройство. Кроме того, инструкции можно распространять через сеть или посредством других компьютерночитаемых носителей. Таким образом, машиночитаемый носитель может включать в себя любой механизм для хранения или передачи информации в форме, подлежащей считыванию машиной (например, компьютером), но не ограничивается гибкими дисками, оптическими дисками, компакт-дисками, ROM на основе компакт-дисков (CD-ROM), и магнитооптическими дисками, постоянными запоминающими устройствами (ROM), оперативными запоминающими устройствами (RAM), стираемыми программируемыми постоянными запоминающими устройствами (EPROM), электрически стираемыми программируемыми постоянными запоминающими устройствами (EEPROM), магнитными или оптическими картами, флэш-памятью или материальным машиночитаемым носителем, который используется при передаче информации по Интернет посредством электрической, оптической, акустической или другими формами распространяющихся сигналов (например, несущих волн, инфракрасных сигналов, цифровых сигналов и т.д.). Соответственно, компьютерночитаемый носитель включает в себя любой тип материального машиночитаемого носителя, подходящего для хранения и передачи электронных инструкций или информаций в форме, подходящей для считывания машиной (например, компьютером).

Следующие примеры относятся к вариантам осуществления в соответствии с этим описанием. Один или более вариантов осуществления позволяют выполнить устройство, систему, машиночитаемое и запоминающее устройство, машиночитаемый носитель и способ для определения того, что устройство находится в состоянии с низкой мощностью; инициировать переход устройства из состояния с низкой мощностью в активное состояние, где фиксированное минимальное время восстановления определено для переходов из состояния с низкой мощностью в активное состояние; идентифицировать возможность устройства, соответствующую переходу устройству из состояния с низкой мощностью в активное состояние; и завершить переход устройства из состояния с низкой мощностью в активное состояние, основываясь по меньшей мере частично на возможности, где переход должен завершиться перед истечением фиксированного минимального времени восстановления.

По меньшей мере, в одном примере возможность включает в себя возможность прерывания, и прерывание следует получать из устройства, где прерывание представляет собой индикацию того, что устройство готово для завершения перехода. Устройство можно контролировать для прерывания.

Один или более примеров могут дополнительно обеспечить то, что переход должен завершиться согласно определенному времени восстановления для устройства, если прерывание не получено перед определенным временем восстановления.

По меньшей мере, в одном примере определенное время восстановления включает в себя фиксированное минимальное время восстановления. Определенное время восстановления может включать в себя объявленное время восстановления, определенное для устройства.

По меньшей мере, в одном примере возможность включает в себя объявленное время восстановления для устройства, и объявленное время восстановления короче, чем фиксированное минимальное время восстановления.

По меньшей мере, в одном примере объявленное время восстановления можно применить к переходу устройства из состояния с низкой мощностью в активное состояние вместо фиксированного минимального времени восстановления.

По меньшей мере, в одном примере фиксированное минимальное время восстановления можно применить к другому устройству при переходе другого устройства из состояния с низкой мощностью в активное состояние.

По меньшей мере, в одном примере устройство включает в себя устройство, совместимое с быстродействующими межсоединениями периферийных компонентов (PCI). Состояние с низкой мощностью может включать в себя состояние D3, и активное состояние может включать в себя состояние D0.

По меньшей мере, в одном примере завершение перехода устройства из состояния с низкой мощностью в активное состояние должно включать в себя отправку запроса на доступ к конфигурации в устройство.

По меньшей мере, в одном примере устройство включает в себя по меньшей мере одно из следующего: корневой порт, порт, расположенный дальше по ходу, или конечную точку, выполненную как единое целое с корневым комплексом.

Один или более примеров могут дополнительно обеспечить машиночитаемую память, хранящую структуру возможности управления мощностью, определяющую возможности управления мощностью по меньшей мере одного устройства; и контроллер управления мощностью для идентификации конкретной возможности для устройства из структуры возможности управления мощностью, и завершить переход устройства из состояния с низкой мощностью в активное состояние, основываясь по меньшей мере частично на конкретной возможности, где переход должен завершиться перед истечением фиксированного минимального времени восстановления, определенного для переходов из состояния с низкой мощностью в активное состояние.

По меньшей мере, в одном примере структура возможности управления мощностью определяет для устройства то, определено ли альтернативное время восстановления для устройства.

По меньшей мере, в одном примере структура возможности управления мощностью определяет альтернативное время восстановления для устройства, которое короче, чем фиксированное минимальное время восстановления.

По меньшей мере, в одном примере структура возможности управления мощностью определяет для устройства то, поддерживается ли прерывание устройством, и завершен ли переход устройства из состояния с низкой мощностью в активное состояние, основываясь на получении прерывания из устройства.

По меньшей мере, в одном примере устройство должно контролировать прерывание в случае, если структура возможности управления мощностью показывает, что устройство поддерживает прерывание.

По меньшей мере, в одном примере инициирование перехода устройства из состояния с низкой мощностью в активное состояние включает в себя подачу питания на устройство.

Ссылка на всем протяжении данного описания на "один вариант осуществления" или "вариант осуществления" означает, что конкретная особенность, структура, или характеристика, описанная в связи с вариантом осуществления, включена по меньшей мере в один вариант осуществления настоящего изобретения. Таким образом, появление фраз "в одном варианте осуществления" или "в варианте осуществления" в различных местах на всем протяжении данного описания не обязательно полностью относится к одному и тому же варианту осуществления. Кроме того, конкретные особенности, структуры или характеристики можно объединить любым подходящим способом в одном или более вариантах осуществления.