Изобретение относится к области радиотехники и может быть использовано в устройствах приема цифровых информационных сигналов для цифровой демодуляции двоичных сигналов с относительной фазовой манипуляцией второго порядка (ОФМ2).

Известно устройство некогерентной демодуляции сигналов с однократной (двоичной) относительной фазовой модуляцией второго порядка [1]. Устройство содержит два коррелятора, генератор гармонических колебаний, фазовращатель, линии задержки, вычислитель откликов и схему сравнения. Его недостатком является аналоговая обработка сигнала, сложность реализации корреляторов, линий задержки и вычислителя, неидентичность каналов квадратурной обработки сигнала.

Известен демодулятор, описанный в [2]. В этом демодуляторе производится нелинейное преобразование входного сигнала в импульсную последовательность с определением фазового сдвига подсчетом числа тактовых импульсов на интервале смещения во времени входного и опорного сигналов, далее в многоканальной линии задержки формируются отклики демодулятора, которые корректируются сигналами кольца фазовой автоподстройки частоты, а затем подаются в фазовый дискриминатор. Недостатком устройства является неоптимальная аналого-цифровая обработка сигнала, приближенная оценка фазового сдвига, особенно затруднительная для высокочастотных радиосигналов, что приводит к снижению помехоустойчивости, а также сложность практической реализации.

Наиболее близким по технической сущности и внутренней структуре к предлагаемому устройству является цифровой демодулятор сигналов с относительной фазовой манипуляцией [3], способный выполнять демодуляцию сигналов с ОФМ первого порядка. Его недостатком является отсутствие возможности демодуляции сигналов с относительной фазовой манипуляцией второго порядка.

Задачей предлагаемого технического решения является обеспечение высокоскоростной цифровой демодуляции сигналов с относительной фазовой манипуляцией второго порядка.

Поставленная задача решается тем, что цифровой демодулятор сигналов с относительной фазовой манипуляцией второго порядка, содержащий аналого-цифровой преобразователь (АЦП), регистр сдвига многоразрядных кодов на четыре отсчета, первый и второй n-каскадные каналы квадратурной обработки (ККО) сигналов и генератор тактовых импульсов (ГТИ), дополнительно содержит первый и второй блоки обработки отсчетов (БОО), каждый из которых состоит из первого и второго многоразрядных регистров сдвига, первого, второго и третьего сумматора, первого, второго и третьего вычитателя и блока формирования решения (БФР), содержащего первый, второй, третий и четвертый квадратичные преобразователи (КП), первый, второй и третий вычитатели, первый и второй мультиплексоры и триггер, выход каждого ККО соединен с входом соответствующего БОО, в котором вход первого регистра сдвига соединен с первыми входами первого сумматора и первого вычитателя, образуя вход БОО, а выход первого регистра сдвига подключен к входу второго регистра сдвига и вторым входам первого сумматора и первого вычитателя, выход второго регистра сдвига соединен с первыми входами второго и третьего сумматора и первыми входами второго и третьего вычитателя, вторые входы второго сумматора и второго вычитателя соединены с выходом первого сумматора, вторые входы третьего сумматора и третьего вычитателя соединены с выходом первого вычитателя, выходы второго и третьего сумматора и второго и третьего вычитателя образуют соответственно первый, второй, третий и четвертый выходы БОО, первые выходы первого и второго БОО соединены с первым и вторым входами первого КП БФР, вторые выходы первого и второго БОО соединены с первым и вторым входами второго КП БФР, третьи выходы первого и второго БОО соединены с первым и вторым входами третьего КП БФР, а четвертые выходы первого и второго БОО соединены с первым и вторым входами четвертого КП БФР, выходы первого и второго КП соединены с первым и вторым входами первого вычитателя БФР и с первым и вторым входами первого мультиплексора БФР, а управляющий вход первого мультиплексора БФР – с выходом знакового разряда первого вычитателя БФР, выходы третьего и четвертого КП соединены с первым и вторым входами второго вычитателя БФР и с первым и вторым входами второго мультиплексора БФР, а управляющий вход второго мультиплексора БФР – с выходом знакового разряда второго вычитателя БФР, выходы первого и второго мультиплексоров БФР подключены к первому и второму входам третьего вычитателя БФР, а его выходной знаковый разряд соединен с входом триггера, на управляющий вход которого подается сигнал тактовой синхронизации демодулятора, тактовые входы первого и второго ККО, регистров первого и второго БОО подключены к выходам ГТИ, выход триггера является выходом демодулятора.

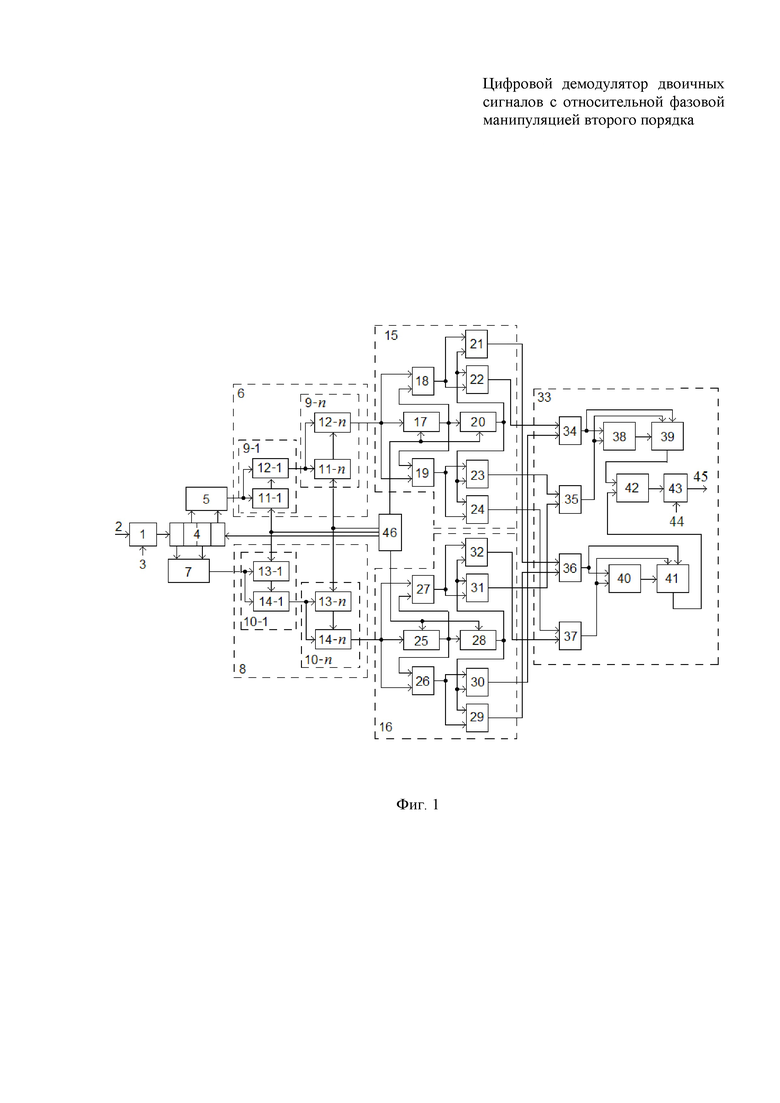

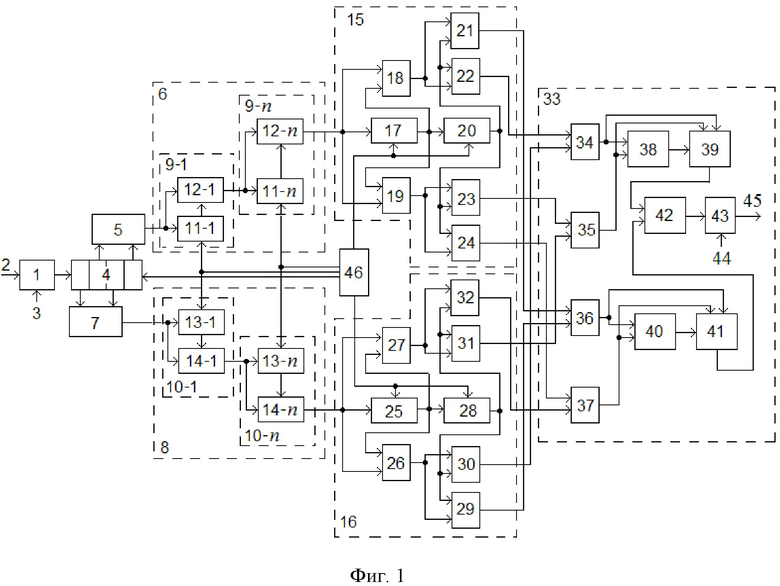

Предлагаемое техническое решение поясняется чертежами.

На фиг. 1 представлена структурная схема предлагаемого устройства;

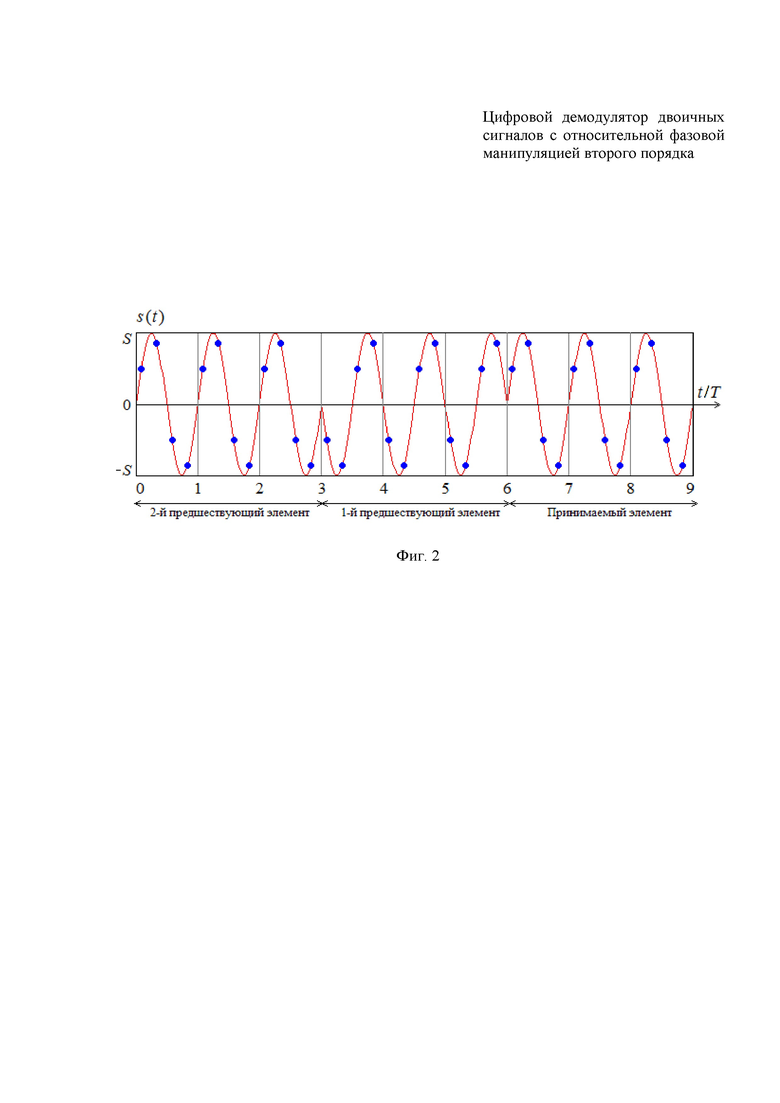

На фиг. 2 – процесс квантования;

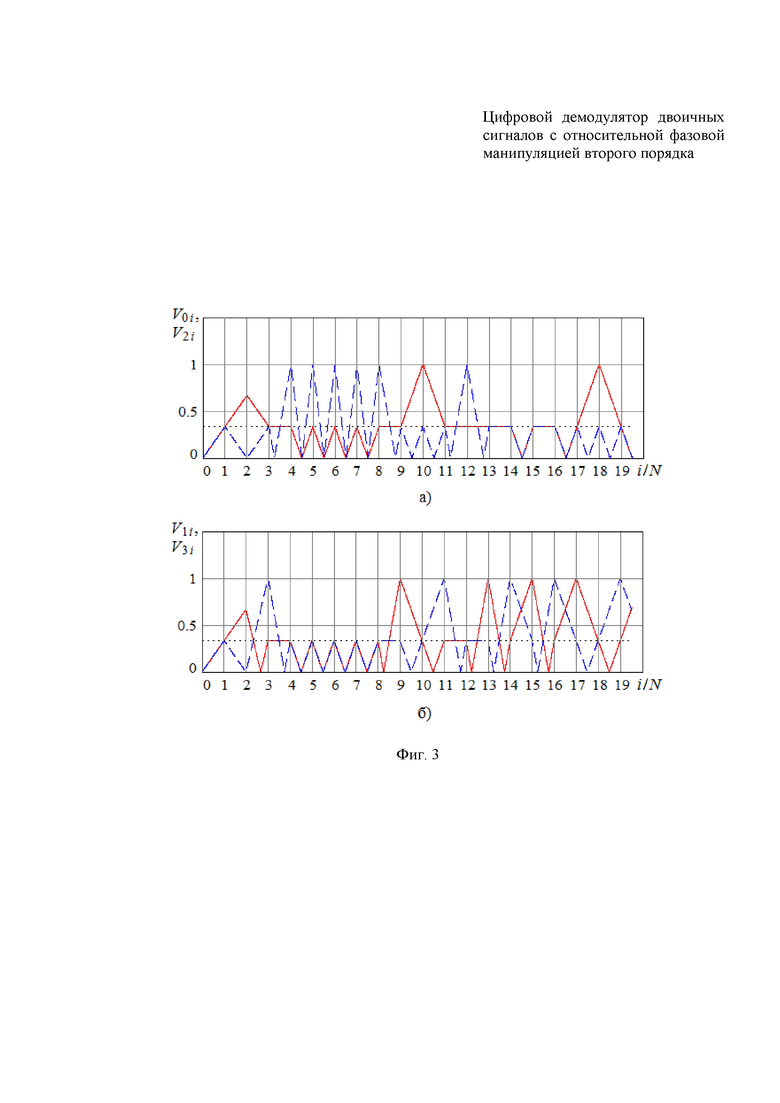

На фиг. 3 – моделирование работы демодулятора без помех;

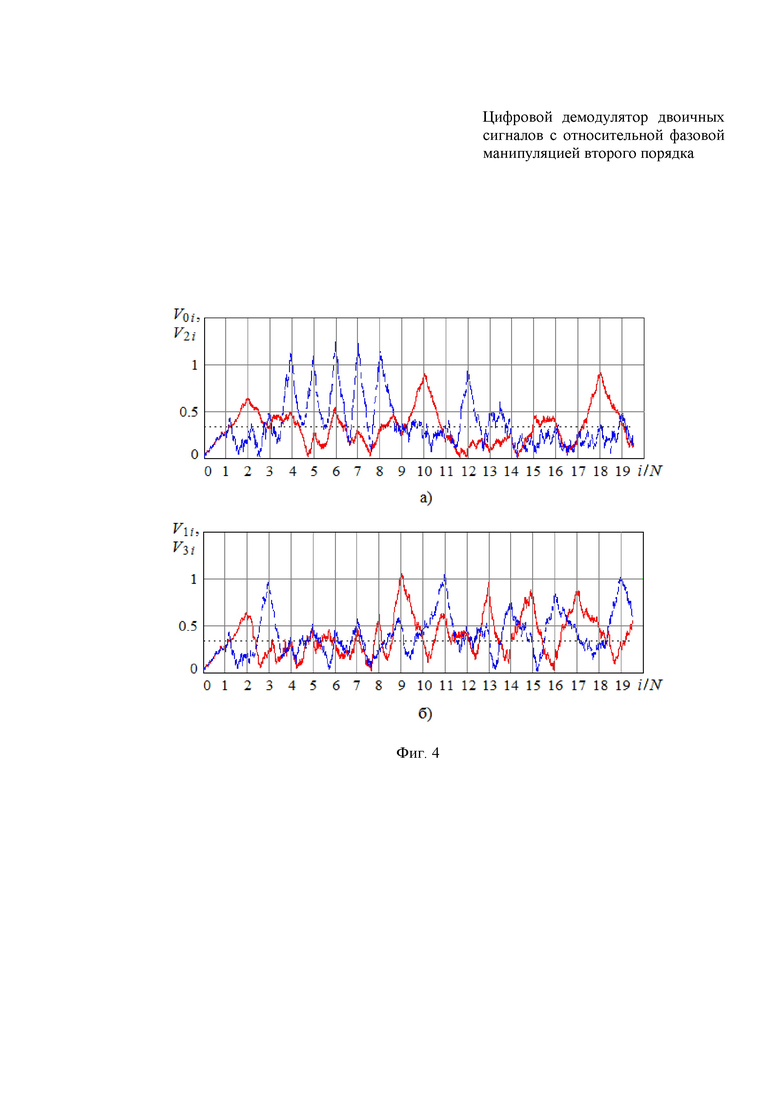

На фиг. 4 – моделирование работы демодулятора при наличии шумовой помехи;

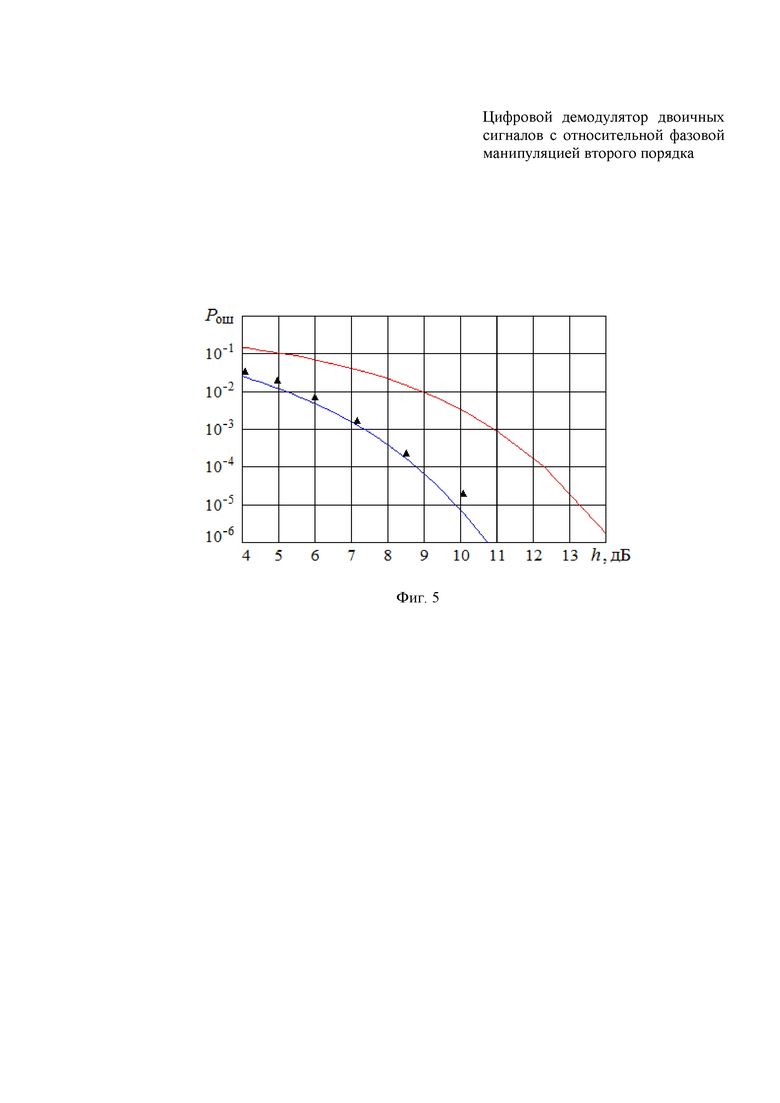

На фиг. 5 показаны результаты расчета и моделирования вероятности ошибок демодулятора по изобретению.

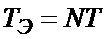

Устройство (фиг.1) содержит аналого-цифровой преобразователь АЦП 1, на вход которого поступает принимаемый сигнал 2 с выхода усилителя промежуточной частоты приемника, а на управляющий вход – тактовые импульсы 3. Выход АЦП 1 соединен с входом регистра 4 сдвига многоразрядных кодов на четыре отсчета, четные выходы которого соединены с соответствующими входами вычитателя 5 первого канала квадратурной обработки ККО 6, а нечетные выходы – с соответствующими входами вычитателя 7 второго ККО 8. Каждый из ККО 6, ККО 8, помимо вычитателя, содержит n каскадно соединенных блоков накопления отсчетов БНО. Количество БНО n зависит от числа N периодов сигнала в информационном символе и определяется двоичным логарифмом N (

Первый ККО 6 содержит последовательно соединенные БНО 9-1, …, 9-n , а второй ККО 8 – последовательно соединенные БНО 10-1, …, 10-n. Каждый из БНО состоит из регистра сдвига многоразрядных кодов и сумматора. Блоки 9-1, …, 9-n накопления отсчетов содержат регистры 11-1, …, 11-n сдвига многоразрядных кодов и сумматоры 12-1, …, 12-n соответственно, а БНО 10-1, …, 10-n – соответственно регистры 13-1, …, 13-n сдвига многоразрядных кодов и сумматоры 14-1, …, 14-n. В каждом блоке накопления отсчетов 9 (как и 10) первый вход регистра 11 (13) сдвига является входом блока 9 (10) накопления отсчетов. Второй вход сумматора 12 (14) соединен с выходом регистра 11 (13) сдвига. Выход сумматора 12 (14) является выходом блока 9 (10) накопления отсчетов, а тактовый вход регистра 11 (13) сдвига является управляющим входом блока 9 (10) накопления отсчетов. Выход вычитателя 5 соединен с входом блока 9-1 накопления отсчетов ККО 6, а выход блока 9-n накопления отсчетов ККО 6 – с входом первого блока обработки отсчетов БОО 15. Выход вычитателя 7 соединен с входом БНО 10-1 ККО 8, а выход БНО 10-n ККО 8 – с входом второго блока обработки отсчетов БОО 16.

В БОО 15 (16) вход первого регистра сдвига 17 (25) соединен с первыми входами первого сумматора 18 (26) и первого вычитателя 19 (27), образуя вход БОО 15 (16), а выход первого регистра сдвига 17 (25) подключен к входу второго регистра сдвига 20 (28) и вторым входам первого сумматора 18 (26) и первого вычитателя 19 (27), выход второго регистра сдвига 20 (28) соединен с первыми входами второго 22 (30) и третьего 23 (30) сумматора и первыми входами второго 21 (29) и третьего 24 (32) вычитателя, а вторые входы второго сумматора 22 (30) и второго вычитателя 21 (29) соединены с выходом первого сумматора 18 (26), вторые входы третьего сумматора 23 (30) и третьего вычитателя 24 (32) соединены с выходом первого вычитателя 19 (27), выходы второго 22 (30) и третьего 23 (30) сумматора и второго 21 (29) и третьего24 (32) вычитателя образуют соответственно первый, второй, третий и четвертый выходы БОО 15 (16).

Первые выходы первого БОО 15 и второго БОО 16 соединены с первым и вторым входами первого квадратичного преобразователя КП 33 БФР, вторые выходы первого БОО 15 и второго БОО 16 соединены с первым и вторым входами второго КП 34 блока формирования решения БФР, третьи выходы первого БОО 15 и второго БОО 16 соединены с первым и вторым входами третьего КП 35 блока формирования решения БФР, а четвертые выходы первого БОО 15 и второго БОО 16 соединены с первым и вторым входами четвертого КП 36 БФР, выходы первого 34 и второго 35 КП соединены с первым и вторым входами первого вычитателя 38 БФР и с первым и вторым входами первого мультиплексора 39 БФР, а управляющий вход первого мультиплексора 39 БФР – с выходом знакового разряда первого вычитателя 38 БФР, выходы третьего36 и четвертого 37 КП соединены с первым и вторым входами второго вычитателя 40 БФР и с первым и вторым входами второго мультиплексора 41 БФР, а управляющий вход второго мультиплексора 41 БФР – с выходом знакового разряда второго вычитателя 40 БФР, выходы первого 39 и второго 41 мультиплексоров БФР подключены к первому и второму входам третьего вычитателя 42 БФР, а его выходной знаковый разряд соединен с входом триггера 43 БФР, на управляющий вход которого подается сигнал тактовой синхронизации демодулятора 44, тактовые входы первого ККО 6 и второго ККО 8, регистров первого 15 и второго 16 БОО подключены к выходам генератора тактовых импульсов ГТИ 46, а выход триггера 43 БФР является выходом 45 цифрового демодулятора двоичных сигналов.

Устройство работает следующим образом.

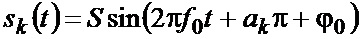

Сигнал с ОФМ второго порядка представляет собой последовательность информационных символов, k-й из которых является гармоническим колебанием вида

Таблица истинности имеет следующий вид.

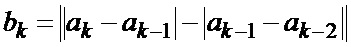

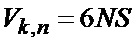

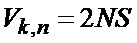

В принятых обозначениях

Повышение помехоустойчивости при демодуляции сигнала с ОФМ второго порядка по сравнению с классической ОФМ (первого порядка) при сохранении скорости передачи обеспечивается обработкой «в целом» трех последних принятых элементов [1], что и реализуется в предлагаемом устройстве.

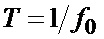

Входной сигнал с ОФМ второго порядка на входе 2 АЦП 1 квантуется во времени по четыре отсчета на период повторения

Процесс квантования показан на фиг. 2 точками для трех последовательных информационных элементов длительностью

На вход вычитателя 5 поступают четные отсчеты

На вход вычитателя 7 поступают нечетные отсчеты

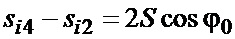

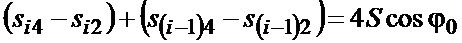

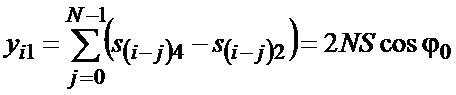

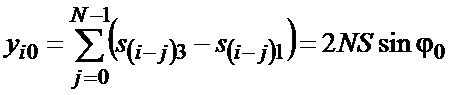

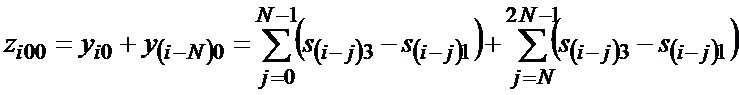

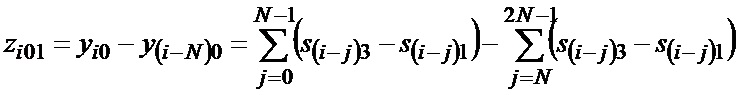

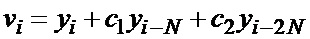

В первом БОО 15 производится обработка «в целом» четных отсчетов трех последних принятых символов, каждый длительностью по N периодов несущей, для четырех возможных комбинаций информационных фазовых сдвигов. В первом сумматоре 18 первого БОО 15 вычисляется величина

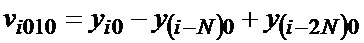

а в первом вычитателе 19 первого БОО 15 – разность

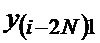

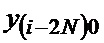

значения

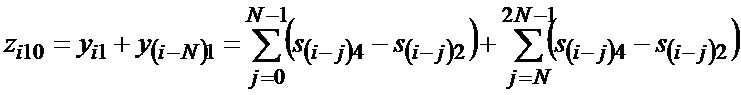

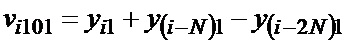

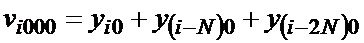

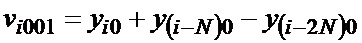

Во втором сумматоре 22 первого БОО 15 вычисляется величина

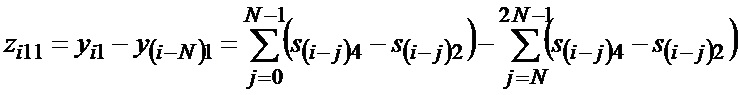

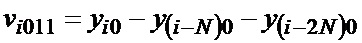

во втором вычитателе 21 первого БОО 15 –

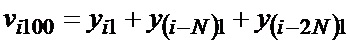

в третьем сумматоре 23 первого БОО 15 –

а в третьем вычитателе 24 первого БОО 15 –

Значения

Аналогично во втором БОО 16 производится обработка «в целом» нечетных отсчетов трех последних принятых символов. В первом сумматоре 26 второго БОО 16 вычисляется величина

а в первом вычитателе 27 второго БОО 16 – разность

значения

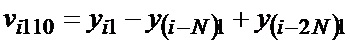

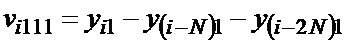

Во втором сумматоре 30 второго БОО 16 вычисляется величина

во втором вычитателе 29 второго БОО 16 –

в третьем сумматоре 31 второго БОО 16 –

а в третьем вычитателе 32 второго БОО 16 –

Значения

Результаты обработки отсчетов (3)-(6) и (7)-(10) в первом БОО 15 и втором БОО 16 поступают в блок формирования решения 33.

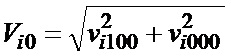

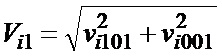

В первом квадратичном преобразователе 34 БФР 33 вычисляется величина

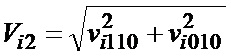

во втором КП 35 БФР 33 –

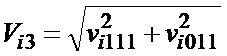

в третьем КП 36 БФР 33 –

а в четвертом КП 37 БФР 33 –

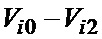

Далее в БФР 33 выбирается наибольшее значение из

Аналогично в вычитателе 40 БФР 33 формируется разность

Величины A и B поступают на первый и второй входы вычитателя 42 БФР 33, знаковый разряд которого формирует двоичный логический уровень

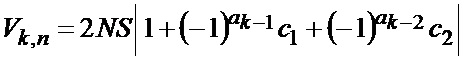

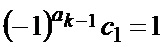

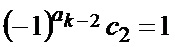

В общем виде величины

где

С учетом (1), (2), (15) для значений откликов квадратичных преобразователей после поступления k-го информационного символа получим

где

а, если не согласована (для трех других каналов), то

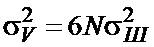

При воздействии полосового гауссовского шума с дисперсией отсчетов на выходе АЦП

Предполагается, что отсчеты шума на выходе АЦП статистически независимы.

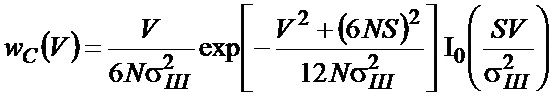

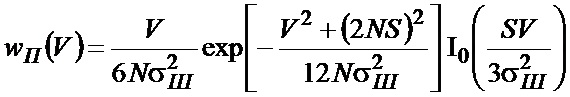

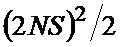

Одномерная плотность вероятностей значений V в согласованном с сигналом канале обработки соответствует распределению Райса [4] вида

а в несогласованном (помеховом) канале –

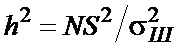

Здесь

При расчетах помехоустойчивости необходимо учитывать коррелированность откликов в различных каналах.

Отношение сигнал/шум

На фиг. 3 показаны результаты имитационного моделирования работы демодулятора сигнала с ОФМ второго порядка при отсутствии помехи

На фиг. 3б показаны аналогичные зависимости

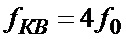

Для определения помехоустойчивости демодулятора можно использовать известные [4] выражения для оптимального некогерентного демодулятора сигналов с ОФМ первого порядка

и для оптимального когерентного демодулятора

где

Зависимости (16), (17) вероятностей

Предлагаемое цифровое техническое решение требует минимальных аппаратных затрат при реализации на программируемых логических интегральных схемах.

Использованная литература:

1. Окунев Ю.Б. Цифровая передача информации фазомодулированными сигналами. – М.: Радио и связь, 1991. – 296 с.

2. Тримайлов А.Е., Крутов М.И., Горляковский В.А. Цифровой демодулятор сигналов фазоразностной модуляции первого и второго порядка // Авторское свидетельство SU 1838884А3, МПК H04L27/22, опубл. 30.08.93 (Бюлл. № 32), заявка № 4938353/09 от 20.05.1991.

3. Литвиненко В.П., Глушков А.Н. Цифровой демодулятор сигналов с относительной фазовой манипуляцией // Патент № 2505922C2, МПК H04B1/10, H03D3/02, опубл. 27.01.2014 (Бюлл. № 3), заявка № 2011130805/08 от 22.07.2011.

4. Финк Л.М. Теория передачи дискретных сообщений. – М.: Сов. Радио, 1970. – 728 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой некогерентный демодулятор сигналов с амплитудно-фазовой манипуляцией | 2021 |

|

RU2766429C1 |

| Цифровой демодулятор сигналов с двухуровневой амплитудно-фазовой манипуляцией и относительной оценкой амплитуды символа | 2022 |

|

RU2790140C1 |

| Цифровой некогерентный демодулятор сигналов с амплитудно-четырехпозиционной фазовой манипуляцией | 2021 |

|

RU2761521C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2505922C2 |

| Цифровой демодулятор сигналов с амплитудной - относительной фазовой манипуляцией | 2022 |

|

RU2790205C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С АМПЛИТУДНО-ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2022 |

|

RU2786159C1 |

| ЦИФРОВОЙ НЕКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР ЧЕТЫРЕХПОЗИЦИОННЫХ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2017 |

|

RU2649782C1 |

| НЕКОГЕРЕНТНЫЙ ЦИФРОВОЙ ДЕМОДУЛЯТОР "В ЦЕЛОМ" КОДИРОВАННЫХ СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2014 |

|

RU2556429C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С МНОГОПОЗИЦИОННОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2021 |

|

RU2776968C1 |

| ЦИФРОВОЕ КВАДРАТУРНОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ И ДЕМОДУЛЯЦИИ | 2015 |

|

RU2591032C1 |

Изобретение относится к области радиотехники и может быть использовано в устройствах приема цифровых информационных сигналов для цифровой демодуляции двоичных сигналов с относительной фазовой манипуляцией второго порядка (ОФМ2). Достигаемый технический результат – обеспечение высокоскоростной цифровой демодуляции сигналов с относительной фазовой манипуляцией второго порядка. Цифровой демодулятор сигналов с относительной фазовой манипуляцией второго порядка содержит аналого-цифровой преобразователь (АЦП), регистр сдвига многоразрядных кодов на четыре отсчета, первый и второй n-каскадные каналы квадратурной обработки (ККО) сигналов, генератор тактовых импульсов (ГТИ), первый и второй блоки обработки отсчетов (БОО), каждый из которых состоит из первого и второго многоразрядных регистров сдвига, первого, второго и третьего сумматоров, первого, второго и третьего вычитателей и блока формирования решения (БФР), содержащего первый, второй, третий и четвертый квадратичные преобразователи (КП), первый, второй и третий вычитатели, первый и второй мультиплексоры и триггер. 5 ил.

Цифровой демодулятор двоичных сигналов с относительной фазовой манипуляцией второго порядка, содержащий аналого-цифровой преобразователь (АЦП), регистр сдвига многоразрядных кодов на четыре отсчета, первый и второй n-каскадные каналы квадратурной обработки (ККО) сигналов и генератор тактовых импульсов (ГТИ), отличающийся тем, что он дополнительно содержит первый и второй блоки обработки отсчетов (БОО), каждый из которых состоит из первого и второго многоразрядных регистров сдвига, первого, второго и третьего сумматоров, первого, второго и третьего вычитателей и блока формирования решения (БФР), содержащего первый, второй, третий и четвертый квадратичные преобразователи (КП), первый, второй и третий вычитатели, первый и второй мультиплексоры и триггер, выход каждого ККО соединен с входом соответствующего БОО, в котором вход первого регистра сдвига соединен с первыми входами первого сумматора и первого вычитателя, образуя вход БОО, а выход первого регистра сдвига подключен к входу второго регистра сдвига и вторым входам первого сумматора и первого вычитателя, выход второго регистра сдвига соединен с первыми входами второго и третьего сумматоров и первыми входами второго и третьего вычитателей, вторые входы второго сумматора и второго вычитателя соединены с выходом первого сумматора, вторые входы третьего сумматора и третьего вычитателя соединены с выходом первого вычитателя, выходы второго и третьего сумматоров и второго и третьего вычитателей образуют соответственно первый, второй, третий и четвертый выходы БОО, первые выходы первого и второго БОО соединены с первым и вторым входами первого КП БФР, вторые выходы первого и второго БОО соединены с первым и вторым входами второго КП БФР, третьи выходы первого и второго БОО соединены с первым и вторым входами третьего КП БФР, а четвертые выходы первого и второго БОО соединены с первым и вторым входами четвертого КП БФР, выходы первого и второго КП соединены с первым и вторым входами первого вычитателя БФР и с первым и вторым входами первого мультиплексора БФР, а управляющий вход первого мультиплексора БФР – с выходом знакового разряда первого вычитателя БФР, выходы третьего и четвертого КП соединены с первым и вторым входами второго вычитателя БФР и с первым и вторым входами второго мультиплексора БФР, а управляющий вход второго мультиплексора БФР – с выходом знакового разряда второго вычитателя БФР, выходы первого и второго мультиплексоров БФР подключены к первому и второму входам третьего вычитателя БФР, а его выходной знаковый разряд соединен с входом триггера, на управляющий вход которого подается сигнал тактовой синхронизации демодулятора, тактовые входы первого и второго ККО, регистров первого и второго БОО подключены к выходам ГТИ, выход триггера является выходом демодулятора.

| ЛИТВИНЕНКО В.П | |||

| и др Цифровой демодулятор "в целом" фазоманипулированных сигналов, кодированных последовательностями Уолша, Вестник Воронежского государственного технического университета, 2017, т.3, # 13, с.69-70, рис.1, 2, 3 | |||

| НЕКОГЕРЕНТНЫЙ ЦИФРОВОЙ ДЕМОДУЛЯТОР "В ЦЕЛОМ" КОДИРОВАННЫХ СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2014 |

|

RU2556429C1 |

| RU 26605952 C1, 06.07.2018 | |||

| Демодулятор псевдослучайных сигналов с относительной фазовой модуляцией | 2014 |

|

RU2625529C2 |

| US 4715047 A1, 22.12.1987 | |||

| ГЛУШКОВ А.Н | |||

| и др | |||

| Цифровой демодулятор сигналов с относительной фазовой манипуляцией, Вестник Воронежского государственного технического университета, 2016, т.12, # 2, с.94, рис.1 | |||

| УСТРОЙСТВО ВЫБОРА МИНИМАЛЬНОГО ИЛИ МАКСИМАЛЬНОГО ЧИСЛОВОГО ЗНАЧЕНИЯ ИЗ ДВУХ n-РАЗРЯДНЫХ ЧИСЕЛ | 2003 |

|

RU2262130C1 |

Авторы

Даты

2019-06-07—Публикация

2018-11-27—Подача