Изобретение относится к области вычислительной техники и может быть использовано при разработке узлов микропроцессора, в частности арифметических устройств, устройств приоритета и тому подобного.

В вычислительной технике часто нужно выбрать из двух или более чисел одно, которое является меньшим или большим.

Известно устройство выбора минимальной или максимальной величины, содержащее сумматор, усилитель знака разности, коммутатор (US №5515306, кл. G 06 F 7/00, 1996).

Недостатком известного устройства является большая задержка усилителя знака разности и то, что решение о том, какое из чисел надо пропустить через коммутатор, принимается только после того, как перенос в сумматоре пробежит от младшего разряда к старшему разряду.

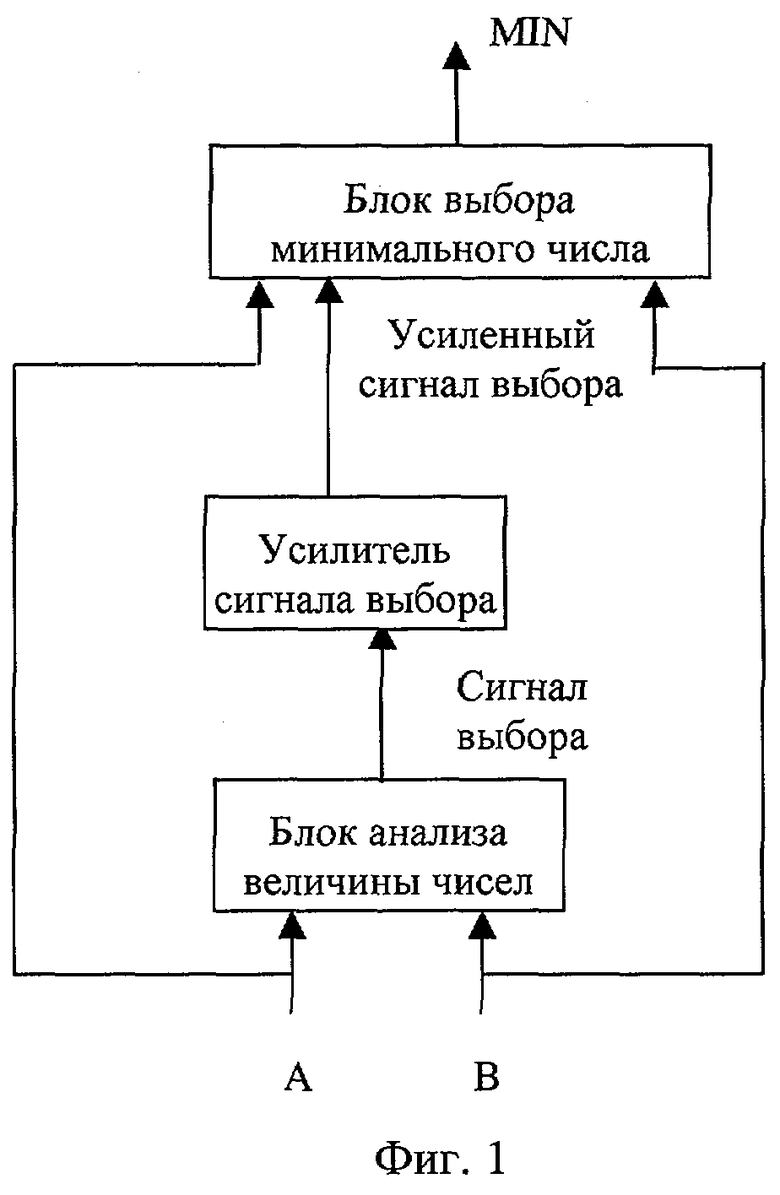

Наиболее близким по технической сущности к заявляемому изобретению является устройство выбора максимального значения из n-разрядных чисел, содержащее блок анализа величины чисел, выход которого подключен через усилитель сигнала выбора к блоку выбора минимального числа, выход которого является выходом устройства (US №5721809, кл. G 06 F 7/00, 1998).

Недостатком этого устройства является относительно большое время анализа одного разряда (около 5 логических уровней), а также то, что решение о том, какое из чисел надо пропустить через коммутатор, принимается только после анализа всех разрядов чисел. Кроме того, необходимо учесть задержку усилителя сигнала выбора.

Техническим результатом является повышение быстродействия устройства выбора минимального или максимального значения из двух n-разрядных чисел.

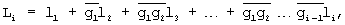

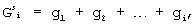

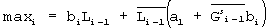

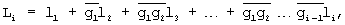

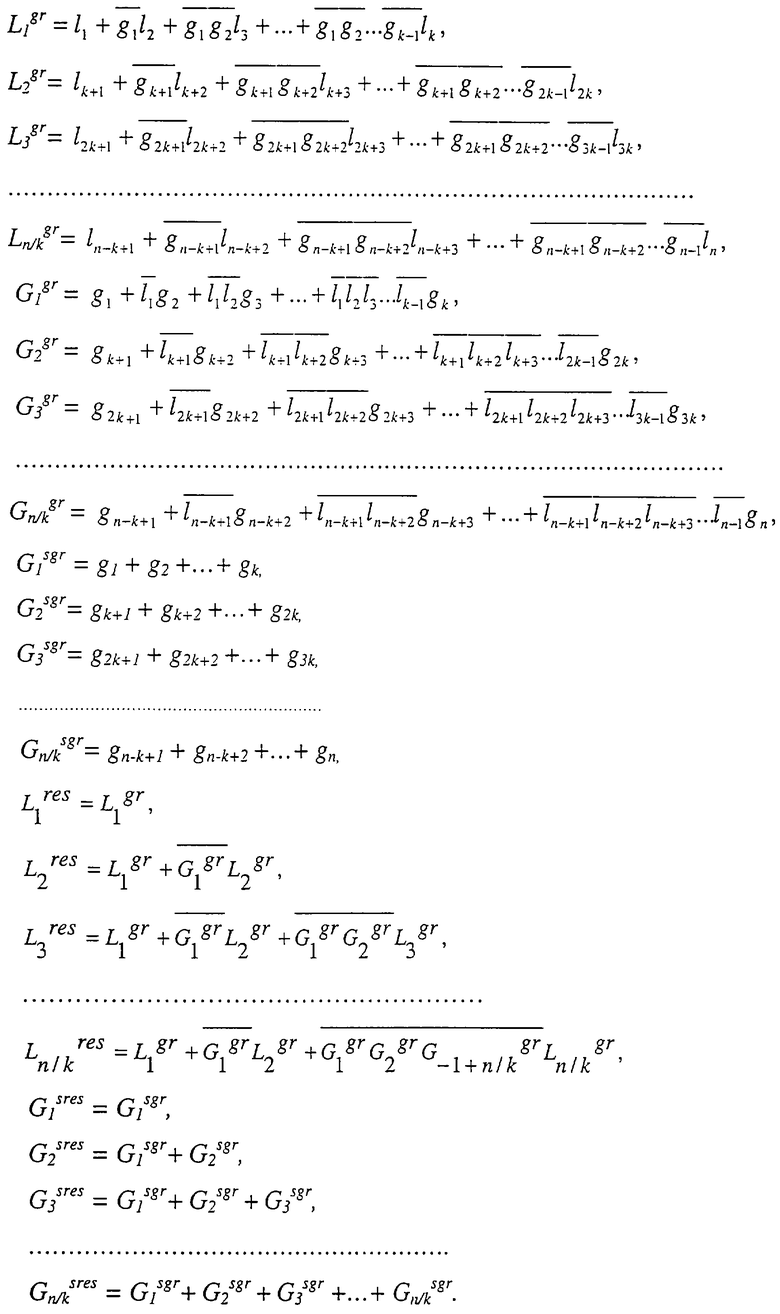

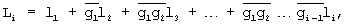

Достигается это тем, что устройство выбора минимального или максимального числового значения из двух n-разрядных чисел содержит блок преобразования чисел в поразрядные сигналы, входы которого являются входами устройства, выход через блок формирования выбирающих стробов подключен к входу управления коммутатора выбора минимального или максимального числа, выход которого является выходом устройства, а первый и второй информационные входы подключены к соответствующим входам устройства, кроме того, блок преобразования чисел в поразрядные сигналы обеспечивает формирование сигналов

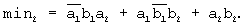

и

и  ,

,

где i=1, 2, ..., n, аi и bi - i-ые разряды двух n-разрядных двоичных чисел А и В, причем ai и bi - старшие разряды чисел, a an и bn - младшие разряды чисел, при этом блок формирования выбирающих стробов для выбора минимального или максимального числа реализует для каждого разряда следующие две логические функции:

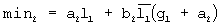

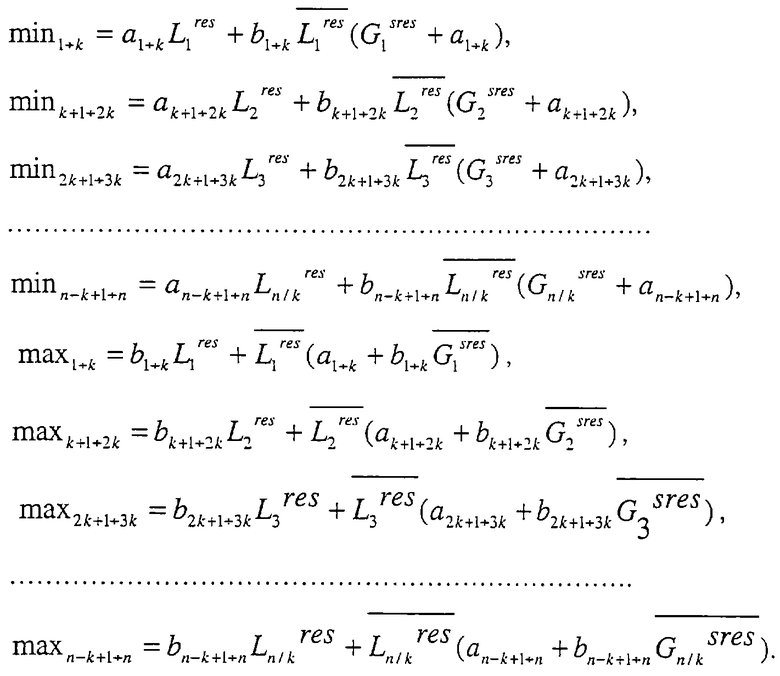

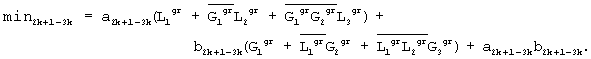

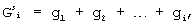

или для каждой группы по k разрядов:

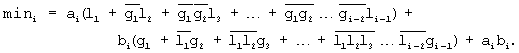

а коммутатор выбора минимального или максимального числа реализует следующие логические функции:

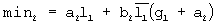

min1=a1b1 - для первого разряда,

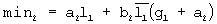

- для второго разряда,

- для второго разряда,

, где i=3, 4, 5,..., n, - для 3÷n разрядов,

, где i=3, 4, 5,..., n, - для 3÷n разрядов,

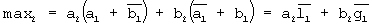

max1=a1+b1 - для первого разряда,

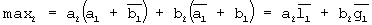

- для второго разряда,

- для второго разряда,

, где i=3, 4, 5, ..., n, - для 3÷n разрядов,

, где i=3, 4, 5, ..., n, - для 3÷n разрядов,

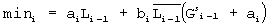

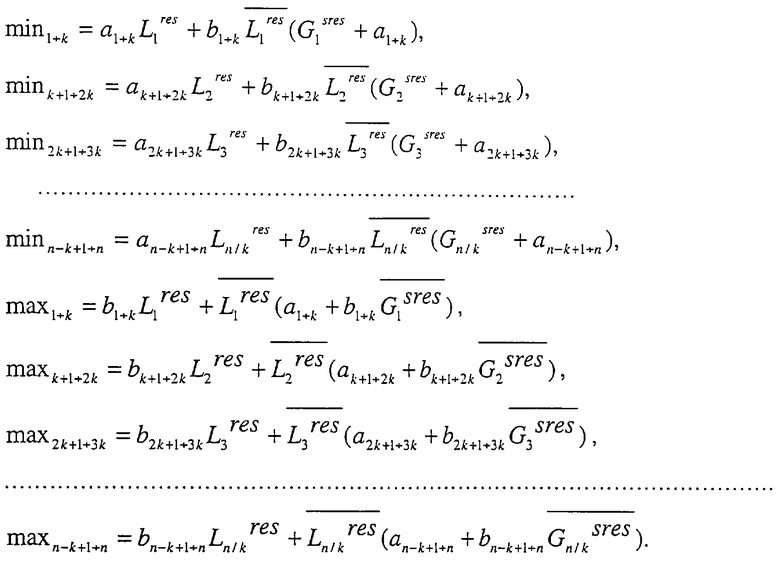

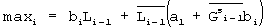

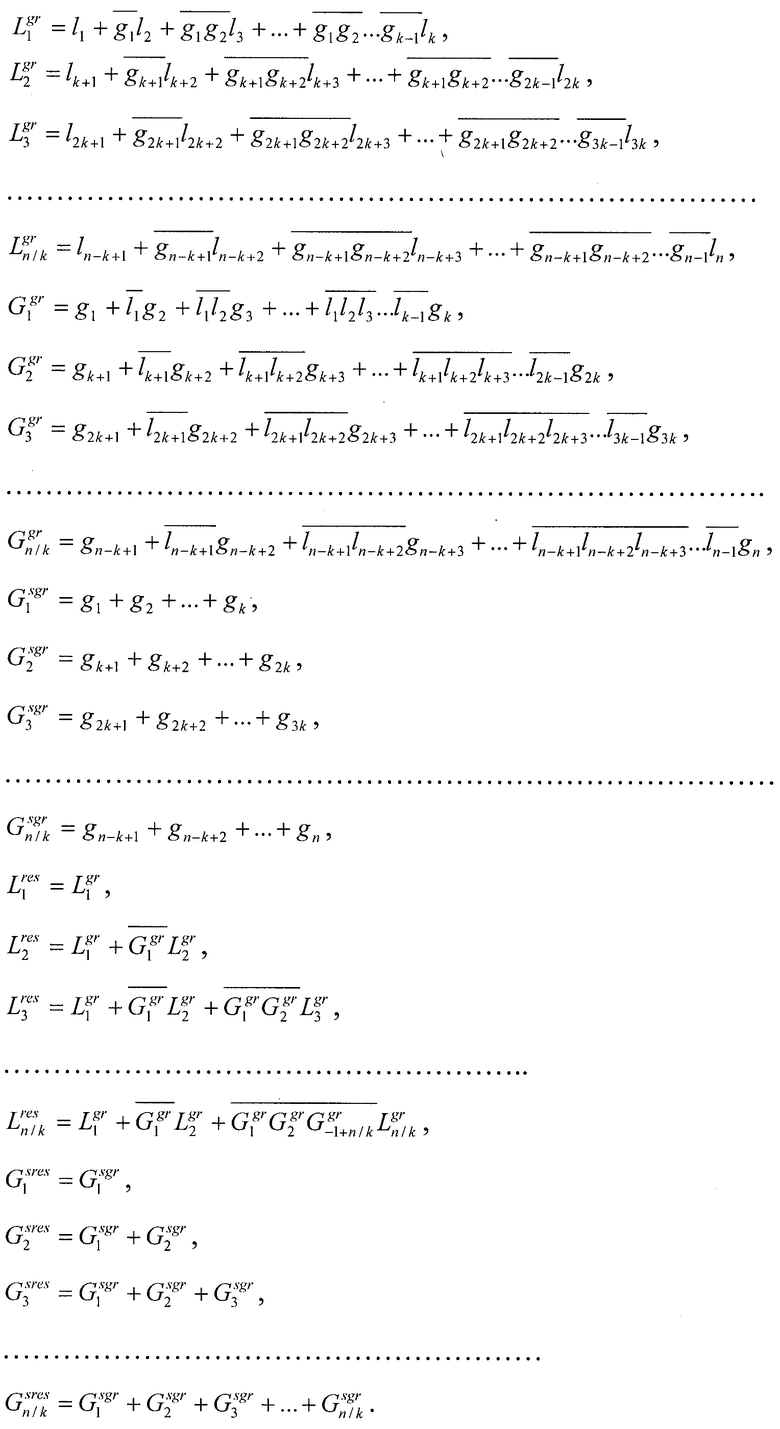

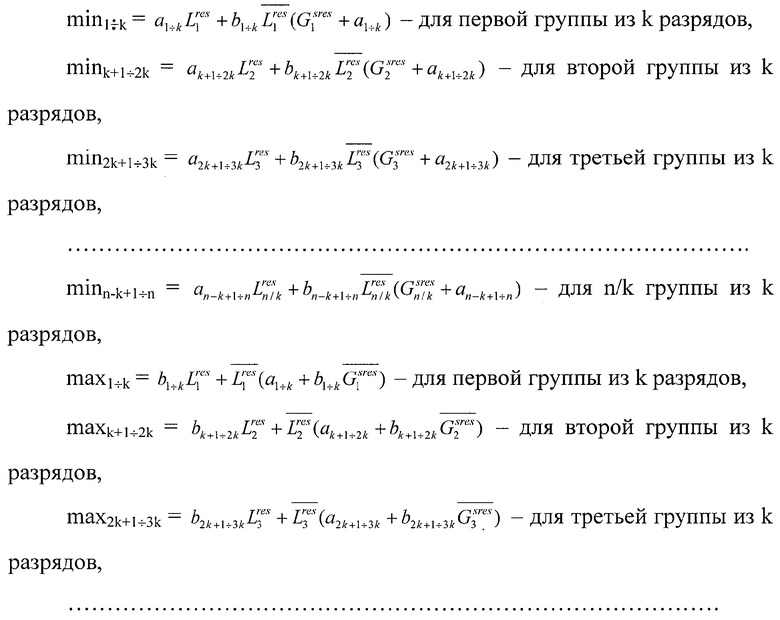

или для каждого разряда каждой группы по k разрядов реализует следующие логические функции:

Сущность изобретения заключается в том, что выполнение заявленного устройства вышеописанным образом позволяет осуществить выбор старших разрядов минимального или максимального значения чисел, не дожидаясь сравнения младших разрядов этих чисел.

Сравнение предлагаемого устройства с ближайшим аналогом позволяет утверждать о соответствии критерию «новизна», а отсутствие отличительных признаков в аналогах говорит о соответствии критерию «изобретательский уровень».

Предварительные испытания позволяют судить о возможности широкого промышленного использования.

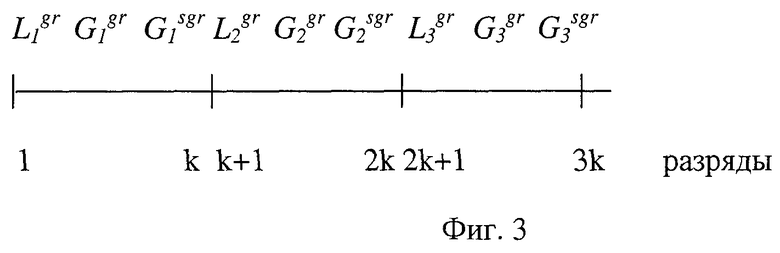

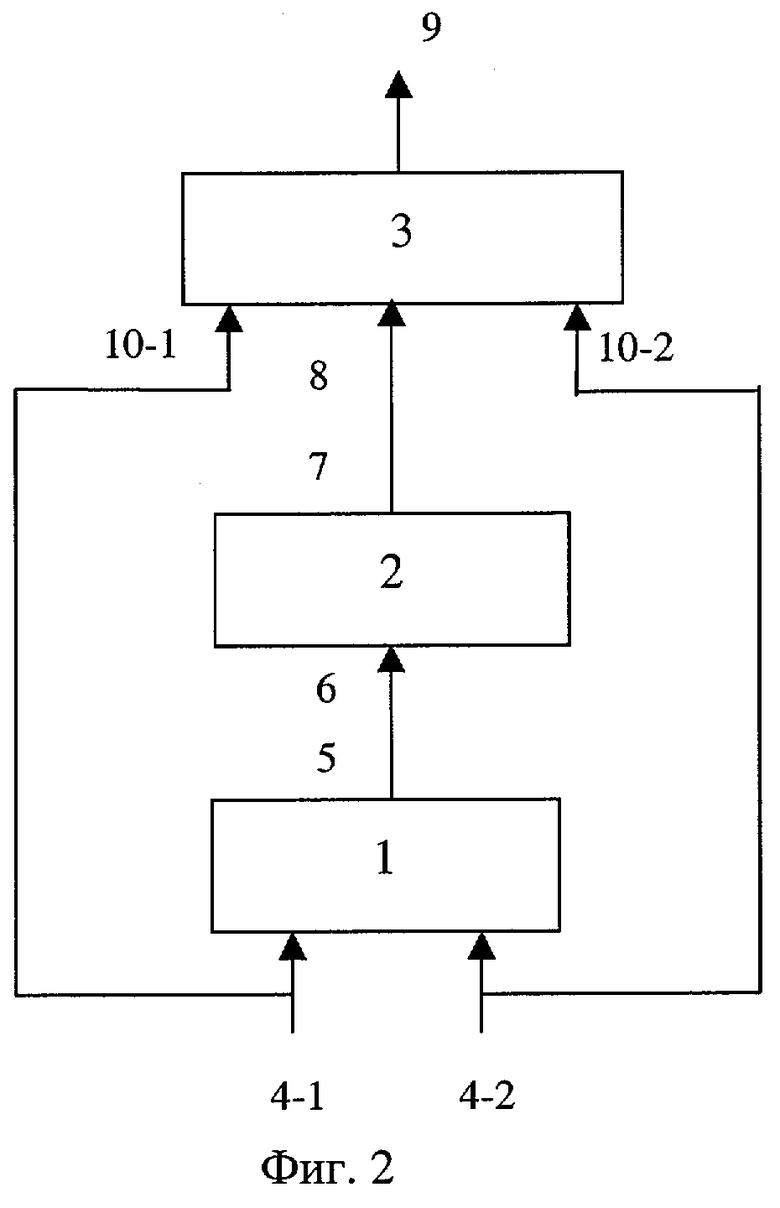

На фиг.1 представлен ближайший аналог, на фиг.2 - функциональная блок-схема предложенного устройства, а на фиг.3 иллюстрация разбиения сравниваемых чисел на k-разрядные группы.

Устройство выбора минимальной или максимальной числовой величины из двух n-разрядных чисел содержит блок 1 преобразования чисел в поразрядные сигналы, блок 2 формирования выбирающих стробов и коммутатор 3 выбора минимального или максимального числа. Входы блока 1 являются входами 4-1 и 4-2 устройства, выход 5 через блок 2 формирования выбирающих стробов, имеющий вход 6 и выход 7, подключен к входу 8 управления коммутатора 3 выбора минимального или максимального числа. Выход коммутатора 3 является выходом 9 устройства, а первый и второй информационные входы 10-1 и 10-2 подключены к соответствующим входам 4-1 и 4-2 устройства.

Блок 1 преобразования чисел в поразрядные сигналы обеспечивает формирование в каждом разряде чисел двух сигналов

и

и  , где i=1, 2,..., n, ai и bi - i-ые разряды n-разрядных двоичных чисел А и В.

, где i=1, 2,..., n, ai и bi - i-ые разряды n-разрядных двоичных чисел А и В.

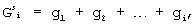

Блок 2 формирования выбирающих стробов для выбора минимального или максимального числа реализует для каждого разряда чисел следующие логические функции:

или для каждой группы по k разрядов:

Коммутатор 3 выбора минимальной или максимальной величины реализует следующие логические функции:

min1=a1b1 - для первого разряда,

- для второго разряда,

- для второго разряда,

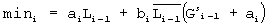

, где i=3, 4, 5,..., n - для 3÷n разрядов,

, где i=3, 4, 5,..., n - для 3÷n разрядов,

max1=a1+b1 - для первого разряда,

- для второго разряда,

- для второго разряда,

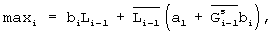

, где i=3, 4, 5, ..., n - для 3-n разрядов,

, где i=3, 4, 5, ..., n - для 3-n разрядов,

или для каждого разряда каждой группы по k разрядов реализует следующие логические функции:

Устройство работает следующим образом.

При поступлении на входы 4-1 и 4-2 устройства, например, двух двоичных чисел А и В блок 1 преобразования чисел в поразрядные сигналы формирует для каждого разряда поразрядные сигналы li и gi, которые поступают на вход 6 блока 2 формирования выбирающих стробов, который формирует для каждого разряда или для каждой группы выбирающие стробы для коммутатора 3 выбора минимального или максимального числа согласно вышеуказанным формулам.

Следует отметить, что выбор старших разрядов минимального или максимального значения осуществляется, не дожидаясь сравнения младших разрядов этих чисел.

Табл.1 представляет собой таблицу истинности для определения двух старших разрядов минимальной и максимальной величин по двум старшим разрядам чисел А и В.

Из табл.1 получаем выражение для min1:

min1=a1b1

Действительно, если старший разряд хотя бы одного из чисел равняется "0", то и старший разряд минимальной величины будет равняться "0"; min1="1", только в случае равенства "1" старших разрядов обоих чисел.

Для второго разряда минимальной величины получаем:

Так как  и

и  , и l1 равно "1", если старший разряд числа А меньше, чем старший разряд числа В, g1 равно "1", если старший разряд числа А больше, чем старший разряд числа В, то выражение для min2 примет вид:

, и l1 равно "1", если старший разряд числа А меньше, чем старший разряд числа В, g1 равно "1", если старший разряд числа А больше, чем старший разряд числа В, то выражение для min2 примет вид:

min2=a2l1+b2g1+a2b2

а это выражение имеет следующий смысл: если старший разряд числа А меньше, чем старший разряд числа В, то в качестве второго разряда минимальной величины выбирается а2. Если старший разряд числа А больше, чем старший разряд числа В, то в качестве второго разряда минимальной величины выбирается b2. Если старший разряд числа А не меньше и не больше, чем старший разряд числа В (то есть, они равны), то второй разряд минимальной величины равен "1", только если вторые разряды обоих чисел равны "1".

Для следующих разрядов минимальной величины по аналогии с предыдущей формулой можно считать, что

Так как выражение в первых скобках равно Li-1, а во вторых скобках - Gi-1, то выражение для mini примет вид:

mini=aiLi-1+biGi-1+aibi,

а после разложения по Li-1 получим:

Так как Gs i-1=g1+g2+...+gi-1, то

т.е. выражение для i-ого разряда минимальной величины примет вид:

Последнее выражение можно реализовать на мультиплексоре с двух направлений, на управляющий вход которого подается сигнал Li-1, а на информационные входы ai и bi(Gs i-1+a1) соответственно.

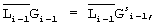

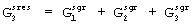

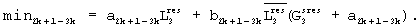

Использование функций Li-1, Gi-1 и Gs i-1 позволяет распараллелить анализ сравниваемых чисел (см. фиг.3). Вычислим для каждой k-разрядной группы групповые функции Li gr, Gi gr и Gi sgr (здесь индекс i обозначает номер группы), при этом функции используют все разряды только своей группы. Так, для первой группы L1 gr=Lk, G1 gr=Gk, G1 sgr=Gs k функции второй группы используют разряды с номера k+1 до 2k, функции третьей группы используют разряды с номера 2k+1 до 3k и так далее. Для третьей группы справедливо следующее выражение для вычисления разрядов минимальной величины:

Так как выражение в первой и второй скобках равно L3 res и G3 res соответственно, то

min2k+1-3k=a2k+1-3kL3 res+b2k+1-3kG3 res+a2k+1-3kb2k+1-3k.

Это выражение можно разложить по L3 res, избавляясь от функции G3 res и заменяя ее более простой функцией  :

:

Полученное выражение также реализуется на мультиплексоре с двух направлений, управляемом сигналом L3 res.

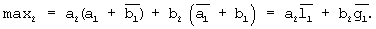

Из табл. 1 следует, что старший разряд максимальной величины равен логической сумме старших разрядов чисел А и В:

max1=a1+b1

Для второго разряда получаем:

Используя вышеприведенные рассуждения, аналогичные для определения разрядов минимальной величины, получим следующие выражения для максимальной величины:

Полученные выражения также реализуется на мультиплексоре с двух направлений.

Следует отметить, что, используя несколько устройств, выполненных согласно предложенному техническому решению, можно реализовать выбор из 3 и более n-разрядных чисел с получением значительно большего выигрыша по времени по сравнению с ближайшми аналогом.

Таким образом, в предложенном изобретении достигается требуемый технический результат.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ МАНТИСС И НОРМАЛИЗАЦИИ РЕЗУЛЬТАТА ПРИ ВЫЧИСЛЕНИЯХ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ | 2003 |

|

RU2242045C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ПОРЯДКА РЕЗУЛЬТАТА СЛОЖЕНИЯ ЧИСЕЛ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ | 2004 |

|

RU2267806C1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| СПОСОБ СУММИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ | 1993 |

|

RU2051407C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для выделения экстремального числа из @ @ -разрядных двоичных чисел | 1982 |

|

SU1070543A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для выбора упорядоченной последовательности данных | 1983 |

|

SU1109738A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

Изобретение относится к области вычислительной техники и может быть использовано при разработке узлов микропроцессора, в частности арифметических устройств, устройств приоритета и тому подобного. Техническим результатом является увеличение быстродействия устройства. Устройство содержит блок преобразования чисел в поразрядные сигналы, блок формирования выбирающих стробов, коммутатор выбора минимального или максимального числа. 3 з.п. ф-лы, 3 ил., 1 табл.

и

и  , где i=1, 2,..., n, аi и bi - i-е разряды двух n-разрядных двоичных чисел А и В, причем a1 и b1 - старшие разряды чисел, a an и bn - младшие разряды чисел.

, где i=1, 2,..., n, аi и bi - i-е разряды двух n-разрядных двоичных чисел А и В, причем a1 и b1 - старшие разряды чисел, a an и bn - младшие разряды чисел.

или для каждой группы по k разрядов следующие логические функции:

min1=a1b1 - для первого разряда,

- для второго разряда,

- для второго разряда,

, где i=3, 4, 5,..., n, - для 3÷n разрядов,

, где i=3, 4, 5,..., n, - для 3÷n разрядов,

max1=a1+b1 - для первого разряда,

- для второго разряда,

- для второго разряда,

где i=3, 4, 5,..., n, - для 3÷n разрядов,

где i=3, 4, 5,..., n, - для 3÷n разрядов,

или для каждого разряда каждой группы по k разрядов реализует следующие логические функции:

- для n/k группы из k разрядов.

- для n/k группы из k разрядов.

| US 5721809 А, 24.02.1998 | |||

| УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ КОДОВ | 1991 |

|

RU2006913C1 |

| Устройство для выбора максимального числа из множества @ двоичных чисел | 1988 |

|

SU1619249A1 |

| Устройство для выбора минимального числа | 1978 |

|

SU681428A1 |

| US 5515306 А, 07.05.1996. | |||

Авторы

Даты

2005-10-10—Публикация

2003-11-28—Подача