Изобретение относится к области импульсной техники и может быть использовано в прецизионных генераторах импульсов.

В прецизионных генераторах импульсов, предназначенных для генерирования последовательностей импульсов с задаваемыми временными параметрами: длительностью, временной задержкой и периодом повторения, возникает проблема фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска. Это означает, что отсчёт любых временных параметров генерируемой последовательности импульсов осуществляется относительно импульса внешнего запуска.

Обычно генераторы импульсов строятся как цифровые устройства, и имеют свой точный тактовый генератор. Если в качестве источника сигнала синхронизации выбирается встроенный источник тактовых импульсов, то временные параметры генерируемых импульсов кратны периоду тактовых импульсов, а погрешность их установки определяется в основном погрешностью периода тактовых импульсов. Однако при синхронизации от внешнего импульса запуска, который никак не привязан к тактовым импульсам самого генератора, погрешность привязки к импульсу внешнего запуска может варьироваться в пределах одного периода тактовых импульсов. Для исключения этой вариативности положение тактового импульса относительно импульса внешнего запуска должно быть одним и тем же, то есть задержка фронта тактового импульса должна быть постоянной относительно фронта импульса внешнего запуска.

Известен способ, реализуемый устройством [RU2256290 C2. Устройство фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска. 05.05.2003г.] в котором реализуется способ фазовой привязки, сущность которого состоит в преобразовании задержки между импульсом внешнего запуска и предшествующим ему тактовым импульсом в пропорциональное напряжение и, далее, с помощью аналого-цифрового преобразователя в цифровой код, сохранении его в виде цифрового кода и последующем обратном преобразовании сохранённого цифрового кода в уровень напряжения с помощью цифро-аналогового преобразователя и, далее, преобразовании напряжения в задержку всех последующих тактовых импульсов. Из задержанных тактовых импульсов формируются последовательности выходных импульсов прецизионного генератора с заданными временными параметрами – задержкой от начала периода, задержкой между парными импульсами, длительностью импульсов, периодом повторения.

Формирование временных параметров (временных интервалов) осуществляется классическими методами с использованием счётчиков тактовых импульсов, регистров, содержащих коды временных параметров, и схем совпадения. Выходные сигналы схем совпадения синхронизируются задержанными тактовыми импульсами. Поэтому медленные изменения их положения относительно импульса внешнего запуска под воздействием дестабилизирующих факторов и дрожание фронтов (джиттер – быстрое изменение положения) приводят к погрешности формирования последовательности импульсов.

Преобразование задержки тактовых импульсов относительно импульса внешнего запуска в напряжение, далее в цифровой код, затем снова в напряжение и, наконец, опять в задержку приводит к накоплению ошибок в длинной цепи преобразований. Кроме того, преобразование временного интервала в напряжение и обратное преобразование осуществляется аналоговыми устройствами на фоне импульсных помех, порождаемых работой цифровых устройств генератора, что также увеличивает погрешность фазовой привязки.

Основными недостатками являются: высокая чувствительность к шумам, создаваемым цифровыми устройствами генератора, длительный процесс фазовой синхронизации, большая систематическая погрешность и остаточный джиттер.

Известен также способ преодоления указанных недостатков, выбираемый в качестве прототипа [RU 2447576 С2. Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска. 29.06.2010 г.], состоящий в прямом преобразовании задержки в цифровой код, сохранении этого кода и последующем преобразовании кода в задержку тактовых импульсов. Преобразование задержки в цифровой код осуществляется сохранением в запоминающем регистре, в момент появления импульса внешнего запуска, выходных сигналов многоотводной линии задержки, по которой распространяется электромагнитная волна тактового импульса. Полученный цифровой код преобразуется дешифратором в сигналы управления мультиплексором, выделяющим лишь один из выходных сигналов многоотводной линии задержки, представляющий собой задержанные тактовые импульсы, привязанные к импульсу внешнего запуска.

Этот способ обеспечивает полный отказ от аналоговых узлов при запоминании и воспроизведении задержки.

Недостатком его является большая задержка фронта первого тактового импульса относительно фронта импульса внешнего запуска, что связано с необходимостью преобразования кода, сохранённого в запоминающем регистре в сигналы управления мультиплексором и ожиданием фронта тактового импульса на выбранном выводе многоотводной линии задержки, который появится не ранее чем через период тактового импульса.

Эта задержка ограничивает максимальную частоту выходных импульсов импульсных генераторов, поскольку следующий импульс внешнего запуска может быть подан лишь после окончания цикла генерирования последовательности выходных импульсов прецизионного генератора, включающего и задержку первого тактового импульса относительно импульса внешнего запуска. Кроме того, большая величина задержки фронта первого тактового импульса относительно импульса внешнего запуска приводит к большей абсолютной погрешности её воспроизведения.

Технической задачей, на решение которой направлен предлагаемый способ, является уменьшение задержки первого тактового импульса относительно импульса внешнего запуска и уменьшение погрешности формирования временных интервалов.

Решение задачи обеспечивается выделением тактового импульса на выводе многоотводной линии задержки, на котором распространяющийся вдоль многоотводной линии задержки тактовый импульс задерживается на минимальный интервал времени по отношению к импульсу внешнего запуска. Выделение осуществляется организацией состязаний выходных импульсов синхронных делителей частоты с одинаковым коэффициентом деления на входе схемы логического суммирования, при этом на вход тактирования синхронных делителей частоты поступают задержанные тактовые импульсы с соответствующих выводов многоотводной линии задержки.

Делители удерживаются в начальном состоянии до прихода внешнего запускающего импульса. Выходной сигнал синхронного делителя частоты, на вход тактирования которого поступил тактовый импульс с минимальной задержкой относительно импульса внешнего запуска, выигрывает состязание и блокирует высоким уровнем своего выходного сигнала фронты выходных сигналов остальных делителей. Таким образом, на выходе схемы логического суммирования (элемента ИЛИ) образуется последовательность тактовых импульсов с точностью до задержки одного сегмента многоотводной линии задержки привязанная к импульсу внешнего запуска. Частота повторения тактовых импульсов на выходе элемента ИЛИ (SCLK) уменьшена в коэффициент деления раз (минимально в 2 раза). Делители работают на частоте исходного тактового сигнала, а точность привязки определяется задержкой одного сегмента многоотводной линии задержки.

Достоинством способа является возможность получения высокой точности фазовой привязки при высокой скорости вхождения в синхронизм, определяемой лишь задержкой срабатывания синхронного делителя частоты (одного триггера) и схемы логического суммирования. Существенно, что требования к рабочей частоте синхронных делителей частоты определяются, прежде всего, частотой тактовых импульсов, а не точностью синхронизации.

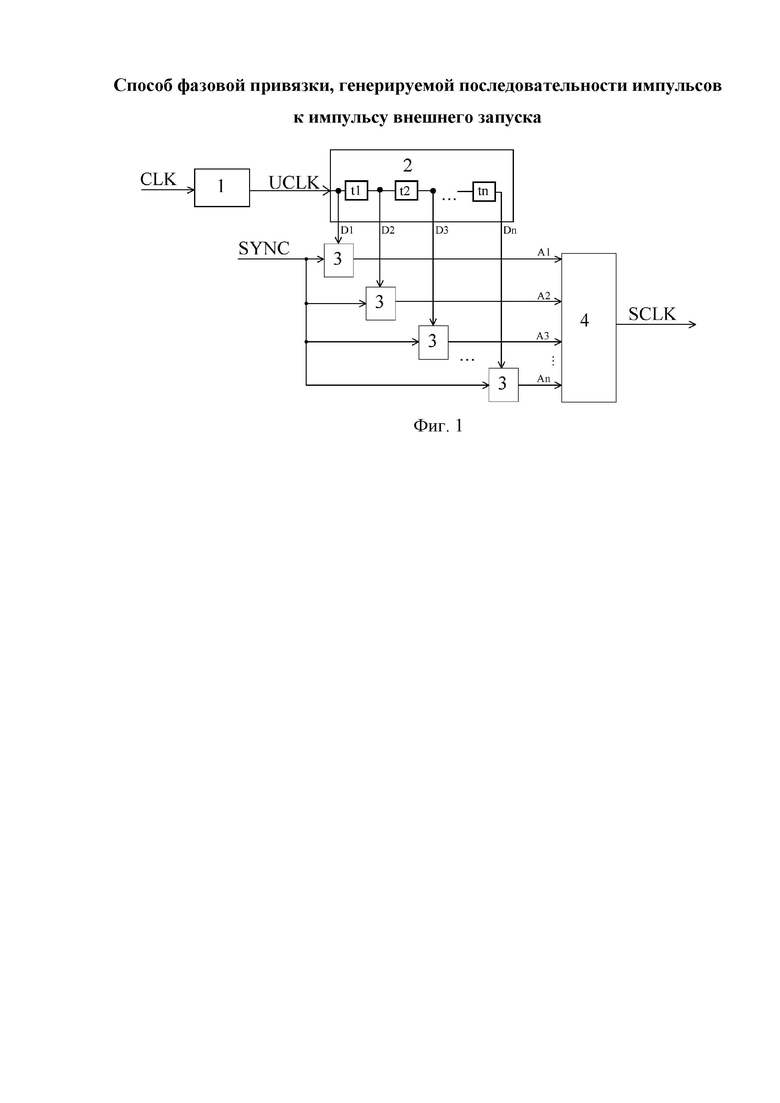

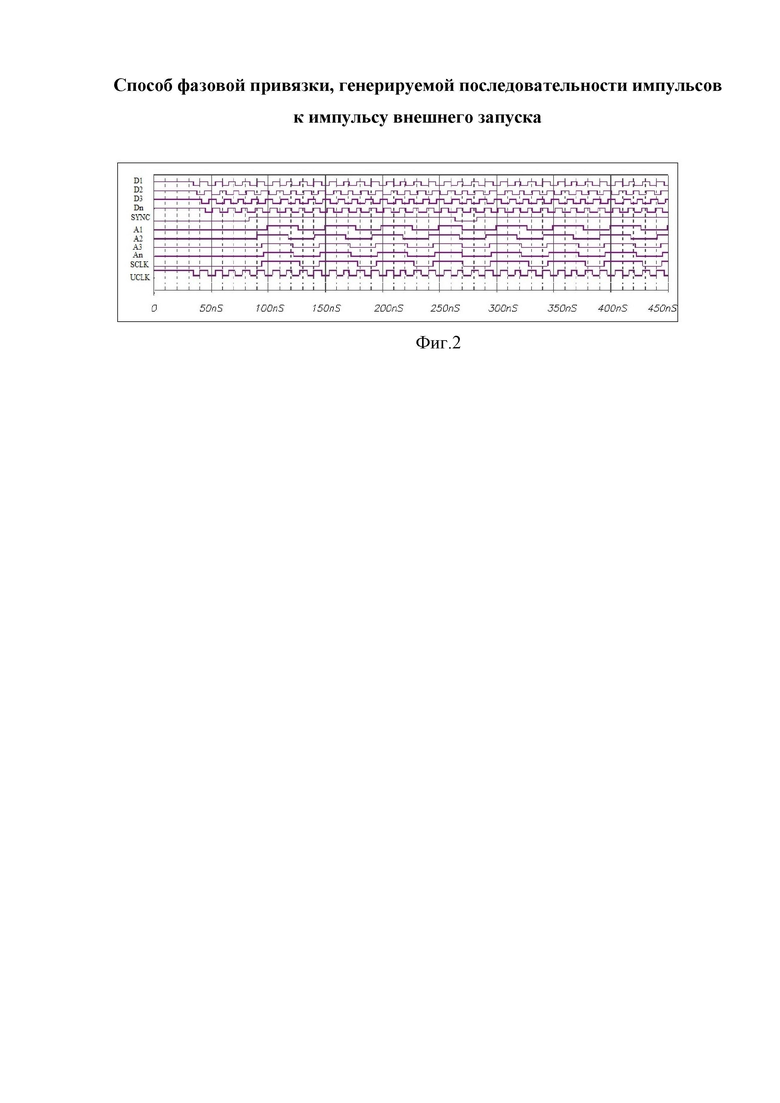

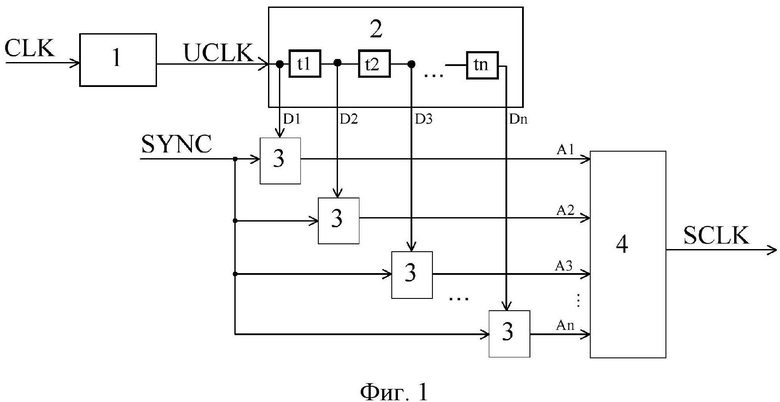

Сущность изобретения поясняется чертежами, где на фиг. 1 показана структурная схема, реализующая способ; на фиг. 2. представлена временная диаграмма, поясняющая структурную схему, реализующую описанный способ.

На фиг. 1: умножитель частоты 1; многоотводная линия задержки 2; синхронный делитель частоты 3; схема логического суммирования 4 (ИЛИ). Тактовые импульсы (CLK) поступают на вход умножителя частоты 1, выход которого соединён с входом многоотводной линии задержки 2. Выводы многоотводной линии задержки 2 соединены с входами тактирования соответствующих синхронных делителей частоты 3, на входы, разрешения счёта, которых подаётся сигнал разрешения счёта (SYNC), а выходы подключены к схеме логического суммирования 4. Тактовые импульсы (SCLK) привязанные к внешнему запускающему импульсу, из которого сформирован сигнал разрешения счёта (SYNC) присутствуют на выходе схемы логического суммирования 4.

Многоотводная линия задержки может быть построена на любой элементной базе, в том числе на логических элементах, представляя собой цепь последовательно соединенных устройств с ответвлениями Di в точках соединения выхода и входа смежных элементов (например, t1 и t2 – на фиг. 1), на основе фазосдвигающих LC-цепей и др. На вход многоотводной линии задержки 2 подаются импульсы (UCLK) с выхода умножителя частоты 1, частота которых в m раз выше частоты тактовых импульсов, а период, соответственно, T/m – в m раз меньше периода тактовых импульсов T. Применение умножителя частоты 1 позволяет сократить количество отводов многоотводной линии задержки 2 и количество делителей частоты 3 в коэффициент умножения m раз.

Возможно построение схемы без умножителя частоты. При этом частота тактовых импульсов на выходе устройства будет определяться коэффициентом деления синхронных делителей частоты и будет ниже частоты входных тактовых импульсов.

Проходя через многоотводную линию задержки 2 с количеством отводов n, импульсы задерживаются на каждом её элементе на фиксированное время ti. Максимальное время задержки равно n*ti. Максимальная задержка многоотводной линии задержки должна удовлетворять условию T/m-n*ti < ti, то есть должна быть немного меньше периода импульсов поступающих на её вход.

В момент поступления сигнала разрешения счёта (SYNC), сформированного из импульса внешнего запуска, на входы разрешения счёта синхронных делителей частоты 3, они срабатывают по фронту каждого импульса (Di), появляющемся на соответствующем отводе многоотводной линии задержки. Их выходные сигналы (Аi) состязаются на входах схемы логического суммирования 4. При этом состязание выигрывает выходной сигнал синхронного делителя частоты (А2 на фиг. 2), на входе тактирования которого появляется фронт импульса (Di) с минимальной задержкой относительно импульса внешнего запуска. Этот выходной сигнал своим высоким уровнем блокирует фронты выходных сигналов (Аi) остальных делителей частоты. При этом блокировка должна продолжаться в течении периода следования импульсов на каждом из выходов многоотводной линии задержки (Di). Это условие обеспечивается при минимальном коэффициенте деления синхронных делителей частоты равном 2. Для снижения требований к быстродействию схемы логического суммирования целесообразно выбирать коэффициент деления делителей частоты 3-4. Это позволяет увеличить длительность низкого уровня (паузы) сигнала на выходе схемы логического суммирования (SCLK). Синхронизированный тактовый сигнал SCLK отстаёт от выходного сигнала делителя частоты выигравшего соревнование (А2 на фиг. 2) на величину задержки схемы логического суммирования.

Синхронные делители частоты удерживаются в начальном состоянии пассивным (низким) уровнем сигнала разрешения счёта (SYNC – фиг. 2), сформированного из импульса внешнего запуска. Перевод его из пассивного состояния в активное (высокий уровень) разрешает работу синхронных делителей частоты по входу тактирования. Первый же импульс, поступающий на вход тактирования синхронного делителя частоты, переводит его вывод в высокий уровень, формируя фронт выходного сигнала.

Сигнал разрешения счёта (SYNC) является внешним по отношению к устройству. Простейший способ формирования этого сигнала реализуется с помощью триггера, устанавливаемого фронтом импульса внешнего запуска и сбрасываемого по окончании цикла формирования импульсной последовательности генератором импульсов. Следующий импульс внешнего запуска приведёт к повторению цикла формирования импульсной последовательности. При этом тактовые импульсы, а, следовательно, и формируемая генератором импульсов импульсная последовательность вновь будет привязана к фронту импульса внешнего запуска.

Фронт выходного сигнала на выходе схемы логического суммирования будет привязан к импульсу внешнего запуска с максимальной ошибкой дискретности равной задержке одного элемента многоотводной линии задержки.

Временная диаграмма устройства фазовой привязки (фиг. 2) приведена для некоторого момента появления импульса разрешения счёта SYNC, сформированного из импульса внешнего запуска.

UCLK – выход схемы умножения; D1, D2, D3, Dn – входной и выходные импульсы многоотводной линии задержки, А1, А2, А3, Аn – выходные сигналы синхронных делителей частоты, SCLK – импульс тактового генератора, привязанный по фазе к импульсу внешнего запуска. Для конкретной реализации джиттер выходного сигнала SCLK не превышает ±2 нс при частоте тактового генератора 20 МГц, 4 отводной линии задержки и коэффициентов умножения умножителя частоты и деления синхронных делителей частоты – 4.

Уменьшение джиттера достигается уменьшением интервала задержки. При этом придётся повысить коэффициент умножения тактовой частоты или при сохранении коэффициента умножения увеличить количество каналов делителей. Первое усложняет умножитель, требует взаимного согласования коэффициентов умножения и коэффициентов деления синхронных делителей частоты или введения дополнительного делителя частоты. Вариант с увеличением количества отводов многоотводной линии задержки масштабируется лучше.

Изобретение относится к области импульсной техники и может быть использовано в прецизионных генераторах импульсов. Технический результат - уменьшение задержки между импульсом внешнего запуска и началом синхронизированной тактовой последовательности, повышение точности фазовой привязки тактовых импульсов опорного генератора к импульсу внешнего запуска. Данный способ заключается в выборе отвода многоотводной линии задержки, на котором фронт распространяющегося вдоль неё тактового сигнала задержан относительно импульса внешнего запуска на минимальное время. Реализация способа осуществляется за счёт организации состязаний однотипных синхронных делителей частоты, на входы синхронизации которых подаются тактовые сигналы с отводов многоотводной линии задержки, а на управляющие входы разрешения синхронных делителей частоты – общий для них разрешающий перепад, сформированный из импульса внешнего запуска. Синхронный делитель частоты, выигравший состязание, формирует фронт тактового импульса. 2 ил.

Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска, состоящий в выделении тактовых импульсов с отвода многоотводной линии задержки, на котором распространяющийся вдоль нее тактовый импульс задерживается на минимальный интервал времени по отношению к импульсу внешнего запуска, отличающийся тем, что тактовые импульсы с каждого вывода многоотводной линии задержки делятся однотипными синхронными делителями частоты, запуск которых разрешается по импульсу внешнего запуска, при этом на входе схемы логического сложения выходных сигналов синхронных делителей частоты тактовые импульсы формируются тем синхронным делителем частоты, на входе тактирования которого появляется фронт импульса с минимальной задержкой относительно импульса внешнего запуска, причем выходной сигнал упомянутого синхронного делителя частоты своим высоким уровнем блокирует фронты выходных сигналов остальных синхронных делителей частоты, при этом блокировка фронтов выходных сигналов остальных синхронных делителей частоты должна продолжаться в течение периода следования импульсов на каждом из выходов многоотводной линии задержки.

| СПОСОБ ФАЗОВОЙ ПРИВЯЗКИ ГЕНЕРИРУЕМОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ К ИМПУЛЬСУ ВНЕШНЕГО ЗАПУСКА | 2010 |

|

RU2447576C2 |

| УСТРОЙСТВО ФАЗОВОЙ ПРИВЯЗКИ ГЕНЕРИРУЕМОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ К ИМПУЛЬСУ ВНЕШНЕГО ЗАПУСКА | 2003 |

|

RU2256290C2 |

| Устройство фазирования тактовых импульсов | 1975 |

|

SU617834A2 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР ИМПУЛЬСНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1990 |

|

RU2042264C1 |

| US 4101838 A1, 18.07.1978 | |||

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Регулируемый трансформатор | 1985 |

|

SU1282228A1 |

Авторы

Даты

2019-07-03—Публикация

2018-03-15—Подача