Изобретение относится к области импульсной техники и может быть использовано в прецизионных генераторах импульсов.

В прецизионных генераторах импульсов, предназначенных для генерирования последовательностей импульсов с задаваемыми временными параметрами: длительностью, временной задержкой и периодом повторения, возникает проблема синхронизации генерируемой последовательности импульсов внешним импульсом. Это означает, что отсчет любых временных параметров генерируемой последовательности импульсов осуществляется относительно внешнего импульса запуска.

Обычно прецизионные генераторы импульсов строятся как цифровые устройства, и имеют свой точный источник тактовых импульсов. Если в качестве источника сигнала синхронизации выбирается встроенный источник тактовых импульсов, то временные параметры генерируемых импульсов кратны периоду тактовых импульсов, а погрешность их установки определяется в основном погрешностью периода тактовых импульсов. Однако при синхронизации от внешнего импульса, который никак не привязан к тактовым импульсам самого генератора, погрешность привязки к внешнему импульсу может варьироваться в пределах одного периода тактовых импульсов. Для исключения этой вариативности положение тактового импульса относительно внешнего импульса синхронизации должно быть одним и тем же, то есть задержка фронта (или спада) тактового импульса должна быть постоянной относительно фронта (спада) внешнего импульса синхронизации.

Известен способ, устраняющий эти недостатки [1. ЕАПО 039506 B1. Способ синхронизации тактовых импульсов внешним импульсом. 30.11.2020 г.].

Способ состоит в сохранении m-разрядного двоичного кода, представляющего совокупность логических уровней сигнала на входе и m-1 начальных отводах многоотводной линии задержки при распространении в ней тактовых импульсов, в запоминающем регистре в момент появления внешнего импульса (его фронта или спада), и последующем сравнении этого кода, с текущим кодом многоотводной линии задержки, на последних m-отводах из (k + m) ее отводов, при этом тактовые импульсы формируются на выходе схемы совпадения (сравнения кодов) в момент совпадения кодов. Положение тактовых импульсов фиксировано относительно внешнего импульса синхронизации с погрешностью не превышающей задержки одного элемента многоотводной линии задержки.

Недостатком этого решения является то, что величина ошибки, определяемая задержкой одного элемента многоотводной линии задержки, ограничена быстродействием схемы совпадения, которая может не успеть сравнить коды на ее входах за время равное задержке одного элемента, т.к. произойдет смена кода на выводах элемента задержки.

Этот недостаток отсутствует при применении для синхронизации способа [2. RU 2693595 С2. Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска. 15.03.2018 г.] состоящего в выделении тактовых импульсов с отвода многоотводной линии задержки, на котором распространяющийся вдоль нее тактовый импульс задерживается на минимальный интервал времени по отношению к импульсу внешнего запуска, за счет одновременно запуска однотипных синхронных делителей частоты тактируемых каждый со своего вывода многоотводной линии задержки, выходные сигналы которых суммируются схемой логического сложения. Фронт синхронизированного тактового импульса формируется синхронным делителем, выигравшим состязание (первым, сработавшим после импульса внешнего запуска).

Недостатком способа является необходимость использования повышенной частоты тактовых импульсов, т.к. частота выходных тактовых импульсов меньше входной. Поэтому требуются счетные триггеры, работающие на повышенной частоте, а их количество не менее двух в каждом делителе. Кроме того, на высоких частотах сложнее обеспечить высокую стабильность кварцевых тактовых генераторов, умножение же частоты прецизионных кварцевых генераторов приводит к увеличению фазовых шумов, что увеличивает джиттер синхронизированных тактовых импульсов.

Требования к быстродействию элементной базы позволяет снизить способ, принимаемый за прототип [3. RU 2785070 С1. Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска. 23.05.2022 г.]. Способ состоит в коммутировании тактовых импульсов с одного из выводов многоотводной линии задержки, на котором распространяющийся вдоль нее тактовый импульс задерживается на некоторый интервал времени по отношению к импульсу внешнего запуска, на соответствующий вход элемента логического суммирования, с выхода которого и снимаются привязанные по фазе тактовые импульсы, при этом положение фронта тактового импульса относительно импульса внешнего запуска сохраняется по этому фронту в триггерах в течение короткого интервала времени, определяемого длительностью сформированного импульса из импульса внешнего запуска, а изменивший свое состояние триггер коммутирует вывод многоотводной линии задержки, на котором фронт тактового импульса отстает на превышающий время переключения триггера интервал, при этом возможность изменения состояния триггеров блокируется до следующего импульса внешнего запуска, сформированный из которого импульс сброса устанавливает триггеры в начальное состояние. При этом способе синхронизации все триггеры работают на частоте тактового генератора, погрешность синхронизации определяется задержкой одного элемента многоотводной линии задержки, а для повышения точности синхронизации нет необходимости в повышении тактовой частоты генератора, что дополнительно позволяет уменьшить величину джиттера.

Недостатком этого способа является необходимость применения многоотводной линии задержки с большим количеством отводов, такого же большого количества триггеров, и коммутатора с большим количеством входов.

Технической задачей, на решение которой направлен предлагаемый способ, является резкое уменьшение объема оборудования при сохранении или повышении точности привязки тактовых импульсов к импульсу внешнего запуска.

Решение обеспечивается многошаговой (минимально двухшаговой) синхронизацией тактовых импульсов. Импульс сброса, сформированный из внешнего импульса синхронизации, сбрасывает триггеры, запоминающие состояние многоотводных линий задержки (первой - с суммарной задержкой равной периоду тактовых импульсов и второй - с суммарной задержкой немного превышающей задержку одного элемента первой многоотводной задержки), а задержанный по отношению к импульсу сброса первый импульс разрешения записи разрешает фронту тактового импульса, распространяющегося в первой многоотводной линии задержки, установить один из триггеров первой группы триггеров, входами синхронизации подключенными к выводам первой многоотводной линии задержки, при этом выходные сигналы этих триггеров управляют первым коммутатором, коммутирующим задержанный тактовый импульс с вывода первой многоотводной линии задержки на вход второй многоотводной линии задержки. Второй, задержанный по отношению к внешнему импульсу, импульс разрешения записи позволяет фронту тактового импульса распространяющегося по второй многоотводной линии задержки установить один из триггеров второй группы триггеров, которые своими выходами управляют вторым коммутатором, выходной импульс которого синхронизирован относительно внешнего импульса с погрешностью равной T/(pq), где T - период тактовых импульсов, а p, q - количество отводов первой и второй многоотводных линий задержки, соответственно). Состояния триггеров каждой из групп остается неизменным до прихода следующего внешнего импульса.

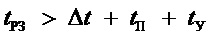

Импульсы разрешения записи в триггеры имеют длительность не менее  , где Δt = Δt1 или Δt = Δt2 - задержка одной секции первой, или второй многоотводной линии задержки, соответственно, tП, tУ - время предустановки и удержания данных относительно фронта импульса на входе синхронизации триггера (параметры триггера), а задержка второго импульса разрешения записи относительно внешнего импульса выбирается равной

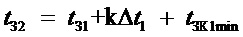

, где Δt = Δt1 или Δt = Δt2 - задержка одной секции первой, или второй многоотводной линии задержки, соответственно, tП, tУ - время предустановки и удержания данных относительно фронта импульса на входе синхронизации триггера (параметры триггера), а задержка второго импульса разрешения записи относительно внешнего импульса выбирается равной  , где tЗ1 - задержка первого импульса разрешения записи относительно внешнего импульса, kΔt - задержка между управляющим и коммутируемым сигналом на управляющем и сигнальном входах первого коммутатора (k - целое число), tЗК1min - минимальная в условиях эксплуатации задержка первого коммутатора.

, где tЗ1 - задержка первого импульса разрешения записи относительно внешнего импульса, kΔt - задержка между управляющим и коммутируемым сигналом на управляющем и сигнальном входах первого коммутатора (k - целое число), tЗК1min - минимальная в условиях эксплуатации задержка первого коммутатора.

В зависимости от положения внешнего импульса относительно фронта тактовых импульсов, в активное состояние может перейти более чем один триггер, что приведет к увеличению длительности тактового импульса, но не изменит положение фронта тактового импульса на выходе (его фронт по-прежнему будет синхронизирован по фазе). Выбор сигнального вывода многоотводной линии задержки (и первой и второй) осуществляется так, чтобы к моменту появления на нем фронта тактового импульса соответствующий канал коммутатора уже был открыт, что исключает влияние времени задержки установления триггера на величину джиттера тактового импульса. Поскольку тактовые импульсы распространяются по многоотводным линиям задержки непрерывно, то триггеры обеих групп не должны переключаться вне интервала разрешения записи. Для JK-триггеров с инверсным входом K это достигается фиксированием его в высоком состоянии. При высоком уровне разрешения записи триггер устанавливается, поскольку на его входе J присутствует высокий уровень, а при низком уровне на входе J - находится в режиме хранения. Триггеры, на входы которых во время разрешения записи не пришел фронт тактового импульса с соответствующего вывода многоотводной линии задержки, в режиме хранения сохраняют низкий уровень, а соответствующий им канал коммутатора закрыт для прохождения тактовых импульсов.

С приходом очередного внешнего импульса все триггеры сбрасываются сформированным из него импульсом сброса, а коммутаторы закрываются, и процесс синхронизации повторяется.

Если период тактовых импульсов равен Т, а ошибка фазовой синхронизации тактовых импульсов не должна превышать Δt, то количество выводов многоотводной линии задержки в прототипе с учетом входного вывода m = T/Δt. При этом количество триггеров для сохранения положения фронта тактового импульса в момент прихода внешнего импульса также равно m.

В предлагаемом решении следует использовать первую многоотводную линию задержки с количеством выводов p. При этом задержка одной секции первой многоотводной линии задержки Δt1 = T/p. Вторая многоотводная линия задержки должна иметь количество выводов q, а задержка одной ее секции выбирается Δt2 = Δt = Δt1/q = T/(pq). Здесь p - полное количество выводов первой многоотводной линии задержки включая вход, при этом секций задержки на единицу меньше числа выводов. Интервал между задержанным импульсом на последнем выводе первой многоотводной линии задержки и тактовым импульсом следующего периода также равен Δt, т. е. имеет место циклический порядок. Т.к. для второй линии задержки циклически порядок отсутствует (длительность тактового импульса много больше полной задержки второй многоотводной линии задержки), то для нее q - это количество отводов без учета первого. Т.е. суммарная задержка второй многоотводной линии задержки должна гарантировано перекрывать задержку одной секции первой многоотводной линии задержки. Количество отводов второй многоотводной линии задержки может быть на один два больше расчетного, но количество триггеров равно расчетному. Это определяется необходимостью перекрытия суммарной задержкой второй многоотводной линии задержки одного сегмента первой многоотводной линии задержки, т. к. необходимо иметь дополнительную задержку тактовых импульсов на сигнальном входе второго коммутатора превышающую время установления триггера.

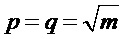

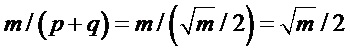

Так как m = pq, то минимум оборудования (количество триггеров и входов коммутаторов) определяется суммой p + q и достигается при  . В этом случае выигрыш в оборудовании по сравнению с прототипом составляет примерно

. В этом случае выигрыш в оборудовании по сравнению с прототипом составляет примерно  .

.

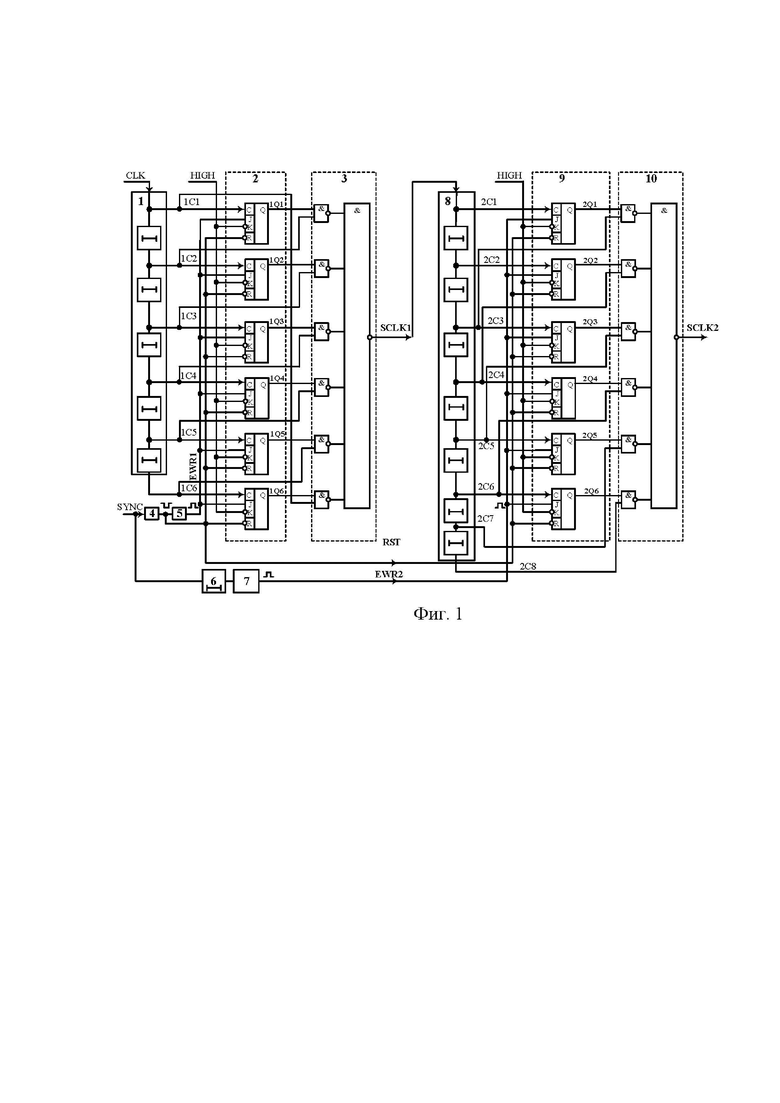

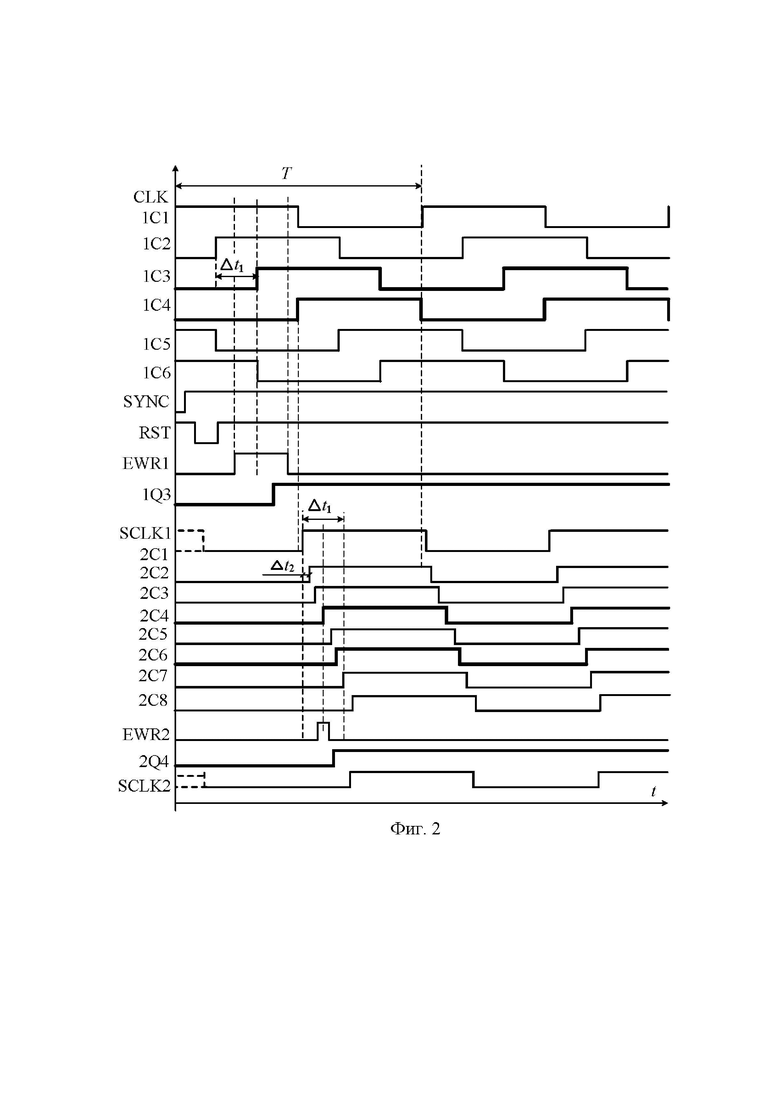

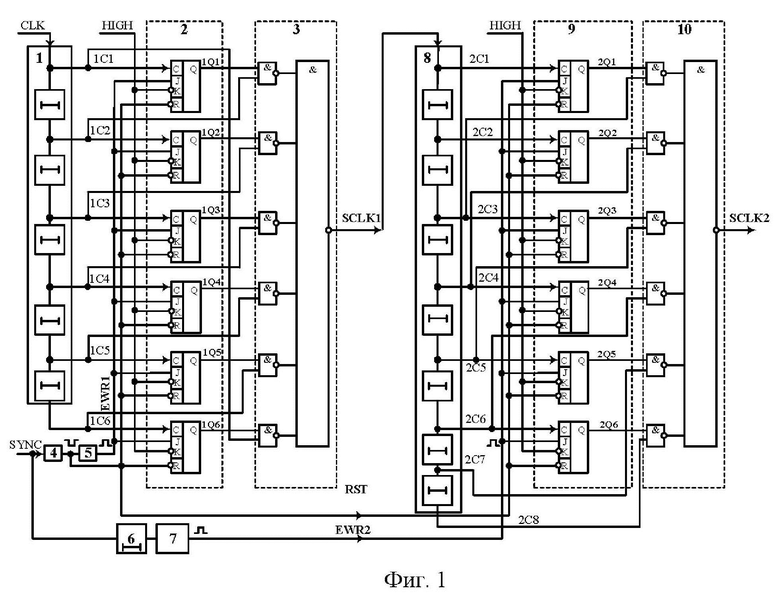

Предлагаемое решение поясняется: фиг. 1 - функциональная схема устройства, реализующего способ фазовой привязки тактовых импульсов к внешнему импульсу; фиг. 2 - временная диаграмма.

Способ реализуется устройством, приведенным на фигуре 1 и состоящим из: многоотводной линии задержки 1; синхронизируемых фронтом JK-триггеров 2; коммутатора 3 из логических элементов «И-НЕ»; одновибраторов 4, 5 и 7; элемента задержки 6; многоотводной линии задержки 8; JK-триггеров 9; коммутатора 10.

Тактовые импульсы «CLK» поступают на вход многоотводной линии задержки 1. Выводы многоотводной линии задержки 1 соединены с входами синхронизации C соответствующих триггеров 2 и сигнальными входами коммутатора 3 (вторыми входами логических элементов «И-НЕ») со сдвигом по отношению к управляющим входам коммутатора 3, к которым присоединены соответствующие выходы триггеров 2 (первыми входами логических схем «И-НЕ»). На вход одновибратора 4 поступает внешний импульс «SYNC», а выход одновибратора 4 соединен со входами сброса R триггеров 2, 9 и входом одновибратора 5 (линия «RST»), выход которого присоединен ко входам J триггеров 2 (линия «»EWR1), а на инверсные входы K которых подается сигнал высокого уровня «HIGH». Вход элемента задержки 6 присоединен ко входу одновибратора 4, а выход ко входу одновибратора 7, выход которого соединен со входами J триггеров 9 (линия разрешения записи «EWR2»).

Выход коммутатора 3 соединен со входом многоотводной линии задержки 8 (линия «SCLK1»), выходы которой соединены с соответствующими входами С триггеров 9 и сигнальными входами коммутатора 10 со сдвигом по отношению к управляющим входам коммутатора 10, к которым присоединены соответствующие выходы триггеров 9, инверсные входы K которых подключены к высокому уровню «HIGH». На выходе коммутатора 10 присутствуют синхронизированные по фазе тактовые импульсы «SCLK2».

Коммутаторы 1 и 10 построены на логических элементах «И-НЕ», при этом двухвходовые элементы «И-НЕ» образуют ключи с инверсией выходных сигналов, выходы которых присоединены к многовходовому элементу «И-НЕ», образующему схему сложения для кодированных в инверсной логике сигналов.

Устройство работает следующим образом. На вход многоотводной линии задержки 1 поступают тактовые импульсы CLK. Фронт очередного импульса появляется поочередно на первом выводе многоотводной линии задержки С1, затем на втором - С2 и т.д. С приходом импульса внешнего запуска «SYNC» одновибратор 4 формирует отрицательный импульс фиксированной длительности, достаточной для сброса триггеров 2 и 9 по инверсному входу R (начальное состояние). Низкий уровень с выходов триггеров 2 поступает на управляющие входы коммутатора 3 (первые входы двухвходовых логических элементов «И-НЕ»), а с выходов триггеров 9 на управляющие входы коммутатора 10, при этом на выходах коммутаторов 3 и 10 устанавливается уровень логического нуля. По завершении импульса одновибратора 4 запускается одновибратор 5 и формирует короткий импульс разрешения записи на входах J триггеров 2.

Один или два триггера из триггеров 2, на вход синхронизации (С) которых во время интервала разрешения записи tРЗ1 поступает фронт тактового импульса с выхода многоотводной линии задержки 1, устанавливаются в состояние логической единицы. При этом высокий уровень с их выходов поступает на соответствующие управляющие входы коммутатора 2, а в момент появления фронта тактового импульса на соответствующих выводах многовыводной линии задержки 1 (на фиг.1 это вывод следующий за выводом сформировавшим управляющий сигнал) соответствующие каналы коммутатора 2 уже открыты и синхронизированный тактовый импульс «SCLK1» появится на выходе с коммутатора 2 с некоторой задержкой.

По окончании импульса разрешения записи с выхода одновибратора 5 все триггеры 2 будут переведены в режим хранения и тактовые импульсы будут проходить на выход коммутатора с тех же выводов многоотводной линии задержки 1 до прихода следующего внешнего импульса.

Полная задержка многоотводной линии задержки 1 должна быть примерно равна T(1-1/p) = T(1-1/  ), при этом управляющие сигналы с вывода Q6 триггеров 2 коммутируют на выход коммутатора 3 сигнал с выводов 1С1 многоотводной линии задержки 1 (для сигналов на выходах многоотводной линии задержки 1 имеет место циклический порядок, и следующий тактовый импульс на выводе 1С1 задержан относительно тактового импульса на вывода 1С6 на длительность задержки ее сегмента Δt1).

), при этом управляющие сигналы с вывода Q6 триггеров 2 коммутируют на выход коммутатора 3 сигнал с выводов 1С1 многоотводной линии задержки 1 (для сигналов на выходах многоотводной линии задержки 1 имеет место циклический порядок, и следующий тактовый импульс на выводе 1С1 задержан относительно тактового импульса на вывода 1С6 на длительность задержки ее сегмента Δt1).

Выходной сигнал коммутатора 3 «SCLK» поступает на вход многоотводной линии 8 и, распространяясь по ней, фронтом тактового импульса сохраняет положение фронта в триггерах 9 в течении интервал импульса разрешения записи, сформированного одновибратором 7 из задержанного элементом задержки 6 внешнего импульса. Управляющий сигнал с одного из триггеров 9 открывает соответствующий канал коммутатора 10, на выход которого поступают задержанные и синхронизированные по фазе с погрешностью Δt тактовые импульсы «SCLK2». Т. к. для распространяющегося по многоотводной линии 8 тактового импульса в момент синхронизации циклический порядок отсутствует (длительность тактового импульса во много раз больше суммарной задержки многоотводной линии 8), для дополнительной задержки линия должна иметь дополнительные сегменты (на фиг. 1 многоотводная линия задержки 8 имеет два дополнительных сегмента, т.к. задержка установки триггера может быть больше задержки ее сегмента).

Временная диаграмма устройства (фиг. 2) иллюстрирует способ фазовой привязки. На диаграмме: 1С1 … 1С6, 2С1 … 2С8 - выходные сигналы многоотводных линий задержки 1 и 8 соответственно; 1Q1 … 1Q6, 2Q1 …2Q6 - выходные сигналы триггеров 2 и 9 соответственно; SYNC -внешний импульс; RST - импульс сброса, EWR1 - импульс разрешения записи в триггеры 2; EWR2 - импульс разрешения записи в триггеры 9; CLK - тактовые импульсы; SCLK1 - синхронизированные тактовые импульсы на выходе коммутатора 3; SCLK2 - синхронизированные тактовые импульсы на выходе коммутатора 10; Т - период тактовых импульсов; Δt1 - задержка одной секции многоотводной линии 1; Δt2 - задержка одной секции многоотводной линии 2

До прихода внешнего импульса SYNC на выходах коммутаторов 3 и 10 присутствуют синхронизированные с погрешностью Δt1 и Δt2 тактовые импульсы SCLK1 и SCLK2, соответственно, потому состояние этих сигналов в момент прихода внешнего импульса SYNC неопределенно. Сформированным из SYNC одновибратором 4 сигналом сброса RST все триггеры сбрасываются (на их выходах логический нуль) и коммутаторы 3 и 10 не пропускают тактовые импульсы. Во время высокого уровня сигнала разрешения записи EWR1 фронт тактового сигнала 1С3 устанавливает высокий уровень сигнала на выходе 1Q3 триггеров 2, разрешая прохождение на выход коммутатора 3 тактового импульса с выхода 1С4 многоотводной линии задержки 1. Эти сигналы (1С3, 1Q3, 1С4) выделены на диаграмме.

Синхронизированный тактовый импульс с выхода коммутатора 3 поступает на вход многоотводной линии задержки 8 и распространяется по ней. В интервале действия высокого уровня EWR2 фронт тактового импульса с выхода 2С4 многоотводной линии задержки 8 устанавливает высокий уровень на выходе 2Q4 триггеров 9, разрешает этим передачу тактового импульса с выхода 2С6 на выход коммутатора 9 (выходной сигнал SCLK2). На диаграмме также выделены сигналы 2С4, 2Q4 и 2С6 определяющие синхронизированные по фазе тактовые импульсы SCLK2.

Таким образом, предложенный способ фазовой синхронизации тактовых импульсов обеспечивает высокую точность синхронизации при небольших аппаратных затратах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска | 2022 |

|

RU2785070C1 |

| Способ фазовой синхронизации тактовых импульсов внешним импульсом запуска | 2024 |

|

RU2824042C1 |

| Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска | 2018 |

|

RU2693595C1 |

| Способ синхронизации тактовых импульсов внешним импульсом | 2019 |

|

RU2721231C1 |

| СПОСОБ ФАЗОВОЙ ПРИВЯЗКИ ГЕНЕРИРУЕМОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ К ИМПУЛЬСУ ВНЕШНЕГО ЗАПУСКА | 2010 |

|

RU2447576C2 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

| Устройство задержки импульсов | 1982 |

|

SU1112543A1 |

| СПОСОБ ФОРМИРОВАНИЯ ПАЧЕК ИМПУЛЬСОВ | 1995 |

|

RU2098919C1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство для имитации технической системы конвейерного типа | 1988 |

|

SU1522159A1 |

Изобретение относится к области импульсной техники и может быть использовано в прецизионных генераторах импульсов. Техническим результатом изобретения является обеспечение высокой точности синхронизации при небольших аппаратных затратах. Способ фазовой синхронизации тактовых импульсов внешним импульсом дополнительно включает запоминание текущего положения фронта тактового импульса, распространяющегося в первой многоотводной линии задержки в триггерах первой группы в момент прихода внешнего импульса синхронизации. При этом активный триггер, сохранивший положение фронта тактового импульса, коммутирует тактовый импульс с одного из выводов первой многоотводной линии задержки на вход второй многоотводной линии задержки. Положение фронта распространяющегося по ней тактового импульса сохраняется в триггерах второй группы в момент прихода задержанного внешнего импульса синхронизации, а активный триггер этой группы определяет, с какого вывода второй многоотводной линии задержки будет передаваться синхронизированная тактовая последовательность на выход. 2 ил.

Способ фазовой синхронизации тактовых импульсов внешним импульсом, состоящий в коммутировании тактовых импульсов с одного из выводов первой многоотводной линии задержки, на котором распространяющийся вдоль неё тактовый импульс задерживается на минимальный интервал времени по отношению к внешнему импульсу, на соответствующий вход первого коммутатора, с выхода которого снимаются синхронизированные по фазе тактовые импульсы, при этом положение фронта тактового импульса относительно внешнего импульса сохраняется по этому фронту в триггерах первой группы в течение короткого интервала времени, определяемого длительностью сформированного импульса из импульса внешнего запуска, а изменивший своё состояние триггер первой группы определяет вывод первой многоотводной линии задержки, на котором фронт тактового импульса отстаёт на превышающий время переключения триггера интервал, отличающийся тем, что с целью сокращения объёма оборудования и повышения точности синхронизации тактовый импульс с выхода первого коммутатора подаётся на вход второй многоотводной линии задержки с суммарной задержкой не менее задержки одной секции первой многоотводной линии задержки, а синхронизация тактовых импульсов осуществляется относительно второго короткого импульса, сформированного из внешнего импульса, задержанного на точно фиксированный интервал времени, сохранением положения фронта триггером второй группы управляющим вторым коммутатором, на выход которого поступает тактовый импульс с вывода второй многоотводной линии задержки, на котором его фронт отстаёт на превышающий время переключения триггера интервал, при этом возможность изменения состояния всех триггеров блокируется до следующего внешнего импульса, сформированный из которого импульс сброса устанавливает триггеры в начальное состояние.

| Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска | 2022 |

|

RU2785070C1 |

| ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2267221C1 |

| МОИСЕЕВ М.И | |||

| Реализация внешнего запуска в прецизионных генераторах прямоугольных импульсов // Известия Юго-Западного государственного университета | |||

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| Способ местного предохранения металлических изделий против цементации | 1934 |

|

SU39506A1 |

| Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска | 2018 |

|

RU2693595C1 |

| Оптическая система для съемочного кинематографического аппарата | 1929 |

|

SU16515A1 |

| МАГНИТНЫЙ БАРАБАННЫЙ СЕПАРАТОР | 0 |

|

SU185779A1 |

| US | |||

Авторы

Даты

2024-07-05—Публикация

2024-01-24—Подача