Изобретение относится к области импульсной техники и может быть использовано в прецизионных генераторах импульсов.

В прецизионных генераторах импульсов, предназначенных для генерирования последовательностей импульсов с задаваемыми временными параметрами: длительностью, временной задержкой и периодом повторения, возникает проблема синхронизации генерируемой последовательности импульсов внешним импульсом. Это означает, что отсчёт любых временных параметров генерируемой последовательности импульсов осуществляется относительно внешнего импульса запуска.

Обычно прецизионные генераторы импульсов строятся как цифровые устройства, и имеют свой точный источник тактовых импульсов. Если в качестве источника сигнала синхронизации выбирается встроенный источник тактовых импульсов, то временные параметры генерируемых импульсов кратны периоду тактовых импульсов, а погрешность их установки определяется в основном погрешностью периода тактовых импульсов. Однако при синхронизации от внешнего импульса, который никак не привязан к тактовым импульсам самого генератора, погрешность привязки к внешнему импульсу может варьироваться в пределах одного периода тактовых импульсов. Для исключения этой вариативности положение тактового импульса относительно внешнего импульса синхронизации должно быть одним и тем же, то есть задержка фронта (или спада) тактового импульса должна быть постоянной относительно фронта (спада) внешнего импульса синхронизации.

Известен способ, решающий эту задачу [1. ЕАПО 039506 B1. Способ синхронизации тактовых импульсов внешним импульсом. 30.11.2020 г.].

Способ состоит в сохранении m-разрядного двоичного кода, представляющего совокупность логических уровней сигнала на входе и m-1 начальных отводах многоотводной линии задержки при распространении в ней тактовых импульсов, в запоминающем регистре в момент появления внешнего импульса (его фронта или спада), и последующем сравнении этого кода, с текущим кодом многоотводной линии задержки, на последних m-отводах из (k+m)её отводов, при этом тактовые импульсы формируются на выходе схемы совпадения (сравнения кодов) в момент совпадения кодов. Положение тактовых импульсов фиксировано относительно внешнего импульса синхронизации с погрешностью, не превышающей задержки одного элемента многоотводной линии задержки.

Недостатком этого решения является то, что величина ошибки, определяемая задержкой одного элемента многоотводной линии задержки, ограничена быстродействием схемы совпадения, которая может не успеть сравнить коды на её входах за время равное задержке одного элемента, т.к. произойдёт смена кода на выводах элемента задержки.

Этот недостаток отсутствует при применении для синхронизации способа [2. RU 2693595 С2. Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска. 15.03.2018 г.] состоящего в выделении тактовых импульсов с отвода многоотводной линии задержки, на котором распространяющийся вдоль неё тактовый импульс задерживается на минимальный интервал времени по отношению к импульсу внешнего запуска, за счёт одновременно запуска однотипных синхронных делителей частоты тактируемых каждый со своего вывода многоотводной линии задержки, выходные сигналы которых суммируются схемой логического сложения. Фронт синхронизированного тактового импульса формируется синхронным делителем, выигравшим состязание (первым, сработавшим после импульса внешнего запуска).

Недостатком способа является необходимость использования повышенной частоты тактовых импульсов, т.к. частота выходных тактовых импульсов меньше входной. Поэтому требуются счётные триггеры, работающие на повышенной частоте, а их количество не менее двух в каждом делителе. Кроме того, на высоких частотах сложнее обеспечить высокую стабильность кварцевых тактовых генераторов, умножение же частоты прецизионных кварцевых генераторов приводит к увеличению фазовых шумов, что увеличивает джиттер синхронизированных тактовых импульсов.

Требования к быстродействию элементной базы позволяет снизить способ, принимаемый за прототип [3. RU2785070 С1. Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска. 23.05.2022 г.]. Способ состоит в коммутировании тактовых импульсов с одного из выводов многоотводной линии задержки, на котором распространяющийся вдоль неё тактовый импульс задерживается на некоторый интервал времени по отношению к импульсу внешнего запуска, на соответствующий вход элемента логического суммирования, с выхода которого и снимаются привязанные по фазе тактовые импульсы, при этом положение фронта тактового импульса относительно импульса внешнего запуска сохраняется по этому фронту в триггерах в течение короткого интервала времени, определяемого длительностью сформированного импульса из импульса внешнего запуска, а изменивший своё состояние триггер коммутирует вывод многоотводной линии задержки, на котором фронт тактового импульса отстаёт на превышающий время переключения триггера интервал, при этом возможность изменения состояния триггеров блокируется до следующего импульса внешнего запуска, сформированный из которого импульс сброса устанавливает триггеры в начальное состояние. При этом способе синхронизации все триггеры работают на частоте тактового генератора, погрешность синхронизации определяется задержкой одного элемента многоотводной линии задержки, а для повышения точности синхронизации нет необходимости в повышении тактовой частоты генератора, что дополнительно позволяет уменьшить величину джиттера.

Недостатком этого способа является увеличение времени необходимого для фазовой синхронизации тактовых импульсов на величину задержки и длительности задержанного импульса внешнего запуска, что приводит к снижению максимальной частоты следования импульсов внешнего запуска, и снижение точности синхронизации из-за неэффективности уменьшения интервала дискретизации, ограниченного величиной нестабильности задержки задержанного импульса внешнего запуска.

Технической задачей, на решение которой направлен предлагаемый способ, является повышении рабочей частоты в режиме внешнего запуска за счёт сокращения времени синхронизации и повышение точности фазовой синхронизации.

Решение задачи обеспечивается запоминанием текущего положения фронта тактового импульса, распространяющегося в многоотводной линии задержки в одном из триггеров, подключенных входами синхронизации к выводам многоотводной линии задержки, при поступлении импульса внешнего запуска. При этом выходные сигналы триггеров, изменивших своё состояние по фронту тактового импульса с соответствующего вывода многоотводной линии задержки, прямыми выходами подключёнными ко входам элемента И-НЕ блокируют его выходным сигналом последующее изменение состояния триггеров, а инверсными выходами управляют коммутатором, коммутирующим тактовые импульсы с нескольких последующих выводов многоотводной линии задержки на выход, причём положение фронта тактового импульса определяется первым триггером в цепочке триггеров изменивших своё состояние.

Низкий уровень импульса внешнего запуска устанавливает триггеры (состояние логической единицы), а управляющие сигналы низкого уровня, поступающие на вход коммутатора с инверсных выходов триггеров, закрывают все каналы коммутатора, препятствуя прохождению тактовых импульсов на его выход. При этом выходные сигналы высокого уровня с прямых выходов триггеров через логический элемент И-НЕ разрешают переключение триггеров в низкий уровень при поступлении на входы синхронизации фронта, распространяющегося по многоотводной линии задержки тактового импульса.

По фронту импульса внешнего запуска разрешается работа триггеров в синхронном режиме и один из триггеров фронтом распространяющегося тактового импульса с некоторой задержкой установится в состояние логического нуля и заблокирует через элемент И-НЕ возможность последующего изменения состояния всех триггеров по фронту тактового импульса на их входах синхронизации, а высокий уровень управляющего сигнала с инверсного выхода этого триггера разрешит прохождение тактового импульса с соответствующего вывода многоотводной линии задержки на выход коммутатора. Из-за задержки сигнала блокировки несколько последующих триггеров успеют переключиться в состояние логического нуля и их выходные сигналы высокого уровня с инверсных выходов разрешат прохождение тактовых импульсов на выход коммутатора. При этом положение фронтов тактовых импульсов будет определяться первым из триггеров в цепочке триггеров, установившихся в состояние логического нуля.

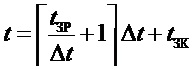

Первый импульс синхронизированной тактовой последовательности на выходе коммутатора задержан относительно фронта импульса внешнего запуска на

,

,

где tЗР – время задержки распространения сигнала от входа синхронизации триггера до выхода, Δt – задержка одной секции многоотводной линии задержки (интервал дискретизации), tЗК – задержка коммутатора. Единица в этом выражении учитывает тот факт, что импульс внешнего запуска может поступить на вход устройства непосредственно после появления фронта тактового импульса на одном из выводов многоотводной линии задержки и фронт на следующем её выводе появится только через Δt.

Минимальный период следования импульсов внешнего запуска также ограничен минимально допустимой длительностью импульса установки триггеров по входу асинхронной установки.

Таким образом, в сравнении с прототипом время задержки и длительность задержанного импульса внешнего запуска исключаются из полного времени синхронизации, что позволяет повысить максимальную частоту следования импульсов внешнего запуска. Выбор шага дискретизации равного задержке сегмента Δt многоотводной линии задержки ограничен лишь разбросом времени задержки tЗР применяемых триггеров.

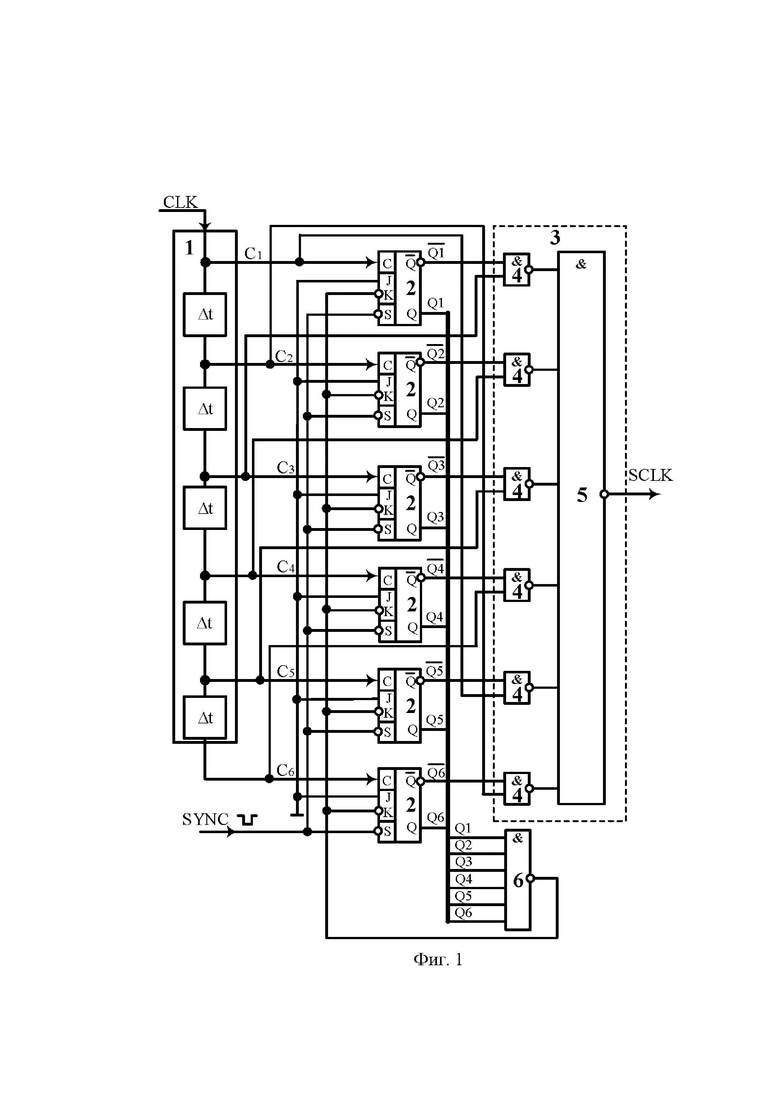

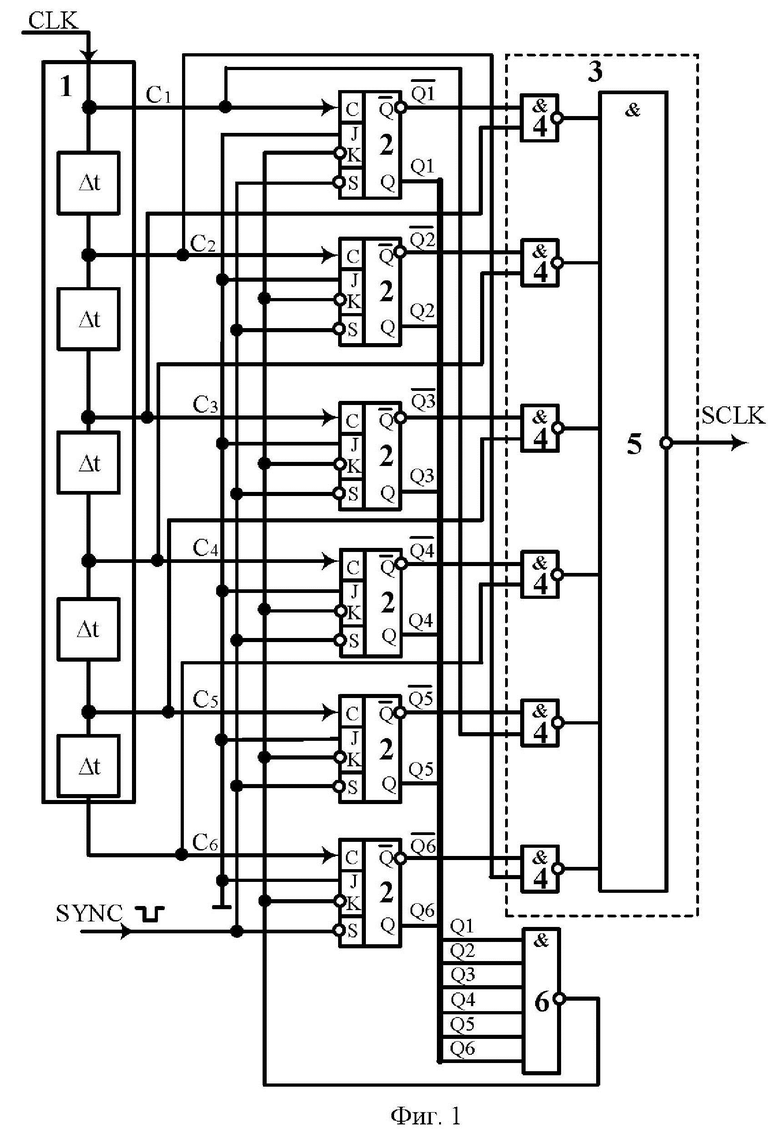

Предлагаемое решение поясняется: фиг. 1 – функциональная схема устройства, реализующего способ фазовой привязки тактовых импульсов к внешнему импульсу; фиг. 2 – временная диаграмма.

Способ реализуется устройством, приведенным на фигуре 1 и состоящим из: многоотводной линии задержки 1; синхронизируемых фронтом  -триггеров 2; коммутатора 3 из двухвходовых логических элементов «И-НЕ» 4 и многовходового логического элемента «И-НЕ» 5; многовходового логического элемента «И-НЕ» 6.

-триггеров 2; коммутатора 3 из двухвходовых логических элементов «И-НЕ» 4 и многовходового логического элемента «И-НЕ» 5; многовходового логического элемента «И-НЕ» 6.

Тактовые импульсы «CLK» поступают на вход многоотводной линии задержки 1. Выводы многоотводной линии задержки 1 соединены с входами синхронизации C соответствующих триггеров 2 и сигнальными входами коммутатора 3 (вторыми входами логических элементов «И-НЕ» 4) со сдвигом по отношению к управляющим входам коммутатора 3 (здесь сдвиг равен 2), к которым присоединены соответствующие инверсные выходы Q̅1…Q̅6 триггеров 2 (к первым входам логических элементов «И-НЕ» 4). При этом прямые выходы триггеров 2 соединены со входами многовходового логического элемента «И-НЕ» 6, выход которого присоединён к инверсным входам  триггеров 2. На объединённые входы S установки триггеров 2 подаётся сигнал «SYNC» внешнего запуска, а объединённые входы J триггеров 2 заземлены (логический нуль).

триггеров 2. На объединённые входы S установки триггеров 2 подаётся сигнал «SYNC» внешнего запуска, а объединённые входы J триггеров 2 заземлены (логический нуль).

Полная задержка многоотводной линии задержки 1 должна быть примерно равна периоду тактовых импульсов T, при этом управляющий сигнал с выхода Ǭ5триггеров 2 коммутирует на выход коммутатора 3 сигнал с выводаС1многоотводной линии задержки 1 (для сигналов на выходах многоотводной линии задержки 1 имеет место циклический порядок, и следующий тактовый импульс на выводе С1 задержан относительно тактового импульса на выводеС6 на длительность задержки её сегмента Δt), а управляющий сигнал с выхода Ǭ6 – коммутирует сигнал с вывода C2.

Устройство работает следующим образом. На вход многоотводной линии задержки 1 поступают тактовые импульсы «CLK». Фронт очередного импульса появляется поочерёдно на первом выводе многоотводной линии задержки С1, затем на втором – С2 и т.д. В паузе между импульсами «SYNC» внешнего запуска триггеры 2 по инверсному входу S устанавливаются. При этом высокие уровни с выходов Q1…Q6 поступают на входы логического элемента «И-НЕ» 6, а логический нуль с его выхода поступает на инверсные входы  триггеров 2. На инверсных выходах Ǭ1…Ǭ6 триггеров 2 устанавливается низкий уровень, запрещающий прохождение сигналов с выводов С1 … С6 многоотводной линии задержки 1 через логические элементы «И-НЕ» 4 коммутатора 3. При поступлении сигнала внешнего запуска «SYNC» триггеры переводятся в синхронный режим, т.к. на их инверсных входах S установки появляется уровень логической единицы. При этом фронт тактового импульса, распространяющегося по многоотводной линии задержки, сбрасывает один из триггеров 2, т.к. на входах

триггеров 2. На инверсных выходах Ǭ1…Ǭ6 триггеров 2 устанавливается низкий уровень, запрещающий прохождение сигналов с выводов С1 … С6 многоотводной линии задержки 1 через логические элементы «И-НЕ» 4 коммутатора 3. При поступлении сигнала внешнего запуска «SYNC» триггеры переводятся в синхронный режим, т.к. на их инверсных входах S установки появляется уровень логической единицы. При этом фронт тактового импульса, распространяющегося по многоотводной линии задержки, сбрасывает один из триггеров 2, т.к. на входах  - триггеров 2 присутствует комбинация 00. Низкий уровень сигнала с прямого выхода Q этого триггера приводит к появлению высокого уровня на выходе логического элемента «И-НЕ» 6. На входах

- триггеров 2 присутствует комбинация 00. Низкий уровень сигнала с прямого выхода Q этого триггера приводит к появлению высокого уровня на выходе логического элемента «И-НЕ» 6. На входах  всех триггеров 2 устанавливается комбинация 01, что при поступлении на вход синхронизации триггера фронта тактового импульса приводит к подтверждению текущего состояния (режим хранения). Из-за задержки выходного сигнала триггера по отношению к фронту тактового импульса и задержки логического элемента «И-НЕ» несколько последующих триггеров успевают сброситься в логический нуль. Сброшенные триггеры высоким уровнем на инверсных выходах Ǭ разрешают прохождение на выход коммутатора 3 тактовых импульсов с соответствующих выводов многоотводной линии задержки. При этом положение фронта тактового импульса «SCLK» на выходе коммутатора 3определяется первым в цепочке сброшенных триггеров 2. Текущее состояние сохраняется до прихода нового импульса внешнего запуска «SYNC».

всех триггеров 2 устанавливается комбинация 01, что при поступлении на вход синхронизации триггера фронта тактового импульса приводит к подтверждению текущего состояния (режим хранения). Из-за задержки выходного сигнала триггера по отношению к фронту тактового импульса и задержки логического элемента «И-НЕ» несколько последующих триггеров успевают сброситься в логический нуль. Сброшенные триггеры высоким уровнем на инверсных выходах Ǭ разрешают прохождение на выход коммутатора 3 тактовых импульсов с соответствующих выводов многоотводной линии задержки. При этом положение фронта тактового импульса «SCLK» на выходе коммутатора 3определяется первым в цепочке сброшенных триггеров 2. Текущее состояние сохраняется до прихода нового импульса внешнего запуска «SYNC».

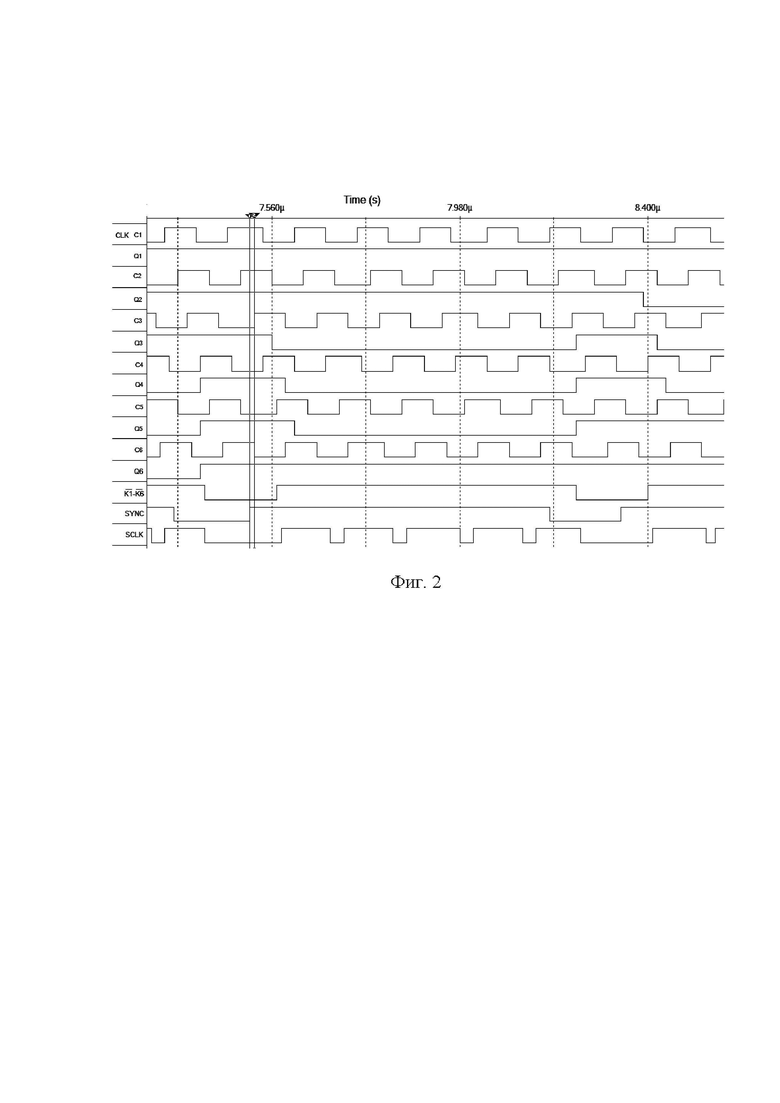

Временная диаграмма устройства (фиг. 2) иллюстрирует способ фазовой привязки. На диаграмме: «CLK» – входные тактовые импульсы (они же выходные С1); С1 … С6 – выходные сигналы многоотводной линий задержки 1; Q1 … Q6 – выходные сигналы триггеров 2;  –сигнал на объединённых инверсных входах KJK-триггеров: «SYNC» –импульс внешнего запуска; «SCLK» – синхронизированные тактовые импульсы на выходе коммутатора (временная диаграмма снята в режиме симуляции устройства).

–сигнал на объединённых инверсных входах KJK-триггеров: «SYNC» –импульс внешнего запуска; «SCLK» – синхронизированные тактовые импульсы на выходе коммутатора (временная диаграмма снята в режиме симуляции устройства).

До момента прихода фронта импульса внешнего запуска«SYNC» (фронт выделен на диаграмме окружностью) низким уровнем этого сигнала все выходы триггеров переводятся в высокий уровень. Вертикальная линия курсора 1, проходящая через фронт импульса внешнего запуска «SYNC», отмечает момент начала процесса синхронизации. Вертикальная линия курсора 2 проходит через ближайший фронт тактовых импульсов, присутствующий на выводе C3 многоотводной линии задержки. По фронту тактового импульса на выводе С3 многоотводной линии задержки на прямом выходе Q3 триггера с задержкой устанавливается низкий уровень. При этом высокий уровень на инверсном выходе этого триггера открывает коммутатор и пропускает на выход коммутатора тактовые импульсы с вывода С5. Сигнал низкого уровня с прямого выхода Q3 триггера поступает на вход многовходового элемента «И-НЕ» 6, а его выходной сигнал высокого уровня, поступающий на объединённые инверсные входы КJK-триггеров (сигнал  , фиг. 2) с задержкой, переводит триггеры в режим хранения, запрещая любые последующие изменения состояния триггеров до следующего импульса внешнего запуска. Так как перевод триггеров в режим хранения задержан относительно фронта первого тактового импульса, вызвавшего изменение состояния триггеров, то в течение интервала этой задержки сигнал низкого уровня установится на прямых выводах Q4 и Q5 триггеров. Выходные сигналы высокого уровня с инверсных выходов этих триггеров, поступая на управляющие входы коммутатора, пропустят на его выход тактовые импульсы с выводов C6 и C1 многоотводной линии задержки. Это приводит увеличению длительности синхронизированных тактовых импульсов «SCLK», но положение их фронтов определяется тактовыми импульсами с вывода многоотводной линии задержки, на котором фронт тактового импульса был задержан на минимальный временной интервал относительно импульса внешнего запуска.

, фиг. 2) с задержкой, переводит триггеры в режим хранения, запрещая любые последующие изменения состояния триггеров до следующего импульса внешнего запуска. Так как перевод триггеров в режим хранения задержан относительно фронта первого тактового импульса, вызвавшего изменение состояния триггеров, то в течение интервала этой задержки сигнал низкого уровня установится на прямых выводах Q4 и Q5 триггеров. Выходные сигналы высокого уровня с инверсных выходов этих триггеров, поступая на управляющие входы коммутатора, пропустят на его выход тактовые импульсы с выводов C6 и C1 многоотводной линии задержки. Это приводит увеличению длительности синхронизированных тактовых импульсов «SCLK», но положение их фронтов определяется тактовыми импульсами с вывода многоотводной линии задержки, на котором фронт тактового импульса был задержан на минимальный временной интервал относительно импульса внешнего запуска.

Таким образом, предложенный способ фазовой синхронизации тактовых импульсов внешним импульсом запуска обеспечивает уменьшение времени синхронизации, а погрешность синхронизации в предельном случае ограничивается лишь разбросом задержек триггеров при синхронном сбросе.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ фазовой синхронизации тактовых импульсов внешним импульсом | 2024 |

|

RU2822445C1 |

| Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска | 2022 |

|

RU2785070C1 |

| Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска | 2018 |

|

RU2693595C1 |

| Способ синхронизации тактовых импульсов внешним импульсом | 2019 |

|

RU2721231C1 |

| СПОСОБ ФАЗОВОЙ ПРИВЯЗКИ ГЕНЕРИРУЕМОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ К ИМПУЛЬСУ ВНЕШНЕГО ЗАПУСКА | 2010 |

|

RU2447576C2 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ГЕНЕРАТОРА ИМПУЛЬСОВ | 2004 |

|

RU2259630C1 |

| Формирователь импульсов (его варианты) | 1990 |

|

SU1837387A1 |

| Устройство задержки последовательности импульсов с цифровым управлением | 1985 |

|

SU1285576A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ | 2011 |

|

RU2474043C1 |

Изобретение относится к области импульсной техники. Техническим результатом является уменьшение времени синхронизации и возможность повышения точности синхронизации за счёт повышения частоты дискретизации периода тактовых импульсов. Он достигается запоминанием текущего положения фронта тактового импульса, распространяющегося в многоотводной линии задержки, в одном из триггеров, подключенных входами синхронизации к выводам многоотводной линии задержки, при поступлении импульса внешнего запуска. При этом выходные сигналы триггеров, изменивших своё состояние по фронту тактового импульса с соответствующего вывода многоотводной линии задержки, блокируют последующее изменение состояния триггеров и коммутируют тактовые импульсы с нескольких последующих выводов многоотводной линии задержки на выход коммутатора, причём положение фронтов тактовых импульсов определяется первым триггером в цепочке триггеров, изменивших своё состояние. 2 ил.

Способ фазовой синхронизации тактовых импульсов внешним импульсом запуска, состоящий в запоминании текущего положения фронта тактового импульса, распространяющегося в многоотводной линии задержки в одном из триггеров, подключенных входами синхронизации к выводам многоотводной линии задержки, при поступлении импульса внешнего запуска, отличающийся тем, что с целью уменьшения времени на синхронизацию выходные сигналы триггеров, изменивших своё состояние по фронту тактового импульса с соответствующего вывода многоотводной линии задержки, прямыми выходами, подключёнными ко входам элемента И-НЕ, блокируют его выходным сигналом последующее изменение состояния триггеров, а инверсными выходами управляют коммутатором, коммутирующим тактовые импульсы с нескольких последующих выводов многоотводной линии задержки на выход, причём положение фронта тактового импульса определяется первым триггером в цепочке триггеров, изменивших своё состояние.

| Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска | 2022 |

|

RU2785070C1 |

| Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска | 2018 |

|

RU2693595C1 |

| СПОСОБ ФАЗОВОЙ ПРИВЯЗКИ ГЕНЕРИРУЕМОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ К ИМПУЛЬСУ ВНЕШНЕГО ЗАПУСКА | 2010 |

|

RU2447576C2 |

| US 20050047540 A1, 03.03.2005. | |||

Авторы

Даты

2024-08-01—Публикация

2024-02-13—Подача