Изобретение относится к вычислительной технике и может использоваться в интегральных устройствах, а именно в цифро-сигнальных процессорах с системой команд VLIW (Very Long Instruction Word), т.е. в формате команд с большим числом бит в слове.

В известных специализированных процессорах, например, согласно патенту США US4991169, блоки и узлы спроектированы исключительно для узкого применения. В другом цифро-сигнальном процессоре, известном из патента США US8543635, для реализации трансфер-функции (Z-трансформ) используется последовательность сумматоров-вычитателей, задержек (регистров) для реализации функций фильтров. В устройстве, описанном в патенте США US4821294, используется кодовый коррелятор, понижающий (down) конвертор, отдельный процессор для трекинга.

Наиболее близким аналогом рассматриваемого технического решения можно считать устройство, раскрытое в заявке на патент США US2010/0191786 (опубликована 29.07.2010, МПК G06F5/01, G06F7/50, G06F9/38). В частности, в заявке описывается блок обработки цифровых сигналов, в котором для свертывания исходного сигнала используется последовательность сумматоров-вычитателей, а для реализации фильтров используются регистры задержек.

Однако это устройство имеет узкую область использования, а именно может служить только для создания нечетного симметричного систолического фильтра.

Решаемой изобретением задачей является расширение функциональных возможностей цифро-сигнального процессора.

Техническим результатом является обеспечение универсальности цифро-сигнального процессора для его быстрого перепрограммирования при реализации конкретных задач.

Для решения поставленной задачи с достижением технического результата заявленный цифро-сигнальный процессор содержит аналого-цифровой преобразователь (АЦП), десимэйшн фильтр, тестовый регистр перед операционной частью процессора, блок арифметических и логических операций, соединенные первыми входами и выходами последовательно. Вход аналого-цифрового преобразователя служит входом цифро-сигнального процессора. Устройство содержит перепрограммируемую память, блок памяти коэффициентов, блок инструкций. Первый выход перепрограммируемой памяти соединен с первым входом блока памяти коэффициентов, второй выход перепрограммируемой памяти соединен со вторым входом аналого-цифрового преобразователя, третий выход перепрограммируемой памяти соединен с первым входом блока инструкций, а первый вход-выход перепрограммируемой памяти служит для записи и контроля записанной информации в память. Устройство содержит тестовый регистр после операционной части процессора, первый блок оперативной памяти, второй блок оперативной памяти, блок умножения, блок контроля сканирования и выходной цифровой преобразователь. Первый выход блока памяти коэффициентов соединен с первым входом блока умножения и со вторым входом блока арифметических и логических операций. Выход блока инструкций соединен со вторым входом блока памяти коэффициентов, седьмым входом блока арифметических и логических операций, первым входом тестового регистра после операционной части процессора, первым входом первого блока оперативной памяти, вторым входом блока умножения, вторым входом второго блока оперативной памяти, и первым входом выходного цифрового преобразователя. Первый вход-выход тестового регистра после операционной части процессора соединен с первым входом-выходом тестового регистра перед операционной части процессора, а второй вход-выход тестового регистра после операционной части процессора соединен с первым входом-выходом блока контроля сканирования. Первый выход тестового регистра после операционной части процессора соединен со вторым входом тестового регистра перед операционной части процессора, второй выход тестового регистра после операционной части процессора соединен со вторым входом блока контроля сканирования, второй вход тестового регистра после операционной части процессора служит для контроля и передачи записываемой информации извне, третий вход-выход тестового регистра после операционной части процессора служит для чтения и записи информации через внешний вывод. Первый выход первого блока оперативной памяти соединен с третьим входом блока арифметических и логических операций, его второй выход – с четвертым входом блока арифметических и логических операций, а его третий выход – с первым входом блока контроля сканирования. Первый выход блока арифметических и логических операций соединен с первым входом второго блока оперативной памяти и вторым входом первого блока оперативной памяти. Второй выход блока арифметических и логических операций соединен со вторым входом блока инструкций. Первый выход блока оперативной памяти соединен с пятым входом блока арифметических и логических операций и третьим входом блока умножения. Второй выход второго блока оперативной памяти соединен с шестым входом блока арифметических и логических операций. Выход блока умножения соединен с третьим входом первого блока оперативной памяти и третьим входом второго блока оперативной памяти. Выход блока контроля сканирования соединен со вторым входом выходного цифрового преобразователя, выход которого служит выходом цифро-сигнального процессора. Цифро-сигнальный процессор также имеет блок синхронизации, выход которого соответственно соединен с управляющими входами аналого-цифрового преобразователя (АЦП), десимэйшн фильтра, тестового регистра перед операционной части процессора, блока арифметических и логических операций, перепрограммируемой памяти, блока памяти коэффициентов, блока инструкций, тестового регистра после операционной части процессора, первого блока оперативной памяти, второго блока оперативной памяти, блока умножения, блока контроля сканирования, выходного цифрового преобразователя.

Преимущества, а также особенности настоящего изобретения поясняются с помощью варианта его выполнения со ссылками на фигуры.

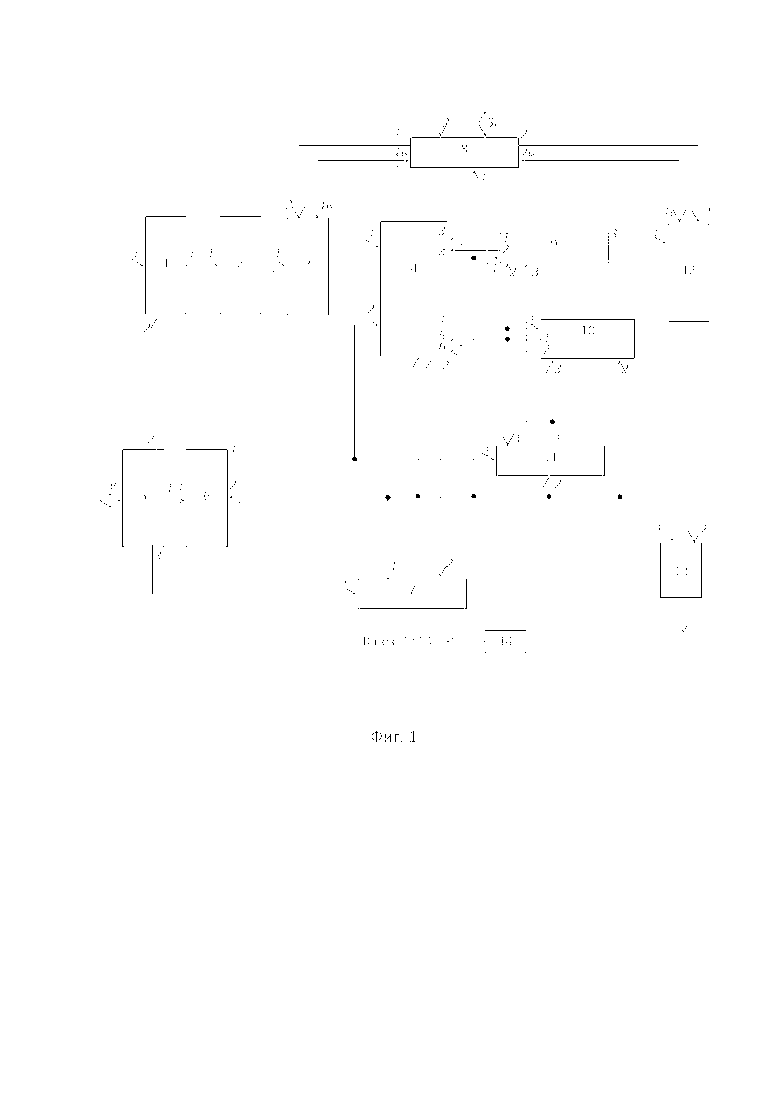

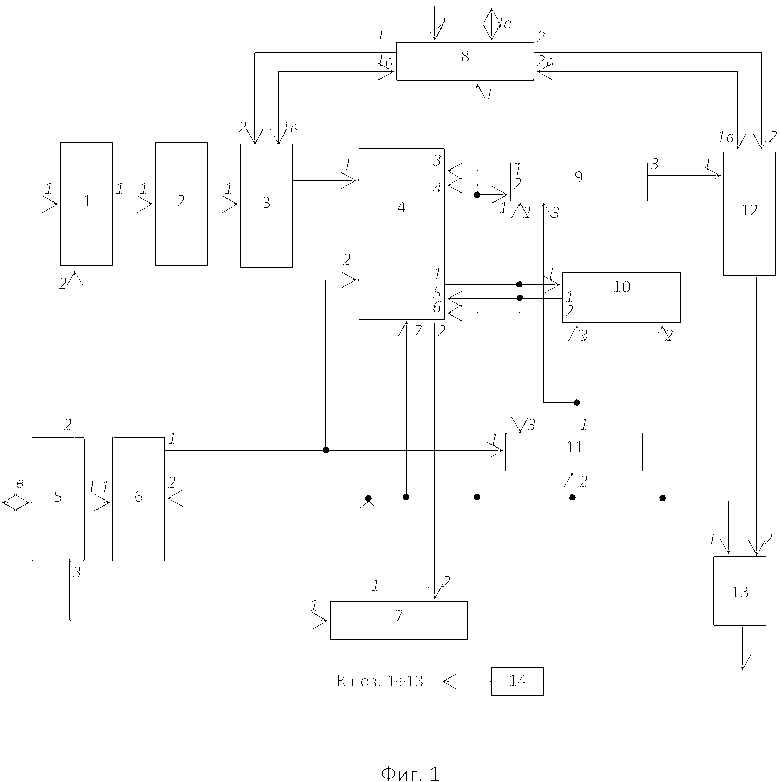

На фиг. 1 изображена функциональная схема заявленного цифро-сигнального процессора.

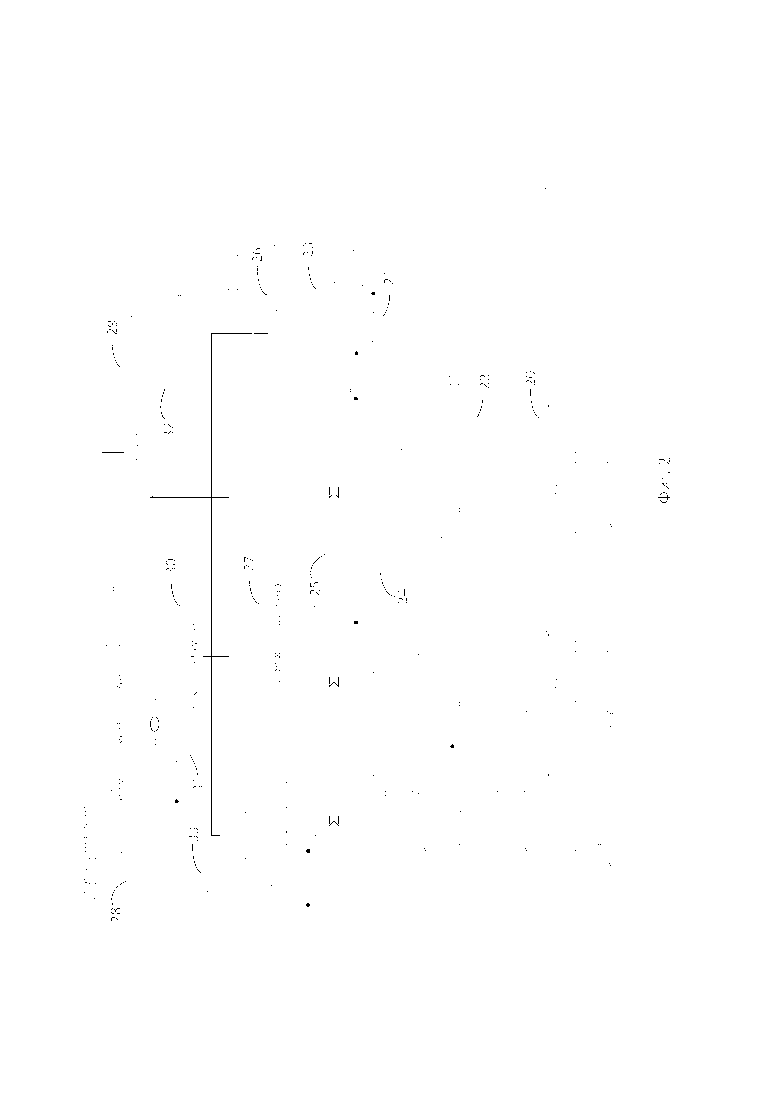

На фиг. 2 приведена принципиальная схема блока арифметических и логических операций.

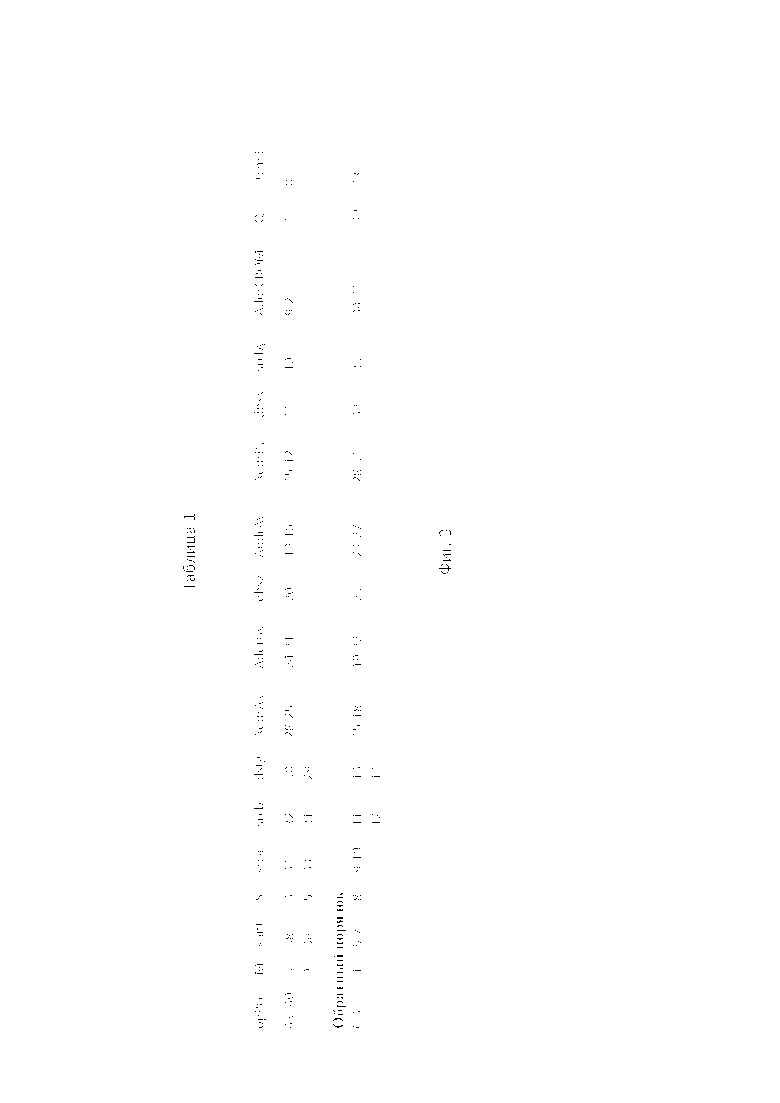

На фиг. 3 приведена Таблица 1 распределения битов в общей длине командного слова (как пример) арифметических и логических операций блока на фиг. 2.

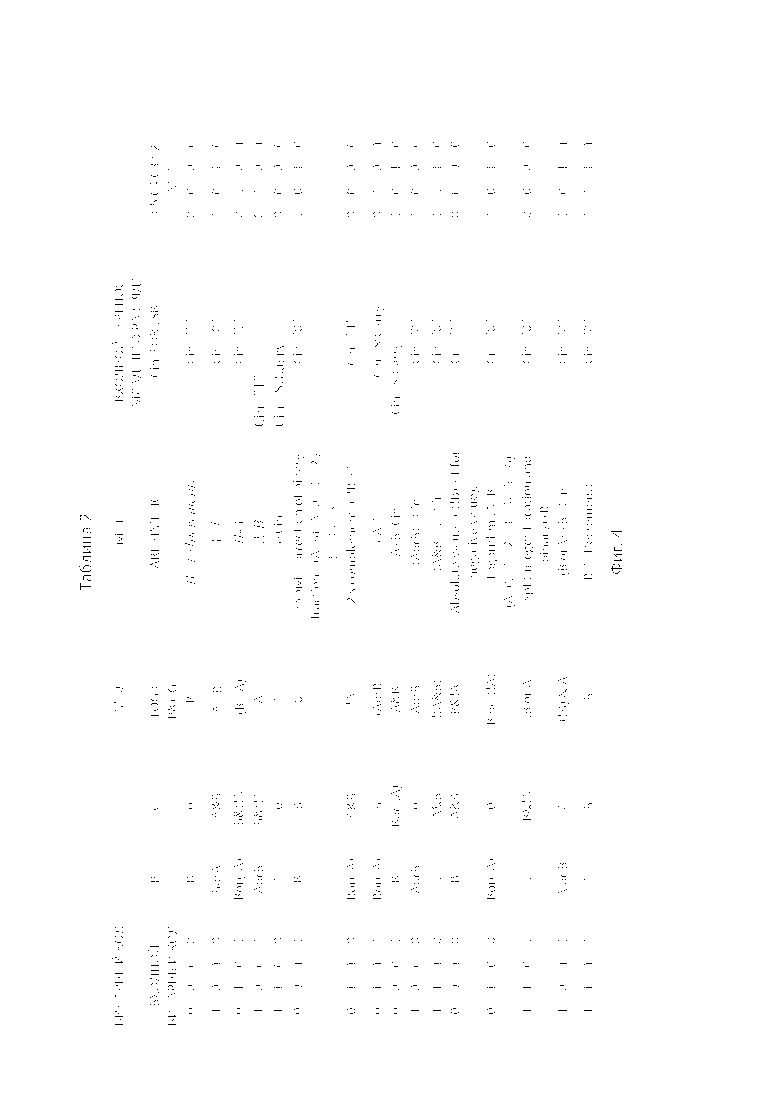

На фиг. 4 приведена Таблица 2 операций для арифметического и логического устройства.

Цифро-сигнальный процессор (фиг. 1) содержит аналого-цифровой преобразователь (АЦП) 1, десимэйшн фильтр 2 (CIC «cascaded integrator–comb» фильтр), тестовый регистр 3 перед операционной частью процессора, блок 4 арифметических и логических операций, соединенные первыми входами и выходами последовательно, перепрограммируемую память 5, блок 6 памяти коэффициентов, и блок 7 инструкций. Вход аналого-цифрового преобразователя 1 служит входом цифро-сигнального процессора. Первый выход перепрограммируемой памяти 5 соединен с первым входом блока 6 памяти коэффициентов, второй выход перепрограммируемой памяти 5 соединен со вторым входом аналого-цифрового преобразователя 1, третий выход перепрограммируемой памяти 5 соединен с первым входом блока 7 инструкций, а первый вход-выход перепрограммируемой памяти 5 служит для записи и контроля записанной информации в память.

Устройство также содержит тестовый блок 8 после операционной части процессора, первый блок 9 оперативной памяти, второй блок 10 оперативной памяти, блок 11 умножения, тестового регистра 12 после операционной части и выходной цифровой преобразователь 13.

Первый выход блока 6 памяти коэффициентов соединен с первым входом блока 11 умножения и со вторым входом блока 4 арифметических и логических операций. Выход блока 7 инструкций соединен со вторым входом блок 6 памяти коэффициентов, седьмым входом блока 4 арифметических и логических операций, первым входом тестового регистра 8 после операционной части процессора, первым входом первого блока 9 оперативной памяти, вторым входом блока 11 умножения, вторым входом второго блока 10 оперативной памяти, первым входом выходного цифрового преобразователя 13.

Первый вход-выход тестового блок 8 соединен с первым входом-выходом тестового регистра 3 перед операционной части процессора. Второй вход-выход тестового блока 8 соединен с первым входом-выходом тестового регистра 12 после операционной части. Первый выход тестового блока 8 соединен со вторым входом тестового регистра 3 перед операционной части процессора. Второй выход тестового блока 8 соединен со вторым входом тестового регистра 12 после операционной части. Второй вход тестового блока 8 после операционной части процессора служит для контроля и передачи записываемой информации после выполнения операций, третий вход-выход тестового блока 8 служит для чтения и записи информации через внешний вывод – контроля сканирования тестового регистра 3 и тестового регистра 12 после операционной части.

Первый выход первого блока 9 оперативной памяти соединен с третьим входом блока 4 арифметических и логических операций, его второй выход – с четвертым входом блока 4 арифметических и логических операций, и его третий выход – с первым входом блока 12 контроля сканирования.

Первый выход блока 4 арифметических и логических операций соединен с первым входом второго блока 10 оперативной памяти и со вторым входом первого блока 9 оперативной памяти. Второй выход блока 4 арифметических и логических операций соединен со вторым входом блока 7 инструкций. Первый выход блока 10 оперативной памяти соединен с пятым входом блока 4 арифметических и логических операций и с третьим входом блока 11 умножения, (причем второй вход для блока умножения является управляющим кодом – типом операции). Второй выход второго блока 10 оперативной памяти соединен с шестым входом блока 4 арифметических и логических операций. Выход блока 11 умножения соединен с третьим входом первого блока 9 оперативной памяти и с третьим входом второго блока 10 оперативной памяти. Выход тестового регистра 12 после операционной части со вторым входом выходного цифрового преобразователя 13, выход которого служит выходом цифро-сигнального процессора.

Цифро-сигнальный процессор также имеет блок 14 синхронизации, выход которого соответственно соединен с управляющими входами аналого-цифрового преобразователя (АЦП) 1, десимэйшн фильтра 2, тестового регистра 3 перед операционной части процессора, блока 4 арифметических и логических операций, перепрограммируемой памяти 5, блока 6 памяти коэффициентов, блока 7 инструкций, тестового блока 8, первого блока 9 оперативной памяти, второго блока 10 оперативной памяти, блока 11 умножения, тестового регистра 12 после операционной части, выходного цифрового преобразователя 13.

Работает цифро-сигнальный процессор (фиг. 1) следующим образом.

Устройство работает следующим образом.

На первый вход АЦП 1 поступает аналоговый сигнал, который в анлого-цифровом преобразователе 1 формируется в последовательность одного или нескольких бит (в частности, для преобразователя на базе дельта-сигма второго порядка это может быть однобитовая информация). Далее код поступает на десимэйшн фильтр 2 (CIC «cascaded integrator–comb» фильтр) и через тестовый регистр 3 перед операционной частью цифро-сигнального процессора на первый вход блока 4 арифметических и логических операций. Десиммэйшн фильтр 2 преобразует битовую (или несколько бит) последовательность в параллельное слово, например, в 16 или 24 разряда в зависимости от требований по точности вычислений. Эти данные по первому входу для блока 4 арифметических и логических операций являются численным, цифровым значением аналогового сигнала. Дальнейшие операции определяются кодом, поступающим на седьмой вход из блока 7 инструкций. Блок 7 инструкций - это или ПЗУ, или ППЗУ. Емкость блока 7 инструкций также определяется областью применения – объёмом программы. Тестовый регистр 3 перед оперционной части и тестовый регистр 12 после операционной части предназначены для упрощения контроля качества изделия. Считывание данных посредством сдвига информации через последовательный выход этих регистров поступает на выход устройства для сранения с эталонным (ожидаемым) результатом (вход/выход 3в). После выполнения операции в блоке 4 арифметических и логических операций (таблица 2 на фиг.4) результат поступает на второй вход первого блока 9 оперативной памяти и на первый вход второго блока 10 оперативной памяти. Запись информации определяется кодом инструкции. Соответственно кодом инструкции в этой же команде определяются и ячейки памяти, из которых осуществляется считывание информации для блока 4 арифметических и логических операций. В блоке 11 умножения два операнда из оперативной памяти 10 и из блока 6 памяти коэффициентов, поступающие на первый и третий входы перемножаются в указанном блоке. Результат операции с первого выхода блока 11 умножения записывается в блоки оперативной памяти 9 и/или 10. Ширина (число бит) длинного слова инструкций (VLIW) из блока 7 инструкций позволяет производить значительный объём вычислений за один цикл. С третьего выхода блока 9 оперативной памяти информация поступает на первый вход тестового регистра 12 после операционной части, который обеспечивает проверку цифровой части цифро-сигнального процессора перед поступлением информации в цифро-аналоговый преобразователь 13. Такая конфигурация обеспечивает гибкость при проверке качества устройства в режиме контроля годности. Цифро-аналоговый преобразователь 13 формирует аналоговый сигнал для внешних устройств.

В зависимости от области применений осуществляется перепрограммирование памяти 5 по входу/выходу в (фиг. 1). Например, со второго выхода этого блока осуществляется задание для частоты квантования анагово-цифрового преобразователя 1 (так называемого – jversampking ratio) для чего сигналы поступают на второй вход указанного АЦП 1. Блок 6 памяти коэффициентов служит для задания их величин с выхода 1 этого блока, адрес ячейки определяется состоянием сигнала на втором входе блока 6. Коэффициенты определяют частотные характеристики фильтров в зовисимости от области применения, которые поступают на второй вход блока 4 арифметических и логических операций и на первый вход блока 11 умножения. На первом выходе блока 7 инструкций формируется код длинного слова (VLIW), управляющий блоками параллельно. Каждый новый период тактового сигнала на блоки поступает следующее кодовое слово (VLIW), которое также зависит от состояний на первом и втором входах 2 блока 7 инструкций. На первый вход блока 7 поступают сигналы с третьего выхода перепрограммируемой памяти 5, которые выпоняют функцию выбора подпрограммы в блоке 7 инструкций. Состояния из блока 4 арифметических и логических операций по второму выходу также обеспечивают переходы между подпрограммами. Блок 11 умножения управляется по его второму входу. Команды из блока 7 инструкций могут быть, например, - truncation или rounding,то есть без учёта значения младшего бита или с учётом значения младшего бита.

Первый вход-выход (1в – фиг. 1) тестового блока 8 соединен с первым входом-выходом тестового регистра 3 перед операционной части процессора. Второй вход-выход (2в) тестового блока 8 соединен с первым (1в) входом-выходом тестового регистра 12 после операционной части. Первый выход тестового блока 8 соединен со вторым входом тестового регистра 3 перед операционной части процессора. Второй выход 2 тестового блока 8 соединен со вторым входом тестового регистра 12 после операционной части. Второй вход тестового блока 8 после операционной части процессора служит для контроля и передачи записываемой информации после выполнения операций, третий (3в) вход-выход тестового блока 8 служит для чтения и записи информации через внешний вывод – контроля сканирования тестового регистра 3 перед операционной частью и тестового регистра 12 после операционной части. Блоки тестового регистра 3 перед оперционной части, тестового регистра 12 после операционной части и тестового блока 8 после операционной части процессора предназначены для тестирования изделия и существенно упрощают эту процедуру посредством чтения или записи последовательной информации в тестовом регистре 3 перед операционной части и в тестовом регистре 12 после операционной части.

Ниже приведены два примера расшифровки мнемонического программируемого кода.

Блок 4 арифметических и логических операций (фиг. 1) состоит из следующих узлов (фиг. 2):

Входной мультиплексор 20 - MUX;

Дешифратор 21 - PGLE;

Мультиплексоры 22 log_exp - Muxlogexp;

Формирователь 23 входного переноса - Carryin;

Модули 24 PG (где Р – узел разрешения переноса (propagation), G – generation – узел генерации переноса – независимости формирования переноса от предыдущего разряда);

Модули 25 суммирования сложения - (Σ);

Дешифратор 26 сдвига – Decoder of shift;

Сдвигатель 27 - Shifter;

Регистр 28 состояний - Status Register;

Накопитель 29 - Accumulator;

Элемент 30 –формирователь сигнала «0» ZERO для регистра состояний, когда все разряды равны 0;

Блок 31 формирования сигнала переполнения для регистра 28 состояний;

Блок 32 формирования младшего разряда при операциях сдвига;

Блок 33 формирования старшего разряда при операциях сдвига.

1) Входной мультиплексор 20 – MUX (фиг. 2) – это первый блок (фиг. 2) для блока 4 арифметических и логических операций (АЛУ), в котором определяется к какому источнику информации подключён блока 4 АЛУ. Далее для блока 4 арифметических и логических операций формируются в зависимости от состояния сигналов на входах SRCA и SRCB внутренние уже источники –A и B. Для A источниками являются Ax, Ay, CROM ( /SRCAx=2'b00, SRCAy=2'b01, //SRCCROM=2'b10 ( opALURAM [22:21]). Для B источники Bx, By, DF (SRCBx=2'b00, SRCBy=2'b01, SRCDF=2'b10 (opALURAM[20:19] ); Входной мультиплексор 20 функционирует как обычный мультиплексор.

2) Decoder for P&G – это управляющий дешифратор 21 в соответствии с приведенной фиг. 2 для блока 4 арифметических и логических операций (например, 16 логических и 16 арифметических операций (Таблица 2, фиг. 4) в зависимости от M, где М – сигнал, определяющий класс операции - например, «0» - логические оперции, «1» - арифметические операции);

3) Muxlogexp мультиплексор 22 выполняет функцию определения логарифма и экспоненты (для A и B);

4) Формирователь 23 входного переноса Carryin – перенос для младшего разряда слова t (0/1 в зависимости от инструкции);

5) Модуль 24 PG предназначен для двух сигналов - (P) и (G). В модуле 24 PG формируются логические функции – P[i] = A[i] V B[i] и G[i] = A[i] & B[i] , где V – операция «ИЛИ» и &- операция «И»;

6) Модуль 25 суммирования SUM (Σ);

7) Дешифратор 26 сдвига формирует 8 сигналов – llsh1, lrsh1, alsh1, arsh1, rlsh1, nsh, alsh2, arsh2;

8) Shifter – сдвигатель 27 в соответствии с вышеприведённым п.7 , например, alsh1 – арифметичсекий (а) сдвиг (sh) влево (l) на один разряд (1);

9) Status Register – Регистр 28 состояний для сохранения статуса операции (SS – знак, C - перенос из старшего разряда, OF –переполнение, Zero – результат равен 0);

10) Накопитель 29 Accumulator регистр промежуточного хранения с последующей перезаписью результата в RAM1, или RAM2 (блоки 9 и 10 на фиг. 1). Или DDS – digital delta sigma (дельта-сигма) (блок 13 на фиг. 1).

Третий и четвертый входы на фиг.1 соответствуют входам Ax и Bx на фиг.2. Пятый и шестой входы на фиг.1 соответствуют входам Ay и By на фиг.2. Первый вход 1 на фиг.1 – это вход DF (данные от десимэйшн фильтра). Второй вход на фиг.1 соответствует входу CROM на фиг 2. Седьмой вход 7 на фиг.1 (это управляющие сигналы, определяющие всю работу блока 4 арифметических и логических операций соответствует входам <15,16,17>, М (<14>), S, <10,11,12,13> в совокупности.

Источники данных для блока 4 арифметических и логических операций:

- Ax и Bx;

- Ax и By;

- Ax и DF;

- Ay и Bx;

- Ay и By;

- Ay и DF;

- CROM и Bx;

- CROM и By;

- CROM и DF.

Устройство на фиг. 2 работает следующим образом:

На седьмой вход блока 4 арифметических и логических операций поступают управляющие сигналы, которые определяют тип выполняемой оперции и с какими данными это будет осуществлено. Например, считываемые состояния из блоков 9 и 10 оперативной памяти или из десимэйшн фильтра 2 через тестовый регистр 3 и блока 6 памяти коэффициентов. Тип оперции в блоке 4 арифметических и логических операций согласуется с таблицей 2 (фиг. 4).

Выходы дешифратора 21 PG (Decoder for P&G) – четыре сигнала для PG ( pgc2, pgc3, pgc4, pgc5) и три сигнала для Log и Exp операций - ExpI, ExpM, Log.

Блок формирователя 23 входного переноса Carryin формирует “0” или “1” в зависимости от типа операции. Например, “1” для вычитания.

Модуль 24 PG формирует два сигнала для каждого разряда - P и G;

Модуль 25 суммирования вычисляет результат перед сдвигателем и сигнал переноса для следующего разряда;

Блок сдвигателя 27 (shifter) выполняет восемь операций – сдвиги в сторону старших или младших разрядов или циклический сдиг;

Блок регистра 28 состояний (Status Register [3:0]) предназначен для выполнения операций перехода по условию (ROM- jump instructions);

Блок аккумулятора – Накопитель 29 (Accumulator) для сохранения результата после сдвигателя перед загрузкой в память (RAM1/2).

Таблица 2 (фиг. 4) поясняет, какие операции выполняются в блоке 4 арифметических и логических операций. Например, при входном коде <0,0,0,0> формируемые сигналы: на P – B, а на G – 0, что соответствует логической оперции (М=0) – В или арифметической операции (М=1) В+1. Входной сигнал переноса для младшего разряда равен - Cin=1 (это и есть сложение с 1 (increment). Сигналы в управляющем дешифраторе 21 при этом не изменяются С5, С4, С3, С2 = <0,0,0,0>. Рассмотрим следующий пример. Код операции <1,0,0,1> и М= 1. При этом формируется Р= AorB (A ИЛИ B) и G= B&(!A). Арифметическая операция соответствует A-B. Если же в коде «0» на выводе М (М=0), то выполняется логическая операция А (передача данных ). Заметим, что сигналы в управляющем дешифраторе 21 при этом изменяются С5, С4, С3, С2 = <0,1,0,1>. И т.д.

Перепрограммирование устройства осуществляется в блоке 7 инструкций.

В приложении 1 приведены мнемонические коды для типов операций, источников и блоков для записи результата операции.

Перепрограммирование устройства осуществляется за счёт написания различного (по назначению - области применения) мнемонического кода. Разработчик, оперируя данными в определении активности того или иного блока и типами необходимых операций пишет мнемоническую последовательность для каждого такта – см, пример, выделенный жирным шрифтом ниже.

Наиболее успешно заявленный «Цифро-сигнальный процессор (ЦСП) с системой команд VLIW» промышленно применим в системах обработки информации с фильтрацией, в слуховых аппаратах, в системах коммуникации.

Пример мнемонического кода (определения) для ЦСП (цифро-сигнального процессора) приведен ниже.

Рассмотрим пример оперции в мнемоническом коде:

(12) Band Split Filter

* (a) (s7 = s2 - s6 ) Clip if OF

* AxR[1] ByR[15] AyR[12]

*

BminusA sshInst nshCp SE srcAy srcBy dstgRx AxR[1] dstAx srcxALU AyR[12] ByR[15]

Это часть операции для фильтра (в данном случае для бэнд фильтра):

1) * (a) (s7 = s2 - s6 ) Clip if OF

2) * AxR[1] ByR[15] AyR[12]

Закомментированное значком * - только пояснение для самого разработчика программы (напоминание).

3) BminusA – означает мнемоническое обозначение операции В-А.

4) sshInst – активизация операции сдвига.

5) nshCp – нет сдвига и ограничение сигнала.

6) SE – выбор источника данных.

7) srcAy srcBy – источники информации поступают на входы Ау и Ву блока 20.

8) dstgRx – означает, что запись результата операции будет осуществляться в блок памяти 9.

9) AxR[1] – запись по адресу Аx в регистр блока памяти № 1 (9).

10) srcxALU – при этом источник записываемого результата – блок 4 арифметического и логического устройства.

11) AyR[12] ByR[15] – источники данных для выполнения операции будут считываться из регистров 12 и 15 блока памяти 10 (у).

И т.д.

Пример № 2 (код 30-ой операции):

(30) H channel detection filter

* (a) q6 = 2^-6 * q5

* AyR[15] AyR[15]

*

tA sshInst ashr6 SE srcAy dstgRy AyR[15] dstAy srcyALU

*----------------------------------------------------------------------------------------

1) tA – означает мнемоническое обозначение операции A – передача А.

2) sshInst – активизация операции сдвига.

3) ashr6 –арифметический сдвил вправо на 6 разрядов.

4) SE – выбор источника данных.

5) srcAy – источник информации поступают на вход Ау блока 20.

6) dstgRу – означает, что запись результата операции будет осуществляться в блок памяти 10.

7) AуR[15] – запись по адресу Аx в регистр блока памяти № 1 (9).

8) dstAy –запись осуществлянтся по коду Ау.

9) srcyALU - при этом источник результата операции – блок 4 арифметических и логических операций.

Приложение 1

*****************************************************************

* *

* Def_Inst.sma *

* *

*****************************************************************

* *

* *

* *

* DSP Instruction Code Definitions *

* *

* *

* *

*

*****************************************************************

*****************************************************************

State Machine Configuration Длина VLIW – 64 бита.

48,8,8

LIST OFF

************************ "Do" Bits ************************

OpMp = ^0 ; Multiplier / Enable

MPYCROM = OpMp[1] ; Multiply: (Coefficient ROM) * By

MPYRAM = OpMp[5] ; Multiply: (RAM Ay) * By

round = OpMp[2] ; round (default)

trunc = OpMp[0] ; truncate

addrCROM = ^3 ; Coefficient ROM Address

srcy = ^10 ; Register Y Source, either ALU or MPY output

srcyALU = srcy[0] ; ALU

srcyMPY = srcy[1] ; Multiplier

dbsy = ^11 ; for destination = register Y, choose; operand: 0 = addrAy, or 1 = addrBy

dstAy = dbsy[0] ; Write Address Is addrAy

dstBy = dbsy[1] ; Write Address Is addrBy

addrBy = ^12 ; Register Y, B operand address

ByR = addrBy ; / ByR[n]

addrAy = ^16 ; Register Y, A operand address

AyR = addrAy ; / AyR[n]

srcx = ^20 ; Register X Source, either ALU or MPY output

srcxALU = srcx[0] ; ALU

srcxMPY = srcx[1] ; Multiplier

dbsx = ^21 ; for destination = register X, choose

; operand: 0 = addrAx, or 1 = addrBx

dstAx = dbsx[0] ; Write Address Is addrAx

dstBx = dbsx[1] ; Write Address Is addrBx

addrBx = ^22 ; Register X, B operand address

BxR = addrBx ; / BxR[n]

addrAx = ^26 ; Register X, A operand address

AxR = addrAx ; / AxR[n]

dstg = ^30 ; Result Destination General Register(s):

; (RX, RY, RX&RY, DDS)

dstgDDS = dstg[0] ; Digital Delta-Sigma

dstgRy = dstg[1] ; Register Y

dstgRx = dstg[2] ; Register X

dstgRxRy = dstg[3] ; Register X & Register Y

srcB = ^32 ; Source for operand B: (BX, BY, DF, -)

srcBx = srcB[0] ; Register X

srcBy = srcB[1] ; Register Y

srcBCROM = srcB[2] ; CROM

srcBDF = srcB[3] ; Decimation Filter

srcA = ^34 ; Source for operand A: (AX, AY, CROM, -)

srcAx = srcA[0] ; Register X

srcAy = srcA[1] ; Register Y

srcACROM = srcA[2] ; Coefficient ROM

srcADF = srcA[3] ; Decimation Filter

S = ^36 ; Status Register

SD = S[0] ; Disable

SE = S[1] ; Enable

shift = ^37 ; Shift Operation Bit Base

nsh = shift[0] ; No Shift Operation

ashl1 = shift[1] ; Arithmetic Left-Shift 1

ashl2 = shift[2] ; Arithmetic Left-Shift 2

ashl3 = shift[3] ; Arithmetic Left-Shift 3

ashl4 = shift[4] ; Arithmetic Left-Shift 4

ashl5 = shift[5] ; Arithmetic Left-Shift 5

ashl6 = shift[6] ; Arithmetic Left-Shift 6

ashl7 = shift[7] ; Arithmetic Left-Shift 7

ashl8 = shift[8] ; Arithmetic Left-Shift 8

lshr1 = shift[9] ; Logical Right-Shift 1

lshr2 = shift[10] ; Logical Right-Shift 2

lshr3 = shift[11] ; Logical Right-Shift 3

lshl1 = shift[12] ; Logical Left-Shift 1

lshl2 = shift[13] ; Logical Left-Shift 2

lshl3 = shift[14] ; Logical Left-Shift 3

nshOF = shift[15] ; Special Overflow Shift

ashr1 = shift[31] ; Arithmetic Right-Shift 1

ashr2 = shift[30] ; Arithmetic Right-Shift 2

ashr3 = shift[29] ; Arithmetic Right-Shift 3

ashr4 = shift[28] ; Arithmetic Right-Shift 4

ashr5 = shift[27] ; Arithmetic Right-Shift 5

ashr6 = shift[26] ; Arithmetic Right-Shift 6

ashr7 = shift[25] ; Arithmetic Right-Shift 7

ashr8 = shift[24] ; Arithmetic Right-Shift 8

ashr9 = shift[23] ; Arithmetic Right-Shift 9

ashr10 = shift[22] ; Arithmetic Right-Shift 10

ashr11 = shift[21] ; Arithmetic Right-Shift 11

ashr12 = shift[20] ; Arithmetic Right-Shift 12

ashr13 = shift[19] ; Arithmetic Right-Shift 13

ashr14 = shift[18] ; Arithmetic Right-Shift 14

ashr15 = shift[17] ; Arithmetic Right-Shift 15

ashr16 = shift[16] ; Arithmetic Right-Shift 16

nshCp = nshOF ; nsh, Clip if ALU operation in same instruction overflowed

ashl1Cp = ashl1 ; Arithmetic left-shifts also Clip if overflow

ashl2Cp = ashl2

ashl3Cp = ashl3

ashl4Cp = ashl4

ashl5Cp = ashl5

ashl6Cp = ashl6

ashl7Cp = ashl7

ashl8Cp = ashl8

SSh = ^42 ; Select Shift Source

SShCROM = SSh[0] ; Coefficient ROM value specifies shift

SShInst = SSh[1] ; Instruction

M = ^43 ; ALU Mode: 0=Logic, 1=Arithmetic, set below

opPG = ^44 ; ALU Operation Bit Bit Base

* Logic Operations (ALU M=0)

tB = opPG[0] ; bitwise B (transfer)

AandB = opPG[1] ; bitwise A and B

nAandB = opPG[2] ; bitwise !A and B

zeros = opPG[3] ; bitwise 000...000

nAorB = opPG[4] ; bitwise !A or B

AxnorB = opPG[5] ; bitwise A xnor B

nA = opPG[6] ; bitwise !A

AnorB = opPG[7] ; bitwise !(A or B)

AorB = opPG[8] ; bitwise A or B

tA = opPG[9] ; bitwise A (transfer)

AxorB = opPG[10] ; bitwise A xor B

AandnB = opPG[11] ; bitwise A and !B

ones = opPG[12] ; bitwise 111...111

AornB = opPG[13] ; bitwise A or !B

AnandB = opPG[14] ; bitwise !(A and B)

nB = opPG[15] ; bitwise !B

* Arithmetic Operations (ALU M=1)

Bplus1 = opPG[0]+M ; B+1

AplusBplusCin = opPG[1]+M ; A+B+Cin

abs1CB = opPG[2]+M ; Abs(B), 1's complement if input is negative

expMB = opPG[3]+M ; Given B, generate correction for fraction part of exp(B)

logB = opPG[4]+M ; Log(A+B)

BminusA = opPG[5]+M ; B-A

negB = opPG[6]+M ; -B, 2's complement of input; for 1's compl use nB

BminusAminus1 = opPG[7]+M ; B-A-1

; = opPG[8]+M ; (A or B)+Cin

AminusB = opPG[9]+M ; A-B

AplusB = opPG[10]+M ; A+B

; = opPG[11]+M ; (B or A)+B+Cin

BplusCin = opPG[12]+M ; B+Cin

expIB = opPG[13]+M ; Generate integer part of exp(B)

; = opPG[14]+M ; (A and B)-1+Cin

Bminus1 = opPG[15]+M ; B-1

******************** Coefficient ROM Addresses ********************

FlOnGnL2 = AddrCROM[0]

ThELd2 = AddrCROM[1]

SpEL2 = AddrCROM[2]

AttEL2 = AddrCROM[3]

RelEL2 = AddrCROM[4]

ThISLd2 = AddrCROM[5]

SpIL2 = AddrCROM[6]

AttISL2 = AddrCROM[7]

RelISL2 = AddrCROM[8]

ThIFLd2 = AddrCROM[9]

AttIFL2 = AddrCROM[10]

RelIFL2 = AddrCROM[11]

ThOLrel2 = AddrCROM[12]

AttOL2 = AddrCROM[13]

RelOL2 = AddrCROM[14]

; = AddrCROM[15]

FlOnGnH2 = AddrCROM[16]

ThEHd2 = AddrCROM[17]

SpEH2 = AddrCROM[18]

AttEH2 = AddrCROM[19]

RelEH2 = AddrCROM[20]

ThISHd2 = AddrCROM[21]

SpIH2 = AddrCROM[22]

AttISH2 = AddrCROM[23]

RelISH2 = AddrCROM[24]

ThIFHd2 = AddrCROM[25]

AttIFH2 = AddrCROM[26]

RelIFH2 = AddrCROM[27]

ThOHrel2 = AddrCROM[28]

AttOH2 = AddrCROM[29]

RelOH2 = AddrCROM[30]

; = AddrCROM[31]

Vol2 = AddrCROM[32]

ARU = AddrCROM[33]

PhsRv = AddrCROM[34]

GainDg2 = AddrCROM[35]

HPDCFc = AddrCROM[36]

MAXId2 = AddrCROM[37]

halfFS = AddrCROM[38]

RcvrTrim = AddrCROM[39]

BSFbl0 = AddrCROM[40]

nBSFal1div2 = AddrCROM[41]

BSFal2div2 = AddrCROM[42]

BSFbh0div2 = AddrCROM[43]

nBSFal1div4 = AddrCROM[44]

BSFal2div4 = AddrCROM[45]

; = AddrCROM[46]

; = AddrCROM[47]

************************ Condition Codes ************************

Not = ^4<> ; Inverses Condition (hardware)

Never = 0 ; Never Jump (Implied)

Always = NOT Never ; Always Jump

Return = ^5 ; Return To Address In Subroutine Register

Call = ^6 ; Save Next Address In Subroutine Register

ResetSync = ^7 ; "Do" Bit To Reset Sync Flag (Careful!)

If = 0 ; Add "English" For Readability

Cond1 = 1 ; Spare Status Condition 1 (LSB)

Cond2 = 2 ; Spare Status Condition 2

Cond3 = 3 ; Spare Status Condition 3 (MSB)

ARU_Busy = 4 ; ARU Is Busy

Sync = 5 ; 20kHz Wait Flag

Test0 = 6 ; Test Flag 0

Test1 = 7 ; Test Flag 1

Zero = 8 ; ALU Result Is Zero

Over = 9 ; ALU Result Has Overflowed

OF = Over ; (for compatibility w/ Slava's Verilog)

Carry = 10 ; ALU Carry Flag Is Set

C = Carry ; (for compatibility w/ Slava's Verilog)

Sign = 11 ; ALU Result Is Negative

Minus = Sign ; (colloquial to match Plus)

SS = Sign ; (for compatibility w/ Slava's Verilog)

Plus = 12 ; Composite: !(Sign|Zero)

Sign_Over = 13 ; Composite: (Sign XNOR Over) for "Greater-than-or-Equal" even if Overflow

GE = Sign_Over ; "Greater-than-or-Equal" (easier mnemonic); for use after subtraction

LT = NOT GE ; "Less Than"; for use after subtraction

OverShift = 14 ; Shifter Has Overflowed

CondQ = 15 ; "Noise Color" select, MPY quantization 0=Trunc, 1=Round,(formerly condM)

LIST ON

На основании этого кода можно привести пример программы для коррекции частотной характеристики звукового сигнала (в частности для людей, имеющих нарушения со слухом)

*************************************************************************************************

Include def_inst.sma

*==========================================================================

*==========================================================================

*==========================================================================

* Registers Usage:

*

* X Registers:

* ------------

* Rx0: (p1/2,store)(p1/2,store)

* Rx1: (s7/8,store)(s9,temp)(s7,store)

* Rx2: (s9/10,store)(s5,temp)(s9/10,store)

* Rx3: (s17/18,store)(s19,temp)(s17/18,store)

* Rx4: (s19/20,store)(s15,temp)(s19/20,store)

* Rx5: (s27/28,store)(s22,temp)(s27/28,store)

* Rx6: (s29/30,store)(s11,temp)(s25,temp)(s29/30,store)

* Rx7: (s37/38,store)(s39,temp)(s37/38,store)

* Rx8: (s39/40,store)(s35,temp)(s39/40,store)

* Rx9: (q3,store)(q3,store)

* Rx10: (q7,store)(q7,store)

* Rx11: (VOL2,temp)(GCH2n,temp)

* Rx12: (ThIFLd2,temp)(d7,temp)(GISTL2n,temp)(GISTL2n-GISoL2n,temp) (d8,temp)/(d9,temp)

* (d10,temp)(d15,temp)(d18,temp)(ThIFHd2,temp)(d27,temp)(GISTH2n,temp)

* (GISTH2n-GISoH2n,temp) (d28,temp)/(d29,temp) (d30,temp)(d35,temp)

* Rx13: (GCL2n,temp)

* Rx14: (xlp,temp)

* Rx15: (s21,temp)(xhp,temp)(ymL,temp)

*

* Y Registers:

* ------------

* Ry0: (GEoL2n,store)(GEL2n,store)

* Ry1: (GISoL2n,store)(GISL2n,store)

* Ry2: (GIFoL2n,store)(GIFL2n,store)

* Ry3: (GOoL2n,store)(GOL2n,store)

* Ry4: (GEoH2n,store)(GEH2n,store)

* Ry5: (GISoH2n,store)(GISH2n,store)

* Ry6: (GIFoH2n,store)(GIFH2n,store)

* Ry7: (GOoH2n,store)(GOH2n,store)

* Ry8: (GTL2n,store)(LM,store)(gtLn,temp)(xhp,temp)(ymH,temp)(yadd,temp)

* (ydg,temp)/(ypr,temp)/(yaru,temp) (yrt,temp)

* Ry9: (GainDg2,temp) ( (15.35-GainDg2),temp )

* Ry10:

* Ry11:

* Ry12: (s6,temp)(xabsL,temp)(q1,temp)(q2,temp)(xdetL,temp)(XLd2,temp)[ (15.35-GainDg2) -XLd2 ]

* (d21,temp)(d22,temp)(GETH2n,temp)(GETH2n-GEoH2n,temp) (d23,temp)/(d24,temp) (d25,temp)

* (xlp,temp)

* Ry13: (s21,temp)(s29,temp)(s26,temp)(xlp,temp)(s16,temp)(xhp,temp)(s36,temp)(temp)(d6,temp)

* (d11,temp)(d12,temp)(GIFTL2n,temp)(GIFTL2n-GIFoL2n,temp) (d13,temp)/(d14,temp)

* (temp2,temp)(d26,temp)(d31,temp)(d32,temp)(GIFTH2n,temp) (GIFTH2n-GIFoH2n,temp)

* (d33,temp)/(d34,temp)

* Ry14: (xhpdc,temp)(xlp1,temp)(xhp1,temp)(s31,temp)(s32,temp)(d1,temp)(d2,temp)(GETL2n,temp)

* (GETL2n-GEoL2n,temp) (d3,temp)/(d4,temp) (GOTL2n,temp)(GOTL2n-GOoL2n,temp)

* (d16,temp)/(d17,temp) (GCH2n,temp)(GTH2n,temp)(HM,temp)(gtHn,temp)

* Ry15: (p3,temp)(s1,temp)(s2,temp)(s11,temp)(s12,temp)(xabsH,temp)(q5,store)(q6,store)

* (xdetH,temp)(XHd2,temp)[ (15.35-GainDg2) -XHd2 ](GOTH2n,temp)(GOTH2n-GOoH2n,temp)

* (d36,temp)/(d37,temp) (d38,temp) (testPh)

*

*

*==========================================================================

* Основная программа

*----------------------------------------------------------------------------------------

* Initialize all Registers to Zero

InitZero:

* (01) Rx[0], Ry[0] = 0

zeros sshInst nsh SE dstgRxRy AxR[0] dstAx srcxALU AyR[0] dstAy srcyALU

* (02) Rx[1], Ry[1] = 0

zeros sshInst nsh SE dstgRxRy AxR[1] dstAx srcxALU AyR[1] dstAy srcyALU

* (03) Rx[2], Ry[2] = 0

zeros sshInst nsh SE dstgRxRy AxR[2] dstAx srcxALU AyR[2] dstAy srcyALU

* (04) Rx[3], Ry[3] = 0

zeros sshInst nsh SE dstgRxRy AxR[3] dstAx srcxALU AyR[3] dstAy srcyALU

* (05) Rx[4], Ry[4] = 0

zeros sshInst nsh SE dstgRxRy AxR[4] dstAx srcxALU AyR[4] dstAy srcyALU

* (06) Rx[5], Ry[5] = 0

zeros sshInst nsh SE dstgRxRy AxR[5] dstAx srcxALU AyR[5] dstAy srcyALU

* (07) Rx[6], Ry[6] = 0

zeros sshInst nsh SE dstgRxRy AxR[6] dstAx srcxALU AyR[6] dstAy srcyALU

* (08) Rx[7], Ry[7] = 0

zeros sshInst nsh SE dstgRxRy AxR[7] dstAx srcxALU AyR[7] dstAy srcyALU

* (09) Rx[8], Ry[8] = 0

zeros sshInst nsh SE dstgRxRy AxR[8] dstAx srcxALU AyR[8] dstAy srcyALU

* (09b) Rx[9], Ry[9] = 0

zeros sshInst nsh SE dstgRxRy AxR[9] dstAx srcxALU AyR[9] dstAy srcyALU

* (010) Load GainDg2 into register so it can be added to another CROM value

* GainDg2 = GainDg2

* ByR[9] ACROM

*

tA sshInst nshCp SE srcACROM dstgRy ByR[9] dstBy srcyALU GainDg2

* (011) Rx[10], Ry[10] = 0

zeros sshInst nsh SE dstgRxRy AxR[10] dstAx srcxALU AyR[10] dstAy srcyALU

* (012) Rx[11], Ry[11] = 0

zeros sshInst nsh SE dstgRxRy AxR[11] dstAx srcxALU AyR[11] dstAy srcyALU

* (013) Rx[12], Ry[12] = 0

zeros sshInst nsh SE dstgRxRy AxR[12] dstAx srcxALU AyR[12] dstAy srcyALU

* (014) Rx[13], Ry[13] = 0

zeros sshInst nsh SE dstgRxRy AxR[13] dstAx srcxALU AyR[13] dstAy srcyALU

* (015) Rx[14], Ry[14] = 0

zeros sshInst nsh SE dstgRxRy AxR[14] dstAx srcxALU AyR[14] dstAy srcyALU

* (016) Rx[15], Ry[15] = 0

zeros sshInst nsh SE dstgRxRy AxR[15] dstAx srcxALU AyR[15] dstAy srcyALU

* (017) Intermediate result for calculating ThOLd2 & ThOHd2

* (15.35 - GainDg2) = MAXId2 - GainDg2

* AyR[9] BCROM AyR[9]

*

BminusA sshInst nshCp SE srcAy srcBCROM dstgRy AyR[9] dstAy srcyALU MAXId2

*

*

*----------------------------------------------------------------------------------------

*----------------------------------------------------------------------------------------

* (1)

* (a) Initial Home Position:

* (i) Synchronize to 128 steps per program cycle, wait until synchronized

* (ii) EEPROM updates here

* (iii) Coeff ROM selections updated here

*

* (b) filler instruction: Input compression Fast L channel

* ThIFLd2 = ThIFLd2

* AxR[12] ACROM

*

Home: tA sshInst nsh SE srcACROM dstgRx AxR[12] dstAx srcxALU ThIFLd2, NOT Sync @ . ; Home

*----------------------------------------------------------------------------------------

* (2)

* (a) On 2nd program instruction, ResetSync immediately after sync is true

*

* (b) DC Bias Reject Filter instruction

* p3 = p1/2 + xi

* AyR[15] AxR[0] BDF

*

AplusB sshInst nshCp SE srcAx srcBDF dstgRy AxR[0] AyR[15] dstAy srcyALU, ResetSync@0

*----------------------------------------------------------------------------------------

* (3)

* (a) DC Bias Reject Filter instruction

* xhpdc = HPDCFc * p3

* AyR[14] CROM ByR[15]

*

MPYCROM round dstgRy AyR[14] ByR[15] dstAy srcyMPY HPDCFc

*----------------------------------------------------------------------------------------

* (4) Note: Instruction (4)originally intended to form 1 instruction with (3). But only one

* CROM access allowed per instruction, so broke up into 2 instructions.

*

* (a) filler instruction: Input compression L channel constant gain

* VOL2 = VOL2

* AxR[11] ACROM

*

tA sshInst nsh SE srcACROM dstgRx AxR[11] dstAx srcxALU VOL2

*----------------------------------------------------------------------------------------

* (5)

* (a) HPDC Reject filter

* p1/2 = xhpdc - xi

* AxR[0] ByR[14] ADF

*

* (b) BSF filter

* s1 = BSFbl0 * xhpdc

* AyR[15] CROM ByR[14]

*

BminusA sshInst nsh SE srcADF srcBy dstgRxRy AxR[0] dstAx srcxALU ByR[14] AyR[15] dstAy srcyMPY MPYCROM round BSFbl0

*----------------------------------------------------------------------------------------

* (6) Band Split Filter

* (a) s2 = halfFS * s1

* ByR[15] CROM ByR[15]

*

* (b) s9 = s1 + s7/8

* AxR[1] ByR[15] AxR[1]

*

AplusB sshInst nshCp SE srcAx srcBy dstgRxRy AxR[1] dstAx srcxALU MPYCROM round ByR[15] dstBy srcyMPY halfFS

*----------------------------------------------------------------------------------------

* (7) Band Split Filter

* (a) (xlp1 = (s2 + s9/10) * 2 )Clip if OF

* ByR[14] AyR[15] BxR[2]

*

* (b) s21 = BSFbh0div2 * xhpdc

* AxR[15] CROM ByR[14]

*

AplusB sshInst ashl1Cp SE srcAy srcBx dstgRxRy AxR[15] BxR[2] dstAx srcxMPY MPYCROM round AyR[15] ByR[14] dstBy srcyALU BSFbh0div2

*----------------------------------------------------------------------------------------

* (8) Band Split Filter

* (a) s21 = s21 , xfer from X reg to Y reg

* AyR[13] AxR[15]

*

* (b) s5 = nBSFal1div2 * xlp1

* BxR[2] CROM ByR[14]

*

tA sshInst nsh SE srcAx dstgRxRy AxR[15] BxR[2] dstBx srcxMPY MPYCROM round AyR[13] ByR[14] dstAy srcyALU nBSFal1div2

*----------------------------------------------------------------------------------------

* (9) Band Split Filter

* (a) s29 = s27/28 - s21

* ByR[13] AxR[5] ByR[13]

*

* (b) s22 = halfFS * s21

* AxR[5] CROM ByR[13]

*

AminusB sshInst nshCp SE srcAx srcBy dstgRxRy AxR[5] dstAx srcxMPY MPYCROM round ByR[13] dstBy srcyALU halfFS

*----------------------------------------------------------------------------------------

* (10) Band Split Filter

* (a) (s9/10 = s9 - s5 ) Clip if OF

* AxR[2] BxR[1] AxR[2]

*

* (b) s6 = BSFal2div2 * xlp1

* AyR[12] CROM ByR[14]

*

BminusA sshInst nshCp SE srcAx srcBx dstgRxRy AxR[2] BxR[1] dstAx srcxALU MPYCROM round AyR[12] ByR[14] dstAy srcyMPY BSFal2div2

*----------------------------------------------------------------------------------------

* (11) Band Split Filter

* (a) (xhp1 = (s22 + s29/30) * 4)Clip if OF

* ByR[14] AxR[5] BxR[6]

*

* (b) s11 = BSFbl0 * xlp1

* BxR[6] CROM ByR[14]

*

AplusB sshInst ashl2Cp SE srcAx srcBx dstgRxRy AxR[5] BxR[6] dstBx srcxMPY MPYCROM round ByR[14] dstBy srcyALU BSFbl0

*----------------------------------------------------------------------------------------

* (12) Band Split Filter

* (a) (s7 = s2 - s6 ) Clip if OF

* AxR[1] ByR[15] AyR[12]

*

BminusA sshInst nshCp SE srcAy srcBy dstgRx AxR[1] dstAx srcxALU AyR[12] ByR[15]

*----------------------------------------------------------------------------------------

* (13) Band Split Filter

* (a) s11 = s11 , xfer from X reg to Y reg

* AyR[15] AxR[6]

*

* (b) s25 = nBSFal1div4 * xhp1

* AxR[6] CROM ByR[14]

*

tA sshInst nsh SE srcAx dstgRxRy AxR[6] dstAx srcxMPY MPYCROM round AyR[15] ByR[14] dstAy srcyALU nBSFal1div4

*----------------------------------------------------------------------------------------

* (14) Band Split Filter

* (a) (s19 = s11 + s17/18 ) Clip if OF

* AxR[3] ByR[15] AxR[3]

*

* (b) s12 = halfFS * s11

* ByR[15] CROM ByR[15]

*

AplusB sshInst nshCp SE srcAx srcBy dstgRxRy AxR[3] dstAx srcxALU MPYCROM round ByR[15] dstBy srcyMPY halfFS

*----------------------------------------------------------------------------------------

* (15) Band Split Filter

* (a) (s29/30 = s29 - s25 ) Clip if OF

* BxR[6] AyR[13] BxR[6]

*

* (b) s26 = BSFal2div4 * xhp1

* AyR[13] CROM ByR[14]

*

AminusB sshInst nshCp SE srcAy srcBx dstgRxRy BxR[6] dstBx srcxALU MPYCROM round AyR[13] ByR[14] dstAy srcyMPY BSFal2div4

*----------------------------------------------------------------------------------------

* (16) Band Split Filter

* (a) (s27/28 = s22 - s26 ) Clip if OF

* BxR[5] BxR[5] AyR[13]

*

* (b) s31 = BSFbh0div2 * xhp1

* ByR[14] CROM ByR[14]

*

BminusA sshInst nshCp SE srcAy srcBx dstgRxRy BxR[5] dstBx srcxALU MPYCROM round AyR[13] ByR[14] dstBy srcyMPY BSFbh0div2

*----------------------------------------------------------------------------------------

* (17) Band Split Filter

* (a) (xlp = (s12 + s19/20) * 2 ) Clip if OF

* AxR[14] AyR[15] BxR[4]

*

* (b) ByR[13] = "

*

AplusB sshInst ashl1Cp SE srcAy srcBx dstgRxRy AxR[14] BxR[4] dstAx srcxALU AyR[15] ByR[13] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (18) Band Split Filter

* (a) (s39 = s37/38 - s31 ) Clip if OF

* AxR[7] AxR[7] ByR[14]

*

* (b) s32 = halfFS * s31

* ByR[14] CROM ByR[14]

*

AminusB sshInst nshCp SE srcAx srcBy dstgRxRy AxR[7] dstAx srcxALU MPYCROM round ByR[14] dstBy srcyMPY halfFS

*----------------------------------------------------------------------------------------

* (19)

* (a) L channel detection filter

* xabsL = abs1C( xlp )

* AyR[12] ByR[13]

*

* (b) Band Split Filter

* s15 = nBSFal1div2 * xlp

* AxR[4] CROM ByR[13]

*

abs1CB sshInst nsh SE srcBy dstgRxRy AyR[12] ByR[13] dstAy srcyALU MPYCROM round AxR[4] dstAx srcxMPY nBSFal1div2

*----------------------------------------------------------------------------------------

* (20) Band Split Filter instruction

* (a) (s19/20 = s19 - s15 ) Clip if OF

* AxR[4] BxR[3] AxR[4]

*

* (b) s16 = BSFal2div2 * xlp

* ByR[13] CROM ByR[13]

*

BminusA sshInst nshCp SE srcAx srcBx dstgRxRy AxR[4] BxR[3] dstAx srcxALU MPYCROM round ByR[13] dstBy srcyMPY BSFal2div2

*----------------------------------------------------------------------------------------

* (21) Band Split Filter

* (a) (s17/18 = s12 - s16 ) Clip if OF

* AxR[3] ByR[15] AyR[13]

*

BminusA sshInst nshCp SE srcAy srcBy dstgRx AxR[3] dstAx srcxALU AyR[13] ByR[15]

*----------------------------------------------------------------------------------------

* (22) Band Split Filter

* (a) (xhp = (s32 + s39/40) * 4 ) Clip if OF

* ByR[13] AyR[14] BxR[8]

* (b) AxR[15]

*

AplusB sshInst ashl2Cp SE srcAy srcBx dstgRxRy AxR[15] BxR[8] dstAx srcxALU AyR[14] ByR[13] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (23)

* (a) filler instruction: H channel detection filter

* xabsH = abs1C( xhp )

* AyR[15] ByR[13]

*

* (b) Band Split Filter

* s35 = nBSFal1div4 * xhp

* AxR[8] CROM ByR[13]

*

abs1CB sshInst nsh SE srcBy dstgRxRy AxR[8] dstAx srcxMPY MPYCROM round AyR[15] ByR[13] dstAy srcyALU nBSFal1div4

*----------------------------------------------------------------------------------------

* (24) Band Split Filter

* (a) (s39/40 = s39 - s35 ) Clip if OF

* AxR[8] BxR[7] AxR[8]

*

* (b) s36 = BSFal2div4 * xhp

* ByR[13] CROM ByR[13]

*

BminusA sshInst nshCp SE srcAx srcBx dstgRxRy AxR[8] BxR[7] dstAx srcxALU MPYCROM round ByR[13] dstBy srcyMPY BSFal2div4

*----------------------------------------------------------------------------------------

* (25) Band Split Filter

* (a) (s37/38 = s32 - s36 ) Clip if OF

* AxR[7] ByR[14] AyR[13]

*

BminusA sshInst nshCp SE srcAy srcBy dstgRx AxR[7] dstAx srcxALU AyR[13] ByR[14]

*----------------------------------------------------------------------------------------

* (26) L channel detection filter

* (a) (q1 = xabsL - q3 ) Clip if OF

* ByR[12] ByR[12] AxR[9]

*

BminusA sshInst nshCp SE srcAx srcBy dstgRy AxR[9] ByR[12] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (27) L channel detection filter

* (a) q2 = 2^-7 * q1

* AyR[12] AyR[12]

*

tA sshInst ashr7 SE srcAy dstgRy AyR[12] dstAy srcyALU

*----------------------------------------------------------------------------------------

* (28) L channel detection filter

* (a) (xdetL = q2 + q3 ) Clip if OF

* AyR[12] AyR[12] BxR[9]

*

* (b) q3

* BxR[9]

*

AplusB sshInst nshCp SE srcAy srcBx dstgRxRy BxR[9] dstBx srcxALU AyR[12] dstAy srcyALU

*----------------------------------------------------------------------------------------

* (29) H channel detection filter

* (a) (q5 = xabsH - q7 ) Clip if OF

* ByR[15] ByR[15] AxR[10]

*

BminusA sshInst nshCp SE srcAx srcBy dstgRy AxR[10] ByR[15] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (30) H channel detection filter

* (a) q6 = 2^-6 * q5

* AyR[15] AyR[15]

*

tA sshInst ashr6 SE srcAy dstgRy AyR[15] dstAy srcyALU

*----------------------------------------------------------------------------------------

* (31) H channel detection filter

* (a) (xdetH = q6 + q7 ) Clip if OF

* AyR[15] AyR[15] BxR[10]

*

* (b) q7 = "

* BxR[10]

*

AplusB sshInst nshCp SE srcAy srcBx dstgRxRy BxR[10] dstBx srcxALU AyR[15] dstAy srcyALU

*----------------------------------------------------------------------------------------

* (32) L channel detector

* (a) XLd2 = log2( xdetL )

* ByR[12] ByR[12]

*

logB sshInst nsh SE srcBy dstgRy ByR[12] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (33) L channel DGC instructions

* (a) (GCL2n = FLONGNL2 + VOL2 ) Clip if OF

* AxR[13] ACROM BxR[11]

*

AplusB sshInst nshCp SE srcACROM srcBx dstgRx AxR[13] BxR[11] dstAx srcxALU FLONGNL2

*----------------------------------------------------------------------------------------

* (34) L channel DGC instructions

* (a) (d1 = ThELd2 - XLd2 ) Clip if OF

* ByR[14] BCROM AyR[12]

*

BminusA sshInst nshCp SE srcAy srcBCROM dstgRy AyR[12] ByR[14] dstBy srcyALU ThELd2

*----------------------------------------------------------------------------------------

* (35) L channel DGC instructions

* (a) temp = SpEL2 + SpEL2

* AyR[13] ACROM BCROM

*

AplusB sshInst nsh SE srcACROM srcBCROM dstgRy AyR[13] dstAy srcyALU SpEL2

*----------------------------------------------------------------------------------------

* (36) L channel DGC instructions

* (a) filler instruction: Input compression Slow L subsystem

* (d6 = ThISLd2 - XLd2 ) Clip if OF

* ByR[13] BCROM AyR[12]

*

* (b) test if need to multiply by (SpEL2 = 0)

*

BminusA sshInst nshCp SE srcAy srcBCROM dstgRy AyR[12] ByR[13] dstBy srcyALU ThISLd2, OF @ SpEL2zero ; . +2

*----------------------------------------------------------------------------------------

* (37) L channel DGC instructions

* (a) d2 = SpEL2 *S d1

* ByR[14] ACROM ByR[14]

*

SpEL2norm:

tB sshCROM SE srcBy dstgRy ByR[14] dstBy srcyALU SpEL2, Always @ ContinueToEL ;. +2

*----------------------------------------------------------------------------------------

* (38) L channel DGC instructions

* (a) d2 = 0, if overflow, zero output

* AyR[14] ALU

*

SpEL2zero:

zeros sshInst nsh SE dstgRy AyR[14] dstAy srcyALU

*----------------------------------------------------------------------------------------

* (39) L channel DGC instructions

* (a) GETL2n = GCL2n + d2

* ByR[14] AxR[13] ByR[14]

*

ContinueToEL:

AplusB sshInst nshCp SE srcAx srcBy dstgRy AxR[13] ByR[14] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (40) L channel DGC instructions

* (a) (GETL2n - GEoL2n) = GETL2n - GEoL2n

* ByR[14] ByR[14] AyR[0]

*

BminusA sshInst nshCp SE srcAy srcBy dstgRy AyR[0] ByR[14] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (41)

* (a) filler instruction: DGC Input compression Fast L subsystem

* (d11 = ThIFLd2 - XLd2 ) Clip if OF

* ByR[13] BxR[12] AyR[12]

*

* (b) filler instruction: DGC Input compression Slow L subsystem

* d7 = SpIL2 * d6

* BxR[12] CROM ByR[13]

*

* (c) Expansion L channel: attack or release?

*

BminusA sshInst nshCp SE srcAy srcBx dstgRxRy BxR[12] dstBx srcxMPY MPYCROM trunc AyR[12] ByR[13] dstBy srcyALU SpIL2, GE @ ReleaseEL ;. +3

*----------------------------------------------------------------------------------------

* (42) L channel DGC instructions

* (a) d3 = AttEL2 *S (GETL2n - GEoL2n)

* ByR[14] CROM ByR[14]

*

AttackEL:

tA sshCROM SE srcBy dstgRy ByR[14] dstBy srcyALU AttEL2

*----------------------------------------------------------------------------------------

* (43) L channel DGC instructions

* (a) (GEL2n = GEoL2n + d3 ) Clip if OF

* AyR[0] AyR[0] ByR[14]

*

AplusB sshInst nshCp SE srcAy srcBy dstgRy AyR[0] ByR[14] dstAy srcyALU, Always @ ResumeEL ;. +3

*----------------------------------------------------------------------------------------

* (44) L channel DGC instructions

* (a) d4 = RelEL2 *S (GETL2n - GEoL2n)

* ByR[14] CROM ByR[14]

*

ReleaseEL:

tA sshCROM SE srcBy dstgRy ByR[14] dstBy srcyALU RelEL2

*----------------------------------------------------------------------------------------

* (45) L channel DGC instructions

* (a) (GEL2n = GEoL2n + d4 ) Clip if OF

* AyR[0] AyR[0] ByR[14]

*

AplusB sshInst nshCp SE srcAy srcBy dstgRy AyR[0] ByR[14] dstAy srcyALU

*----------------------------------------------------------------------------------------

* (46) L channel DGC instructions

* (a) (d5 = GEL2n - GCL2n ) Clip if OF

* AyR[14] ByR[0] AxR[13]

*

ResumeEL:

BminusA sshInst nshCp SE srcAx srcBy dstgRy AxR[13] AyR[14] ByR[0] dstAy srcyALU

*----------------------------------------------------------------------------------------

* (47) L channel DGC instructions

* (a) filler instruction: DGC Input compression Slow L subsystem

* (GISTL2n = GCL2n + d7 ) Clip if OF

* BxR[12] AxR[13] BxR[12]

*

* (b) filler instruction: DGC Input compression Fast L subsystem

* d12 = SpIL2 * d11

* ByR[13] CROM ByR[13]

*

* (c) test for Expansion L subsystem min Gain

*

AplusB sshInst nshCp SE srcAx srcBx dstgRxRy AxR[13] BxR[12] dstBx srcxALU MPYCROM trunc ByR[13] dstBy srcyMPY SpIL2, LT @ MinIsGEL2n ;. +2

*----------------------------------------------------------------------------------------

* (48) L channel DGC instructions

* (a) GTL2n = GCL2n

* AyR[8] AxR[13]

*

MinIsGCL2n:

tA sshInst nsh SE srcAx dstgRy AxR[13] AyR[8] dstAy srcyALU, Always @ ContinueToISL ;. +2

*----------------------------------------------------------------------------------------

* (49) L channel DGC instructions

* (a) GTL2n = GEL2n

* ByR[8] AyR[0]

*

MinIsGEL2n:

tA sshInst nsh SE srcAy dstgRy AyR[0] ByR[8] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (50) L channel DGC instructions

* (a) ( (GISTL2n - GISoL2n) = GISTL2n - GISoL2n) ) Clip if OF

* BxR[12] BxR[12] AyR[1]

*

ContinueToISL:

BminusA sshInst nshCp SE srcAy srcBx dstgRxRy BxR[12] dstBx srcxALU AyR[1]

*----------------------------------------------------------------------------------------

* (51) L channel DGC instructions

* (a) filler instruction: IFL subsystem

* (GIFTL2n = d12 + GCL2n ) Clip if OF

* AyR[13] AyR[13] BxR[13]

*

* (b) ISL subsystem: attack or release?

*

AplusB sshInst nshCp SE srcAy srcBx dstgRy BxR[13] AyR[13] dstAy srcyALU, GE @ ReleaseISL ;. +3

*----------------------------------------------------------------------------------------

* (52) L channel DGC instructions

* (a) d8 = AttISL2 *S (GISTL2n - GISoL2n)

* BxR[12] CROM BxR[12]

*

AttackISL:

tA sshCROM SE srcBx dstgRx BxR[12] dstBx srcxALU AttISL2

*----------------------------------------------------------------------------------------

* (53) L channel DGC instructions

* (a) (GISL2n = d8 + GISoL2n ) Clip if OF

* ByR[1] AxR[12] ByR[1]

*

AplusB sshInst nshCp SE srcAx srcBy dstgRy AxR[12] ByR[1] dstBy srcyALU, Always @ ResumeISL ;. +3

*----------------------------------------------------------------------------------------

* (54) L channel DGC instructions

* (a) d9 = RelISL2 *S (GISTL2n - GISoL2n)

* BxR[12] CROM BxR[12]

*

ReleaseISL:

tA sshCROM SE srcBx dstgRx BxR[12] dstBx srcxALU RelISL2

*----------------------------------------------------------------------------------------

* (55) L channel DGC instructions

* (a) (GISL2n = d9 + GISoL2n ) Clip if OF

* ByR[1] AxR[12] ByR[1]

*

AplusB sshInst nshCp SE srcAx srcBy dstgRy AxR[12] ByR[1] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (56) L channel DGC instructions

* (a) (d10 = GISL2n - GTL2n ) Clip if OF

* AxR[12] ByR[1] AyR[8]

*

ResumeISL:

BminusA sshInst nshCp SE srcAy srcBy dstgRx AxR[12] dstAx srcxALU AyR[8] ByR[1]

*----------------------------------------------------------------------------------------

* (57)

* (a) filler instruction: DGC Output limiting L channel subsystem: GOTL2n intermediate (last instruction to use XLd2)

* ([ (15.35-GainDg2) - XLd2 ] = (15.35-GainDg2) - XLd2 ) Clip if OF

* AyR[12] ByR[9] AyR[12]

*

* (b) test for ISL subsystem min Gain

*

BminusA sshInst nshCp SE srcAy srcBy dstgRy AyR[12] ByR[9] dstAy srcyALU, GE @ ContinueToIFL ;. +2

*----------------------------------------------------------------------------------------

* (58) L channel DGC instructions

* (a) GTL2n = GISL2n

* ByR[8] AyR[1]

*

MinIsGISL2n:

tA sshInst nsh SE srcAy dstgRy AyR[1] ByR[8] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (59)

* (a) L channel DGC instructions

* ( (GIFTL2n - GIFoL2n) = GIFTL2n - GIFoL2n ) Clip if OF

* ByR[13] ByR[13] AyR[2]

*

* (b) min Gain is GTL2n => keep GTL2n unchanged

MinIsGTL2nISL:

ContinueToIFL:

BminusA sshInst nshCp SE srcAy srcBy dstgRy AyR[2] ByR[13] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (60)

* (a) filler instruction: H channel detector

* XHd2 = log2( xdetH )

* AyR[15] AyR[15]

*

* (b) IFL subsystem: attack or release?

*

logB sshInst nsh SE srcAy dstgRy AyR[15] dstAy srcyALU, GE @ ReleaseIFL ;. +3

*----------------------------------------------------------------------------------------

* (61) L channel DGC instructions

* (a) d13 = AttIFL2 * (GIFTL2n - GIFoL2n)

* ByR[13] CROM ByR[13]

*

AttackIFL:

MPYCROM trunc dstgRy ByR[13] dstBy srcyMPY AttIFL2

*----------------------------------------------------------------------------------------

* (62) L channel DGC instructions

* (a) (GIFL2n = d13 + GIFoL2n ) Clip if OF

* ByR[2] AyR[13] ByR[2]

*

AplusB sshInst nshCp SE srcAy srcBy dstgRy AyR[13] ByR[2] dstBy srcyALU, Always @ ResumeIFL ;. +3

*----------------------------------------------------------------------------------------

* (63) L channel DGC instructions

* (a) d14 = RelIFL2 * (GIFTL2n - GIFoL2n)

* ByR[13] CROM ByR[13]

*

ReleaseIFL:

MPYCROM trunc dstgRy ByR[13] dstBy srcyMPY RelIFL2

*----------------------------------------------------------------------------------------

* (64) L channel DGC instructions

* (a) (GIFL2n = d14 + GIFoL2n ) Clip if OF

* ByR[2] AyR[13] ByR[2]

*

AplusB sshInst nshCp SE srcAy srcBy dstgRy AyR[13] ByR[2] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (65) L channel DGC instructions

* (a) (d15 = GIFL2n - GTL2n ) Clip if OF

* AxR[12] ByR[2] AyR[8]

*

ResumeIFL:

BminusA sshInst nshCp SE srcAy srcBy dstgRx AxR[12] dstAx srcxALU AyR[8] ByR[2]

*----------------------------------------------------------------------------------------

* (66)

* (a) filler instruction: H channel constant gain

* (GCH2n = FLONGNH2 + VOL2 ) Clip if OF

* BxR[11] ACROM BxR[11]

*

* (b) test for IFL subsystem min Gain

*

AplusB sshInst nshCp SE srcACROM srcBx dstgRx BxR[11] dstBx srcxALU, GE @ ContinueToOL ;. +2

*----------------------------------------------------------------------------------------

* (67) L channel DGC instructions

* (a) GTL2n = GIFL2n

* ByR[8] AyR[2]

*

MinIsGIFL2n:

tA sshInst nsh SE srcAy dstgRy AyR[2] ByR[8] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (68)

* (a) OL subsystem instruction: Finish GOTL2n calculation

* GOTL2n = ThOLd2 - XLd2

* = ((ThOL-MAXO)/6) + [(15.35-GainDg2) -XLd2]

* (GOTL2n = ThOLrel2 + [(15.35-GainDg2) -XLd2] ) Clip if OF

* ByR[14] BCROM AyR[12]

*

* (b) min Gain is GTL2n => keep GTL2n unchanged

*

MinIsGTL2nIFL:

ContinueToOL:

AplusB sshInst nshCp SE srcAy srcBCROM dstgRy AyR[12] ByR[14] dstBy srcyALU ThOLrel2

*----------------------------------------------------------------------------------------

* (69) H channel DGC instructions

* (a) OL subsystem instruction

* ((GOTL2n - GOoL2n) = GOTL2n - GOoL2n ) Clip if OF

* ByR[14] ByR[14] AyR[3]

*

BminusA sshInst nshCp SE srcAy srcBy dstgRy AyR[3] ByR[14] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (70) H channel DGC instructions

* (a) filler instruction: EH subsystem

* (d21 = ThEHd2 - XHd2 ) Clip if OF

* ByR[12] BCROM AyR[15]

*

* (b) OL subsystem: attack or release?

*

BminusA sshInst nshCp SE srcAy srcBCROM dstgRy AyR[15] ByR[12] dstBy srcyALU, GE @ ReleaseOL ;. +3

*----------------------------------------------------------------------------------------

* (71) L channel DGC instructions

* (a) d16 = AttOL2 * (GOTL2n - GOoL2n)

* ByR[14] CROM ByR[14]

*

AttackOL:

MPYCROM trunc dstgRy ByR[14] dstBy srcyMPY AttOL2

*----------------------------------------------------------------------------------------

* (72) L channel DGC instructions

* (a) (GOL2n = d16 + GOoL2n ) Clip if OF

* ByR[3] AyR[14] ByR[3]

*

AplusB sshInst nshCp SE srcAy srcBy dstgRy AyR[14] ByR[3] dstBy srcyALU, Always @ ResumeOL ;. +3

*----------------------------------------------------------------------------------------

* (73) L channel DGC instructions

* (a) d17 = RelOL2 * (GOTL2n - GOoL2n)

* ByR[14] CROM ByR[14]

*

ReleaseOL:

MPYCROM trunc dstgRy ByR[14] dstBy srcyMPY RelOL2

*----------------------------------------------------------------------------------------

* (74) L channel DGC instructions

* (a) (GOL2n = d17 + GOoL2n ) Clip if OF

* ByR[3] AyR[14] ByR[3]

*

AplusB sshInst nshCp SE srcAy srcBy dstgRy AyR[14] ByR[3] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (75) L channel DGC instructions

* (a) (d18 = GOL2n - GTL2n ) Clip if OF

* AxR[12] ByR[3] AyR[8]

*

ResumeOL:

BminusA sshInst nshCp SE srcAy srcBy dstgRx AxR[12] dstAx srcxALU AyR[8] ByR[3]

*----------------------------------------------------------------------------------------

* (76)

* (a) filler instruction: DGC constant Gain H subsystem

* GTH2n = GCH2n , preload GCH2n into GTH2n, later if incorrect,

* AyR[14] AxR[11] will overwrite. Otherwise, leave unchanged

*

* (b) test for OL subsystem min Gain

*

tA sshInst nsh SE srcAx dstgRy AxR[11] AyR[14] dstAy srcyALU, GE @ ContinueToEH1 ;. +2

*----------------------------------------------------------------------------------------

* (77) L channel DGC instructions

* (a) GTL2n = GOL2n

* ByR[8] AyR[3]

*

MinIsGOL2n:

tA sshInst nsh SE srcAy dstgRy AyR[3] ByR[8] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (78)

* (a) H channel DGC instructions

* temp2 = SpEH2 + SpEH2

* AyR[13] ACROM BCROM

*

* (b) min Gain is GTL2n => keep GTL2n unchanged

*

MinIsGTL2nOL:

ContinueToEH1:

AplusB sshInst nsh SE srcACROM srcBCROM dstgRy AyR[13] dstAy srcyALU

*----------------------------------------------------------------------------------------

* (79) H channel DGC instructions

* (a) filler instruction: Input compression Slow H subsystem

* d26 = ThISHd2 - XHd2

* ByR[13] BCROM AyR[15]

*

* (b) Test if need to multiply by (SpEH2 = 0)

*

BminusA sshInst nsh SE srcAy srcBCROM dstgRy AyR[15] ByR[13] dstBy srcyALU ThISHd2, OF @ SpEH2zero ;. +2

*----------------------------------------------------------------------------------------

* (80) H channel DGC instructions

* (a) d22 = SpEH2 *S d21

* ByR[12] ACROM ByR[12]

*

SpEH2norm:

tB sshCROM SE srcBy dstgRy ByR[12] dstBy srcyALU SpEH2, Always @ ContinueToEH2 ;. +2

*----------------------------------------------------------------------------------------

* (81) H channel DGC instructions

* (a) d22 = 0

* AyR[12] ALU

*

SpEH2zero:

zeros sshInst nsh SE dstgRy AyR[12] dstAy srcyALU

*----------------------------------------------------------------------------------------

* (82) H channel DGC instructions

* (a) (GETH2n = d22 + GCH2n ) Clip if OF

* AyR[12] AyR[12] BxR[11]

*

ContinueToEH2:

AplusB sshInst nshCp SE srcAy srcBx dstgRy BxR[11] AyR[12] dstAy srcyALU

*----------------------------------------------------------------------------------------

* (83) H channel DGC instructions

* (a) ( (GETH2n - GEoH2n) = GETH2n - GEoH2n ) Clip if OF

* ByR[12] ByR[12] AyR[4]

*

BminusA sshInst nshCp SE srcAy srcBy dstgRy AyR[4] ByR[12] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (84) H channel DGC instructions

* (a) filler instruction: IFH subsystem

* ThIFHd2 = ThIFHd2

* AxR[12] ACROM

*

* (b) EH subsystem: attack or release?

*

tA sshInst nsh SE srcACROM dstgRx AxR[12] dstAx srcxALU ThIFHd2, GE @ ReleaseEH ;. +3

*----------------------------------------------------------------------------------------

* (85) H channel DGC instructions

* (a) d23 = AttEH2 *S (GETH2n - GEoH2n)

* ByR[12] CROM ByR[12]

*

AttackEH:

tB sshCROM SE srcBy dstgRy ByR[12] dstBy srcyALU AttEH2

*----------------------------------------------------------------------------------------

* (86) H channel DGC instructions

* (a) (GEH2n = d23 + GEoH2n ) Clip if OF

* ByR[4] AyR[12] ByR[4]

*

AplusB sshInst nshCp SE srcAy srcBy dstgRy AyR[12] ByR[4] dstBy srcyALU, Always @ ResumeEH ; .+3

*----------------------------------------------------------------------------------------

* (87) H channel DGC instructions

* (a) d24 = RelEH2 *S (GETH2n - GEoH2n)

* ByR[12] CROM ByR[12]

*

ReleaseEH:

tB sshCROM srcBy dstgRy ByR[12] dstBy srcyALU RelEH2

*----------------------------------------------------------------------------------------

* (88) H channel DGC instructions

* (a) (GEH2n = d24 + GEoH2n ) Clip if OF

* ByR[4] AyR[12] ByR[4]

*

AplusB sshInst nshCp SE srcAy srcBy dstgRy AyR[12] ByR[4] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (89) H channel DGC instructions

* (a) (d25 = GEH2n - GCH2n ) Clip if OF

* AyR[12] ByR[4] AxR[11]

*

ResumeEH:

BminusA sshInst nshCp SE srcAx srcBy dstgRy AxR[11] AyR[12] ByR[4] dstAy srcyALU

*----------------------------------------------------------------------------------------

* (90) H channel DGC instructions

* (a) filler instruction: IFH subsystem

* (d31 = ThIFHd2 - XHd2 ) Clip if OF

* ByR[13] BxR[12] AyR[15]

*

* (b) filler instruction: ISH subsystem

* d27 = SpIH2 * d26

* BxR[12] CROM ByR[13]

*

* (c) test for EH subsystem min Gain

*

BminusA sshInst nshCp SE srcAy srcBx dstgRxRy BxR[12] dstBx srcxMPY MPYCROM trunc AyR[15] ByR[13] dstBy srcyALU SpIH2, GE @ ContinueToIH ;. +2

*----------------------------------------------------------------------------------------

* (91) H channel DGC instructions

* (a) GTH2n = GEH2n

* ByR[14] AyR[4]

*

MinIsGEH2n:

tA sshInst nsh SE srcAy dstgRy AyR[4] ByR[14] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (92)

* (a) H channel DGC instructions

* (GISTH2n = d27 + GCH2n ) Clip if OF

* AxR[12] AxR[12] BxR[11]

*

* (b) filler instruction: IFH subsystem

* d32 = SpIH2 * d31

* ByR[13] CROM ByR[13]

*

* (c) min Gain is GCH2n => already loaded into GTH2n previously, don't change value of GTH2n

*

MinIsGCH2n:

ContinueToIH:

AplusB sshInst nshCp SE srcAx srcBx dstgRxRy AxR[12] BxR[11] dstAx srcxALU MPYCROM trunc ByR[13] dstBy srcyMPY SpIH2

*----------------------------------------------------------------------------------------

* (93) H channel DGC instructions

* (a) ( (GISTH2n - GISoH2n) = GISTH2n - GISoH2n ) Clip if OF

* BxR[12] BxR[12] AyR[5]

*

BminusA sshInst nshCp SE srcAy srcBx dstgRx BxR[12] dstBx srcxALU AyR[5]

*----------------------------------------------------------------------------------------

* (94)

* (a) filler instruction: IFH subsystem

* (GIFTH2n = d32 + GCH2n ) Clip if OF

* AyR[13] AyR[13] BxR[11]

*

* (b) ISH subsystem: attack or release?

*

AplusB sshInst nshCp SE srcAy srcBx dstgRy BxR[11] AyR[13] dstAy srcyALU, GE @ ReleaseISH ;. +3

*----------------------------------------------------------------------------------------

* (95) H channel DGC instructions

* (a) d28 = AttISH2 *S (GISTH2n - GISoH2n)

* BxR[12] CROM BxR[12]

*

AttackISH:

tB sshCROM SE srcBx dstgRx BxR[12] dstBx srcxALU AttISH2

*----------------------------------------------------------------------------------------

* (96) H channel DGC instructions

* (a) (GISH2n = d28 + GISoH2n ) Clip if OF

* ByR[5] AxR[12] ByR[5]

*

AplusB sshInst nshCp SE srcAx srcBy dstgRy AxR[12] ByR[5] dstBy srcyALU, Always @ ResumeISH ;. +3

*----------------------------------------------------------------------------------------

* (97) H channel DGC instructions

* (a) d29 = RelISH2 *S (GISTH2n - GISoH2n)

* BxR[12] CROM BxR[12]

*

ReleaseISH:

tB sshCROM SE srcBx dstgRx BxR[12] dstBx srcxALU RelISH2

*----------------------------------------------------------------------------------------

* (98) H channel DGC instructions

* (a) (GISH2n = d29 + GISoH2n ) Clip if OF

* ByR[5] AxR[12] ByR[5]

*

AplusB sshInst nshCp SE srcAx srcBy dstgRy AxR[12] ByR[5] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (99) H channel DGC instructions

* (a) (d30 = GISH2n - GTH2n ) Clip if OF

* AxR[12] ByR[5] AyR[14]

*

ResumeISH:

BminusA sshInst nshCp SE srcAy srcBy dstgRx AxR[12] dstAx srcxALU AyR[14] ByR[5]

*----------------------------------------------------------------------------------------

* (100) H channel DGC instructions

* (a) filler instruction: OH subsystem: GOTH2n intermediate (last instruction using XHd2)

* ([ (15.35-GainDg2) - XHd2 ] = (15.35-GainDg2) - XHd2 ) Clip if OF

* AyR[15] ByR[9] AyR[15]

*

* (b) test for ISH subsystem min Gain

*

BminusA sshInst nshCp SE srcAy srcBy dstgRy AyR[15] ByR[9] dstAy srcyALU, GE @ ContinueToOH2 ;. +2

*----------------------------------------------------------------------------------------

* (101) H channel DGC instructions

* (a) GTH2n = GISH2n

* ByR[14] AyR[5]

*

MinIsGISH2n:

tA sshInst nsh SE srcAy dstgRy AyR[5] ByR[14] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (102)

* (a) IFH subsystem

* ( (GIFTH2n - GIFoH2n) = GIFTH2n - GIFoH2n ) Clip if OF

* ByR[13] ByR[13] AyR[6]

*

* (b) min Gain is GTH2n => keep GTH2n unchanged

*

MinIsGTH2nISH:

ContinueToOH2:

BminusA sshInst nshCp SE srcAy srcBy dstgRy AyR[6] ByR[13] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (103)

* (a) filler instruction: L channel log2 to linear conversion

* LM = expMB( GTL2n )

* ByR[8] ByR[8]

*

* (b) DGC IFH subsystem: attack or release?

*

expMB sshInst nsh SE srcBy dstgRy ByR[8] dstBy srcyALU, GE @ ReleaseIFH ;. +3

*----------------------------------------------------------------------------------------

* (104)H channel DGC instructions

* (a) d33 = AttIFH2 * (GIFTH2n - GIFoH2n)

* ByR[13] CROM ByR[13]

*

AttackIFH:

MPYCROM trunc dstgRy ByR[13] dstBy srcyMPY AttIFH2

*----------------------------------------------------------------------------------------

* (105)H channel DGC instructions

* (a) (GIFH2n = d33 + GIFoH2n ) Clip if OF

* ByR[6] AyR[13] ByR[6]

*

AplusB sshInst nshCp SE srcAy srcBy dstgRy AyR[13] ByR[6] dstBy srcyALU, Always @ ResumeIFH ;. +3

*----------------------------------------------------------------------------------------

* (106)H channel DGC instructions

* (a) d34 = RelIFH2 * (GIFTH2n - GIFoH2n)

* ByR[13] CROM ByR[13]

*

ReleaseIFH:

MPYCROM trunc dstgRy ByR[13] dstBy srcyMPY RelIFH2

*----------------------------------------------------------------------------------------

* (107)H channel DGC instructions

* (a) (GIFH2n = d34 + GIFoH2n ) Clip if OF

* ByR[6] AyR[13] ByR[6]

*

AplusB sshInst nshCp SE srcAy srcBy dstgRy AyR[13] ByR[6] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (108)H channel DGC instructions

* (a) (d35 = GIFH2n - GTH2n ) Clip if OF

* AxR[12] ByR[6] AyR[14]

*

ResumeIFH:

BminusA sshInst nshCp SE srcAy srcBy dstgRx AxR[12] dstAx srcxALU AyR[14] ByR[6]

*----------------------------------------------------------------------------------------

* (109)

* (a) filler instruction: L channel log2 to linear conversion

* gtLn = expIB( LM )

* ByR[8] ByR[8]

*

* (b) min Gain test IFH subsystem

*

expIB sshInst nsh SE srcBy dstgRy ByR[8] dstBy srcyALU, GE @ ContinueToOH ;. +2

*----------------------------------------------------------------------------------------

* (110)H channel DGC instructions

* (a) GTH2n = GIFH2n

* ByR[14] AyR[6]

*

MinIsGIFH2n:

tA sshInst nsh SE srcAy dstgRy AyR[6] ByR[14] dstBy srcyALU

*----------------------------------------------------------------------------------------

* (111)

* (a) DGC Output limiting H channel subsystem: Finish GOTH2n calculation

* GOTH2n = ThOHd2 - XHd2

* = ((ThOH-MAXO)/6) + [(15.35-GainDg2) -XHd2]

* (GOTH2n = ThOHrel2 + [(15.35-GainDg2) -XHd2] ) Clip if OF

* AyR[15] BCROM AyR[15]

*

* (b) min Gain is GTH2n => don't overwrite GTH2n

*

MinIsGTH2nIFH:

ContinueToOH:

AplusB sshInst nshCp SE srcAy srcBCROM dstgRy AyR[15] dstAy srcyALU ThOHrel2

*----------------------------------------------------------------------------------------

* (112)

* (a) DGC Output limiting H channel subsystem

* ( (GOTH2n - GOoH2n) = GOTH2n - GOoH2n ) Clip if OF

* ByR[15] ByR[15] AyR[7]

*