Изобретение относится к области электроники и микропроцессорной техники и может быть использовано в конструкциях современных, высокопроизводительных RISC-микропроцессоров и микроконтроллеров для повышения быстродействия и упрощения их конструкции.

В общем случае стек (от англ. stack - стопка) - структура данных, представляющая из себя список элементов, организованных по принципу LIFO (англ. Last In - First Out, «последним пришел - первым вышел»).

В рамках заявляемого технического решения термин стек употребляется применительно к области памяти процессора, организованной по принципу "магазина" (по аналогии с магазином в огнестрельном оружии - стрельба начнется с патрона, заряженного в магазин последним) и обеспечивающей сохранение адресов возврата при вызове подпрограмм и обслуживании прерываний для последующей передачи управления в точку вызова подпрограммы или на адрес, перед которым был выполнен переход к процедуре обслуживания прерывания.

Отметим также, что архитектура RISC (Reduced Instruction Set Computer - компьютер с сокращенным набором команд) является основой современных высокопроизводительных микропроцессоров и микроконтроллеров.

Основными требованиями архитектуры RISC являются:

1. Любая операция должна выполняться за один такт.

2. Система команд должна содержать минимальное количество наиболее часто используемых команд одинаковой длины.

3. Операции обработки данных реализуются только в формате регистр-регистр. Обмен между регистрами и памятью выполняется только командами загрузки-записи.

В дальнейшем эти требования были несколько смягчены, и в настоящее время незыблемым остается только требование: обработка данных ведется только командами в формате регистр-регистр. А требование выполнения любой операции за один такт стало трактоваться как выполнение любых операции за одинаковый интервал времени - машинный цикл, или как загрузка конвейера команд в темпе "команда за такт".

Но, тем не менее, соответствие этому требованию позволяет упростить логику декодирования команд благодаря использованию команды фиксированной длины и фиксированного формата, возможность исполнения которых за фиксированный интервал времени позволяет с помощью довольно несложных схемотехнических решений реализовать не только высокую скорость выполнения элементарных операций при сохранении простоты устройства управления и синхронизации процессора, но также организовать как конвейеризацию, так и пространственный параллелизм вычислений.

Следует также отметить, что в наши дни лучшие черты RISC-архитектуры широко заимствуются при разработке современных высокопроизводительных микропроцессоров и микроконтроллеров, в связи с чем технической задачей заявляемого технического решения является создание специфической конструкции аппаратного стека процессора, позволяющей выполнять сложные машинные операции за один такт.

К числу таких сложных операций относятся вызовы подпрограмм и обслуживание прерываний, поскольку при выполнении они предполагают переход на заданный адрес, то есть, запись значения адреса перехода в регистр программного счетчика (PC) процессора, с одновременным сохранением адреса возврата из подпрограммы, то есть, с сохранением текущего значения PC, что довольно сложно реализовать за одинаковый со всеми остальными командами интервал времени.

Рассмотрим, как эта операция реализуется в конструкции характерных представителей семейств микропроцессоров и микроконтроллеров.

Известен микроконтроллер семейства TMS 1000 (pat. US 3988604, pat. US 4024386). Упрощенная блок-схема этого микроконтроллера представлена в его техническом описании (TMS 1000 Series Data Manual, The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group).

В микроконтроллерах этого семейства эффективный адрес при обращении к постоянному запоминающему устройству (ПЗУ) программ (ROM) образуется подачей на его адресные входы текущего содержимого программного счетчика (PROGRAM COUNTER) и содержимого регистра адреса страницы (PAGE ADDRESS REGISTER). Такое разделение обусловлено ограниченностью аппаратных ресурсов микроконтроллера.

При выполнении операции вызова подпрограммы (CALL) текущее состояние программного счетчика сохраняется в регистре возврата из подпрограммы (SUBROUTINE RETURN REGISTER), а содержимое регистра адреса страницы записывается в регистр буфера страницы (PAGE BUFFER REGISTER). После этого в программный счетчик и регистр адреса страницы записывается эффективный адрес перехода к вызываемой подпрограмме из ПЗУ программ, и выполнение операций продолжается с адреса, содержащегося в программном счетчике и регистре адреса страницы.

При выполнении операции возврата из подпрограммы (RETN) на адрес, откуда эта подпрограмма была вызвана, содержимое регистра буфера страницы переписывается в регистр адреса страницы, а программный счетчик загружается значением регистра возврата из подпрограммы. После чего выполнение операций продолжается с эффективного адреса, содержащегося в программном счетчике и регистре адреса страницы, то есть с адреса, откуда была вызвана подпрограмма.

Такое решение представляет собой простейший одноранговый стек, предоставляющий возможностью сохранения лишь одного адреса возврата из подпрограммы или процедуры обслуживания прерывания.

Недостатком подобного решения являются малая глубина вложения вызовов подпрограмм, поскольку регистр буфера страницы и регистр возврата из подпрограммы способны сохранить только один эффективный адрес возврата из подпрограммы, а также невозможность выполнения операции вызова подпрограммы за один такт, поскольку запись адреса перехода к подпрограмме в программный счетчик не может быть выполнена одновременно с сохранением его текущего значения.

Известен процессор семейства ЭВМ PDP (Programmed Data Processor) американской корпорации Digital Equipment Corporation (DEC). В конструкции PDP-8 было найдено элегантное, хотя и несколько необычное, решение: адрес возврата из подпрограммы сохранялся в самой подпрограмме по адресу ее вызова, а выполнение подпрограммы начиналось со следующего адреса.

При выполнении PDP-8 операции вызова подпрограммы по адресу Y (JMS Y) текущее состояние программного счетчика процессора сохраняется по этому адресу - Y, а значение Y+1 заносится в программный счетчик, после чего выполнение операций подпрограммы продолжается с адреса Y+1, содержащегося в программном счетчике до инструкции возврата из подпрограммы (JMPIY). Выполнение этой операции предполагает загрузку PC значением из ячейки памяти с адресом Y, а, следовательно, и возврат управления к месту вызова подпрограммы (PROGRAMMED DATA PROCESSOR-8 USERS HANDBOOK. DIGITAL EQUIPMENT CORPORATION. MAYNARD, MASSACHUSETTS, p.23).

Согласно приведенной в техническом описании блок-схеме PDP-8 (PDP-8 A HIGH SPEED DIGITAL COMPUTER. DIGITAL EQUIPMENT CORPORATION. MAYNARD, MASSACHUSETTS, p.8), в процессе выполнения операции вызова подпрограммы по адресу Y в регистр адреса памяти (MEMORY ADDRESS REGISTER) записывается адрес перехода Y из буферного регистра памяти (MEMORY BUFFER REGISTER) по сигналам генератора основных состояний (MAJOR STATE GENERATOR), управляемого кодом инструкции JMS Y из регистра инструкции (INSTRUCTION REGISTER).

После этого содержимое программного счетчика (PROGRAM COUNTER) через буферный регистр памяти (MEMORY BUFFER REGISTER) заносится в оперативную память (4096-WORD CORE MEMORY) по адресу Y в регистре адреса памяти, а содержимое регистра адреса памяти, содержащее значение адреса перехода Y, переписывается в программный счетчик и инкрементируется. Таким образом начинается выполнение операций подпрограммы с адреса Y+1, содержащегося в программном счетчике.

Роль инструкции возврата из подпрограммы в PDP-8 играет команда перехода по значению, содержащемуся в ячейке памяти. При этом в команде JMPIY заранее программируется переход по значению, содержащемуся в первой ячейке подпрограммы. В результате выполнения инструкции JMPIY содержимое ячейки оперативной памяти по адресу Y через буферный регистр памяти заносится в программный счетчик, что фактически передает управление программой на адрес возврата.

Такая аппаратная реализация механизма возврата из подпрограмм и процедур обслуживания прерываний, по сути, предоставляет свой отдельный одноранговый стек в памяти для каждого вызова подпрограммы или процедуры обслуживания прерывания.

Недостатком такого решения, несмотря на то, что оно значительно увеличивает глубину вложения вызовов подпрограмм, является невозможность выполнения операции вызова подпрограммы за один такт, поскольку запись адреса перехода к подпрограмме в программный счетчик здесь также не может быть выполнена одновременно с сохранением его текущего значения в оперативной памяти. Кроме того, операции обращения к оперативной памяти значительно медленнее операций записи и чтения регистров самого процессора, и подобный принцип сохранения адреса возврата из подпрограммы не позволяет выполнять рекурсивные вызовы подпрограммы из себя самой или процедуры обслуживания прерывания, поскольку новый адрес возврата в этом случае будет занесен в ячейку хранения, но предыдущий адрес возврата, хранящийся в ней, безусловно, будет утерян. К тому же данный механизм сохранения адреса возврата не работоспособен в случае размещения подпрограмм в памяти постоянного запоминающего устройства, запись в которое физически невозможна.

Наиболее близким по технической сущности к заявляемому изобретению, принятым за прототип, является микроконтроллер серии PIC18 фирмы Microchip, который содержит 31-уровневый (в общем случае - N-уровневый) аппаратный стек (31-Level Stack), представленный в виде блок-схемы в фирменном техническом описании (Microchip PIC18(L)F1XK22 Data Sheet, 20-Pin Flash Microcontrollers with nanoWatt XLP Technology. © 2009-2011 Microchip Technology Incorporated. DS41365E - page 10).

В конкретном аппаратном исполнении микроконтроллера Microchip PIC18(L)F1XK22 стек адресов возврата (Return Address Stack) представляет собой отдельную дополнительную область памяти, содержащую 31 регистр (31-Level Stack), и организованную по магазинному типу, причем регистр (ячейка стека), в который производится запись, или из которого производится чтение, определяется специальным указателем стека (Stack Pointer - STKPTR) с логикой управления стеком.

Область стека микроконтроллера PIC18(L)F1XK224 не принадлежит ни к программной области, ни к области данных. Текущее значение программного счетчика (Program Counter - PC) пересылается в стек, когда выполняется команда вызова подпрограммы (CALL) или производится обработка прерывания, при этом указатель стека увеличивается на единицу и указывает на ячейку стека, в которую заносится содержимое PC. В программный счетчик же заносится начальный адрес выполняемой процедуры обработки прерывания или подпрограммы. При выполнении процедуры возврата из подпрограммы (команды RETLW, RETFIE или RETURN), в программный счетчик загружается содержимое текущей ячейки стека, а указатель стека уменьшается на единицу.

Тридцатиодноуровневый аппаратный стек микроконтроллера Microchip PIC18(L)F1XK224 обеспечивает глубину вложений вызовов подпрограмм до 31 с последующим корректным возвратом. При переполнении ограниченного аппаратного стека указатель стека снова указывает на исходную ячейку, и микроконтроллер начнет запись в стек «по кольцу», стирая предыдущее содержимое стека. При извлечении может наблюдаться аналогичный процесс: читается содержимое «дна» стека, а указатель перескакивает на самый верх.

В качестве указателя аппаратного стека обычно используется двоичный счетчик соответствующей разрядности со входом установки в начальное состояние по сигналу сброса, способный выполнять операции инкремента и декремента. Логика управления стеком обычно реализуется посредством дешифратора типа «код-позиция», активизирующего один из регистров стека, согласно номеру (коду) в указателе стека. Для подключения к программному счетчику только одного из регистров стека используются регистры с тристабильным выходным каскадом, способные отключаться от шины, или же выбор выходного кода одного из регистров осуществляется посредством коммутатора (мультиплексора).

Недостатком конструкции, выбранной в качестве прототипа, несмотря на то, что она обеспечивает приемлемую глубину вложения вызовов подпрограмм, является невозможность выполнения операции вызова подпрограммы за один такт, поскольку запись адреса перехода к подпрограмме в программный счетчик здесь также не может быть выполнена одновременно с сохранением его текущего значения в регистрах стека.

Задачей заявляемого технического решения является создание конструкции узла программного счетчика, работающего по принципу стека (или по магазинному принципу), но позволяющего в отличие от прототипа выполнять операции перехода к подпрограмме или к процедуре обслуживания прерывания, а также - возврата из них за один такт, при соблюдении схемотехнической простоты процессора.

Технический результат заключается в повышении быстродействия процессора, и, как следствие, производительности, при упрощении его конструкции.

Указанный технический результат достигается тем, что аппаратный стек процессора с указателем стека и логикой управления стеком, включающий программный счетчик с тристабильными выходными каскадами, согласно решению дополнительно содержит по крайней мере N программных счетчиков с тристабильными выходными каскадами, при этом входы параллельной загрузки всех программных счетчиков соединены поразрядно вместе, выходы всех программных счетчиков соединены поразрядно вместе, входы инкремента всех программных счетчиков соединены вместе, входы разрешения параллельной загрузки всех программных счетчиков соединены вместе, входы выборки каждого из отдельных программных счетчиков подсоединены к одноименным управляющим выходам логики управления стеком так, что в каждый отдельный момент времени только один из программных счетчиков, выбранный указателем стека, может находиться в активном состоянии и выполнять свои функции независимо от остальных.

В конструкцию процессора (микропроцессора, микроконтроллера), содержащую программный счетчик и характерные узлы реализации аппаратного стека, такие как указатель стека с логикой управления стеком и регистры стека, согласно техническому решению, дополнительно вводятся в общем случае N идентичных программных счетчиков, фактически заменяющих в конструкции регистры стека, которые из конструкции исключаются, а указатель стека с логикой управления стеком подключается к блоку N+1 программных счетчиков для выборки активного в данный момент времени программного счетчика.

Выходы программных счетчиков с тристабильными выходными каскадами соединены поразрядно вместе, так что в каждый отдельный момент времени на выходах активны сигналы только одного из счетчиков, выбранного указателем стека посредством логики управления стеком. Входы параллельной загрузки программных счетчиков также соединены поразрядно вместе, что позволяет в каждый отдельный момент времени осуществить параллельную загрузку значением адреса перехода только одного из счетчиков, выбранного указателем стека посредством логики управления стеком. Счетные входы программных счетчиков также объединены, что позволяет подать импульсы инкремента на все счетчики, но при этом инкрементируется только тот из счетчиков, который в данный момент выбран указателем стека посредством логики управления стеком. В результате при выполнении операции перехода к подпрограмме или к процедуре обслуживания прерывания активный на данный момент программный счетчик будет содержать адрес возврата из подпрограммы, который никуда не будет сохраняться, поскольку начальный адрес подпрограммы или процедуры обслуживания прерывания будет записан в следующий программный счетчик, активизированный посредством логики управления стеком в результате инкремента указателя стека. Текущие коды операций подпрограммы выбираются при этом из памяти активным программным счетчиком, в то время как неактивный - содержит и хранит адрес возврата из подпрограммы. Для возврата из подпрограммы или процедуры обслуживания прерывания достаточно декрементировать указатель стека, который посредством логики управления стеком переведет в активное состояние программный счетчик, хранящий адрес возврата из подпрограммы, а текущий счетчик будет при этом переведен в неактивное состояние.

Если же в процессе выполнения подпрограммы случится вызов другой подпрограммы, то текущий активный счетчик будет хранить адрес возврата из нее, а начальный адрес вложенной подпрограммы будет записан в следующий программный счетчик, который будет активизирован посредством логики управления стеком в результате инкремента указателя стека.

Глубина вложения подпрограмм определяется количеством имеющихся программных счетчиков, и ситуации с переполнением обрабатываются аналогично ситуациям с переполнением стека прототипа.

Таким образом, из алгоритма выполнения операции перехода к подпрограмме или к процедуре обслуживания прерывания исключается этап сохранения содержимого программного счетчика в регистре стека, алгоритм же возврата из этих процедур и вовсе упрощается до операции декремента указателя стека, поскольку полностью отсутствует необходимость записи в программный счетчик из стека адреса возврата. А инкремент указателя стека и запись начального адреса подпрограммы в очередной программный счетчик, переведенный в активное состояние посредством логики управления стеком, как и декремент указателя стека в процедуре возврата могут быть выполнены за один такт, что позволяет повысить быстродействие процессора на 30-50% при реализации операций вызова подпрограмм или обслуживания прерывания, а также возврата из них, в силу уменьшения количества тактов, необходимых для выполнения таких операций. В результате также упрощается конструкции узла управления и дешифрации кода инструкции, поскольку заявляемое техническое решение предполагает выполнение всех кодов операций за фиксированное время в один машинный такт.

Существует функциональная аналогия между принципом работы предложенного решения и принципом работы типичного аппаратного стека процессора (микропроцессора, микроконтроллера), а также его конструкцией. Но организованные по магазинному принципу программные счетчики в предложенном решении не только выполняют пассивную функцию хранения адреса возврата из подпрограммы, но и играют роль активного текущего указателя инструкций в памяти. Это позволяет назвать заявляемое техническое решение - активный аппаратный стек процессора.

Заявляемое техническое решение отличается от прототипа наличием новых блоков - N идентичных программных счетчиков, их связями с остальными элементами схемы. Эти отличия позволяют сделать вывод о соответствии заявляемого решения критерию "новизна".

Требуемый результат достигается всей вновь введенной совокупностью существенных признаков, которые в известной патентной и научной литературе не обнаружены на дату подачи заявки. Следовательно, техническое решение соответствует критерию "изобретательский уровень".

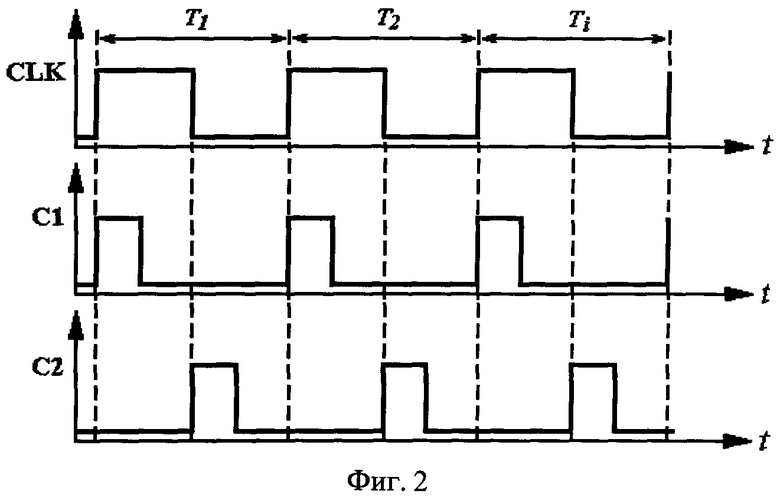

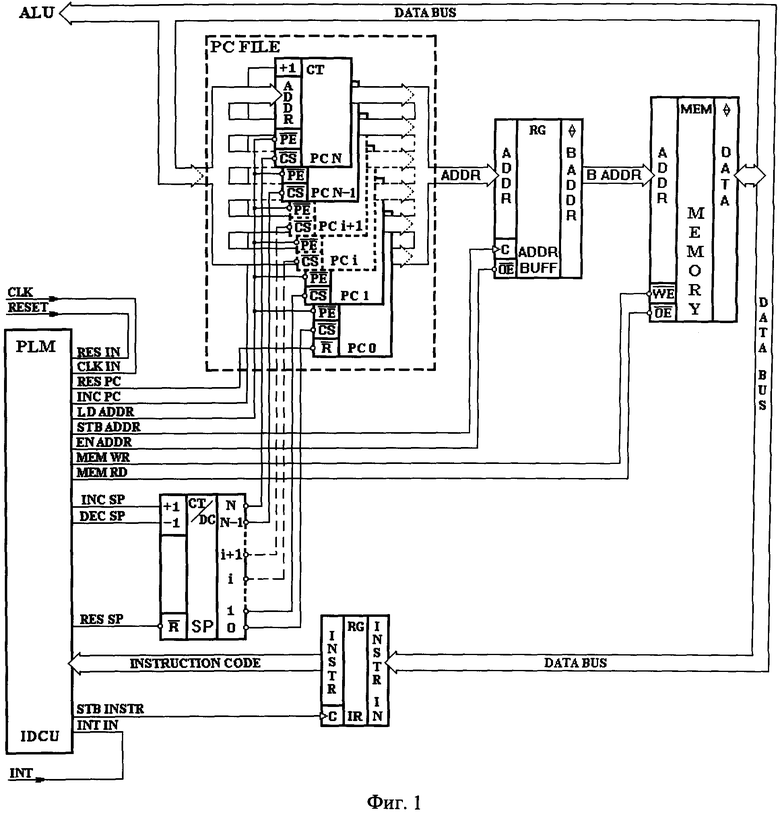

Заявляемое решение поясняется чертежами, где на фиг.1 приведена блок-схема предлагаемого устройства, а на фиг.2 - представлены эпюры сигналов, иллюстрирующие принцип работы устройства потактово.

На чертеже приняты следующие обозначения:

- IDCU - Instruction Decode and Control Unit - устройство управления и синхронизации, обычно выполняемое аппаратно на основе программируемой логической матрицы (PLM);

- SP - Stack Pointer - указатель стека, аппаратно представляющий собой двоичный счетчик (CT) со входом установки в начальное состояние (R) по сигналу сброса, способный выполнять операции инкремента (+1) и декремента (-1), с логикой управления стеком, аппаратно представляющей собой дешифратор (DC) позиционного типа;

- PC FILE - Program Counter File - организованный по магазинному типу файл N+1 программных счетчиков (PC 0, PC 1, … PC N+1); аппаратно представляющих собой двоичные счетчики (CT) с параллельной загрузкой по управляющему сигналу разрешения параллельной записи (PE), имеющих и способных выполнять операции инкремента (+1), а счетчик PC 0 обладает также входом установки в начальное состояние (R) по сигналу сброса;

- IR - Instruction Register - регистр команд (инструкций), аппаратно выполненный на основе регистра (RG) с параллельной загрузкой по стробирующему сигналу (C);

- ADDR BUFF - Address Buffer - буфер адреса, аппаратно выполненный на основе регистра (RG) с параллельной загрузкой по стробирующему сигналу (C) и тристабильным выходным каскадом, управляемым по входу разрешения выходного сигнала (OE);

- MEMORY - память, или запоминающее устройство с тристабильным двунаправленным каскадом вывода данных (DATA), в общем случае - MEM, поскольку может быть выполнено как на основе интегральных схем с произвольным доступом (RAM), так и - только для чтения (ROM);

- ADDR - адресные линии;

- BADDR - буферированные адресные линии;

- DATA BUS - шина данных, тристабильная и двунаправленная;

- INSTRUCTION CODE - код операции (инструкция);

- ALU - Arithmetic-Logical Unit - арифметико-логическое устройство (АЛУ);

Устройство управления и синхронизации - IDCU осуществляет генерацию управляющих сигналов согласно поступающему на его входы коду операции (INSTRUCTION CODE) для всех внутренних узлов процессора, но на чертеже (фиг.1) показаны только те из сигналов, которые относятся к работе активного аппаратного стека процессора и основных взаимодействующих с ним узлов:

- RES IN - Reset Input - вход внешнего сигнала начальной инициализации процессора;

- CLK IN - Clock Input - вход внешнего тактового сигнала;

- RES PC - Reset Program Counter - сигнал установки программного счетчика в исходное состояние;

- INC PC - Increment Program Counter - сигнал увеличения программного счетчика на единицу;

- LD ADDR - Load Address - сигнал параллельной загрузки адреса перехода в программный счетчик;

- STB ADDR - Strobe Address - сигнал (строб) записи эффективного адреса в буфер адреса;

- EN ADDR - Enable Address - сигнал разрешения выдачи эффективного адреса на адресные входы запоминающего устройства (памяти);

- MEM WR - Memory Write - сигнал разрешения записи в память;

- MEM RD - Memory Read - сигнал разрешения чтения из памяти;

- INC SP - Increment Stack Pointer - сигнал увеличения указателя стека на единицу;

- DEC SP - Decrement Stack Pointer - сигнал уменьшения указателя стека на единицу;

- RES SP - Reset Stack Pointer - сигнал установки указателя стека в исходное состояние;

- STB INSTR - Strobe Instruction - сигнал (строб) записи кода операции (инструкции) в регистр команд;

- INT IN - Interrupt Input - вход сигнала прерывания от внешнего источника прерывания.

Согласно представленной на фиг.1 схеме, указатель стека SP своими входами начальной установки R, инкремента +1 и декремента -1 подключен к устройству управления и синхронизации IDCU по управляющим линиям RES SP, INC SP и DEC SP соответственно. Выходы логики управления стеком 0÷N указателя стека SP, осуществляющие выбор активного программного счетчика, подсоединены ко входам активизации CS (Cheap Select) программных счетчиков PC 0, PC 1, … PC N (всего N+1). Одноименные входы инкремента +1, как и входы разрешения параллельной загрузки РЕ (Parallel Enable) программных счетчиков объединены и подключены соответственно к управляющим выходам INC PC и LD ADDR устройства управления и синхронизации IDCU. В каждый отдельный момент времени эти сигналы могут быть активны лишь для одного из программных счетчиков, выбранного в этот момент времени логикой управления стеком указателя стека SP. Программный счетчик PC 0 соединен своим входом начальной установки R с управляющим выходом RES PC устройства управления и синхронизации IDCU, что позволяет инициаллизировать его значением стартового адреса при включении процессора или по сигналу аппаратного сброса RESET. Выходы программных счетчиков PC 0, PC 1, … PC N с тристабильными выходными каскадом соединены поразрядно вместе и подключены к адресным входам ADDR буфера адреса ADDR BUFF, причем в каждый отдельный момент времени на выходах активны сигналы только одного из счетчиков, выбранного указателем стека SP посредством логики управления стеком. Буфер адреса ADDR BUFF соединен по входу стробирующего сигнала C и входу разрешения выходного сигнала ОЕ с устройством управления и синхронизации IDCU, управляющие линии STB ADDR и EN ADDR которого соответственно осуществляют запись в буфер эффективного адреса с выхода активного программного счетчика и разрешают выдачу этого адреса с выходов BADDR буфера на адресные входы ADDR запоминающего устройства MEMORY, к которым выходные линии буфера адреса подсоединены. Входы разрешения записи в память WE (Write Enable) и разрешения выдачи данных OE (Output Enable) запоминающего устройства MEMORY соединены с выходами MEM WR и MEM RD устройства управления и синхронизации IDCU, что позволяет последнему разрешать выдачу данных из памяти MEMORY на двунаправленную и тристабильную шину данных DATA BUS по выходам DATA, или же записывать в память значение с шины через эти же выводы, но выполняющие уже функцию входов.

Через двунаправленную и тристабильную шину данных DATA BUS с выводами DATA запоминающего устройства MEMORY соединяются входы INSTRIN регистра команд IR, в котором по активному сигналу на стробирующем входе C, соединеном с управляющим выходом STB INSTR устройства управления и синхронизации IDCU, и фиксируется поступивший из памяти код операции. С выходов INSTR регистра команд IR, подключенных к устройству управления и синхронизации IDCU, на последнее подается текущий код операции (INSTRUCTION CODE), согласно которому IDCU осуществляет генерацию управляющих сигналов для всех внутренних узлов процессора.

К двунаправленной и тристабильной шине данных DATA BUS подключены также и входы ADDR программных счетчиков PC 0, PC 1, … PC N, соединенные поразрядно вместе, что позволяет осуществить по управляющему сигналу LD ADDR устройства управления и синхронизации IDCU запись адреса передачи управления в случае безусловного перехода, вызова подпрограммы или возникновения прерывания с шины данных в программный счетчик, выбранный по входу CS в качестве активного в данный момент логикой управления стеком указателя стека SP.

К двунаправленной и тристабильной шине данных DATA BUS подключается также арифметико-логическое устройство ALU и другие узлы процессора, не изображенные на схеме фиг.1, поскольку они не находятся в непосредственном взаимодействии с активный аппаратный стеком.

На входы устройства управления и синхронизации IDCU - RES IN, INT IN и CLK IN поступают соответственно внешние сигналы начальной инициализации (сброса) процессора RESET, аппаратного прерывания INT и последовательность тактовых импульсов CLK, осуществляющая синхронизацию всего процессорного устройства.

Активный аппаратный стек процессора работает следующим образом.

При включении напряжения питания или принудительной начальной инициализации процессора на вход RES IN устройства управления и синхронизации IDCU поступает активный уровень внешнего сигнала начальной инициализации RESET, а на вход тактирования CLK IN-последовательность внешних тактовых импульсов CLK. За время действия сигнала RESET синхронно с тактовыми импульсами CLK происходит установка в начальное состояние указателя стека SP активным сигналом RES SP по входу начальной установки R, в результате чего на выходе 0 логики управления стеком появляется активный уровень, который в свою очередь по входу CS переводит в активное состояние программный счетчик PC 0. В этот же момент времени устройство управления и синхронизации IDCU, активным сигналом RES PC инициализирует программный счетчик PC 0 начальным значением адреса инструкции по его входу начальной установки R.

По завершению сигнала RESET, процессор синхронно с тактовыми импульсами CLK переходит к выполнению процедуры выборки из памяти кода операции (FETCH). При этом установленный в активном программном счетчике PC 0 начальный адрес (обычно - это 0) переписывается по адресным входам ADDR в буфер адреса ADDR BUFF синхронно с активным сигналом STB ADDR, подаваемым IDCU на вход С буфера адреса, при этом на управляющем входе EN ADDR последнего устройство управления и синхронизации устанавливает разрешающий уровень, в результате чего значение адреса с выходов BADDR буфера поступает на адресные входы ADDR запоминающего устройства MEMORY.

По сигналу INC PC, поданному устройством управления и синхронизации на входы инкремента +1 программных счетчиков, на выходе активного счетчика PC 0 установится следующее значение адреса - на единицу большее, которое и будет передано на адресные входы ADDR запоминающего устройства MEMORY во время последующей процедуры FETCH.

По сигналу MEM RD от устройства управления и синхронизации IDCU, поступающему на вход разрешения выдачи данных OE запоминающего устройства, содержимое ячейки по адресу 0 поступает на шину данных DATA BUS и фиксируется в регистре команд IR активным сигналом STB INSTR, поданным IDCU на стробирующий вход С регистра.

На этом процедура выборки из памяти кода операции заканчивается, а текущий код операции (INSTRUCTION CODE), поданный с выходов INSTR регистра команд IR на входы устройства управления и синхронизации IDCU, будет определять последовательность управляющих сигналов IDCU, организующих согласованную совместную работу внутренних узлов процессора синхронно с тактовыми импульсами CLK в следующей фазе исполнения инструкции.

Предположим, для определенности, что в данный момент исполняемой является инструкция инкремента программного счетчика, поскольку отсутствие на схеме фиг.1 других узлы процессора, не находящихся в непосредственном взаимодействии с активный аппаратный стеком, не позволяет нам детально рассмотреть иные операции. В этом случае в фазе исполнения инструкции на входы инкремента +1 программных счетчиков устройством управления и синхронизации IDCU будет подан активный сигнал INC PC, в результате чего на выходе активного счетчика PC 0 установится значение, на единицу большее его текущего значения. После чего фаза исполнения инструкции будет окончена, процессор перейдет к процедуре выборки из памяти следующего кода операции по описанному выше алгоритму, и такое последовательное чтение инструкций из памяти с их последующим исполнением будет происходить до тех пор, пока не возникнет аппаратное прерывание, или же в программе, хранимой в памяти, не встретятся инструкции безусловного перехода или вызова подпрограммы.

Рассмотрим работу активного аппаратного стека процессора в случае вызова подпрограммы или возникновения прерывания, а также возврата из этих процедур. Для демонстрации эффективности заявляемого технического решения будем рассматривать алгоритм реализации этих процедур на уровне микроопераций в привязке к последовательности входных тактовых импульсов CLK, изображенной на фиг.2.

Период следования тактовых импульсов CLK, определяет длительность внутреннего такта процессора Ti - минимальный интервал времени за который устройству управления и синхронизации IDCU необходимо организовать как выборку кода инструкции из памяти, так и ее исполнение посредством последовательности микроопераций, выражающихся в подаче управляющих сигналов соответствующим узлам процессора.

Поскольку процессор представляет собой синхронную систему, исполняющую свои внутренние микрооперации в привязке к импульсам синхронизации, становится очевидным, что характерных временных привязок на интервале Ti сигнала CLK - фронт импульса и спад импульса - явно недостаточно для организации выполнения даже минимального числа микрооперации по выборке и исполнению текущей инструкции. Поэтому в схеме устройства управления и синхронизации обычно формируют две последовательности внутренних тактирующих импульсов по фронтам и по спадам сигнала CLK - С1 и С2. Эти две последовательности на длительности интервала Ti обеспечивают четыре привязки по времени - по фронтам и спадам тактирующих импульсов.

В случае выполнения инструкции вызова подпрограммы по фронту импульса С1 устройство управления и синхронизации IDCU подает активный сигнал STB ADDR на вход С буфера адреса, чем фиксирует в нем текущий адрес инструкции с выходов активного программного счетчика. Одновременно IDCU переводит в активное состояние свои управляющие линии EN ADDR и MEM RD, которые разрешают буферу адреса ADDR BUFF выдать адрес инструкции на входы ADDR запоминающего устройства MEMORY, а запоминающему устройству - выдать содержимое ячейки по указанному адресу на шину данных DATA BUS. К концу импульса С1 значение кода операции на линиях шины данных можно считать установившимся, поэтому по спаду С1 устройство управления и синхронизации подает активный сигнал STB INSTR на стробирующий вход С регистра команд IR, тем самым "защелкивая" в нем текущую инструкцию (INSTRUCTION CODE), код которой по линиям выходов INSTR регистра будет удерживаться на входах IDCU в фазе выполнения инструкции. Одновременно с этим устройство управления и синхронизации подает активный сигнал INC PC на входы инкремента+1 программных счетчиков, в результате чего на выходе активного в данный момент программного счетчика, активизированного по входу CS логикой управления стеком, появится адрес следующей инструкции программы.

Таким образом, за первую половину такта 77 сигнала CLK устройство управления и синхронизации завершает процедуру выборки из памяти кода операции вызова подпрограммы.

На этапе выполнения этой операции, как и на этапе перехода к процедуре обслуживания прерывания, выполняются практически одинаковые микрооперации содержание которых сводится к сохранению адреса возврата и загрузке программного счетчика с шины данных DATA BUS адресом соответствующей подпрограммы, но при обслуживании прерывания этот адрес выдается на шину данных внешним устройством, вызвавшим прерывание или специальным внутренним устройством, в том случае, если осуществляется переход к процедуре обслуживания прерывания по фиксированному адресу.

Итак, в обоих рассматриваевымых случаях на момент фронта импульса С2, определяющего начало второй половины такта 77 сигнала CLK, на шине данных DATA BUS присутствует установившееся значение адреса подпрограммы. По фронту С2 устройством управления и синхронизации IDCU подается активный сигнал INC SP на вход инкремента +1 указатель стека SP, в результате чего его содержимое увеличивается на единицу, и логика управления стеком своим выходом i+1 активизирует по входу CS следующий программный счетчик PC i+1, а текущий программный счетчик PC i переходит в неактивное состояние, сохраняя при этом свое значение, которое и является адресом возврата из вызываемой подпрограммы. По спаду импульса С2 в активный программный счетчик PC i+1 записывается значение адреса подпрограммы с шины данных DATA BUS управляющим сигналом LDADDR, подаваемым устройством управления и синхронизации на входы разрешения параллельной загрузки РЕ программных счетчиков. Таким образом, следующая операция выборки из памяти кода операции будет производиться из ячейки памяти с адресом, записанным в активный программный счетчик PC i+1, что, собственно, и представляет собой передачу управления на адрес подпрограммы или процедуры обслуживания прерывания. Как видно из приведенного выше алгоритма, эти операции выполняются процессором, имеющим в своем составе заявляемый активный аппаратный стек, строго за один такт.

Для оценки фактора повышения быстродействия процессора, имеющего в своем составе заявляемый активный аппаратный стек, рассмотрим последовательность микроопераций, выполняемых процессором с обычным стеком адресов возврата при обслуживании прерывания или вызове подпрограммы.

Процедура выборки из памяти кода операции в этом случае особенностей по сравнению с алгоритмом, описанным выше, не имеет, а на этапе осуществления перехода к вызываемой процедуре последовательность микроопераций будет иная. По фронту импульса С2 устройством управления и синхронизации IDCU будет подан активный сигнал INC SP на вход инкремента +1 указатель стека SP, в результате чего его содержимое увеличивается на единицу, а логика управления стеком своим выходом i+1 активизирует по входу CS очередной регистр стека. По спаду С2 в этот регистр будет записано содержимое программного счетчика активным сигналом от устройства управления и синхронизации. Для записи в программный счетчик адреса перехода к подпрограмме с шины данных DATA BUS требуется следующий импульс С1, по которому уже должно начаться выполнение процедуры выборки из памяти кода следующей операции. Следовательно, устройство управления и синхронизации должно блокировать эту последовательность микрокоманд на следующий такт, что приводит к усложнению его структуры для выполнения операций за разное число тактов.

С учетом того, что для выполнения операции вызова подпрограммы или обслуживания прерывания процесору, имеющему в своем составе заявляемый активный аппаратный стек, достаточно состояний, обеспечиваемых импульсами С1 и С2 на длительности такта Ti сигнала CLK, а процессору с традиционным стеком требуется и следующий импульс С1, то очевидно, что, строго говоря, эти операции выполняются процесором с заявляемым решением, на 33% быстрее. Но с учетом того, что операция не может быть закончена в середине тактового импульса, то процессор с традиционным стеком выполняет операцию вызова подпрограммы или обслуживания прерывания за два такта Ti и Ti+1 сигнала CLK. Следовательно, повышение быстродействия процесора с заявляемым решением при выполнении подобных операции достигает 50%, поскольку он выполняет их за один такт, что упрощает схемотехнически конструкцию устройства управления и синхронизации.

Оценим преимущество, которым обладает процесор, имеющий в своем составе заявляемый активный аппаратный стек, по сравнению с процессором с традиционным стеком при выполнении операции возврата из подпрограммы или процедуры обслуживания прерывания.

Процедура выборки из памяти кода операции в этом случае также не имеет особенностей по сравнению с алгоритмом, описанным выше, а на этапе осуществления возврата из вызываемой процедуры последовательность микроопераций, выполняемая процесором с заявляемым решением, будет следующей. По фронту импульса С2 устройством управления и синхронизации IDCU будет подан активный сигнал DEC SP на вход декремента -1 указателя стека SP. В результате чего его содержимое уменьшится на единицу, и если до этого был активным программный счетчик PC i+1, то логика управления стеком активизирует по входу CS своим выходом i программный счетчик PC i, сохранявший до этого момента свое состояние, которое и является адресом возврата из вызываемой подпрограммы. Таким образом, собственно, осуществляется возврат управления из подпрограммы или процедуры обслуживания прерывания в точку их вызова, и эта операция выполняются процессором, имеющим в своем составе заявляемый активный аппаратный стек, строго за один такт.

Для сравнения процессор с традиционным стеком выполняет операцию вызова подпрограммы или обслуживания прерывания следующим образом: по фронту импульса С2 устройством управления и синхронизации IDCU будет подан активный сигнал разрешения выхода регистру стека, выбранного указателем стека SP, в результате чего его содержимое - значение адреса возврата - за время, равное длительности импульса С2, примет на входах программного счетчика установившееся значение, и по спаду С2 активным управляющим сигналом LD ADDR, подаваемым устройством управления и синхронизации на входы разрешения параллельной загрузки РЕ программного счетчика, будет записано в последний. По фронту С1 следующего такта устройство управления и синхронизации должно снять активный сигнал разрешения выхода регистра стека и подать активный сигнал DEC SP на вход декремента -1 указателя стека SP.

Очевидно, что процессор с традиционным стеком выполняет операцию возврата из подпрограммы или процедуры обслуживания прерывания за два такта Ti и Ti+1 сигнала CLK, а процесор с заявляемым решением - за один такт. Следовательно, его быстродействие при выполнении подобных операций на 50% выше процессора с традиционным стеком, при сохранении схемотехнической простоты устройства управления и синхронизации.

Таким образом, сравнение алгоритмов работы процесора, имеющего в своем составе активный аппаратный стек, с процессором, обладающим традиционным стеком, позволяет считать достигнутой цель заявляемого технического решения - создание конструкции узла программного счетчика, работающего по принципу стека (или по магазинному принципу), и позволяющего выполнять операции перехода к подпрограмме или к процедуре обслуживания прерывания, а также возврата из них за один такт, при соблюдении схемотехнической простоты процессора.

Заявляемое решение - активный аппаратный стек - позволяет повысить быстродействие процессора на 30-50% при выполнении операций вызова подпрограмм или обслуживания прерывания, а также возврата из них, в силу уменьшения количества тактов, необходимых для аппаратной реализации таких операций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| СПОСОБ ПЕРЕКЛЮЧЕНИЯ КОНТЕКСТА ВЫЧИСЛИТЕЛЬНОГО ПРОЦЕССА ПРИ ПРЕРЫВАНИИ ПРОГРАММЫ ИЛИ ПЕРЕХОДЕ К ПОДПРОГРАММЕ | 2006 |

|

RU2340933C2 |

| МИКРОПРОЦЕССОР | 1990 |

|

RU2024927C1 |

| Микропрограммное устройство управления | 1986 |

|

SU1481759A1 |

| СПОСОБЫ И УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПОВЕДЕНИЯ ПРЕДСКАЗАНИЯ ПЕРЕХОДОВ ЯВНОГО ВЫЗОВА ПОДПРОГРАММЫ | 2007 |

|

RU2417407C2 |

| СПОСОБ ОБРАБОТКИ ЦИФРОВЫХ ДАННЫХ | 2005 |

|

RU2294010C1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1817096A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

Изобретение относится к области электроники и микропроцессорной техники и может быть использовано в конструкциях современных, высокопроизводительных RISC-микропроцессоров и микроконтроллеров. Технический результат заявленного изобретения заключается в повышении быстродействия процессора, его производительности и упрощении его конструкции за счет создания конструкции узла программного счетчика, работающего по принципу стека и позволяющего выполнять операции перехода к подпрограмме или процедуре обслуживания прерывания. Технический результат достигается за счет того, что аппаратный стек процессора с указателем стека и логикой управления стека включает программный счетчик с тристабильными выходными каскадами, который дополнительно содержит, по крайней мере N программных счетчиков с тристабильными выходными каскадами, при этом входы параллельной загрузки всех программных счетчиков соединены поразрядно вместе, выходы всех программных счетчиков соединены поразрядно вместе, входы инкремента всех программных счетчиков соединены вместе так, что в каждый отдельный момент времени только один из программных счетчиков, выбранный указателем стека, может находиться в активном состоянии и выполнять свои функции независимо от остальных. 2 ил.

Аппаратный стек процессора с указателем стека и логикой управления стека, включающий программный счетчик с тристабильными выходными каскадами, отличающийся тем, что аппаратный стек процессора дополнительно содержит по крайней мере N программных счетчиков с тристабильными выходными каскадами, при этом входы параллельной загрузки всех программных счетчиков соединены поразрядно вместе, выходы всех программных счетчиков соединены поразрядно вместе, входы инкремента всех программных счетчиков соединены вместе, входы разрешения параллельной загрузки всех программных счетчиков соединены вместе, входы выборки каждого из отдельных программных счетчиков подсоединены к одноименным управляющим выходам логики управления стеком так, что в каждый отдельный момент времени только один из программных счетчиков, выбранный указателем стека, может находиться в активном состоянии и выполнять свои функции независимо от остальных.

| US 6658578 B1, 02.12.2003 | |||

| US 6449709 B1, 10.09.2002 | |||

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СФЕРИЧЕСКОЙ ГАЗОДИНАМИЧЕСКОЙ ОПОРЫ ГИРОСКОПА | 1985 |

|

SU1840742A1 |

| ЗАПОМИНАНИЕ ОПЕРАНДОВ СТЕКА В РЕГИСТРЕ | 2001 |

|

RU2271565C2 |

Авторы

Даты

2014-10-10—Публикация

2013-08-09—Подача