Изобретение относится к вычислительной технике и может быть использована для построения серверов различного назначения.

Известен ряд вычислительных систем с распределенной памятью, содержащих процессоры, объединенные некоторой коммуникационной средой. Наиболее известными среди них являются: Intel Paragon, IBM SP1/SP2, Cray T3D и многие другие, включая отечественные кластерные и массово-параллельные установки, например, МВС-1000М, СКИФ Syberia и т.д.

Недостатком таких вычислительных систем является низкая производительность при решении реальных задач.

Наиболее близким к заявляемому является вычислительный модуль многопроцессорной крейтовой системы и многопроцессорная система из этих модулей [РФ №151425 U1, G06F 15/16, 10.04.2015], включающий печатную плату и размещенные на ней: процессор с выводом межпроцессорных каналов, подключенный к оперативной памяти, а также к контроллеру периферийных интерфейсов посредством шины ввода-вывода, контроллер периферийных интерфейсов с подключением к нему шин периферийных интерфейсов, оперативную память, соединители для подключения к коммутационной панели, выполненные с возможностью подключения межпроцессорных каналов и шин периферийных интерфейсов к коммутационной панели, постоянное запоминающее устройство с записанной в нем программой начальной загрузки.

Недостатком данного устройства является отсутствие возможности построения серверов различного назначения.

Техническим результатом является расширение функциональных возможностей за счет обеспечения возможности построения серверов различного назначения.

Технический результат достигается тем, что в «Систему управления вычислительного узла в составе модульной вычислительной платформы «Эльбрус8» для построения серверов различного назначения», содержащую печатную плату, процессор, подключенный к оперативной памяти, контроллер периферийных интерфейсов, шины ввода-вывода, что в ней в качестве контроллера периферийных интерфейсов используется многофункциональный контроллер КПИ-2 и введены пять элементов питания, температурный датчик, мультиплексор, расширительный модуль ввода/вывода, два монитора питания, светодиоды, находящиеся на первой многослойной печатной плате, три процессора, четыре узла ОЗУ, два мультиплексора, три элемента питания, находящиеся на второй многослойной печатной плате, процессорный модуль, находящийся на третьей многослойной печатной плате, коммутатор и сервер управляющий, двухсторонний вход выход которого соединен с вторым двухсторонним входом выходом коммутатор, первый двухсторонний вход выход которого соединен с седьмым двухсторонним входом выходом процессорного модуля, первый, второй, третий и четвертый двухсторонние входы выходы которого соединены соответственно, каждый отдельно, с одноименными двухсторонними входами выходами контроллера периферийных интерфейсов, пятый, шестой, седьмой и восьмой двухсторонние входы выходы которого соединены соответственно, каждый отдельно, с первым, вторым, третьим и четвертым двухсторонними входами выходами мультиплексора, пятый двухсторонний вход выход которого соединен с вторым двухсторонним входом выходом мультиплексора, первый двухсторонний вход выход которого соединен с объединенными двухсторонними входами выходами первого, второго, третьего и четвертого процессоров, двухсторонний вход выход мультиплексора соединен с пятым двухсторонним входом выходом процессорного модуля, шестой двухсторонний вход выход которого соединен с пятым двухсторонним входом выходом расширительного модуля ввода/вывода, четвертый двухсторонний вход выход которого соединен с двухсторонним входом выходом второго монитора питания, двухсторонний вход выход первого монитора питания соединен с двухсторонним входом выходом выходом расширительного модуля ввода/вывода, третий двухсторонний вход выход которого соединен с двухсторонним входом выходом светодиодов, первый двухсторонний вход выход расширительного модуля ввода/вывода с девятым двухсторонним входом выходом выходом контроллера периферийных интерфейсов, двухсторонний вход выход шины ввода/вывода соединен с пятым двухсторонним входом выходом контроллера периферийных интерфейсов, шестой двухсторонний вход выход которого соединен с двухсторонними входами выходами с первого по пятый элементов питания, двухсторонние входы выходы с первого по четвертый узлы ОЗУ соединены соответственно, каждый отдельно, с первого по четвертый двухсторонними входами выходами первого мультиплексора, пятый двухсторонний вход выход которого соединен с двухсторонним входом выходом контроллера периферийных интерфейсов, двухсторонний вход мультиплексора соединен с двухсторонними входами выходами шестого, седьмого и восьмого элементов питания, причем многофункциональный контроллер периферийных интерфейсов КПИ-2 содержит контроллер физического уровня канала ввода-вывода (WLCC_PHY), контроллер канального уровня канала ввода-вывода (WLCC_DLL), коммутатор первого уровня, коммутатор второго уровня, первый составной контроллер, первый контроллер линка PCIe, второй контроллер линка PCIe, первый 4-х портовый контроллер интерфейса USB, второй 4-х портовый контроллер интерфейса USB, второй составной контроллер, контроллер двух устройств интерфейса IDE, третий составной контроллер, контроллер управления питанием и энергосбережением, контроллер интерфейса PCI, звуковой контроллер интерфейса HDA, первый 4-портовый контроллер интерфейса SATA 3.0, второй 4-портовый контроллер интерфейса SATA 3.0, первый контроллер интерфейса Ethernet, второй контроллер интерфейса Ethernet, третий контроллер интерфейса Ethernet и блок управления сигналами тактовой синхронизации, выход которого соединен с объединенными входами синхронизации всех блоков устройства, выход которого соединен с выходом контроллера физического уровня канала ввода-вывода, двухсторонний вход выход которого соединен с первым двухсторонним входом выходом контроллера канального уровня канала ввода-вывода, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом коммутатора первого уровня, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого составного контроллера, третий двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом первого контроллера линка PCIe, четвертый двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом второго контроллера линка PCIe, пятый двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом звукового контроллера интерфейса HDA, шестой двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом первого 4-х портового контроллера интерфейса SATA 3.0, седьмой двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом второго 4-х портового контроллера интерфейса SATA 3.0, восьмой двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом коммутатора второго уровня, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого 4-х портового контроллера интерфейса USB, третий двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом второго 4-х портового контроллера интерфейса USB, четвертый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом второго составного контроллера, пятый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом первого контроллера интерфейса Ethernet, шестой двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом второго контроллера интерфейса Ethernet, седьмой двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом третьего контроллера интерфейса Ethernet, восьмой двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом контроллера двух устройств интерфейса IDE, девятый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом третьего составного контроллера, десятый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом контроллера управления питанием и энергосбережением, одиннадцатый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом, контроллер интерфейса PCI, вторые двухсторонние входы выходы контроллера двух устройств интерфейса IDE, третьего составного контроллера, контроллера управления питанием и энергосбережением, контроллера интерфейса PCI, звукового контроллера интерфейса HDA, первого контроллера интерфейса Ethernet, второго контроллера интерфейса Ethernet и третьего контроллера интерфейса Ethernet соединены с соответствующими двухсторонними входами выходами устройства, вторые и третьи двухсторонние входы выходы первого составного контроллера, первого контроллера линка PCIe и второго составного контроллера соединены с соответствующими двухсторонними входами выходами устройства, с второго по пятый двухсторонние входы выходы второго контроллера линка PCIe, первого 4-х портового контроллера интерфейса USB, второго 4-х портового контроллера интерфейса USB, первого 4-х портового контроллера интерфейса SATA 3.0, второго 4-х портового контроллера интерфейса SATA 3.0 соединены с соответствующими двухсторонними входами выходами устройства, причем соединение между двухсторонними входами выходами коммутатора первого уровня и контроллера канального уровня канала ввода-вывода, коммутатора второго уровня, первого составного контроллера, первого контроллера линка PCIe, второго контроллера линка PCIe, звукового контроллера интерфейса HDA, первого 4-х портового контроллера интерфейса SATA 3.0, второго 4-х портового контроллера интерфейса SATA 3.0 осуществляется интерфейсом типа «Slink», причем соединение между двухсторонними входами выходами коммутатора второго уровня и первого 4-х портового контроллера интерфейса USB, второго 4-х портового контроллера интерфейса USB, второго составного контроллера, контроллера двух устройств интерфейса IDE, третьего составного контроллера, контроллера управления питанием и энергосбережением, контроллера интерфейса PCI, первого контроллера интерфейса Ethernet, второго контроллера интерфейса Ethernet и третьего контроллера интерфейса Ethernet осуществляется интерфейсом типа «IOlink».

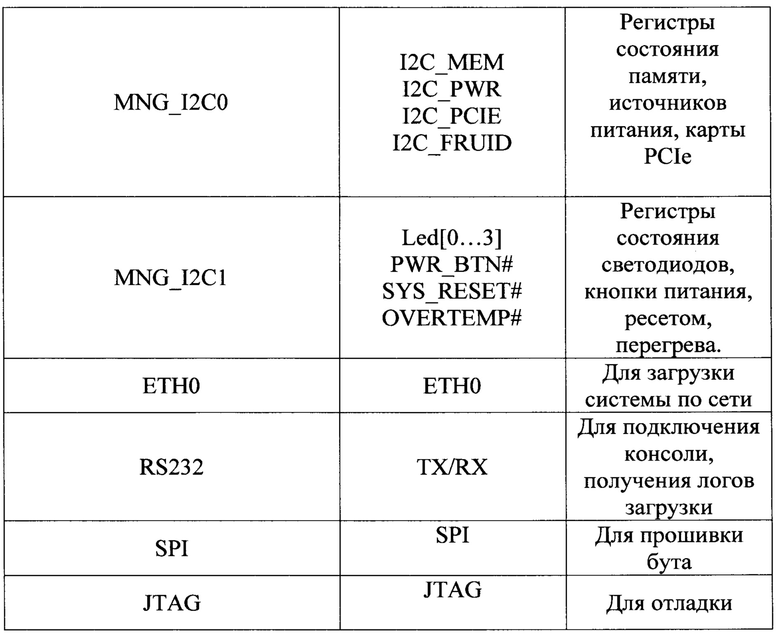

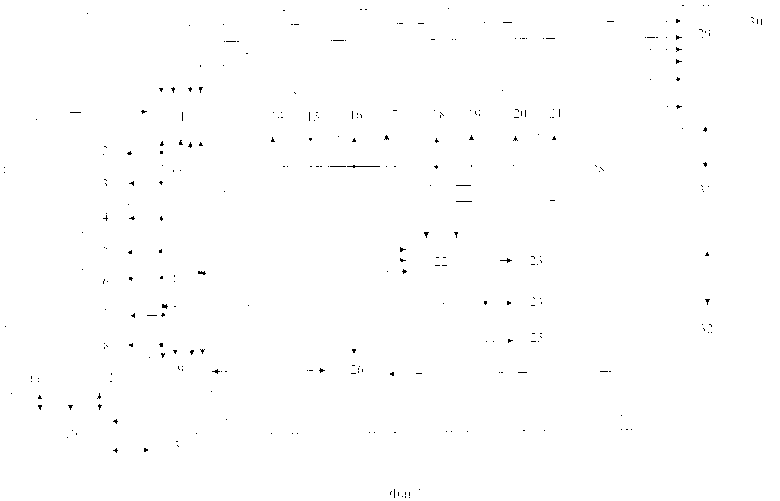

На фиг. 1 представлена блок-схема системы управления вычислительного узла в составе модульной вычислительной платформы «Эльбрус8» для построения серверов различного назначения.

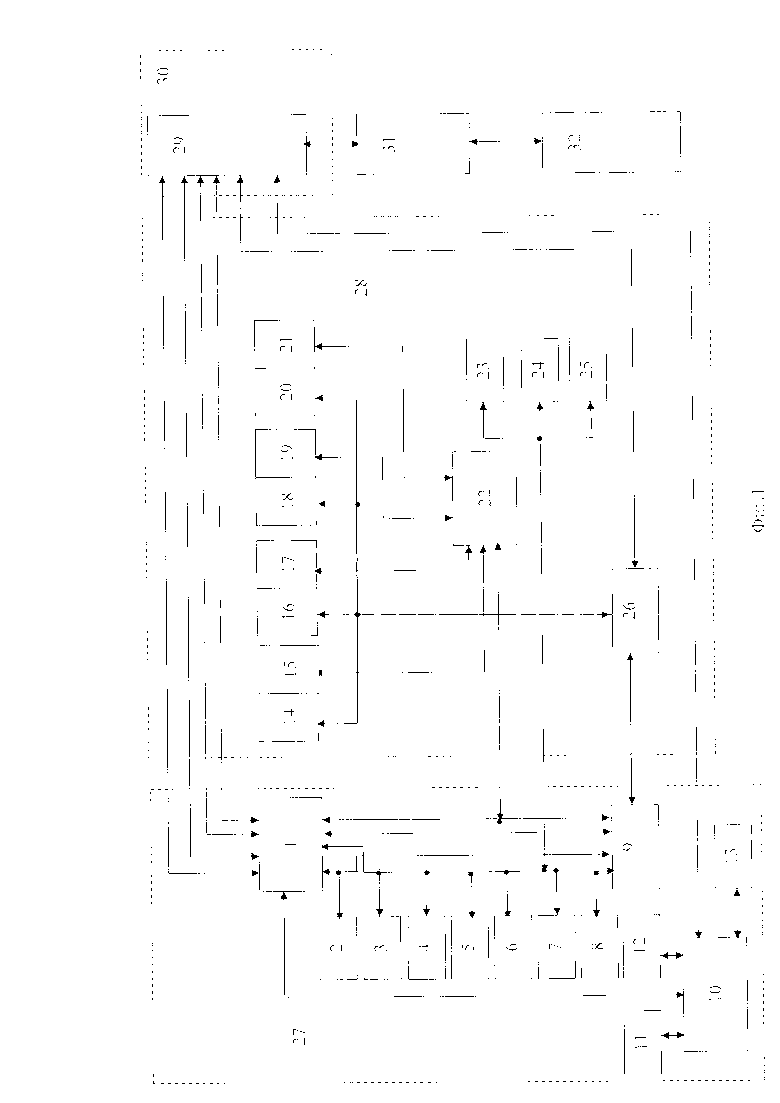

На фиг. 2 представлена блок-схема многофункционального контроллера КПИ-2.

Система управления вычислительного узла в составе модульной вычислительной платформы «Эльбрус8» для построения серверов различного назначения (фиг. 1) содержит, многофункциональный контроллер 1, шину ввода-вывода 2, пять элементов питания 3, 4, 5, 6 и 7, температурный датчик 8, мультиплексор 9, расширительный модуль ввода/вывода 10, два монитора питания 11 и 13, светодиоды 12, находящиеся на первой многослойной печатной плате 27, четыре процессора 14, 16, 18 и 20, четыре узла ОЗУ 15, 17, 19 и 21, два мультиплексора 22 и 26, три элемента питания 23, 24 и 25, находящиеся на второй многослойной печатной плате 28, процессорный модуль 29, находящийся на третьей многослойной печатной плате 30, коммутатор 31 и сервер управляющий 32, двухсторонний вход выход которого соединен с вторым двухсторонним входом выходом коммутатор 31, первый двухсторонний вход выход которого соединен с седьмым двухсторонним входом выходом процессорного модуля 29, первый, второй, третий и четвертый двухсторонние входы выходы которого соединены соответственно, каждый отдельно, с одноименными двухсторонними входами выходами контроллера периферийных интерфейсов 1, пятый, шестой, седьмой и восьмой двухсторонние входы выходы которого соединены соответственно, каждый отдельно, с первым, вторым, третьим и четвертым двухсторонними входами выходами мультиплексора 9, пятый двухсторонний вход выход которого соединен с вторым двухсторонним входом выходом мультиплексора 26, первый двухсторонний вход выход которого соединен с объединенными двухсторонними входами выходами первого, второго, третьего и четвертого процессоров 14, 16, 18 и 20, двухсторонний вход выход мультиплексора 26 соединен с пятым двухсторонним входом выходом процессорного модуля 29, шестой двухсторонний вход выход которого соединен с пятым двухсторонним входом выходом расширительного модуля ввода/вывода 10, четвертый двухсторонний вход выход которого соединен с двухсторонним входом выходом второго монитора питания 13, двухсторонний вход выход первого монитора питания 11 соединен с двухсторонним входом выходом выходом расширительного модуля ввода/вывода 10, третий двухсторонний вход выход которого соединен с двухсторонним входом выходом светодиодов 12, первый двухсторонний вход выход расширительного модуля ввода/вывода 10 с девятым двухсторонним входом выходом выходом контроллера периферийных интерфейсов 1, двухсторонний вход выход шины ввода/вывода 2 соединен с пятым двухсторонним входом выходом контроллера периферийных интерфейсов 1, шестой двухсторонний вход выход которого соединен с двухсторонними входами выходами с первого по пятый элементов питания 3, 4, 5, 6 и 7, двухсторонние входы выходы с первого по четвертый узлы ОЗУ 15, 17, 19 и 21 с единены соответственно, каждый отдельно, с первого по четвертый двухсторонними входами выходами первого мультиплексора 22, пятый двухсторонний вход выход которого соединен с двухсторонним входом выходом контроллера периферийных интерфейсов 1, двухсторонний вход мультиплексора 9 соединен с двухсторонними входами выходами шестого, седьмого и восьмого элементов питания 23, 24 и 25, причем многофункциональный контроллер КПИ-2 1 (фиг. 2) содержит контроллер физического уровня канала ввода-вывода 33 (WLCC_PHY), контроллер канального уровня канала ввода-вывода 34 (WLCC_DLL), коммутатор первого уровня 35, коммутатор второго уровня 36, первый составной контроллер 37, первый контроллер линка PCIe 38, второй контроллер линка PCIe 39, первый 4-х портовый контроллер интерфейса USB 40, второй 4-х портовый контроллер интерфейса USB 41, второй составной контроллер 42, контроллер двух устройств интерфейса IDE 43, третий составной контроллер 44, контроллер управления питанием и энергосбережением 45, контроллер интерфейса PCI 46, звуковой контроллер интерфейса HDA 47, первый 4-портовый контроллер интерфейса SATA 3.0 48, второй 4-портовый контроллер интерфейса SATA 3.0 49, первый контроллер интерфейса Ethernet 50, второй контроллер интерфейса Ethernet 51, третий контроллер интерфейса Ethernet 52 и блок управления сигналами тактовой синхронизации 53, выход которого соединен с объединенными входами синхронизации всех блоков устройства, выход которого соединен с выходом контроллера физического уровня канала ввода-вывода 33, двухсторонний вход выход которого соединен с первым двухсторонним входом выходом контроллера канального уровня канала ввода-вывода 34, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом коммутатора первого уровня 35, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого составного контроллера 37, третий двухсторонний вход выход коммутатора первого уровня 35 соединен с первым двухсторонним входом выходом первого контроллера линка PCIe 38, четвертый двухсторонний вход выход коммутатора первого уровня 35 соединен с первым двухсторонним входом выходом второго контроллера линка PCIe 39, пятый двухсторонний вход выход коммутатора первого уровня 35 соединен с первым двухсторонним входом выходом звукового контроллера интерфейса HDA 47, шестой двухсторонний вход выход коммутатора первого уровня 35 соединен с первым двухсторонним входом выходом первого 4-х портового контроллера интерфейса SATA 3.0 48, седьмой двухсторонний вход выход коммутатора первого уровня 35 соединен с первым двухсторонним входом выходом второго 4-х портового контроллера интерфейса SATA 3.0 49, восьмой двухсторонний вход выход коммутатора первого уровня 35 соединен с первым двухсторонним входом выходом коммутатора второго уровня 36, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого 4-х портового контроллера интерфейса USB 40, третий двухсторонний вход выход коммутатора второго уровня 36 соединен с первым двухсторонним входом выходом второго 4-х портового контроллера интерфейса USB 41, четвертый двухсторонний вход выход коммутатора второго уровня 36 соединен с первым двухсторонним входом выходом второго составного контроллера 42, пятый двухсторонний вход выход коммутатора второго уровня 36 соединен с первым двухсторонним входом выходом первого контроллера интерфейса Ethernet 50, шестой двухсторонний вход выход коммутатора второго уровня 36 соединен с первым двухсторонним входом выходом второго контроллера интерфейса Ethernet 51, седьмой двухсторонний вход выход коммутатора второго уровня 36 соединен с первым двухсторонним входом выходом третьего контроллера интерфейса Ethernet 52, восьмой двухсторонний вход выход коммутатора второго уровня 36 соединен с первым двухсторонним входом выходом контроллера двух устройств интерфейса IDE 43, девятый двухсторонний вход выход коммутатора второго уровня 36 соединен с первым двухсторонним входом выходом третьего составного контроллера 44, десятый двухсторонний вход выход коммутатора второго уровня 36 соединен с первым двухсторонним входом выходом контроллера управления питанием и энергосбережением 45, одиннадцатый двухсторонний вход выход коммутатора второго уровня 36 соединен с первым двухсторонним входом выходом, контроллер интерфейса PCI 46, вторые двухсторонние входы выходы контроллера двух устройств интерфейса IDE 43, третьего составного контроллера 44, контроллера управления питанием и энергосбережением 45, контроллера интерфейса PCI 46, звукового контроллера интерфейса HDA 47, первого контроллера интерфейса Ethernet 50, второго контроллера интерфейса Ethernet 51 и третьего контроллера интерфейса Ethernet 52 соединены с соответствующими двухсторонними входами выходами устройства, вторые и третьи двухсторонние входы выходы первого составного контроллера 37, первого контроллера линка PCIe 38 и второго составного контроллера 42 соединены с соответствующими двухсторонними входами выходами устройства, с второго по пятый двухсторонние входы выходы второго контроллера линка PCIe 39, первого 4-х портового контроллера интерфейса USB 40, второго 4-х портового контроллера интерфейса USB 41, первого 4-х портового контроллера интерфейса SATA 3.0 48, второго 4-х портового контроллера интерфейса SATA 3.0 49 соединены с соответствующими двухсторонними входами выходами устройства, причем соединение между двухсторонними входами выходами коммутатора первого уровня 35 и контроллера канального уровня канала ввода-вывода 34, коммутатора второго уровня 36, первого составного контроллера 37, первого контроллера линка PCIe 38, второго контроллера линка PCIe 39, звукового контроллера интерфейса HDA 47, первого 4-х портового контроллера интерфейса SATA 3.0 48, второго 4-х портового контроллера интерфейса SATA 3.0 49 осуществляется интерфейсом типа «Slink», причем соединение между двухсторонними входами выходами коммутатора второго уровня 36 и первого 4-х портового контроллера интерфейса USB 40, второго 4-х портового контроллера интерфейса USB 41, второго составного контроллера 42, контроллера двух устройств интерфейса IDE 43, третьего составного контроллера 44, контроллера управления питанием и энергосбережением 45, контроллера интерфейса PCI 46, первого контроллера интерфейса Ethernet 50, второго контроллера интерфейса Ethernet 51 и третьего контроллера интерфейса Ethernet 52 осуществляется интерфейсом типа «IOlink».

Работа процессорного модуля МВС-8С (фиг. 1, фиг. 2) заключается в следующем.

При выполнении операций блоки системы выполняют следующие функции.

Многофункциональный контроллер КПИ-2 1 предназначен для обеспечения подключения периферийных интерфейсов.

Шина ввода/вывода 2 обеспечивает подключение периферийных устройств PCIe.

Элементы питания 3, 4, 5, 6, 7 обеспечивают питание компонентов, находящиеся на первой многослойной печатной платы СВ-КПИ 27.

Температурный датчик 8 передает данные о нагреве системы.

Мультиплексор 9 осуществляет мультиплексирование шины I2C.

Расширительный модуль ввода/вывода 10 обеспечивает сопряжение мониторов питания 11, 13, светодиодов 4 шт. 12 и многофункционального контроллера КПИ-2 1.

Мониторы питания 11, 13 обеспечивают заданную последовательность включений питания.

Светодиоды 4 шт. 12 показывают различные режимы работы модуля.

Процессоры 14, 16, 18 и 20 являются многофункциональными вычислительными устройствами.

Узлы ОЗУ 15, 17, 19, 21 содержат по 4 слота каждый и осуществляют хранение входных, промежуточных и выходных данных соответствующих процессоров 14, 16, 18 и 20.

Мультиплексор 22 осуществляет мультиплексирование шины I2C.

Элементы питания 23, 24, 25 обеспечивают питание компонентов, находящиеся на второй многослойной печатной платы СВ-КПУ 28.

Мультиплексор 26 осуществляет мультиплексирование шины I2C.

Третья многослойная печатная плата 30 является системным менеджментом и обеспечивает работу процессорного модуля iMX287 29.

Процессорный модуль iMX287 29 является многофункциональным вычислительным устройством и служит для отслеживания текущих состояний компонентов модуля и изменения их параметров по шинам I2C. Собранная информация может передаваться и приниматься по интерфейсу Ethernet через Коммутатор 31 на Сервер управляющий 32, с которого осуществляется управление всей системой.

Для осуществления возможности мониторинга состояния различных систем в модулях предусмотрен системный менеджмент 30. Он позволяет отслеживать текущее состояние компонентов модуля (таких как датчики температуры 8, встроенные термосенсоры процессоров и т.д.) и менять их параметры. Собранная информация может передаваться и приниматься по интерфейсу Ethernet на управляющий сервер 32, с которого осуществляется управление системой.

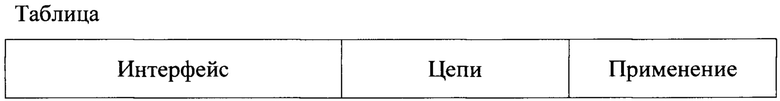

Менеджмент 30 помощью интерфейса I2C соединяется со всеми необходимыми компонентами модуля. Также менеджер соединяется и другими интерфейсами с процессорной 28 и периферийной 27 платами. Перечень интерфейсов приведен ниже в таблице:

Во время работы системы осуществляется управление энергопотреблением.

Для этого в системе Эльбрус-8С есть система контроля температуры и частоты процессора. Эта система опрашивает восемь термосенсоров, входящих в состав процессоров 14, 16, 18, 20, собирает данные о температуре кристалла и на основании полученных данных корректирует частоту. Полученные данные о температуре и частоте можно получить несколькими способами: из внутренних регистров процессора, по отладочному интерфейсу JTAG 1 и 29 и по интерфейсу I2C (связи 14-26, 16-26, 18-26, 20-26, 26-29).

Управление энергопотреблением в ОС «Эьбрус» заключается в реализации поддержки термальной зоны и двух механизмов управления энергопотреблением: статического и динамического.

Поддержка термальной зоны состоит из программного обеспечения уровня ядра операционной системы, реализующего взаимодействие с датчиками температуры через шину I2C. В качестве датчиков температуры в используются микросхемы LM96163 8, позволяющие выполнять мониторинг встроенных в микропроцессоры термодиодов и выдавать сигнал alarm в случае превышения критического значения температуры, задаваемого путем записи этого значения в регистр LM96163. Наличие термальной зоны позволяет отследить ситуацию перегрева микропроцессора: по сигналу alarm операционная система может принять решение использовать пассивное или активное охлаждение. Пассивное охлаждение - отключение процессорных ядер, с точки зрения энергопотребления является оптимальным. Пассивное охлаждение реализуется с помощью статического механизма управления энергопотреблением.

Статический механизм основан на использовании алгоритмов логического включения-выключения процессорных ядер (механизм cpu hotplug), динамический - на использовании архитектурно независимой реализации подсистемы сна, заимствованной из ядра Linux-2.6.33 (подсистема cpuidle).

Статический механизм предназначен для решения задач принудительного снижения энергопотребления вычислительного комплекса, которое необходимо в следующих случаях:

- временный перевод вычислительного комплекса на резервный источник питания (аккумулятор, или дизельный генератор);

- перегрев микропроцессоров из-за тяжелых внешних температурных условий;

- экономия в случае явного отсутствия загруженности вычислительного комплекса задачами.

Само по себе логическое включение-выключение процессорных ядер не приводит к снижению потребляемой мощности, если в реализации микропроцессора не поддержана возможность реального отключения синхроимпульса или синхроимпульса и напряжения. В микропроцессорах аппаратно поддержана возможность отключения-включения синхроимпульса на процессорном ядре после логического выключения-включения. Это позволяет экономить до 30% потребляемой вычислительным комплексом мощности при использовании статического механизма.

Статический механизм предназначен для отключения процессорных ядер по команде оператора, и не предназначен для автоматического отслеживания периодов простоя вычислительного комплекса и управления энергосбережением в течение этих периодов. Для выполнения такого отслеживания и управления предназначен динамический механизм.

При использовании динамического механизма операционной системой «Эльбрус» выполняется отслеживание состоянии простоя (отсутствия задач) С0, в которых специальные алгоритмы принятия решений имеют возможность с помощью специального архитектурно-зависимого драйвера перевести процессорное ядро в одно из состояний сна, поддержанное в аппаратной реализации микропроцессора.

Динамический механизм позволяет экономить до 10% мощности потребляемой вычислительным комплексом.

Загрузка операционной системы по вычислительной сети.

Для реализации функции удаленного управления обеспечена возможность загрузки ОС по локальной вычислительной сети (ЛВС) Ethernet.

На Сервере Управляющем 32, подключенный к вычислительной сети ЛВС, расположены:

- образы корневых файловых систем клиентов, файлы и программы, обеспечивающие загрузку по сети;

- образы корневых файловых систем клиентов, файлы и программы, обеспечивающие загрузку по сети.

На вычислительный модуль, подключенный к сети, будет загружаться операционная система.

Для первоначальной настройки и диагностики функционирования бездискового клиента требуется наличие дополнительное подключение через UART.

Таким образом, система управления вычислительного узла в составе модульной вычислительной платформы «Эльбрус8» расширение функциональных возможностей за счет обеспечения возможности построения серверов различного назначения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессорный модуль системы хранения данных | 2018 |

|

RU2680744C1 |

| Плата системная вычислительного модуля | 2024 |

|

RU2840229C1 |

| Плата системная вычислительного модуля | 2024 |

|

RU2822305C1 |

| СЕРВЕР | 2022 |

|

RU2804258C1 |

| Высокопроизводительная вычислительная платформа на базе процессоров с разнородной архитектурой | 2016 |

|

RU2635896C1 |

| СИСТЕМНАЯ ВЫЧИСЛИТЕЛЬНАЯ ПЛАТА | 2024 |

|

RU2828793C1 |

| Малогабаритный высокопроизводительный вычислительный модуль на базе многопроцессорной Системы-на-Кристалле | 2021 |

|

RU2778213C1 |

| КОНТРОЛИРУЮЩИЙ ПУНКТ ВВОДА-ВЫВОДА ДИСКРЕТНЫХ СИГНАЛОВ | 2019 |

|

RU2714025C1 |

| Плата-переходник для установки в базовые устройства с процессорным модулем форм-фактора COM EXPRESS | 2024 |

|

RU2838350C1 |

| Многоканальный аппаратно-программный комплекс высокоскоростной цифровой обработки сигналов | 2018 |

|

RU2714493C2 |

Изобретение относится к вычислительной технике и может быть использовано для построения серверов различного назначения. Технический результат заключается в повышении быстродействия при обеспечении возможности построения серверов различного назначения. Технический результат достигается за счет системы управления вычислительного узла в составе модульной вычислительной платформы «Эльбрус8» для построения серверов различного назначения, которая содержит многофункциональный контроллер, шину ввода-вывода, пять элементов питания, температурный датчик, мультиплексор, расширительный модуль ввода/вывода, два монитора питания, светодиоды, находящиеся на первой многослойной печатной плате, четыре процессора, четыре узла ОЗУ, два мультиплексора, три элемента питания, находящиеся на второй многослойной печатной плате, процессорный модуль, находящийся на третьей многослойной печатной плате, коммутатор и управляющий сервер. 1 з.п. ф-лы, 1 табл., 2 ил.

1. Система управления вычислительного узла в составе модульной вычислительной платформы для построения серверов различного назначения, содержащая печатную плату, процессор, подключенный к оперативной памяти, контроллер периферийных интерфейсов, шины ввода-вывода, отличающаяся тем, что в ней в качестве контроллера периферийных интерфейсов используется многофункциональный контроллер КПИ-2 и введены пять элементов питания, температурный датчик, мультиплексор, расширительный модуль ввода/вывода, два монитора питания, светодиоды, находящиеся на первой многослойной печатной плате, три процессора, четыре узла ОЗУ, два мультиплексора, три элемента питания, находящиеся на второй многослойной печатной плате, процессорный модуль, находящийся на третьей многослойной печатной плате, коммутатор и сервер управляющий, двухсторонний вход выход которого соединен с вторым двухсторонним входом выходом коммутатора, первый двухсторонний вход выход которого соединен с седьмым двухсторонним входом выходом процессорного модуля, первый, второй, третий и четвертый двухсторонние входы выходы которого соединены соответственно, каждый отдельно, с одноименными двухсторонними входами выходами контроллера периферийных интерфейсов, пятый, шестой, седьмой и восьмой двухсторонние входы выходы которого соединены соответственно, каждый отдельно, с первым, вторым, третьим и четвертым двухсторонними входами выходами мультиплексора, пятый двухсторонний вход выход которого соединен с вторым двухсторонним входом выходом мультиплексора, первый двухсторонний вход выход которого соединен с объединенными двухсторонними входами выходами первого, второго, третьего и четвертого процессоров, двухсторонний вход выход мультиплексора соединен с пятым двухсторонним входом выходом процессорного модуля, шестой двухсторонний вход выход которого соединен с пятым двухсторонним входом выходом расширительного модуля ввода/вывода, четвертый двухсторонний вход выход которого соединен с двухсторонним входом выходом второго монитора питания, двухсторонний вход выход первого монитора питания соединен с двухсторонним входом выходом расширительного модуля ввода/вывода, третий двухсторонний вход выход которого соединен с двухсторонним входом выходом светодиодов, первый двухсторонний вход выход расширительного модуля ввода/вывода с девятым двухсторонним входом выходом контроллера периферийных интерфейсов, двухсторонний вход выход шины ввода/вывода соединен с пятым двухсторонним входом выходом контроллера периферийных интерфейсов, шестой двухсторонний вход выход которого соединен с двухсторонними входами выходами с первого по пятый элементов питания, двухсторонние входы выходы с первого по четвертый узлы ОЗУ соединены соответственно, каждый отдельно, с первого по четвертый двухсторонними входами выходами первого мультиплексора, пятый двухсторонний вход выход которого соединен с двухсторонним входом выходом контроллера периферийных интерфейсов, двухсторонний вход мультиплексора соединен с двухсторонними входами выходами шестого, седьмого и восьмого элементов питания.

2. Система управления вычислительного узла в составе модульной вычислительной платформы для построения серверов различного назначения по п. 1, отличающаяся тем, что многофункциональный контроллер периферийных интерфейсов КПИ-2 содержит контроллер физического уровня канала ввода-вывода (WLCC_PHY), контроллер канального уровня канала ввода-вывода (WLCC_DLL), коммутатор первого уровня, коммутатор второго уровня, первый составной контроллер, первый контроллер линка PCIe, второй контроллер линка PCIe, первый 4-х портовый контроллер интерфейса USB, второй 4-х портовый контроллер интерфейса USB, второй составной контроллер, контроллер двух устройств интерфейса IDE, третий составной контроллер, контроллер управления питанием и энергосбережением, контроллер интерфейса PCI, звуковой контроллер интерфейса HDA, первый 4-портовый контроллер интерфейса SATA 3.0, второй 4-портовый контроллер интерфейса SATA 3.0, первый контроллер интерфейса Ethernet, второй контроллер интерфейса Ethernet, третий контроллер интерфейса Ethernet и блок управления сигналами тактовой синхронизации, выход которого соединен с объединенными входами синхронизации всех блоков устройства, выход которого соединен с выходом контроллера физического уровня канала ввода-вывода, двухсторонний вход выход которого соединен с первым двухсторонним входом выходом контроллера канального уровня канала ввода-вывода, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом коммутатора первого уровня, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого составного контроллера, третий двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом первого контроллера линка PCIe, четвертый двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом второго контроллера линка PCIe, пятый двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом звукового контроллера интерфейса HDA, шестой двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом первого 4-х портового контроллера интерфейса SATA 3.0, седьмой двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом второго 4-х портового контроллера интерфейса SATA 3.0, восьмой двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом коммутатора второго уровня, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого 4-х портового контроллера интерфейса USB, третий двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом второго 4-х портового контроллера интерфейса USB, четвертый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом второго составного контроллера, пятый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом первого контроллера интерфейса Ethernet, шестой двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом второго контроллера интерфейса Ethernet, седьмой двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом третьего контроллера интерфейса Ethernet, восьмой двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом контроллера двух устройств интерфейса IDE, девятый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом третьего составного контроллера, десятый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом контроллера управления питанием и энергосбережением, одиннадцатый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом, контроллер интерфейса PCI, вторые двухсторонние входы выходы контроллера двух устройств интерфейса IDE, третьего составного контроллера, контроллера управления питанием и энергосбережением, контроллера интерфейса PCI, звукового контроллера интерфейса HDA, первого контроллера интерфейса Ethernet, второго контроллера интерфейса Ethernet и третьего контроллера интерфейса Ethernet соединены с соответствующими двухсторонними входами выходами устройства, вторые и третьи двухсторонние входы выходы первого составного контроллера, первого контроллера линка PCIe и второго составного контроллера соединены с соответствующими двухсторонними входами выходами устройства, с второго по пятый двухсторонние входы выходы второго контроллера линка PCIe, первого 4-х портового контроллера интерфейса USB, второго 4-х портового контроллера интерфейса USB, первого 4-х портового контроллера интерфейса SATA 3.0, второго 4-х портового контроллера интерфейса SATA 3.0 соединены с соответствующими двухсторонними входами выходами устройства, причем соединение между двухсторонними входами выходами коммутатора первого уровня и контроллера канального уровня канала ввода-вывода, коммутатора второго уровня, первого составного контроллера, первого контроллера линка PCIe, второго контроллера линка PCIe, звукового контроллера интерфейса HDA, первого 4-х портового контроллера интерфейса SATA 3.0, второго 4-х портового контроллера интерфейса SATA 3.0 осуществляется интерфейсом типа «Slink», причем соединение между двухсторонними входами выходами коммутатора второго уровня и первого 4-х портового контроллера интерфейса USB, второго 4-х портового контроллера интерфейса USB, второго составного контроллера, контроллера двух устройств интерфейса IDE, третьего составного контроллера, контроллера управления питанием и энергосбережением, контроллера интерфейса PCI, первого контроллера интерфейса Ethernet, второго контроллера интерфейса Ethernet и третьего контроллера интерфейса Ethernet осуществляется интерфейсом типа «IOlink».

| 0 |

|

SU151425A1 | |

| ВЫЧИСЛИТЕЛЬНЫЙ КЛАСТЕР С ПОГРУЖНОЙ СИСТЕМОЙ ОХЛАЖДЕНИЯ | 2016 |

|

RU2632400C1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| ЛИНЕЙНЫЙ ЭЛЕКТРОДВИГАТЕЛЬ | 1990 |

|

RU2031518C1 |

| US 7761687 B2, 20.07.2010 | |||

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

Авторы

Даты

2019-07-23—Публикация

2018-12-27—Подача