Изобретение относится к вычислительной технике и может быть использована для создания центров обработки данных, супер-ЭВМ и в качестве узла кластера.

Известен ряд вычислительных систем с распределенной памятью, содержащих процессоры, объединенные некоторой коммуникационной средой. Наиболее известными среди них являются: Intel Paragon, IBM SP1/SP2, Cray T3D и многие другие, включая отечественные кластерные и массово-параллельные установки, например, МВС-1000М, СКИФ Syberia и т.д.

Недостатком таких вычислительных систем является низкая производительность при решении реальных задач.

Наиболее близким к заявляемому является вычислительный модуль многопроцессорной крейтовой системы и многопроцессорная система из этих модулей [РФ №151425 Ul, G06F 15/16, 10.04.2015], включающий печатную плату и размещенные на ней: процессор с выводом межпроцессорных каналов, подключенный к оперативной памяти, а также к контроллеру периферийных интерфейсов посредством шины ввода-вывода, контроллер периферийных интерфейсов с подключением к нему шин периферийных интерфейсов, оперативную память, соединители для подключения к коммутационной панели, выполненные с возможностью подключения межпроцессорных каналов и шин периферийных интерфейсов к коммутационной панели, постоянное запоминающее устройство с записанной в нем программой начальной загрузки.

Недостатком данного устройства является низкое быстродействие, что не позволяет использовать его в качестве узла кластера.

Техническим результатом является повышение быстродействия и расширение функциональных возможностей за счет возможности использования его в качестве узла кластера.

Технический результат достигается тем, что в «Процессорный модуль системы хранения данных», содержащий, процессор, подключенный к оперативной памяти, контроллер периферийных интерфейсов дополнительно в нем в качестве контроллера периферийных в нем используется многофункциональный контроллер КПИ-2, введены процессор, многофункциональный контроллер КПИ-2, восемь разъемов для подключения модуля ОЗУ, соединитель JTAG, два порта для подключения устройств с интерфейсом SATA, RS-232 трансмиттер, порт для подключения устройств с интерфейсом UART, встроенный графический процессор, порт для подключения устройств с интерфейсом RS232, VGA, мультиплексор, шесть портов для подключения устройств с интерфейсом PCIe, две микросхемы физического уровня Gigabit Ethernet, четыре соединителя Ethernet, аппаратный модуль доверенной нагрузки, порт для подключения устройств с интерфейсом USB/Ethernet, два порта для подключения устройств с интерфейсом USB, пять разъемов для подключения устройств с интерфейсом USB, интегральная схема переключателя шины передачи данных, разъем, микросхема часов реального времени, интегральная схема переключателя шины передачи данных, менеджер, мультиплексор, RS-232 трансмиттер и разъем, двухсторонний вход выход второго порта для подключения устройств с интерфейсом SATA соединен с вторым двухсторонним входом выходом второго многофункционального контроллера КПИ-2, третий двухсторонний вход выход которого соединен с первым двухсторонним входом выходом RS-232 трансмиттера, второй двухсторонний вход выход которого соединен с двухсторонним входом выходом разъема, четвертый двухсторонний вход выход второго многофункционального контроллера КПИ-2 соединен с двухсторонним входом выходом пятого порта для подключения устройств с интерфейсом PCIe, и мультиплексора, первый выход которого соединен с входом пятого порта для подключения устройств с интерфейсом PCIe, а второй выход мультиплексора соединен с входом шестого порта для подключения устройств с интерфейсом PCIe, пятый двухсторонний вход выход второго многофункционального контроллера КПИ-2 соединен с первым двухсторонним входом выходом четвертого порта для подключения устройств с интерфейсом PCIe, второй двухсторонний вход выход которого соединен с шестым двухсторонним входом выходом второго многофункционального контроллера КПИ-2, седьмой двухсторонний вход выход которого соединен с первым двухсторонним входом выходом второй микросхемы физического уровня Gigabit Ethernet, второй двухсторонний вход выход которой соединен с двухсторонним входом выходом четвертого соединителя Ethernet, двухсторонние входы выходы пятого, четвертого, третьего и второго разъемов для подключения устройств с интерфейсом USB соединены каждый отдельно соответственно с восьмым, девятым, десятым и одиннадцатым двухсторонними входами выходами второго многофункционального контроллера КПИ-2, первый двухсторонний вход выход которого соединен с вторым двухсторонним входом выходом второго процессора, вход которого соединен с выходом первого процессора, первый двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого многофункционального контроллера КПИ-2, второй двухсторонний вход выход которого соединен с двухсторонним входом выходом первого порта для подключения устройств с интерфейсом SATA, выход порта для подключения устройств с интерфейсом UART соединен с входом RS-232 трансмиттер, первый двухсторонний вход выход которого соединен с третьим двухсторонним входом выходом первого многофункционального контроллера КПИ-2, четвертый двухсторонний вход выход которого соединен с первым двухсторонним входом выходом встроенного графического процессора, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом порта для подключения устройств с интерфейсом RS232, VGA, второй двухсторонний вход выход которого соединен с вторым двухсторонним входом выходом RS-232 трансмиттер, вход второго порта для подключения устройств с интерфейсом PCIe соединен с вторым выходом мультиплексора, первый выход которого соединен с входом первого порта для подключения устройств с интерфейсом PCIe, двухсторонний вход выход которого соединен с объединенными двухсторонним входом мультиплексора и пятым двухсторонним входом выходом первого многофункционального контроллера КПИ-2, шестой двухсторонний вход выход которого соединен с первым двухсторонним входом выходом третьего порта для подключения устройств с интерфейсом PCIe, второй двухсторонний вход выход которого соединен с седьмым двухсторонним входом выходом первого многофункционального контроллера КПИ-2, двухсторонний вход выход второго соединителя Ethernet соединен с третьим двухсторонним входом выходом первой микросхемы физического уровня Gigabit Ethernet, второй двухсторонний вход выход которой соединен с двухсторонним входом выходом первого соединителя Ethernet, первый двухсторонний вход выход микросхемы физического уровня Gigabit Ethernet соединен с восьмым двухсторонним входом выходом первого многофункционального контроллера КПИ-2, двухсторонний вход выход третьего соединителя Ethernet соединен с вторым двухсторонним входом выходом аппаратного модуля доверенной нагрузки, первый двухсторонний вход выход которого соединен с девятым двухсторонним входом выходом первого многофункционального контроллера КПИ-2, десятый, одиннадцатый, двенадцатый и тринадцатый двухсторонние входы выходы которого соединены каждый отдельно соответственно с двухсторонними входами выходами аппаратного модуля доверенной нагрузки, порта для подключения устройств с интерфейсом USB/Ethernet, первого порта для подключения устройств с интерфейсом USB, первого разъема для подключения устройств с интерфейсом USB и второго порта для подключения устройств с интерфейсом USB, второй, третий, четвертый и пятый двухсторонние входы выходы первого процессора соединены каждый отдельно соответственно с двухсторонними входами выходами первого, второго, третьего и четвертого разъемов для подключения модуля ОЗУ, второй, третий, четвертый и пятый двухсторонние входы выходы второго процессора соединены каждый отдельно соответственно с двухсторонними входами выходами пятого, шестого, седьмого и восьмого разъемов для подключения модуля ОЗУ, выход интегральной схемы переключателя шины передачи данных соединен с входом менеджера выход которого соединен с входом интегральной схемы переключателя шины передачи данных и вторым входом интегральной схемы переключателя шины передачи данных, двухсторонний вход выход микросхемы часов реального времени соединен с объединенными двухсторонними входами выходами интегральной схемы переключателя шины передачи данных, разъема и третьим двухсторонним входом выходом интегральной схемы переключателя шины передачи данных, первый двухсторонний вход выход которой соединен с четырнадцатым двухсторонним входом выходом первого многофункционального контроллера КПИ-2, выход соединителя JTAG соединен с входом первого процессора, выход которого соединен с входом второго процессора, выход которого соединен с входом соединителя JTAG, причем многофункциональный контроллер периферийных интерфейсов КПИ-2 содержит контроллер физического уровня канала ввода-вывода (WLCC_PHY), контроллер канального уровня канала ввода-вывода (WLCC_DLL), коммутатор первого уровня, коммутатор второго уровня, первый составной контроллер, первый контроллер линка PCIe, второй контроллер линка PCIe, первый 4-х портовый контроллер интерфейса USB, второй 4-х портовый контроллер интерфейса USB, второй составной контроллер, контроллер двух устройств интерфейса IDE, третий составной контроллер, контроллер управления питанием и энергосбережением, контроллер интерфейса PCI, звуковой контроллер интерфейса HDA, первый 4-портовый контроллер интерфейса SATA 3.0, второй 4-портовый контроллер интерфейса SATA 3.0, первый контроллер интерфейса Ethernet, второй контроллер интерфейса Ethernet, третий контроллер интерфейса Ethernet и блок управления сигналами тактовой синхронизации, выход которого соединен с объединенными входами синхронизации всех блоков устройства, выход которого соединен с выходом контроллера физического уровня канала ввода-вывода, двухсторонний вход выход которого соединен с первым двухсторонним входом выходом контроллера канального уровня канала ввода-вывода, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом коммутатора первого уровня, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого составного контроллера, третий двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом первого контроллера линка PCIe, четвертый двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом второго контроллера линка PCIe, пятый двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом звукового контроллера интерфейса HDA, шестой двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом первого 4-х портового контроллера интерфейса SATA 3.0, седьмой двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом второго 4-х портового контроллера интерфейса SATA 3.0, восьмой двухсторонний вход выход коммутатора первого уровня соединен с первым двухсторонним входом выходом коммутатора второго уровня, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого 4-х портового контроллера интерфейса USB, третий двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом второго 4-х портового контроллера интерфейса USB, четвертый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом второго составного контроллера, пятый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом первого контроллера интерфейса Ethernet, шестой двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом второго контроллера интерфейса Ethernet, седьмой двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом третьего контроллера интерфейса Ethernet, восьмой двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом контроллера двух устройств интерфейса IDE, девятый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом третьего составного контроллера, десятый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом контроллера управления питанием и энергосбережением, одиннадцатый двухсторонний вход выход коммутатора второго уровня соединен с первым двухсторонним входом выходом, контроллер интерфейса PCI, вторые двухсторонние входы выходы контроллера двух устройств интерфейса IDE, третьего составного контроллера, контроллера управления питанием и энергосбережением, контроллера интерфейса PCI, звукового контроллера интерфейса HDA, первого контроллера интерфейса Ethernet, второго контроллера интерфейса Ethernet и третьего контроллера интерфейса Ethernet соединены с соответствующими двухсторонними входами выходами устройства, вторые и третьи двухсторонние входы выходы первого составного контроллера, первого контроллера линка PCIe и второго составного контроллера соединены с соответствующими двухсторонними входами выходами устройства, с второго по пятый двухсторонние входы выходы второго контроллера линка PCIe, первого 4-х портового контроллера интерфейса USB, второго 4-х портового контроллера интерфейса USB, первого 4-х портового контроллера интерфейса SATA 3.0, второго 4-х портового контроллера интерфейса SATA 3.0 соединены с соответствующими двухсторонними входами выходами устройства, причем соединение между двухсторонними входами выходами коммутатора первого уровня и контроллера канального уровня канала ввода-вывода, коммутатора второго уровня, первого составного контроллера, первого контроллера линка PCIe, второго контроллера линка PCIe, звукового контроллера интерфейса HDA, первого 4-х портового контроллера интерфейса SATA 3.0, второго 4-х портового контроллера интерфейса SATA 3.0 осуществляется интерфейсом типа «Slink», причем соединение между двухсторонними входами выходами коммутатора второго уровня и первого 4-х портового контроллера интерфейса USB, второго 4-х портового контроллера интерфейса USB, второго составного контроллера, контроллера двух устройств интерфейса IDE, третьего составного контроллера, контроллера управления питанием и энергосбережением, контроллера интерфейса PCI, первого контроллера интерфейса Ethernet, второго контроллера интерфейса Ethernet и третьего контроллера интерфейса Ethernet осуществляется интерфейсом типа «IOlink».

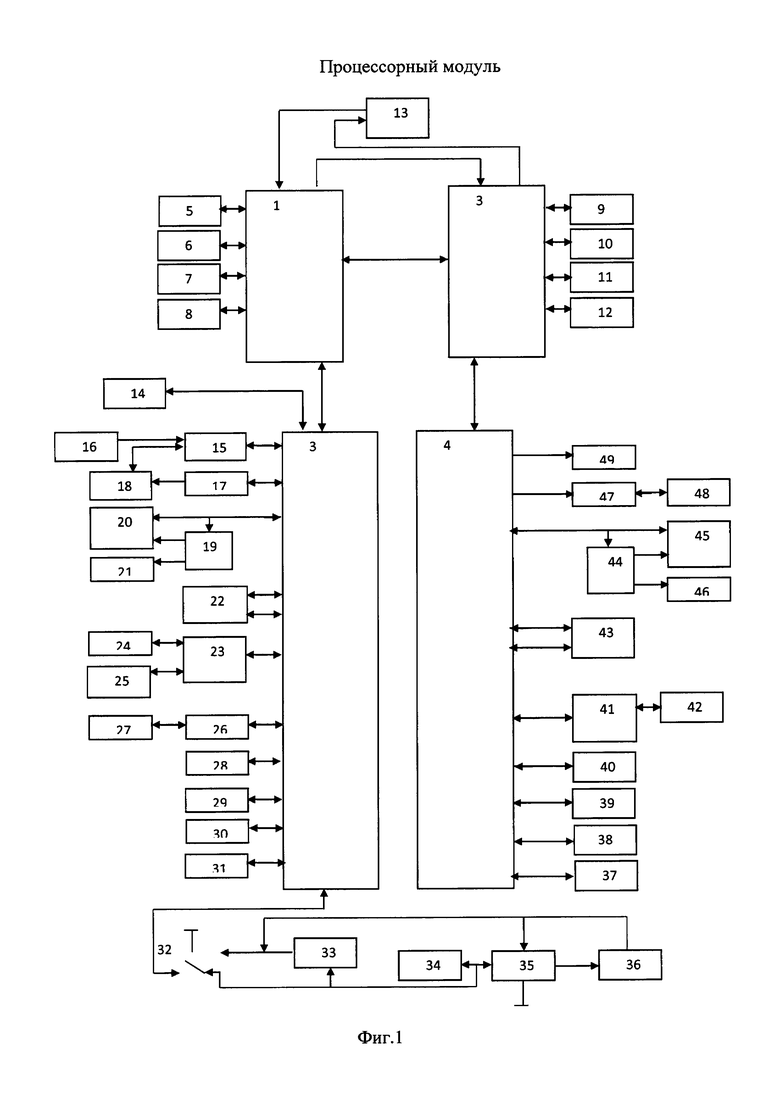

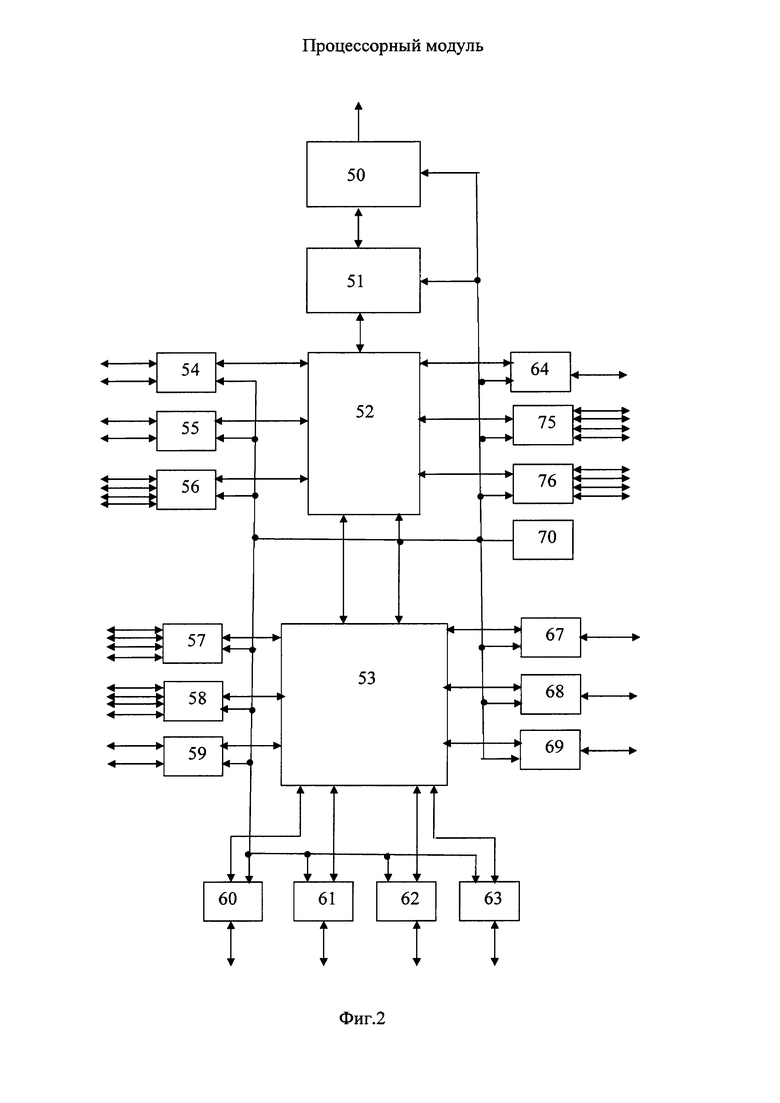

На фиг. 1 представлена блок-схема процессорного модуля. На фиг. 2 представлена блок-схема многофункционального контроллера КПИ-2.

Процессорный модуль системы хранения данных (МСХ-8С) (фиг. 1) содержит два процессора 1 и 2, два многофункциональных контроллера КПИ-2 3 и 4, восемь разъемов для подключения модуля ОЗУ 5, 6, 7, 8, 9, 10, 11 и 12, соединитель JTAG 13, два порта для подключения устройств с интерфейсом SATA 14 и 49, RS-232 трансмиттер 15, порт для подключения устройств с интерфейсом UART 16, встроенный графический процессор 17, порт для подключения устройств с интерфейсом RS232, VGA 18, мультиплексор 19, шесть портов для подключения устройств с интерфейсом PCIe 20, 21, 22, 43, 45 и 46, две микросхемы физического уровня Gigabit Ethernet 23 и 41, четыре соединителя Ethernet 24, 25, 27 и 42, аппаратный модуль доверенной нагрузки 26, порт для подключения устройств с интерфейсом USB/Ethernet 28, два порта для подключения устройств с интерфейсом USB 29 и 31, пять разъемов для подключения устройств с интерфейсом USB 30, 37, 38, 39 и 40, интегральная схема переключателя шины передачи данных 32, разъем 33, микросхема часов реального времени 34, интегральная схема переключателя шины передачи данных 35, менеджер 36, мультиплексор 44, RS-232 трансмиттер 47 и разъем 48.

Многофункциональный контроллер КПИ-2 3(4) (фиг. 2) содержит контроллер физического уровня канала ввода-вывода 50 (WLCC PHY), контроллер канального уровня канала ввода-вывода 51 (WLCC_DLL), коммутатор первого уровня 52, коммутатор второго уровня 53, первый составной контроллер 54, первый контроллер линка PCIe 55, второй контроллер линка PCIe 56, первый 4-х портовый контроллер интерфейса USB 57, второй 4-х портовый контроллер интерфейса USB 58, второй составной контроллер 59, контроллер двух устройств интерфейса IDE 60, третий составной контроллер 61, контроллер управления питанием и энергосбережением 62, контроллер интерфейса PCI 32 63, звуковой контроллер интерфейса HDA 64, первый 4-портовый контроллер интерфейса SATA 3.0 65, второй 4-портовый контроллер интерфейса SATA 3.0 66, первый контроллер интерфейса Ethernet 67, второй контроллер интерфейса Ethernet 68, третий контроллер интерфейса Ethernet 69 и блок управления сигналами тактовой синхронизации 70.

Процессорный модуль системы хранения данных (МСХ-8С) (фиг. 1-фиг. 2) содержит два процессора 1 и 2, два многофункциональных контроллера КПИ-2 3 и 4, восемь разъемов для подключения модуля ОЗУ 5, 6, 7, 8, 9, 10, 11 и 12, соединитель JTAG 13, два порта для подключения устройств с интерфейсом SATA 14 и 49, RS-232 трансмиттер 15, порт для подключения устройств с интерфейсом UART 16, встроенный графический процессор 17, порт для подключения устройств с интерфейсом RS232, VGA 18, мультиплексор 19, шесть портов для подключения устройств с интерфейсом PCIe 20, 21, 22, 43, 45 и 46, две микросхемы физического уровня Gigabit Ethernet 23 и 41, четыре соединителя Ethernet 24, 25, 27 и 42, аппаратный модуль доверенной нагрузки 26, порт для подключения устройств с интерфейсом USB/Ethernet 28, два порта для подключения устройств с интерфейсом USB 29 и 31, пять разъемов для подключения устройств с интерфейсом USB 30, 37, 38, 39 и 40, интегральная схема переключателя шины передачи данных 32, разъем 33, микросхема часов реального времени 34, интегральная схема переключателя шины передачи данных 35, менеджер 36, мультиплексор 44, RS-232 трансмиттер 47 и разъем 48, двухсторонний вход выход второго порта для подключения устройств с интерфейсом SATA 49 соединен с вторым двухсторонним входом выходом второго многофункционального контроллера КПИ-2 4, третий двухсторонний вход выход которого соединен с первым двухсторонним входом выходом RS-232 трансмиттера 47, второй двухсторонний вход выход которого соединен с двухсторонним входом выходом разъема 48, четвертый двухсторонний вход выход второго многофункционального контроллера КПИ-2 4 соединен с двухсторонним входом выходом пятого порта для подключения устройств с интерфейсом PCIe 45, и мультиплексора 44, первый выход которого соединен с входом пятого порта для подключения устройств с интерфейсом PCIe 45, а второй выход мультиплексора 44 соединен с входом шестого порта для подключения устройств с интерфейсом PCIe 45, пятый двухсторонний вход выход второго многофункционального контроллера КПИ-2 4 соединен с первым двухсторонним входом выходом четвертого порта для подключения устройств с интерфейсом PCIe 43, второй двухсторонний вход выход которого соединен с шестым двухсторонним входом выходом второго многофункционального контроллера КПИ-2 4, седьмой двухсторонний вход выход которого соединен с первым двухсторонним входом выходом второй микросхемы физического уровня Gigabit Ethernet 41, второй двухсторонний вход выход которой соединен с двухсторонним входом выходом четвертого соединителя Ethernet 42, двухсторонние входы выходы пятого 40, четвертого 39, третьего 38 и второго 37 разъемов для подключения устройств с интерфейсом USB соединены каждый отдельно соответственно с восьмым, девятым, десятым и одиннадцатым двухсторонними входами выходами второго многофункционального контроллера КПИ-2 4, первый двухсторонний вход выход которого соединен с вторым двухсторонним входом выходом второго процессора 2, вход которого соединен с выходом первого процессора 1, первый двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого многофункционального контроллера КПИ-2 3, второй двухсторонний вход выход которого соединен с двухсторонним входом выходом первого порта для подключения устройств с интерфейсом SATA 14, выход порта для подключения устройств с интерфейсом UART 16 соединен с входом RS-232 трансмиттер 15, первый двухсторонний вход выход которого соединен с третьим двухсторонним входом выходом первого многофункционального контроллера КПИ-2 3, четвертый двухсторонний вход выход которого соединен с первым двухсторонним входом выходом встроенного графического процессора 17, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом порта для подключения устройств с интерфейсом RS232, VGA 18, второй двухсторонний вход выход которого соединен с вторым двухсторонним входом выходом RS-232 трансмиттер 15, вход второго порта для подключения устройств с интерфейсом PCIe 21 соединен с вторым выходом мультиплексора 19, первый выход которого соединен с входом первого порта для подключения устройств с интерфейсом PCIe 20, двухсторонний вход выход которого соединен с объединенными двухсторонним входом мультиплексора 19 и пятым двухсторонним входом выходом первого многофункционального контроллера КПИ-2 3, шестой двухсторонний вход выход которого соединен с первым двухсторонним входом выходом третьего порта для подключения устройств с интерфейсом PCIe 22, второй двухсторонний вход выход которого соединен с седьмым двухсторонним входом выходом первого многофункционального контроллера КПИ-2 3, двухсторонний вход выход второго соединителя Ethernet 25 соединен с третьим двухсторонним входом выходом первой микросхемы физического уровня Gigabit Ethernet 23, второй двухсторонний вход выход которой соединен с двухсторонним входом выходом первого соединителя Ethernet 24, первый двухсторонний вход выход микросхемы физического уровня Gigabit Ethernet 23 соединен с восьмым двухсторонним входом выходом первого многофункционального контроллера КПИ-2 3, двухсторонний вход выход третьего соединителя Ethernet 27 соединен с вторым двухсторонним входом выходом аппаратного модуля доверенной нагрузки 26, первый двухсторонний вход выход которого соединен с девятым двухсторонним входом выходом первого многофункционального контроллера КПИ-2 3, десятый, одиннадцатый, двенадцатый и тринадцатый двухсторонние входы выходы которого соединены каждый отдельно соответственно с двухсторонними входами выходами аппаратного модуля доверенной нагрузки 26, порта для подключения устройств с интерфейсом USB/Ethernet 28, первого порта для подключения устройств с интерфейсом USB 29, первого разъема для подключения устройств с интерфейсом USB 30 и второго порта для подключения устройств с интерфейсом USB 31, второй, третий, четвертый и пятый двухсторонние входы выходы первого процессора 1 соединены каждый отдельно соответственно с двухсторонними входами выходами первого 5, второго 6, третьего 7 и четвертого 8 разъемов для подключения модуля ОЗУ, второй, третий, четвертый и пятый двухсторонние входы выходы второго процессора 2 соединены каждый отдельно соответственно с двухсторонними входами выходами пятого 9, шестого 10, седьмого 11 и восьмого 12 разъемов для подключения модуля ОЗУ, выход интегральной схемы переключателя шины передачи данных 35 соединен с входом менеджера 36 выход которого соединен с входом интегральной схемы переключателя шины передачи данных 35 и вторым входом интегральной схемы переключателя шины передачи данных 32, двухсторонний вход выход микросхемы часов реального времени 34 соединен с объединенными двухсторонними входами выходами интегральной схемы переключателя шины передачи данных 35, разъема 33 и третьим двухсторонним входом выходом интегральной схемы переключателя шины передачи данных 32, первый двухсторонний вход выход которой соединен с четырнадцатым двухсторонним входом выходом первого многофункционального контроллера КПИ-2 3, выход соединителя JTAG 13 соединен с входом первого процессора 1, выход которого соединен с входом второго процессора 2, выход которого соединен с входом соединителя JTAG 13, причем многофункциональный контроллер КПИ-2 3(4) (фиг. 2) содержит контроллер физического уровня канала ввода-вывода 50 (WLCC_PHY), контроллер канального уровня канала ввода-вывода 51 (WLCC_DLL), коммутатор первого уровня 52, коммутатор второго уровня 53, первый составной контроллер 54, первый контроллер линка PCIe 55, второй контроллер линка PCIe 56, первый 4-х портовый контроллер интерфейса USB 57, второй 4-х портовый контроллер интерфейса USB 58, второй составной контроллер 59, контроллер двух устройств интерфейса IDE 60, третий составной контроллер 61, контроллер управления питанием и энергосбережением 62, контроллер интерфейса PCI 32 63, звуковой контроллер интерфейса HDA 64, первый 4-портовый контроллер интерфейса SATA 3.0 65, второй 4-портовый контроллер интерфейса SATA 3.0 66, первый контроллер интерфейса Ethernet 67, второй контроллер интерфейса Ethernet 68, третий контроллер интерфейса Ethernet 69 и блок управления сигналами тактовой синхронизации 70, выход которого соединен с объединенными входами синхронизации всех блоков устройства, выход которого соединен с выходом контроллера физического уровня канала ввода-вывода 50, двухсторонний вход выход которого соединен с первым двухсторонним входом выходом контроллера канального уровня канала ввода-вывода 51, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом коммутатора первого уровня 52, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого составного контроллера 54, третий двухсторонний вход выход коммутатора первого уровня 52 соединен с первым двухсторонним входом выходом первого контроллера линка PCIe 55, четвертый двухсторонний вход выход коммутатора первого уровня 52 соединен с первым двухсторонним входом выходом второго контроллера линка PCIe 56, пятый двухсторонний вход выход коммутатора первого уровня 52 соединен с первым двухсторонним входом выходом звукового контроллера интерфейса HDA 64, шестой двухсторонний вход выход коммутатора первого уровня 52 соединен с первым двухсторонним входом выходом первого 4-х портового контроллера интерфейса SATA 3.0 65, седьмой двухсторонний вход выход коммутатора первого уровня 52 соединен с первым двухсторонним входом выходом второго 4-х портового контроллера интерфейса SATA 3.0 66, восьмой двухсторонний вход выход коммутатора первого уровня 52 соединен с первым двухсторонним входом выходом коммутатора второго уровня 53, второй двухсторонний вход выход которого соединен с первым двухсторонним входом выходом первого 4-х портового контроллера интерфейса USB 57, третий двухсторонний вход выход коммутатора второго уровня 53 соединен с первым двухсторонним входом выходом второго 4-х портового контроллера интерфейса USB 58, четвертый двухсторонний вход выход коммутатора второго уровня 53 соединен с первым двухсторонним входом выходом второго составного контроллера 59, пятый двухсторонний вход выход коммутатора второго уровня 53 соединен с первым двухсторонним входом выходом первого контроллера интерфейса Ethernet 67, шестой двухсторонний вход выход коммутатора второго уровня 53 соединен с первым двухсторонним входом выходом второго контроллера интерфейса Ethernet 68, седьмой двухсторонний вход выход коммутатора второго уровня 53 соединен с первым двухсторонним входом выходом третьего контроллера интерфейса Ethernet 69, восьмой двухсторонний вход выход коммутатора второго уровня 53 соединен с первым двухсторонним входом выходом контроллера двух устройств интерфейса IDE 60, девятый двухсторонний вход выход коммутатора второго уровня 53 соединен с первым двухсторонним входом выходом третьего составного контроллера 61, десятый двухсторонний вход выход коммутатора второго уровня 53 соединен с первым двухсторонним входом выходом контроллера управления питанием и энергосбережением 62, одиннадцатый двухсторонний вход выход коммутатора второго уровня 53 соединен с первым двухсторонним входом выходом, контроллер интерфейса PCI 63, вторые двухсторонние входы выходы контроллера двух устройств интерфейса IDE 60, третьего составного контроллера 61, контроллера управления питанием и энергосбережением 62, контроллера интерфейса PCI 63, звукового контроллера интерфейса HDA 64, первого контроллера интерфейса Ethernet 67, второго контроллера интерфейса Ethernet 68 и третьего контроллера интерфейса Ethernet 69 соединены с соответствующими двухсторонними входами выходами устройства, вторые и третьи двухсторонние входы выходы первого составного контроллера 54, первого контроллера линка PCIe 55 и второго составного контроллера 59 соединены с соответствующими двухсторонними входами выходами устройства, с второго по пятый двухсторонние входы выходы второго контроллера линка PCIe 56, первого 4-х портового контроллера интерфейса USB 57, второго 4-х портового контроллера интерфейса USB 58, первого 4-х портового контроллера интерфейса SATA 3.0 65, второго 4-х портового контроллера интерфейса SATA 3.0 66 соединены с соответствующими двухсторонними входами выходами устройства, причем соединение между двухсторонними входами выходами коммутатора первого уровня 52 и контроллера канального уровня канала ввода-вывода 51, коммутатора второго уровня 53, первого составного контроллера 54, первого контроллера линка PCIe 55, второго контроллера линка PCIe 56, звукового контроллера интерфейса HDA 64, первого 4-х портового контроллера интерфейса SATA 3.0 65, второго 4-х портового контроллера интерфейса SATA 3.0 66 осуществляется интерфейсом типа «Slink», причем соединение между двухсторонними входами выходами коммутатора второго уровня 53 и первого 4-х портового контроллера интерфейса USB 57, второго 4-х портового контроллера интерфейса USB 58, второго составного контроллера 59, контроллера двух устройств интерфейса IDE 60, третьего составного контроллера 61, контроллера управления питанием и энергосбережением 62, контроллера интерфейса PCI 63, первого контроллера интерфейса Ethernet 67, второго контроллера интерфейса Ethernet 68 и третьего контроллера интерфейса Ethernet 69 осуществляется интерфейсом типа «ЮНпк».

Работа (фиг. 1, фиг. 2) заключается в следующем.

В качестве узла кластера используется компьютер архитектуры «Эльбрус», реализованный в виде модуля МСХ-8С, оснащенный как минимум двумя портами Infiniband (либо Ethernet 10Gb) и двумя портами Ethernet 1Gb, а также достаточным объемом оперативной памяти для кэширования данных и хранения метаданных

Модуль МСХ-8С является 2-процессорной системой с производительностью до 1 трлн. оп/с, когерентной распределенной общей оперативной памятью до 128 Гбайт и дисковой памятью до 1 Тбайт и предназначен для работы в составе кластера.

При работе модуля его элементы выполняют следующие функции.

Процессоры 1(2) 1891VM10YA - представляет собой систему на кристалле.

Многофункциональный контроллер КПИ-2 3(4) предназначен для транслирования внутренних шин в стандартные интерфейсы.

Разъемы DDR3 DIMM 5, 6, 7, 8, 9, 10, 11 и 12 предназначены для подключения модуля ОЗУ.

Соединитель JTAG КПУ 13 предназначен для подключения средств диагностики и отладки многофункционального контроллера КПИ-2.

RS-232 трансмиттер 15 предназначен для связи аппаратного модуля доверенной нагрузки 26 с многофункциональным контроллером КПИ-2 3.

Порт для подключения устройств с интерфейсом UART 16 представляет собой аппаратный модуль доверенной нагрузки 26.

Встроенный графический процессор 17, обеспечивает передачу видеоданных по порту для подключения устройств с интерфейсом RS-232, VGA 18.

Мультиплексор 19 предназначен для организации двух связей PCIe х16 через порты 20 и 21.

Шесть портов для подключения устройств с интерфейсом PCIe 20, 21, 22, 43, 45 и 46 предназначены для подключения устройств с интерфейсом PCIe.

Две микросхемы физического уровня Gigabit Ethernet 23 и 41 обеспечивают связь многофункциональным контроллером КПИ-2 3 и 4 и соединителей 24, 25 и 42 посредством интерфейсов Gigabit Ethernet.

Через аппаратный модуль доверенной нагрузки 26 обеспечивается связь многофункционального контроллера КПИ-2 3 и соединителя Ethernet 27.

Порт для подключения устройств с интерфейсом USB/Ethernet 28 предназначен для подключения устройств с интерфейсом USB/Ethernet.

Два порта для подключения устройств с интерфейсом USB 29 и 31 предназначены для подключения устройств с интерфейсом USB.

Пять разъемов для подключения устройств с интерфейсом USB 30, 37, 38, 39 и 40 предназначены для подключения устройств с интерфейсом USB.

Интегральная схема переключателя шины передачи данных 32 осуществляет переключение шины передачи данных.

Разъем 33 служит для загрузки программы начального старта.

Микросхема часов реального времени 34 предназначена для учета хронометрических данных

Интегральная схема переключателя шины передачи данных 35 осуществляет переключение шины передачи данных.

Менеджер 36 предназначен для обеспечения удаленной загрузки программы начального старта.

Мультиплексор 44 предназначен для для организации двух связей PCIe х16 44 и 45.

RS-232 трансмиттер 47 обеспечивает подключение устройств с интерфейсом RS-232 через разъем 48.

Таким образом, процессорный модуль обеспечивает повышение быстродействия и расширение функциональных возможностей за счет возможности использования его в качестве узла кластера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система управления вычислительного узла в составе модульной вычислительной платформы "Эльбрус8" для построения серверов различного назначения | 2018 |

|

RU2695491C1 |

| СЕРВЕР | 2022 |

|

RU2804258C1 |

| Плата системная вычислительного модуля | 2024 |

|

RU2840229C1 |

| МНОГОФУНКЦИОНАЛЬНАЯ СТАНЦИЯ ОБМЕНА ДОКУМЕНТАЛЬНОЙ ИНФОРМАЦИЕЙ | 2011 |

|

RU2474869C1 |

| Плата-переходник для установки в базовые устройства с процессорным модулем форм-фактора COM EXPRESS | 2024 |

|

RU2838350C1 |

| СПОСОБ ОСУЩЕСТВЛЕНИЯ ДОСТУПА К ЦЕЛЕВОМУ ДИСКОВОМУ ЗАПОМИНАЮЩЕМУ УСТРОЙСТВУ, СИСТЕМА РАСШИРЕНИЯ ДИСКОВОЙ ЕМКОСТИ И ДИСКОВЫЙ МАССИВ | 2006 |

|

RU2399951C2 |

| КОНТРОЛИРУЮЩИЙ ПУНКТ ВВОДА-ВЫВОДА ДИСКРЕТНЫХ СИГНАЛОВ | 2019 |

|

RU2714025C1 |

| Высокопроизводительная вычислительная платформа на базе процессоров с разнородной архитектурой | 2016 |

|

RU2635896C1 |

| Плата системная вычислительного модуля | 2024 |

|

RU2822305C1 |

| ВИРТУАЛИЗАЦИЯ МАССОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА ДЛЯ ОБЛАЧНЫХ ВЫЧИСЛЕНИЙ | 2014 |

|

RU2649771C2 |

Изобретение относится к вычислительной технике и может быть использовано для создания центров обработки данных, суперЭВМ и в качестве узла кластера. Техническим результатом является повышение быстродействия и расширение функциональных возможностей за счет возможности использования его в качестве узла кластера. Процессорный модуль системы хранения данных содержит два процессора, два многофункциональных контроллера КПИ-2, восемь разъемов для подключения модуля ОЗУ, соединитель JTAG, два порта для подключения устройств с интерфейсом SATA, RS-232 трансмиттер, порт для подключения устройств с интерфейсом UART, встроенный графический процессор, порт для подключения устройств с интерфейсом RS232, VGA, мультиплексор, шесть портов для подключения устройств с интерфейсом PCIe, две микросхемы физического уровня Gigabit Ethernet, четыре соединителя Ethernet, аппаратный модуль доверенной нагрузки, порт для подключения устройств с интерфейсом USB/Ethernet, два порта для подключения устройств с интерфейсом USB, пять разъемов для подключения устройств с интерфейсом USB, интегральная схема переключателя шины передачи данных, разъем, микросхема часов реального времени, интегральная схема переключателя шины передачи данных, менеджер, мультиплексор, RS-232 трансмиттер и разъем. 1 з.п. ф-лы, 2 ил.

1. Процессорный модуль системы хранения данных, содержащий процессор, подключенный к оперативной памяти, контроллер периферийных интерфейсов, отличающийся тем, что в нем в качестве контроллера периферийных интерфейсов используется многофункциональный контроллер КПИ-2, введены процессор, многофункциональный контроллер КПИ-2, восемь разъемов для подключения модуля ОЗУ, соединитель JTAG, два порта для подключения устройств с интерфейсом SATA, RS-232 трансмиттер, порт для подключения устройств с интерфейсом UART, встроенный графический процессор, порт для подключения устройств с интерфейсом RS232, VGA, мультиплексор, шесть портов для подключения устройств с интерфейсом PCIe, две микросхемы физического уровня Gigabit Ethernet, четыре соединителя Ethernet, аппаратный модуль доверенной нагрузки, порт для подключения устройств с интерфейсом USB/Ethernet, два порта для подключения устройств с интерфейсом USB, пять разъемов для подключения устройств с интерфейсом USB, интегральная схема переключателя шины передачи данных, разъем, микросхема часов реального времени, интегральная схема переключателя шины передачи данных, менеджер, мультиплексор, RS-232 трансмиттер и разъем, двухсторонний вход-выход второго порта для подключения устройств с интерфейсом SATA соединен с вторым двухсторонним входом-выходом второго многофункционального контроллера КПИ-2, третий двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом RS-232 трансмиттера, второй двухсторонний вход-выход которого соединен с двухсторонним входом-выходом разъема, четвертый двухсторонний вход-выход второго многофункционального контроллера КПИ-2 соединен с двухсторонним входом-выходом пятого порта для подключения устройств с интерфейсом PCIe, и мультиплексора, первый выход которого соединен с входом пятого порта для подключения устройств с интерфейсом PCIe, а второй выход мультиплексора соединен с входом шестого порта для подключения устройств с интерфейсом PCIe, пятый двухсторонний вход-выход второго многофункционального контроллера КПИ-2 соединен с первым двухсторонним входом-выходом четвертого порта для подключения устройств с интерфейсом PCIe, второй двухсторонний вход-выход которого соединен с шестым двухсторонним входом-выходом второго многофункционального контроллера КПИ-2, седьмой двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом второй микросхемы физического уровня Gigabit Ethernet, второй двухсторонний вход-выход которой соединен с двухсторонним входом-выходом четвертого соединителя Ethernet, двухсторонние входы-выходы пятого, четвертого, третьего и второго разъемов для подключения устройств с интерфейсом USB соединены каждый отдельно соответственно с восьмым, девятым, десятым и одиннадцатым двухсторонними входами-выходами второго многофункционального контроллера КПИ-2, первый двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом второго процессора, вход которого соединен с выходом первого процессора, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом первого многофункционального контроллера КПИ-2, второй двухсторонний вход-выход которого соединен с двухсторонним входом-выходом первого порта для подключения устройств с интерфейсом SATA, выход порта для подключения устройств с интерфейсом UART соединен с входом RS-232 трансмиттера, первый двухсторонний вход-выход которого соединен с третьим двухсторонним входом-выходом первого многофункционального контроллера КПИ-2, четвертый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом встроенного графического процессора, второй двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом порта для подключения устройств с интерфейсом RS232, VGA, второй двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом RS-232 трансмиттера, вход второго порта для подключения устройств с интерфейсом PCIe соединен с вторым выходом мультиплексора, первый выход которого соединен с входом первого порта для подключения устройств с интерфейсом PCIe, двухсторонний вход-выход которого соединен с объединенными двухсторонним входом мультиплексора и пятым двухсторонним входом-выходом первого многофункционального контроллера КПИ-2, шестой двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом третьего порта для подключения устройств с интерфейсом PCIe, второй двухсторонний вход-выход которого соединен с седьмым двухсторонним входом-выходом первого многофункционального контроллера КПИ-2, двухсторонний вход-выход второго соединителя Ethernet соединен с третьим двухсторонним входом-выходом первой микросхемы физического уровня Gigabit Ethernet, второй двухсторонний вход-выход которой соединен с двухсторонним входом-выходом первого соединителя Ethernet, первый двухсторонний вход-выход микросхемы физического уровня Gigabit Ethernet соединен с восьмым двухсторонним входом-выходом первого многофункционального контроллера КПИ-2, двухсторонний вход-выход третьего соединителя Ethernet соединен с вторым двухсторонним входом-выходом аппаратного модуля доверенной нагрузки, первый двухсторонний вход-выход которого соединен с девятым двухсторонним входом-выходом первого многофункционального контроллера КПИ-2, десятый, одиннадцатый, двенадцатый и тринадцатый двухсторонние входы-выходы которого соединены каждый отдельно соответственно с двухсторонними входами-выходами аппаратного модуля доверенной нагрузки, порта для подключения устройств с интерфейсом USB/Ethernet, первого порта для подключения устройств с интерфейсом USB, первого разъема для подключения устройств с интерфейсом USB и второго порта для подключения устройств с интерфейсом USB, второй, третий, четвертый и пятый двухсторонние входы-выходы первого процессора соединены каждый отдельно соответственно с двухсторонними входами-выходами первого, второго, третьего и четвертого разъемов для подключения модуля ОЗУ, второй, третий, четвертый и пятый двухсторонние входы-выходы второго процессора соединены каждый отдельно соответственно с двухсторонними входами-выходами пятого, шестого, седьмого и восьмого разъемов для подключения модуля ОЗУ, выход интегральной схемы переключателя шины передачи данных соединен с входом менеджера, выход которого соединен с входом интегральной схемы переключателя шины передачи данных и вторым входом интегральной схемы переключателя шины передачи данных, двухсторонний вход-выход микросхемы часов реального времени соединен с объединенными двухсторонними входами-выходами интегральной схемы переключателя шины передачи данных, разъема и третьим двухсторонним входом-выходом интегральной схемы переключателя шины передачи данных, первый двухсторонний вход-выход которой соединен с четырнадцатым двухсторонним входом-выходом первого многофункционального контроллера КПИ-2, выход соединителя JTAG соединен с входом первого процессора, выход которого соединен с входом второго процессора, выход которого соединен с входом соединителя JTAG.

2. Процессорный модуль по п. 1, отличающийся тем, что многофункциональный контроллер периферийных интерфейсов КПИ-2 содержит контроллер физического уровня канала ввода-вывода (WLCC_PHY), контроллер канального уровня канала ввода-вывода (WLCC_DLL), коммутатор первого уровня, коммутатор второго уровня, первый составной контроллер, первый контроллер линка PCIe, второй контроллер линка PCIe, первый 4-портовый контроллер интерфейса USB, второй 4-портовый контроллер интерфейса USB, второй составной контроллер, контроллер двух устройств интерфейса IDE, третий составной контроллер, контроллер управления питанием и энергосбережением, контроллер интерфейса PCI 32, звуковой контроллер интерфейса HDA, первый 4-портовый контроллер интерфейса SATA 3.0, второй 4-портовый контроллер интерфейса SATA 3.0, первый контроллер интерфейса Ethernet, второй контроллер интерфейса Ethernet, третий контроллер интерфейса Ethernet и блок управления сигналами тактовой синхронизации, выход которого соединен с объединенными входами синхронизации всех блоков устройства, выход которого соединен с выходом контроллера физического уровня канала ввода-вывода, двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом контроллера канального уровня канала ввода-вывода, второй двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом коммутатора первого уровня, второй двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом первого составного контроллера, третий двухсторонний вход-выход коммутатора первого уровня соединен с первым двухсторонним входом-выходом первого контроллера линка PCIe, четвертый двухсторонний вход-выход коммутатора первого уровня соединен с первым двухсторонним входом-выходом второго контроллера линка PCIe, пятый двухсторонний вход-выход коммутатора первого уровня соединен с первым двухсторонним входом-выходом звукового контроллера интерфейса HDA, шестой двухсторонний вход-выход коммутатора первого уровня соединен с первым двухсторонним входом-выходом первого 4-портового контроллера интерфейса SATA 3.0, седьмой двухсторонний вход-выход коммутатора первого уровня соединен с первым двухсторонним входом-выходом второго 4-портового контроллера интерфейса SATA 3.0, восьмой двухсторонний вход-выход коммутатора первого уровня соединен с первым двухсторонним входом-выходом коммутатора второго уровня, второй двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом первого 4-портового контроллера интерфейса USB, третий двухсторонний вход-выход коммутатора второго уровня соединен с первым двухсторонним входом-выходом второго 4-портового контроллера интерфейса USB, четвертый двухсторонний вход-выход коммутатора второго уровня соединен с первым двухсторонним входом-выходом второго составного контроллера, пятый двухсторонний вход-выход коммутатора второго уровня соединен с первым двухсторонним входом-выходом первого контроллера интерфейса Ethernet, шестой двухсторонний вход-выход коммутатора второго уровня соединен с первым двухсторонним входом-выходом второго контроллера интерфейса Ethernet, седьмой двухсторонний вход-выход коммутатора второго уровня соединен с первым двухсторонним входом-выходом третьего контроллера интерфейса Ethernet, восьмой двухсторонний вход-выход коммутатора второго уровня соединен с первым двухсторонним входом-выходом контроллера двух устройств интерфейса IDE, девятый двухсторонний вход-выход коммутатора второго уровня соединен с первым двухсторонним входом-выходом третьего составного контроллера, десятый двухсторонний вход-выход коммутатора второго уровня соединен с первым двухсторонним входом-выходом контроллера управления питанием и энергосбережением, одиннадцатый двухсторонний вход-выход коммутатора второго уровня соединен с первым двухсторонним входом-выходом, контроллер интерфейса PCI, вторые двухсторонние входы-выходы контроллера двух устройств интерфейса IDE, третьего составного контроллера, контроллера управления питанием и энергосбережением, контроллера интерфейса PCI, звукового контроллера интерфейса HDA, первого контроллера интерфейса Ethernet, второго контроллера интерфейса Ethernet и третьего контроллера интерфейса Ethernet соединены с соответствующими двухсторонними входами-выходами устройства, вторые и третьи двухсторонние входы-выходы первого составного контроллера, первого контроллера линка PCIe и второго составного контроллера соединены с соответствующими двухсторонними входами-выходами устройства, с второго по пятый двухсторонние входы-выходы второго контроллера линка PCIe, первого 4-портового контроллера интерфейса USB, второго 4-портового контроллера интерфейса USB, первого 4-портового контроллера интерфейса SATA 3.0, второго 4-портового контроллера интерфейса SATA 3.0 соединены с соответствующими двухсторонними входами-выходами устройства, причем соединение между двухсторонними входами-выходами коммутатора первого уровня и контроллера канального уровня канала ввода-вывода, коммутатора второго уровня, первого составного контроллера, первого контроллера линка PCIe, второго контроллера линка PCIe, звукового контроллера интерфейса HDA, первого 4-портового контроллера интерфейса SATA 3.0, второго 4-портового контроллера интерфейса SATA 3.0 осуществляется интерфейсом типа «Slink», причем соединение между двухсторонними входами-выходами коммутатора второго уровня и первого 4-портового контроллера интерфейса USB, второго 4-портового контроллера интерфейса USB, второго составного контроллера, контроллера двух устройств интерфейса IDE, третьего составного контроллера, контроллера управления питанием и энергосбережением, контроллера интерфейса PCI, первого контроллера интерфейса Ethernet, второго контроллера интерфейса Ethernet и третьего контроллера интерфейса Ethernet осуществляется интерфейсом типа «IOlink».

| 0 |

|

SU151425A1 | |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПРОВОЛОЧНОЙ БИСПИРАЛИ»сгсоис;мяП '. T.''UTLJgТс;:::;;чЕскдя 1Б;;5Л';ОТЕКА * | 0 |

|

SU173335A1 |

| СПОСОБ ПОЛУЧЕНИЯ АКТИВИРОВАННОГО УГЛЯ | 0 |

|

SU175051A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| EP 3121718 A1, 25.01.2017. | |||

Авторы

Даты

2019-02-26—Публикация

2018-04-24—Подача