Предлагаемые способ и устройство обработки служебно-технологических команд (СТК) объединены единым изобретательским замыслом и относятся к области радиотехники, а именно, к области передачи и приема служебно-технологических команд, сформированных на базе рекуррентных последовательностей и могут быть использованы в инфокоммуникационных системах для обработки служебно-технологических команд (при малом отношении сигнал/шум на входе приемника) в условиях воздействия преднамеренных помех.

Под формированием служебно-технологических команд понимается процесс формирования сигналов управления по распределению информационных потоков, адресованию, маршрутизации, режимов и сигналов синхронизации, а также других вспомогательных сигналов, предоставляемых пользователям инфокоммуникационных систем.

Известны способы обработки служебно-технологических команд, в частности способ синхронизации нелинейных рекуррентных последовательностей, описанные, например: в статье Уорд Р. "Различение псевдошумовых сигналов методом последовательной оценки". - Зарубежная радиоэлектроника, 1966, №8, с. 20-37, как способ RASE (Rapid Acqusition by Sequental Esti-mation) быстрого распознавания путем последовательной оценки; в книге В.И. Журавлев "Поиск и синхронизация в широкополосных системах" - М.: Радио и связь. 1986, с. 86-102, как способы последовательной оценки символов нелинейной рекуррентной последовательности с одной ступенью проверки на с. 86, последовательной оценки с двумя ступенями проверки с. 92, а также модифицированные способы последовательной оценки, описанные в указанной выше книге, такие как способ последовательной оценки символов и формирование метрик ненадежности с. 95, (а.с. 315298) и способ последовательной мажоритарной оценки символов нелинейных рекуррентных последовательностей с. 97.

Каждый из перечисленных способов обработки служебно-технологических команд, в частности способ синхронизации заключается в разделении принятого информационного сигнала на две ветви обработки, временной задержке информационного сигнала в первой ветви, формировании оценочного сигнала и его задерживании во второй ветви, вычислении коэффициента корреляции между задержанной частью информационного сигнала первой ветви и оценочным значением информационного сигнала во второй ветви, формировании управляющего сигнала и генерировании нелинейной последовательности, синхронной с принимаемой последовательностью.

Недостатками перечисленных способов обработки служебно-технологических команд, в частности способа синхронизации являются относительно высокое время обработки сигналов синхронизации, что обусловлено предварительным квантованием принимаемого сигнала на два или более уровней и проведением оценки сигнала в дискретном виде, приводящим к потере некоторой части информации; необоснованным отказом от учета рекуррентных свойств нелинейной рекуррентной последовательности по предсказанию очередного элемента на основе ранее принятых элементов и использованием задержки сигнала, приводящего к увеличению времени вхождения в синхронизм.

Наиболее близким по своей сущности к заявленному способу обработки служебно-технологических команд, является известный способ синхронизации (патент RU №2153230). Способ-прототип синхронизации М-последовательности с повышенной сложностью заключается в приеме псевдослучайной рекуррентной последовательности, дискретизации, задержке, формировании опорной кодовой последовательности в аналоговом виде, считывании аналоговых значений, квантовании, задержке, корректировке считанных аналоговых значений, задержке откорректированных аналоговых значений, повторной корректировке аналоговых значений, квантовании, запоминании, повторном формировании опорной кодовой последовательности, формировании управляющего воздействия и генерировании псевдослучайной рекуррентной последовательности, синхронной с принимаемой.

Недостатком способа-прототипа является относительно высокое время обработки сигналов синхронизации и низкая помехозащищенность в условиях воздействия преднамеренных помех, что обусловлено детерминированностью структуры используемых М-последовательностей, не обеспечивающих высокую структурную скрытность синхропоследовательностей и помехозащищенность в условиях воздействия преднамеренных помех; формированием оценочных значений элементов сигнала с использованием предсказанных значений, которые на начальном этапе вхождения в синхронизм могут быть ошибочными, что может привести к формированию ошибочных оценочных значений и увеличению времени синхронизации, а также не позволяет функционировать в автоматизированном режиме.

Известны устройства, реализующие рассмотренные выше способы синхронизации псевдослучайной рекуррентной последовательности, описанные, например: в статье Уорд Р. "Различение псевдошумовых сигналов методом последовательной оценки". - Зарубежная радиоэлектроника, 1966, №8, с. 23, рис. 2; в книге В.И. Журавлев "Поиск и синхронизация в широкополосных системах" - М: Радио и связь. 1986, с. 86-102., где устройство, реализующее способ последовательной оценки с одной ступенью проверки изображено на рис. 3.1, а устройство, реализующее способ последовательной оценки с двумя ступенями проверки изображено на с. 98; а.с. 1626426, реализующее модификацию способа последовательной мажоритарной оценки символов псевдослучайной рекуррентной последовательности как устройство поиска псевдошумового сигнала по задержке.

Каждое из перечисленных устройств включает блок формирования оценочного сигнала, каскадно-соединенные по информационным входам линию задержки, коррелятор и устройство управления, выход которого подключен к первому управляющему входу регистра сдвига с обратными связями, выход которого является выходом устройства синхронизации.

Недостатками перечисленных устройств синхронизации являются относительно высокое время обработки сигналов синхронизации, что обусловлено предварительным квантованием принимаемого сигнала на два или более уровней и проведением оценки сигнала в дискретном виде, приводящих к потере некоторой части информации, необоснованным отказом от учета рекуррентных свойств псевдослучайной последовательности по предсказанию очередного символа на основе ранее принятых сигналов и использованием задержки сигнала, приводящих к увеличению времени вхождения в синхронизм.

Наиболее близким по своей сущности к заявленному и принятое в качестве прототипа устройству обработки служебно-технологических команд в инфокоммуникационных системах является устройство синхронизации по патенту RU №2320080. Рассматриваемое устройство-прототип включает дискретизатор, выделитель тактовой частоты, корректор, блок формирования уточненных предсказанных значений, первый коммутатор, второй коммутатор, блок аналоговых линий задержек, блок квантователей, блок цифровых линий задержек, блок управления, генератор опорных кодовых последовательностей, генератор опорного сигнала, цифровой нелинейный узел усложнения.

Недостатком устройства прототипа синхронизации псевдослучайных последовательностей является относительно высокое время обработки сигналов синхронизации, то есть обработки служебно-технологических команд в инфокоммуникационных системах и низкая помехозащищенность в условиях воздействия преднамеренных помех. Это обусловлено тем, что в устройстве оценочные значения элементов принятого сигнала формируются с использованием предсказанных значений, которые на начальном этапе вхождения в синхронизм могут быть ошибочными, а также не производится сравнение значений элементов сигнала в первой ветви обработки квантованных значений со значениями элементов сигнала после дискретно-аналоговой обработки и корректировки и квантования во второй ветви, что может привести к формированию ошибочных оценочных значений и увеличению времени синхронизации.

Технической задачей, на решение которой направлено изобретение является разработка способа безопасной обработки служебно-технологических команд в инфокоммуникационных системах и устройства его реализующего, обеспечивающего скрытность процесса передачи и приема служебно-технологических команд, уменьшение времени обработки за счет повышения точности оценки единичного элемента принятой последовательности в условиях воздействия преднамеренных помех.

Поставленная задача решается следующим образом. В заявленном способе безопасной обработки служебно-технологических команд в инфокоммуникационных системах, заключающемся в передаче служебно-технологических команд, сформированных на основе нелинейных рекуррентных последовательностей, приеме псевдослучайной последовательности и разделении принятой последовательности на две ветви обработки: в первой из которых происходит квантование элементов принятой последовательности, а во второй - дискретизация, задержка, формирование опорной кодовой последовательности в аналоговом виде, считывание аналоговых значений, квантование, задержка, корректировка считанных аналоговых значений, задержка откорректированных аналоговых значений, повторная корректировка аналоговых значений, квантование, запоминание, повторное формирование опорной кодовой последовательности, формирование управляющего воздействия при сравнении опорной кодовой последовательности с откорректированной на продолжительности 2n-m тактов обработки и генерирование псевдослучайной последовательности, синхронной с принимаемой, поразрядное сравнение значений элементов последовательности полученной в первой ветви обработки со значениями элементов последовательности, полученной во второй ветви обработки на продолжительности m-тактов, формирование управляющего воздействия по результатам сравнения на продолжительности m-тактов и разрешении считывания служебно-технологических команд с выхода устройства служебно-технологических команд, сформированных на основе нелинейных рекуррентных последовательностей.

Указанная новая совокупность выполняемых действий заявленного способа безопасной обработки служебно-технологических команд в инфокоммуникационных системах, сформированных на основе нелинейных рекуррентных последовательностей, корректировки с учетом уточненных предсказанных значений на приеме и сравнении значений элементов сигнала после квантования со значениями после корректировки обеспечивает скрытность процесса передачи служебно-технологических команд, уменьшение времени обработки служебно-технологических команд в условиях воздействия преднамеренных помех за счет улучшения точности оценки единичного элемента принятой последовательности.

Для решения поставленной задачи в заявленном устройстве, содержащем дискретизатор, выделитель тактовой частоты, корректор, блок формирования уточненных предсказанных значений, первый коммутатор, второй коммутатор, блок аналоговых линий задержек, блок квантователей, блок цифровых линий задержек, блок управления, генератор опорных кодовых последовательностей, генератор опорного сигнала, цифровой нелинейный узел усложнения, дополнительно введены второй блок квантователей, блок поэлементного сравнения и вычислительный блок. Первый вход второго блока квантователей в параллель соединен с первым входом дискретизатора и первым входом выделителя тактовой частоты. Второй вход второго блока квантователей в параллель соединен с третьим входом блока поэлементного сравнения, четвертым входом генератора опорных кодовых последовательностей, первым входом вычислительного блока, первым входом генератора опорного сигнала, седьмым входом блока формирования уточненных предсказанных значений, четвертым входом первого коммутатора и вторым выходом умножителя тактовой частоты. Выход второго блока квантователей соединен с первым входом блока поэлементного сравнения. Второй вход блока поэлементного сравнения соединен с выходом цифрового нелинейного узла усложнения. Третий вход блок обработки поэлементного сравнения в параллель соединен со вторым входом второго блока квантователей, четвертым входом генератора опорных кодовых последовательностей, первым входом вычислительного блока, первым входом генератором опорного сигнала, седьмым входом блока формирования уточненных предсказанных значений, четвертым входом первого коммутатора и вторым выходом выделителя тактовой частоты. Выход блока поэлементного сравнения соединен с пятым входом вычислительного блока. Первый вход вычислительного блока в параллель соединен со вторым входом второго блока квантователей, с третьим входом блока поэлементного сравнения, четвертым входом генератора опорных кодовых последовательностей, первым входом генератором опорного сигнала, седьмым входом блока формирования уточненных предсказанных значений, четвертым входом первого коммутатора и вторым выходом выделителя тактовой частоты. Второй вход вычислительного блока в параллель соединен с первым выходом второго коммутатора, вторым входом генератора опорного сигнала, первым входом цифрового нелинейного узла усложнения. Третий вычислительного блока в параллель соединен со вторым выходом второго коммутатора, третьим входом генератора опорного сигнала, вторым входом цифрового нелинейного узла усложнения. Четвертый вход вычислительного блока и в параллель соединен с третьим выходом второго коммутатора, четвертым входом генератора опорного сигнала, третьим входом цифрового нелинейного узла усложнения. Выход вычислительного блока является выходом устройства.

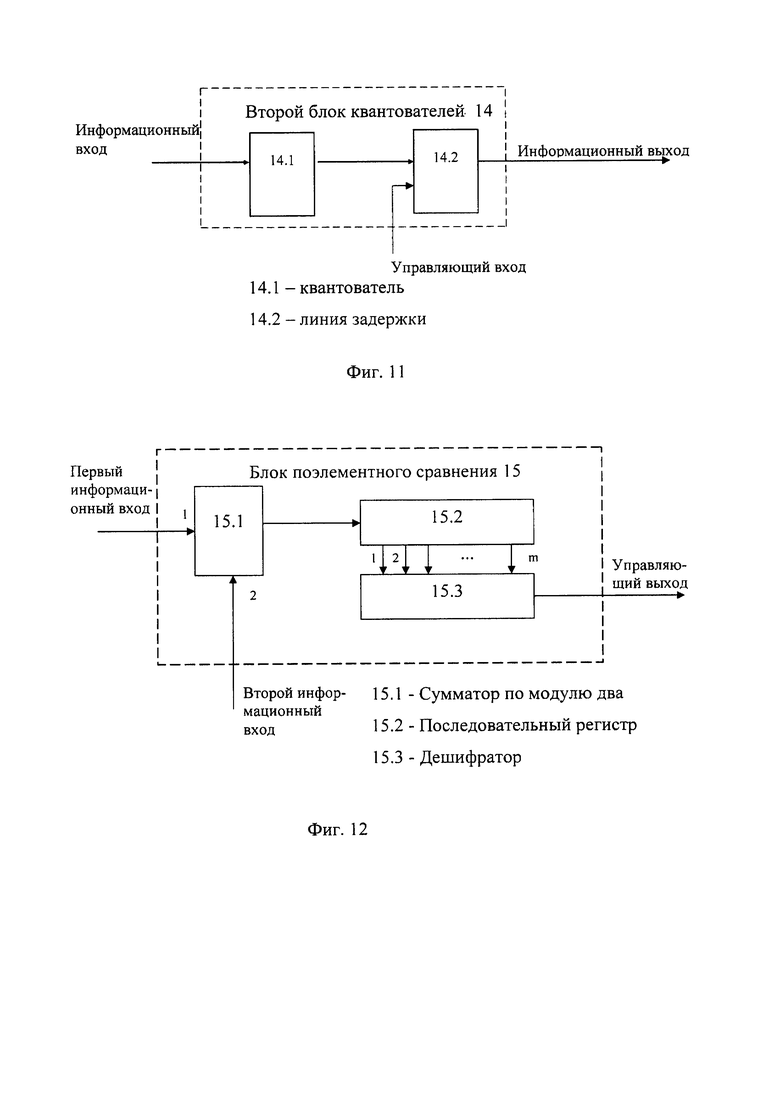

Второй блок квантователей состоит из одного квантователя сигнала по уровню 0 или 1 и линии задержки. Информационный вход второго блока квантователей подключен к входу квантователя, выход квантователя подключен к первому входу линии задержки, управляющий вход второго блока квантователей подключен ко второму входу линии задержки, выход линии задержки подключен к информационному выходу второго блока квантователей. Информационный вход второго блока квантователей является первым входом блока квантователей, управляющий вход второго блока квантователей является входом второго блока квантователей, информационный выход второго блока квантователей является выходом второго блока квантователей. Кроме того, квантователь дополнительно снабжен входом опорного напряжения. По своей физической сути квантователь является компаратором, реагирующим на разность двух сигналов, один из которых опорный. Схемы компараторов, которые могут быть использованы во втором блоке квантователей известны (М.У. Банк "Аналоговые интегральные схемы в радиоаппаратуре". - М.: Радио и связь. 1981, стр. 26, рис. 2.19(a)).

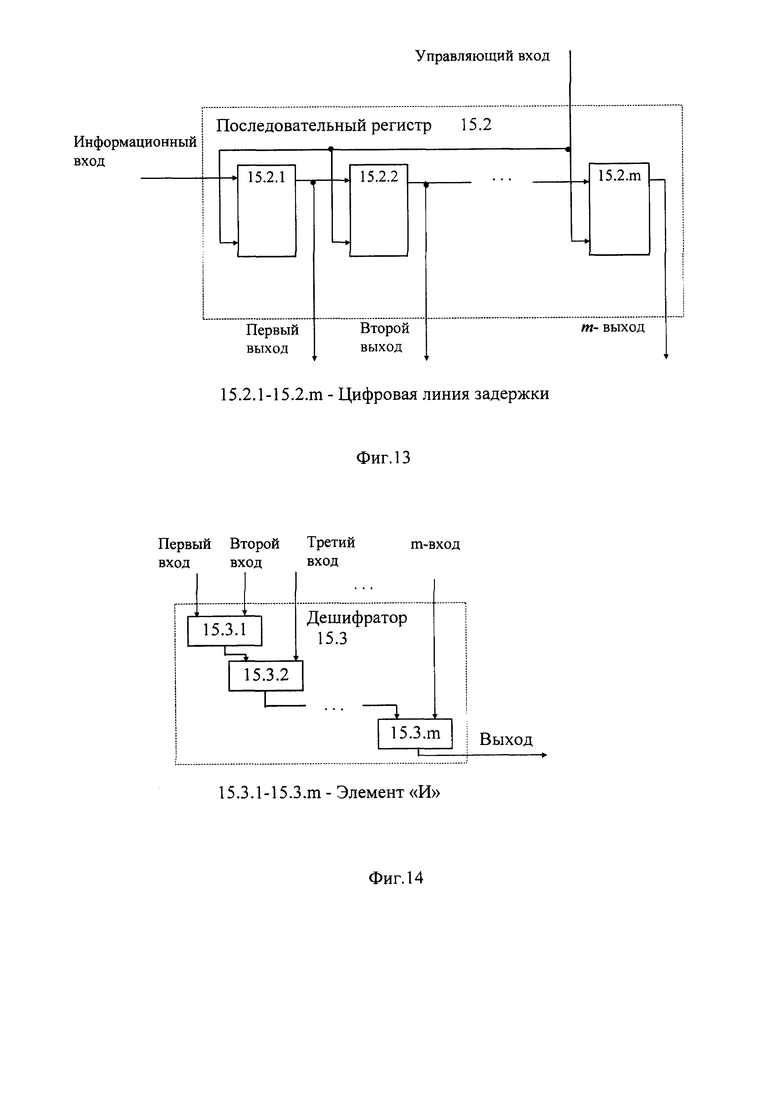

Блок поэлементного сравнения состоит из сумматора по модулю два, последовательного регистра и дешифратора. Первый вход блока поэлементного сравнения является первым входом сумматора по модулю два. Второй вход блока поэлементного сравнения является вторым входом сумматора по модулю два, выход которого является первым входом последовательного регистра. Третий вход блока поэлементного сравнения является вторым входом последовательного регистра. Выходы последовательного регистра от первого до m-го соединены с соответствующими входами дешифратора. Выход дешифратора является управляющим выходом блока поэлементного сравнения.

Вычислительный блок состоит из выключателя разрешения и параддельного регистра. Первый вход вычислительный блока является первым управляющим входом выключателя разрешения, выход которого в параллель соединен с первыми входами первого, второго и третьего элементов регистра. Второй вход вычислительный блока является первым информационным входом регистра и вторым входом первого элемента регистра. Третий вход вычислительный блока является вторым информационным входом регистра и вторым входом второго элемента регистра. Третий вход вычислительного блока является третьим информационным входом регистра и вторым входом третьего элемента регистра, выход которого является выходом параллельного регистра и выходом вычислительный блока. Пятый вход вычислительный блока является управляющим входом выключателя разрешения. Выход вычислительный блока является выходом устройства безопасной обработки служебно-технологических команд.

Благодаря новой совокупности существенных признаков за счет введения второго блока квантователей, блока поэлементного сравнения, вычислительного блока, получение значений сигнала с учетом сравнения значений сигнала, полученных после первого квантования при приеме сигнала в первой ветви обработки и откорректированных значений во второй ветви, не прекращается и производится непрерывно с целью получения более точных значений сигнала, что приводит к сокращению времени при повторном вхождении в связь и приеме последовательности служебно-технологических команд. Таким образом, в рассмотренном устройстве реализуются все процедуры способа безопасной обработки служебно-технологических команд, являющиеся его особенностями и одновременно его достоинствами.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленных технических решений, отсутствуют, что указывает на соответствие заявленных способа и устройства условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными признаками прототипа заявленных объектов, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленных изобретений преобразований на достижение указанного технического результата. Следовательно, заявленные изобретения соответствуют условию патентоспособности "изобретательский уровень".

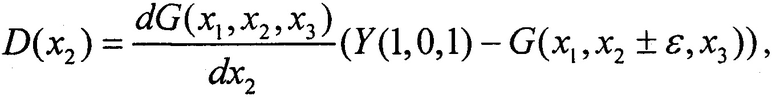

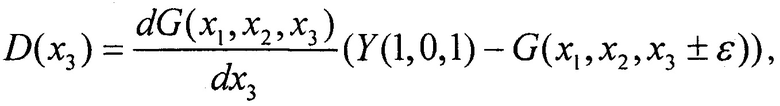

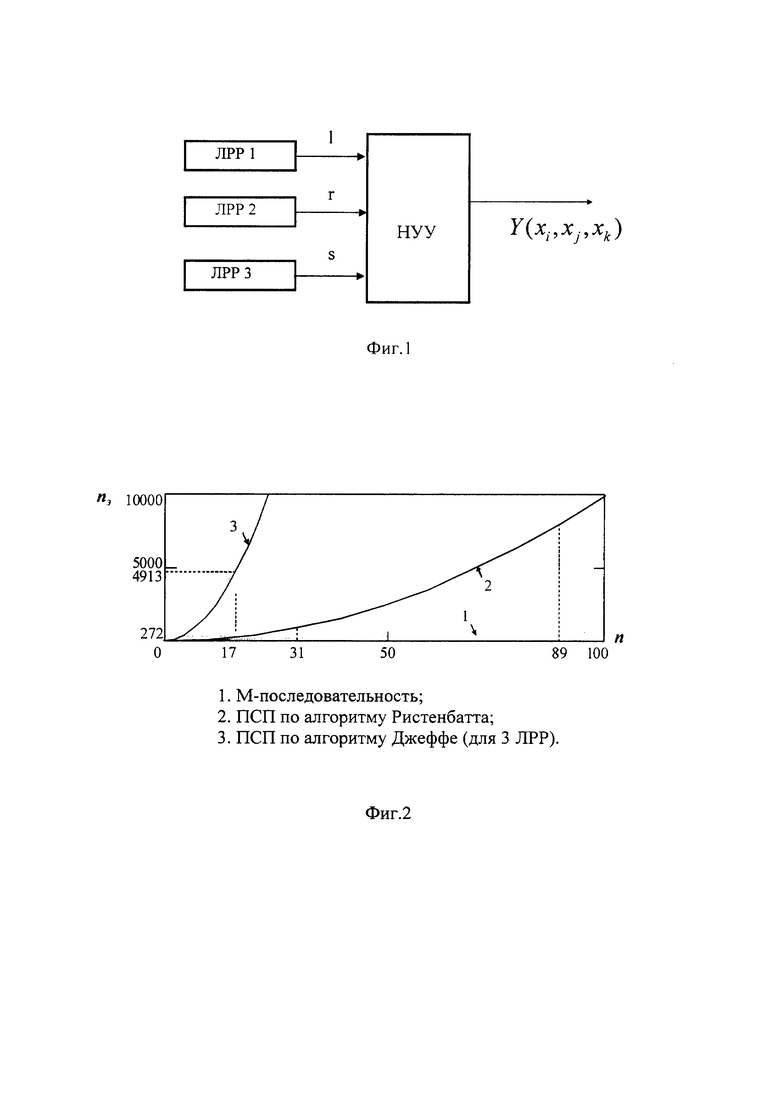

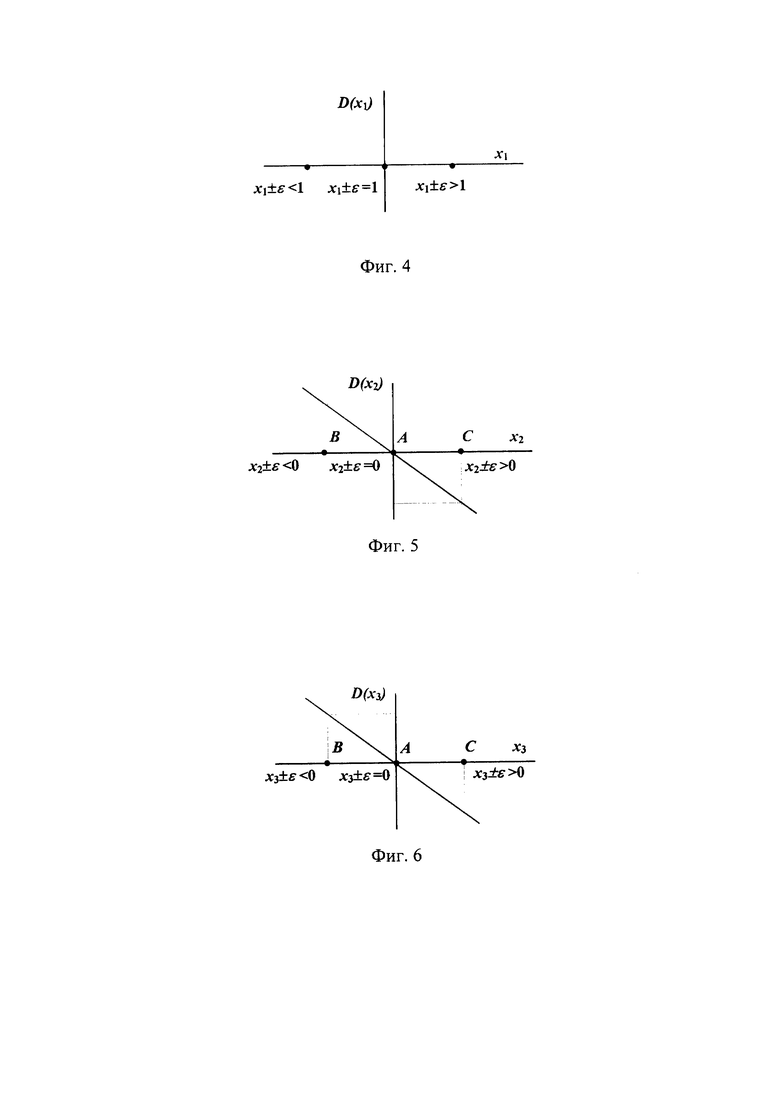

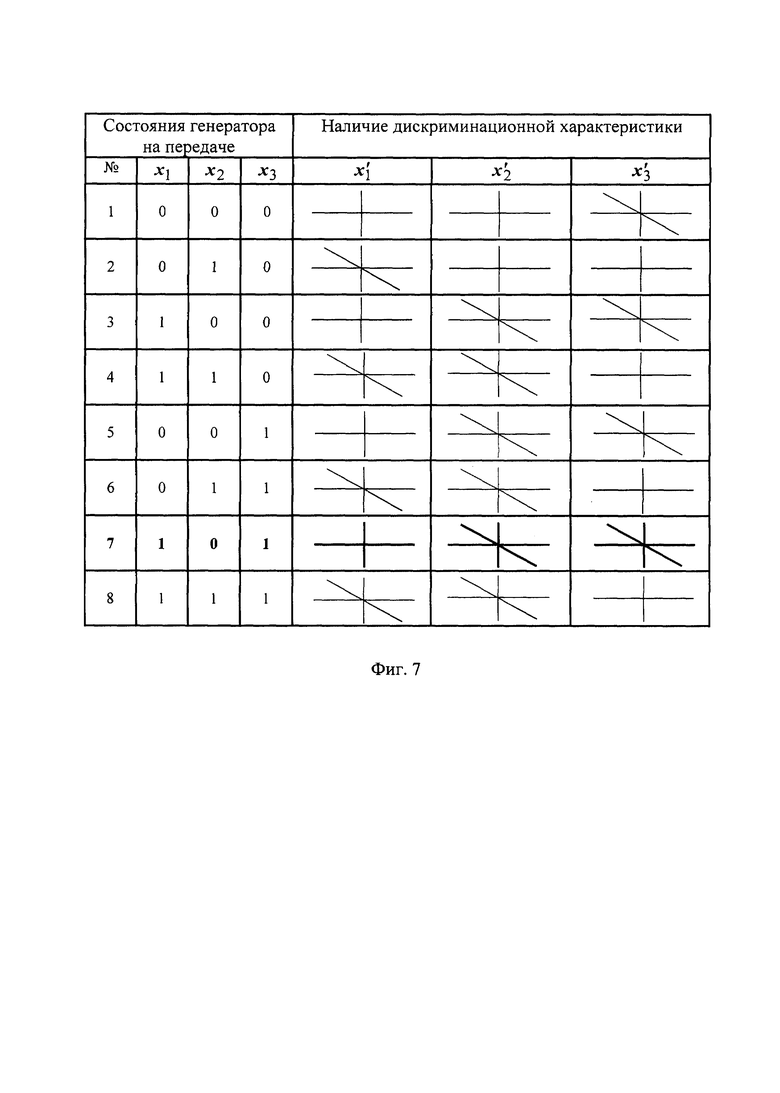

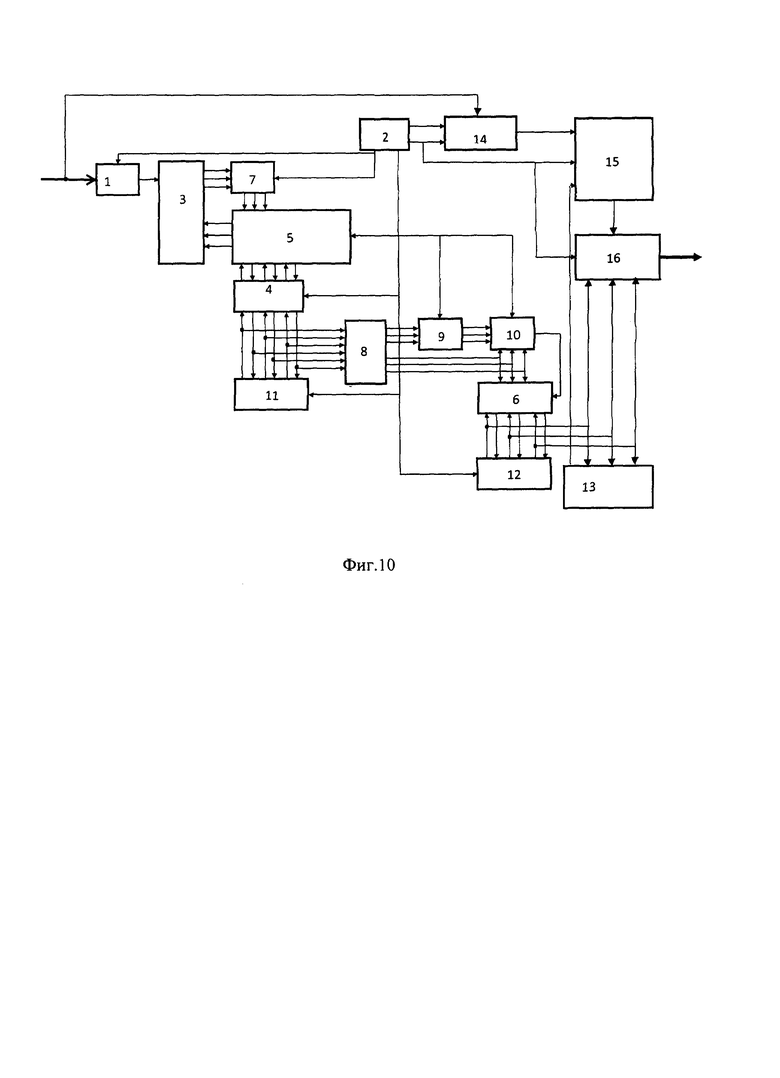

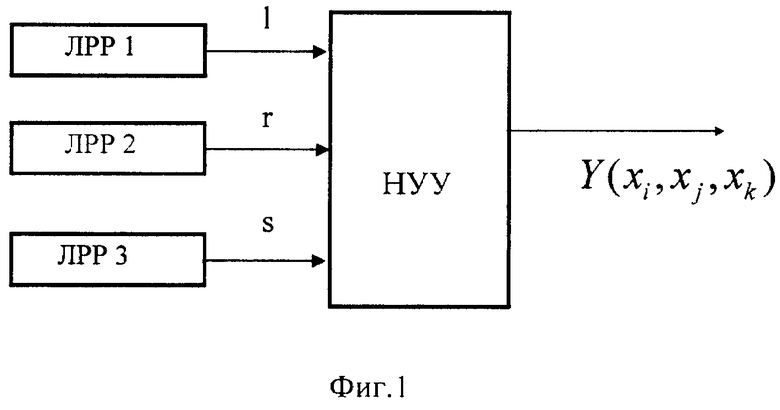

Заявленные объекты изобретения поясняются чертежами и схемами: Фиг. 1 - Структурная схема генератора формирования псевдослучайных последовательностей по алгоритму Джеффе; Фиг. 2 - График сравнения эквивалентной линейной сложности М-последовательностей, последовательностей сформированных по алгоритму Ристенбатта и последовательностей сформированных по алгоритму Джеффе; Фиг. 3 - Графики, поясняющие сущность способа безопасной обработки служебно-технологических команд; Фиг. 4 - Вид дискриминационной характеристики в случае отсутствия корректирующего значения; Фиг. 5 - Вид дискриминационной характеристики в случае формирования корректирующего значения; Фиг. 6 - Вид дискриминационной характеристики в случае формирования корректирующего значения; Фиг. 7 - Таблица состояний генератора передачи при осуществлении корректировки заданных значений; Фиг. 8 - Графики зависимости количества ошибочных значений генераторов на передаче и приеме от количества тактов обработки в случае: 1 - Реализации способа синхронизации, представленного в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью"; 2 - Заявленного способа безопасной обработки служебно-технологических команд; Фиг. 9 - Графики, представляющие результаты моделирования способа безопасной обработки служебно-технологических команд; Фиг. 10 - Структурная схема устройства безопасной обработки служебно-технологических команд. Где 1 - дискретизатор; 2 - умножитель тактовой частоты; 3 - корректор; 4 - блок усреднения; 5 - первый коммутатор; 6 - второй коммутатор; 7 - блок аналоговых линий задержек; 8 - первый блок квантователей; 9 - блок цифровых линий задержек; 10 - блок управления; 11 - аналоговый линейный рекуррентный регистр; 12 - цифровой линейный рекуррентный регистр; 13 - цифровой нелинейный узел усложнения; 14 - второй блок квантователей; 15 - блок поэлементного сравнения; 16 - вычислительный блок; Фиг. 11- Второй блок квантователей, где 14.1 - квантователь, 14.2 - линия задержки; Фиг. 12 - Блок обработки сигналов, где 15.1 - сумматор по модулю два, 15.2 - последовательный регистр, 15.3 - дешифратор; Фиг. 13 - Последовательный регистр, где 15.2.1-15.2.m - цифровая линия задержки; Фиг. 14 - Дешифратор, где 15.3.1-15.3.m - элемент «И»; Фиг. 15 - Блок оценочных значений, где 16.1 - линия задержки, 16.2.1-16.2.3 - элементы параллельного регистра.

Реализация заявленного способа безопасной обработки служебно-технологических команд заключается в следующем. Рассмотрим структуру генератора формирования последовательности, представленную в описании к патенту на изобретение №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью". Генератор сформирован на основе линейного рекуррентного регистра (ЛРР), формирующего М-последовательность, и усложнен внешней нелинейной логикой в виде нелинейного узла усложнения (НУУ). Период такой последовательности равен:

L=2n-1,

где n - порядок порождающего полинома. Эквивалентная линейная сложность псевдослучайной последовательности также равна n. Известно, что структуру любой псевдослучайной последовательности легко вскрыть, перехватив более 2n смежных элементов по криптоалгоритму Берликэмпа-Месси. Это приводит к необходимости использования последовательностей большей структурной сложности, период которых не повторяется на сеансе связи. Это могут быть псевдослучайные последовательности повышенной сложности, нелинейные рекуррентные последовательности, квадратичные и многие другие.

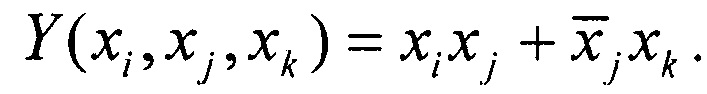

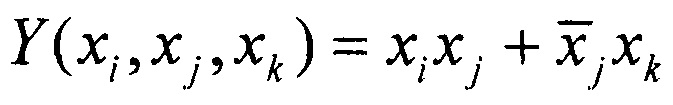

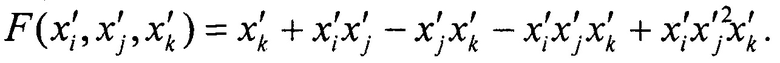

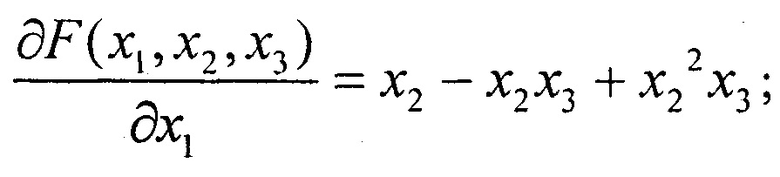

Линейный рекуррентный регистр представляет собой цифровой регистр сдвига с обратными связями. Такие регистры оперируют нулями и единицами, а в качестве преобразователя сигнала в регистре сдвига с обратными связями используют сумматоры по модулю 2. В качестве нелинейных узлов усложнения целесообразно применять те из них, которые не ухудшают баланс выходной последовательности, например, узел, реализующий нелинейную функцию преобразования:

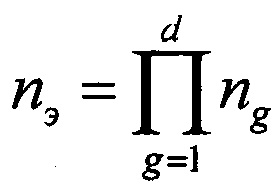

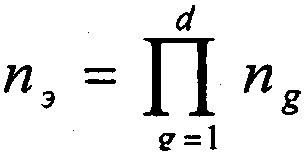

Структурная схема генератора формирующего такие последовательности представлена на Фиг. 1. Применение такого генератора позволяет формировать последовательности Джеффе с эквивалентной линейной сложностью (ЭЛС), определяемой по формуле:

где ng - длина g - го регистра, d - количество ЛРР, используемых в схеме генератора. Графики сравнения ЭЛС различных последовательностей представлены на фиг. 2. Исследования проводились для трех случаев формирования ПСП, при длинах регистров равных 17, 31, 89. Для ЛРР длиной 17 ЭЛС принимает значения 17, 272, 289, для ЛРР длиной 31 соответственно 31, 930, 961, для ЛРР длиной 89 соответственно 89, 7832, 7921. Для М-последовательностей ЭЛС nэ-n, для последовательностей Ристенбатта nэ=n(n-1) для последовательностей Джеффе -

Однако, по принятому из канала связи элементу сигнала Y(xi, xj, xk) невозможно однозначно сказать, какие элементы xi, xj, xk участвовали в его формировании. С этой целью применяют дискретно-аналоговое преобразование. Сущность способа дискретно-аналогового преобразования состоит в замене элементарных логических операций соответствующими аналоговыми.

Рассмотрим функции алгебры логики. Среди булевых функций отметим, например, элементарные булевы функции, которые тесно связаны с основными логическими операциями, это одноместные булевы функции - повторение и отрицание, двухместные - конъюнкция, дизъюнкция, отрицание конъюнкции, отрицание дизъюнкции, импликация, "запрет", "эквивалентность", "сложение по модулю 2". Рассмотрим элементарные логические и аналоговые функции. Отметим, что на основе представленных элементарных функций, реализуются различные нелинейные функции преобразования как дискретных, так и аналоговых значений см. табл. 1. Наиболее полно такое преобразование представленное в описании к патенту RU №2320080 "Способ и устройство синхронизации псевдослучайных последовательностей".

В соответствии с предложенным способом, логическую функцию

можно записать в аналоговом виде

В этом случае таблицы истинности дискретных и аналоговых значений совпадают.

Вместе с тем, во избежание декодирования последовательности по алгоритму Берликемпа-Месси возникает необходимость обработки служебно-технологических команд и синхронизации таких последовательностей за время длительности не более 2n смежных элементов. Эта проблема решается на основе способа безопасной обработки служебно-технологических команд, предложенного авторами изобретений, и обеспечивающем уменьшение времени обработки служебно-технологических команд за счет улучшения точности оценки единичного элемента псевдослучайной последовательности в сравнении с алгоритмом, представленным в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Псевдослучайная последовательность (ПСП) формируется на передающей стороне генератором, структура которого представлена на Фиг. 1. В процессе передачи сигналы искажаются под воздействием шумов и помех. Принимаемый сигнал представляет собой смесь сигнала, шумов и помех. Принятый сигнал обрабатывается в первой ветви обработки, где он квантуется и сравнивается путем сравнения поразрядно по модулю два со значениями, полученными во второй ветви обработки. При совпадении m-количество раз элементов сигнала поразрядно полученных в первой и второй ветви обработки прием служебно-технологических команд считается правильным.

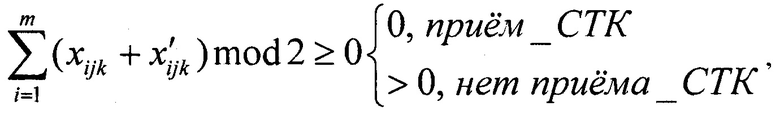

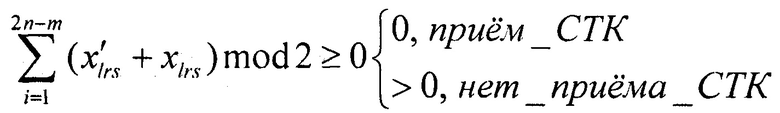

Условия правильного приема служебно-технологических команд принимается по правилу:

где m - количество поразрядных совпадений элементов последовательности полученных в первой и второй ветви обработки; xjjk - элементы последовательности полученных в первой;  - во второй ветви обработки.

- во второй ветви обработки.

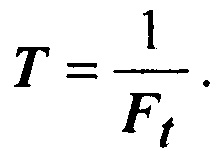

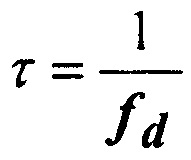

Во второй ветви обработки (фиг. 3в) из принимаемой смеси с помощью известных способов выделяют тактовую частоту Ft. Известные способы выделения тактовой частоты описаны, например, в книге: Е.М. Мартынов "Синхронизация в системах передачи дискретных сообщений". - М.: Связь. 1972, стр. 107. Период следования импульсов с тактовой частотой равен

Используя известные способы деления частоты, получают частоту в k раз превышающую тактовую ƒd=kFt, где k - количество дискретизированных отсчетов на длительности одного информационного элемента сигнала. Значение k целесообразно выбирать в пределах от 2 до 10 (фиг. 3г). Известные способы деления частоты описаны, например, в книге: М.Л. Лейнов, B.C. Качалуба, А.В. Рыжков "Цифровые делители частоты на логических элементах". - М.: Энергия. 1975, стр. 93. Период следования импульсов с частотой в k раз превышающей тактовую равен:

С целью избежания внесения дополнительных искажений, принимаемый сигнал на входе демодулятора не квантуют на два уровня, а дискретизируют с частотой ƒd (фиг. 3д). Известные способы дискретизации сигналов описаны, например, в книге: Ж. Маркюс "Дискретизация и квантование". - М.: Энергия. 1969, стр. 45. После дискретизации каждый дискретизированный отсчет (ДО) поступает на информационный вход корректора, где вырабатываются корректирующие сигналы для каждого значения заданного элемента опорной кодовой последовательности, где под заданными значениями элементов опорной кодовой последовательности (ОКП) будем понимать аналоговые значения, хранящиеся в ячейках ЛРР, к которым подключены отводы нелинейного узла усложнения (НУУ).

Возможность осуществления корректировки значений заданных элементов ОКП, хранящихся в ячейках ЛРР в аналоговом виде, по принимаемому дискретизированному отсчету псевдослучайной последовательности повышенной сложности (ПСП ПС) рассмотрена на примере, представленном в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

С целью наиболее точной корректировки искаженного информационного сигнала различают обработку при смене тактовых интервалов информационного сигнала и внутри тактовых интервалов информационного сигнала.

В моменты смены тактовых интервалов на 1-м ДО из значений ОКП формируют откорректированные значения с учетом уточненных предсказанных значений, сформированных по рекуррентному правилу формирования опорной кодовой последовательности, просуммированных на длительности n - элементов последовательности и деленных на n. Для формирования откорректированных значений используют значение сигнала, принятого из канала связи, уточненное предсказанное значение, значение функции нелинейного преобразования от значений заданных элементов ОКП и производные функции нелинейного преобразования от значений заданных элементов ОКП. С этой целью из 1-го ДО принимаемой ПСП вычитают значение функции нелинейного преобразования от значений заданных элементов ОКП и умножают на заданный весовой коэффициент К2. По физической сущности умножению сигнала на постоянный множитель соответствует усиление сигнала. Известные способы усиления сигналов описаны, например, в книге: А.А. Сикарев, О.Н. Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". - М.: Радио и связь. 1983, стр. 184. Коэффициент К2 определяет превышение значения амплитуды корректирующего сигнала от значения опорного напряжения равного 0.5 в интервале от 0 до 1. Значение коэффициента К2 обязательно дробное в указанном интервале. В этом случае справедливы аналоговые выражения, используемые для замены соответствующих им дискретных.

При этом в качестве значений заданных элементов ОКП для первоначального установления синхронизации могут быть использованы произвольные ненулевые значения элементов ОКП в области определения 0 до 1 или значения, оставшиеся от прошлого сеанса связи. После этого осуществляется корректировка значений заданных элементов ОКП. В каждой ветви корректировки сигнал умножают на значения соответствующих производных аналоговой функции нелинейного преобразования от значений заданных элементов ОКП умножают на коэффициент К1 и суммируют с соответствующими уточненными предсказанными значениями заданных элементов ОКП. Значение коэффициента K1 обязательно дробное и может принимать значения от 0 до 1. Известные способы сложения сигналов описаны, например, в книге: А.А. Сикарев, О.Н. Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". - М.: Радио и связь. 1983, стр. 194.

Корректировка осуществляется одновременно трех заданных значений, участвовавших в формировании выходного элемента ПСП. В каждой ветви корректировки из принятого значения элемента сигнала вычитают значение сигнала, сформированное на приеме, и умножают на значения соответствующих частных производных. Далее суммируют с соответствующими начальными значениями заданных элементов опорной последовательности (ОП). После этого откорректированные значения заданных элементов ОП, полученные на первом ДО, задерживают на время τ, равное длительности одного ДО. Далее осуществляется корректировка заданных значений элементов последовательности на последующих, вплоть до k-го ДО. Откорректированное значение на k-м т.е последнем ДО принимают за откорректированное значение элемента в целом (ТИ) и используют в качестве ОКП для корректировки последующего элемента ПСП в последующем тактовом интервале. Для оценки следующего элемента сигнала все описанные выше операции повторяются. Аналогично первой ветви осуществляется корректировка во второй и третьей ветвях обработки (Фиг. 3ж). После корректировки производится квантование сигнала (Фиг. 3з). Таким образом, формируется последовательность, синхронная с передаваемой. Кроме того, получение откорректированных значений сигнала, с учетом принимаемых предсказанных не прекращается и производится непрерывно с целью получения ОКП сигнала для сокращения времени при повторном приеме и обработке.

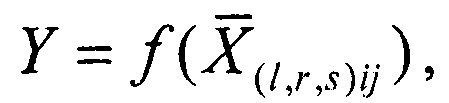

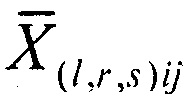

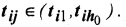

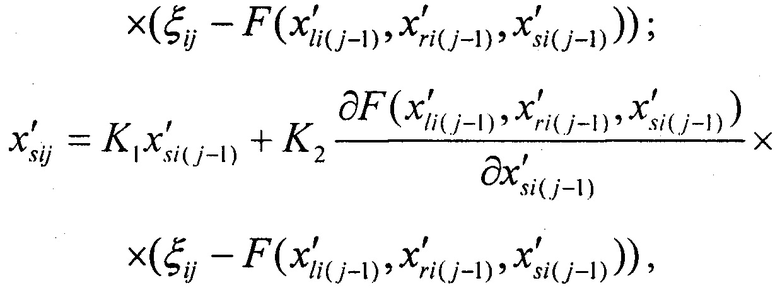

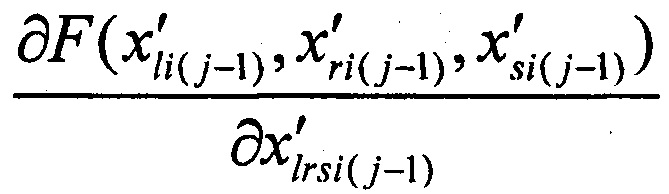

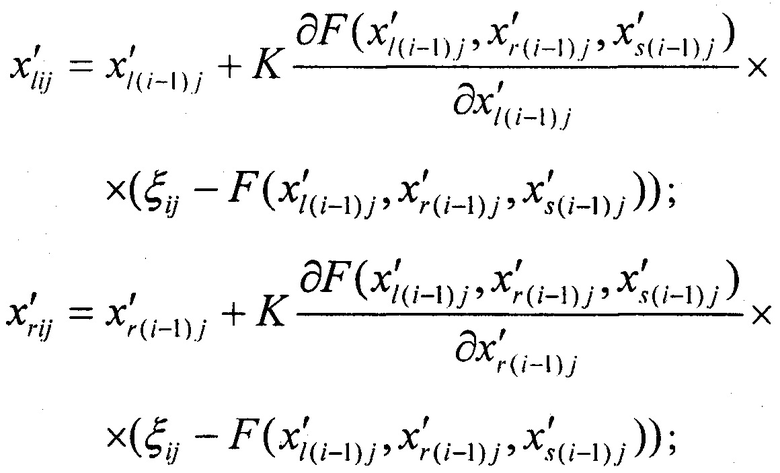

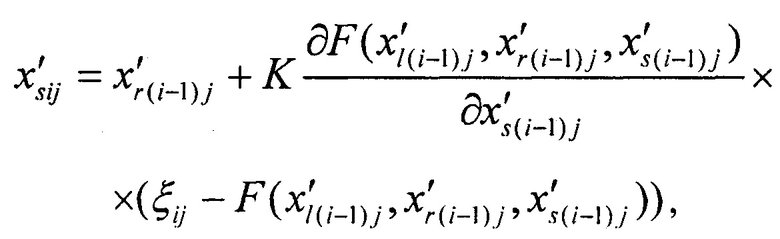

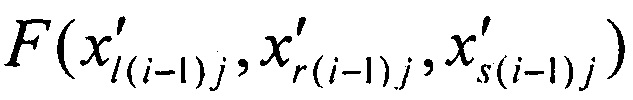

В аналитической форме данные действия можно записать следующим образом:

где  - вектор, составленный из компонентов с номерами

- вектор, составленный из компонентов с номерами  ,r, s в моменты времени i, j.

,r, s в моменты времени i, j.

Выходной элемент формируется в соответствии с функцией нелинейного преобразования трех значений ЛРР (х1, x2, х3), поступающих с выводов генератора формирующего последовательность ( , r, s).

, r, s).

Используя предложенный алгоритм получим уравнения вектора состояния для моментов времени tij, лежащих внутри тактовых интервалов (ТИ) т.е уравнения дискретизированных отсчетов (ДО), то есть для  Уравнения оценивания будут определяться соотношениями

Уравнения оценивания будут определяться соотношениями

где  - аналоговые начальные условия для оценки внутри ТИ первого

- аналоговые начальные условия для оценки внутри ТИ первого  , второго r и третьего s заданных элементов ОП на предыдущем (j-1)-м ДО; K1 и К2 - нормировочные коэффициенты, K1 - определяет степень доверия к откорректированным начальным условиям с каждым тактом он увеличивается т.к увеличивается степень доверия к этим значениям ДО, K2 - определяет степень доверия к оценочному значению принятому из канала связи и с каждым тактом он уменьшается, величина коэффициентов выбирается из области 0 и 1 в дробных значениях; ξij- - наблюдаемая смесь;

, второго r и третьего s заданных элементов ОП на предыдущем (j-1)-м ДО; K1 и К2 - нормировочные коэффициенты, K1 - определяет степень доверия к откорректированным начальным условиям с каждым тактом он увеличивается т.к увеличивается степень доверия к этим значениям ДО, K2 - определяет степень доверия к оценочному значению принятому из канала связи и с каждым тактом он уменьшается, величина коэффициентов выбирается из области 0 и 1 в дробных значениях; ξij- - наблюдаемая смесь;  - аналоговое значение нелинейной функции преобразования от заданных элементов ОП на (j-1)-м ДО;

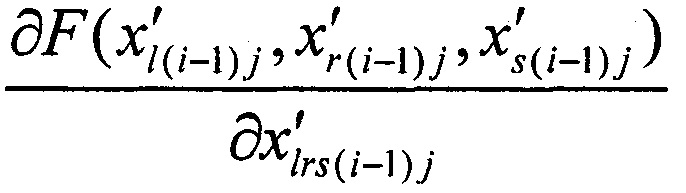

- аналоговое значение нелинейной функции преобразования от заданных элементов ОП на (j-1)-м ДО;  - значения частных производных функции F по соответствующим компонентам

- значения частных производных функции F по соответствующим компонентам  , r, s.

, r, s.

Тогда, уравнения оценивания для моментов времени, tij, соответствующих границам ТИ будут иметь вид:

где  - аналоговые начальные условия для оценки на границах ТИ первого

- аналоговые начальные условия для оценки на границах ТИ первого  , второго r и третьего s заданных элементов опорной последовательности (ОП), взятые на предыдущем (i-1)-м ТИ;

, второго r и третьего s заданных элементов опорной последовательности (ОП), взятые на предыдущем (i-1)-м ТИ;  - аналоговое значение нелинейной функции преобразования от заданных элементов ОП на (i-1)-м ТИ;

- аналоговое значение нелинейной функции преобразования от заданных элементов ОП на (i-1)-м ТИ;  - значения частных производных функции F по соответствующим компонентам

- значения частных производных функции F по соответствующим компонентам  , r, s на (i-1)-м ТИ, К - заданный весовой коэффициент.

, r, s на (i-1)-м ТИ, К - заданный весовой коэффициент.

Установление правильного приема служебно-технологических команд фиксируется по правилу

т.е последовательность считается верно принятой, если наблюдается совпадение состояний значений начальных условий и оценочных значений на протяжении 2n-m тактов обработки.

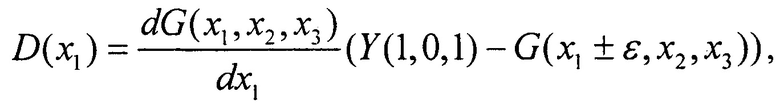

В качестве примера рассмотрим случай формирования оценочного значения на одном такте обработки. Пусть значение выходного элемента ПСП формируется следующим образом: Y(1,0,1)=1. Значения частных производных будут иметь вид:

Пусть значение заданного элемента ОП x1 не соответствует истинному и имеет приращение x1±ε. В этом случае

где D(x1) - корректирующее значение для формирования оценочного значения первого заданного элемента ОП, тогда

D(х1)=(0-0+0)(Y(1,0,1)-G(x1±ε, х2, х3))=0.

Анализируя полученный результат можно сделать вывод, что при любых значениях х1±ε корректирующее значение формироваться не будет, т.е. на данном такте обработки осуществить подстройку первого элемента нельзя. В ЛРР произойдет перезапись ранее хранившегося значения. Дискриминационная характеристика будет отсутствовать (Фиг. 4).

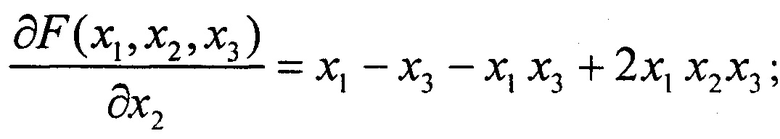

Пусть значение заданного элемента ОП x2 не соответствует истинному и имеет приращение x2±ε. В этом случае

тогда

D(x2)=(1-1-1+0)(Y(1,0,1)-G(x1, х2±ε, х3))=1.

В этом случае:

если х2±ε=0, то есть, если значение х2 соответствует своему истинному значению 0 и приращение ε=0, то корректирующее значение формироваться не будет и D(x2)=0 (см. Фиг. 5, точка А);

если х2±ε<0, то есть, если значение х2 меньше своего истинного значения 0 за счет отрицательного приращения ε, то сформируется положительное корректирующее значение D(x2)>0 (см. Фиг. 5, точка В);

если х2±ε>0, то есть, если значение х2 больше своего истинного значения 0 за счет положительного приращения ε, то сформируется отрицательное корректирующее значение D(x2)<0. Дискриминационная характеристика будет выглядеть, как показано на Фиг. 5, точка C.

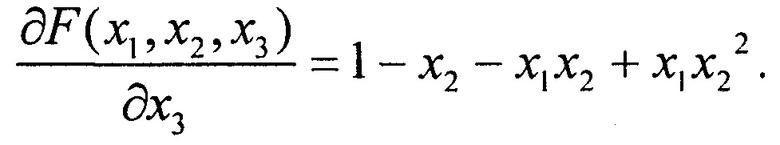

Пусть значение заданного элемента ОП x3 не соответствует истинному и имеет приращение x3±ε. В этом случае

т.е. D(x3)=(1-0-0+0)(Y(1,0,1)-G(x1, х2, х3±ε))=1.

Анализируя полученный результат, можно сделать следующие выводы:

если x3±ε=0, то есть, если значение x3 соответствует своему истинному значению 0 и приращение ε=0, то корректирующее значение формироваться не будет и D(x3)=0 (см. Фиг. 6, точка А);

если x3±ε<0, то есть, если значение x3 меньше своего истинного значения 0 за счет отрицательного приращения ε, то сформируется положительное корректирующее значение D(x3)>0 (см. Фиг. 6, точка В);

если x3±ε>0, то есть, если значение x3 больше своего истинного значения 0 за счет положительного приращения ε, то сформируется отрицательное корректирующее значение D(x3)<0. Дискриминационная характеристика будет выглядеть, как показано на Фиг. 6, точка C.

Отсюда можно прийти к заключению, что на любом такте обработки возможно корректировка лишь некоторых заданных значений. В данном случае возможна корректировка только третьего элемента. Возможные варианты представлены в таблице Фиг. 7. Из таблицы видно, что в первом случае можно осуществить корректировку третьего элемента, во втором - первого, в третьем - второго и третьего и т.д. Рассмотренный пример соответствует седьмому случаю. После обработки сигнала во второй ветви обработки происходит сравнение значений элементов сигнала со значениями, полученными в первой ветви обработки. При совпадении m-количество раз элементов сигнала поразрядно полученных в первой и второй ветви обработки, как указанно выше, полученная синхропоследовательность считается правильной.

Отличие данного способа от известных заключается в том, что не требуется многократная передача служебно-технологических команд по каналу связи с последующей мажоритарной обработкой на приеме, либо безошибочный прием зачетного отрезка рекуррентной последовательности, так как это приводит к увеличению времени обработки принятой последовательности при отношениях сигнал/шум меньше единицы, а также позволяет уменьшить время обработки служебно-технологических команд в условиях радиоэлектронного противодействия за счет улучшения точности оценки единичного элемента принятой последовательности.

Результаты моделирования представлены на Фиг. 8 в виде графиков зависимости количества ошибочных значений генераторов на передаче и приеме от количества тактов обработки в случае:

1 - реализации способа синхронизации, представленного в описании к патенту на изобретение RU №21532300080 "Способ и устройство синхронизации М-последовательности с повышенной сложностью";

2 - заявленного способа безопасной обработки служебно-технологических команд.

Из графиков видно, что определение безошибочного состояния генераторов ПСП на передаче и приеме происходит за меньшее количество тактов обработки при реализации заявленного способа безопасной обработки служебно-технологических команд, что свидетельствует об уменьшении времени обработки принятой последовательности за счет улучшения точности оценки единичного элемента последовательности.

Работоспособность предложенного способа исследовались при различных исходных данных, а именно, при различных: примитивных полиномах и длинах ЛРР; начальных заполнениях ЛРР; точках подключения НУУ к ЛРР; видах функции нелинейного преобразования. Результаты программного моделирования процесса безопасной обработки служебно-технологических команд для ЛРР, построенных на примитивных триномах 17-й, 31-й и НУУ в виде трех трехвходовых узлов, приведены на Фиг. 9, в виде зависимости количества ошибочных значений состояния приемного генератора от числа тактов обработки. Рассмотрено три случая.

В первом случае, для ЛРР длиной 17, при случайном начальном заполнении (8 ячеек регистра из 17 хранят ложные значения) оценка текущего состояния регистра осуществляется в течение 100÷200 тактов, что не превышает nэ=4913. Отметим, что противнику необходимо перехватить 2nэ=9826 смежных элемента ПСП.

Во втором случае, для ЛРР длиной 31, при случайном начальном заполнении (16 ячеек регистра из 31 хранят ложные значения) оценка текущего состояния регистра осуществляется в течение 300÷400 тактов, что не превышает nэ=29791. В этом случае противнику необходимо перехватить 2nэ=59582 смежных элементов ПСП.

Полученные результаты позволяют сделать вывод о работоспособности предложенного способа безопасной обработки служебно-технологических команд и возможности обработки принятой последовательности за время длительности не превышающее 2nэ тактов обработки. Это свидетельствует о том, что для криптоаналитика противника становится скрытным сам факт передачи и обработки служебно-технологических команд в инфокоммуникационных системах.

Устройство безопасной обработки служебно-технологических команд, представленное на Фиг. 10, состоит из дискретизатора 1, выделителя тактовой частоты 2, корректора 3, блока формирования уточненных предсказанных значений 4, первого коммутатора 5, второго коммутатора 6, блока аналоговых линий задержек 7, блока квантователей 8, блока цифровых линий задержек 9, блока управления 10, генератора опорных кодовых последовательностей 11, генератора опорного сигнала 12, цифрового нелинейного узла усложнения 13, второго блока квантователей 14, блока поэлементного сравнения 15 и вычислительного блока 16.

Приемный информационный вход дискретизатора 1 в параллель соединен с входом выделителя тактовой частоты 2 и является входом устройства. Первый управляющий выход выделителя тактовой частоты 2 в параллель соединен с управляющими входами блока формирования уточненного предсказанного значения 4, первого коммутатора 5, блока цифровых линий задержек 9, блока управления 10, генератора опорных кодовых последовательностей 11, генератора опорного сигнала 12. Второй управляющий выход выделителя тактовой частоты 2 в параллель соединен с управляющими входами дискретизатора 1 и блока аналоговых линий задержек 7. Выход дискретизатора 1 подключен к приемному информационному входу корректора 3. Первый, второй и третий информационные входы корректора 3 подключены соответственно к первому, второму и третьему информационным выходам первого коммутатора 5. Первый, второй и третий информационные выходы корректора 3 подключены соответственно к первому, второму и третьему информационным входам блока аналоговых линий задержек 7, выходы которого соединены соответственно с четвертым, пятым и шестым информационными входами первого коммутатора 5. Первый, второй и третий информационные входы блока формирования уточненных предсказанных значений 4 в параллель соединены с первым, вторым и третьим информационными входами блока квантователей 8 и подключены к первому, второму и третьему информационным выходам генератора опорных кодовых последовательностей 11 соответственно. Четвертый, пятый и шестой информационные входы блока формирования уточненных предсказанных значений 4 подключены к четвертому, пятому и шестому информационным выходам первого коммутатора 5 соответственно. Первый, второй и третий информационные выходы блока формирования уточненных предсказанных значений 4 соединены с первым, вторым и третьим информационными входами первого коммутатора 5 соответственно. Четвертый, пятый и шестой информационные выходы блока формирования уточненных предсказанных значений 4 в параллель соединены с четвертым, пятым и шестом информационными входами блока квантователей 8 и с первым, вторым и третьим информационными входами генератора опорных кодовых последовательностей 11 соответственно. Первый, второй и третий выходы блока квантователей 8 соединены соответственно с первым, вторым и третьим входом блока цифровых линий задержек 9, выходы которого подключены соответственно к первому, второму и третьему информационным входам блока управления 10. Управляющий выход блока управления 10 соединен с управляющим входом второго коммутатора 6. Четвертый, пятый и шестой выходы блока квантователей 8 в параллель соединены с четвертым, пятым и шестым информационными входами блока управления 10 соответственно и с первым, вторым и третьим входом второго коммутатора 6 соответственно. Первый, второй и третий выходы генератора опорного сигнала 12 подключены соответственно к четвертому, пятому и шестому входам второго коммутатора 6. Первый, второй и третий выходы второго коммутатора 6 соединены в параллель с первым, вторым и третьим информационными входами генератора опорного сигнала 12 соответственно и с первым, вторым и третьим входами цифрового нелинейного узла усложнения 13 соответственно. Первый вход второго блока квантователей 14 в параллель соединен с первым входом дискретизатора 1 и первым входом выделителя тактовой частоты 2. Второй вход второго блока квантователей 14 в параллель соединен с третьим входом блока поэлементного сравнения 15, четвертым входом генератора опорных кодовых последовательностей 11, первым входом вычислительного блока 16, первым входом генератора опорного сигнала 11, седьмым входом блока формирования уточненных предсказанных значений 4, четвертым входом первого коммутатора 5 и вторым выходом умножителя тактовой частоты 2. Выход второго блока квантователей 14 соединен с первым входом блока поэлементного сравнения 15. Второй вход блока поэлементного сравнения 15 соединен с выходом цифрового нелинейного узла усложнения 13. Третий вход блок обработки поэлементного сравнения 15 в параллель соединен со вторым входом второго блока квантователей 14, четвертым входом генератора опорных кодовых последовательностей 11, первым входом вычислительного блока 16, первым входом генератором опорного сигнала 11, седьмым входом блока формирования уточненных предсказанных значений 4, четвертым входом первого коммутатора 5 и вторым выходом выделителя тактовой частоты 2. Выход блока поэлементного сравнения 15 соединен с пятым входом блока оценочных значений 16. Первый вход вычислительного блока 16 в параллель соединен со вторым входом второго блока квантователей 8, с третьим входом блока поэлементного сравнения 15 четвертым входом генератора опорных кодовых последовательностей 11, первым входом генератором опорного сигнала 12, седьмым входом блока формирования уточненных предсказанных значений 4, четвертым входом первого коммутатора 5 и вторым выходом выделителя тактовой частоты 2. Второй вход блока оценочных значений 16 в параллель соединен с первым выходом второго коммутатора 14, вторым входом генератора опорного сигнала 12, первым входом цифрового нелинейного узла усложнения 13. Третий вход вычислительного блока 16 в параллель соединен со вторым выходом второго коммутатора 6, третьим входом генератора опорного сигнала 12, вторым входом цифрового нелинейного узла усложнения 13. Четвертый вход вычислительного блока 16 в параллель соединен с третьим выходом второго коммутатора 6, четвертым входом генератора опорного сигнала 12, третьим входом цифрового нелинейного узла усложнения 13. Выход блока оценочных значений 16 является выходом устройства.

Дискретизатор 1 предназначен для дискретизации информационного сигнала с частотой в k раз превышающий тактовую частоту информационного сигнала. По физической сущности дискретизатор 1 является прерывателем. Схемы прерывателей, которые можно использовать в качестве дискретизатора 1, известны и приведены, например, в книге: Ж. Маркюс "Дискретизация и квантование". -М.: Энергия. 1969, стр. 52, рис. 2.11.

Выделитель тактовой частоты 2 предназначен для выделения тактовой частоты и частоты дискретизации в k раз превышающий тактовую из принимаемой ПСП. По физической сущности схема выделителя тактовой частоты 2 соответствует схеме фазового дискриминатора. Схема фазового дискриминатора, который может быть использован в устройстве синхронизации, известна и приведена, например, в книге Е.М. Мартынова "Синхронизация в системах передачи дискретных сообщений". - М.: Связь. 1972, стр. 108, рис. 6.16. С учетом особенностей заявленного устройства, схема выделителя тактовой частоты 2 может быть реализована, как показано на Фиг. 12 в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Корректор 3 предназначен для получения откорректированных значений заданных элементов опорной кодовой последовательности и его структура идентична структуре, показанной на Фиг. 13 в описании к патенту на изобретение №2153230 RU "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Блок формирования уточненных предсказанных значений 4 предназначен для формирования уточненных предсказанных значений из заданных значений ОКП, его структура идентична структуре, показанной на Фиг. 4 в описании к патенту на изобретение RU №2320080 "Способ и устройство синхронизации псевдослучайных последовательностей".

Первый коммутатор 5 предназначен для переключения режимов работы устройства безопасной обработки служебно-технологических команд при получении откорректированных значений заданных элементов опорной кодовой последовательности внутри тактовых интервалов и на его границах. Структурная схема первого коммутатора 5 идентична структурной схеме, показанной на Фиг. 16 в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Второй коммутатор 6 предназначен для переключения режимов работы устройства безопасной обработки служебно-технологических команд в режиме генерации ПСП. Структурная схема второго коммутатора 6 идентична структурной схеме, показанной на Фиг. 18 в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Блок аналоговых линий задержек 7 предназначен для задерживания аналоговых откорректированных значений заданных элементов опорной кодовой последовательности на время длительности одного дискретизированного отсчета принимаемого сигнала. Структурная схема блока аналоговых линий задержек 7 идентична структурной схеме, показанной на Фиг. 20 в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Блок квантователей 8 предназначен для квантования аналоговых откорректированных значений заданных элементов опорной кодовой последовательности по уровню 0 и 1. Структурная схема блока квантователей 8 идентична структурной схеме, показанной на Фиг. 22 в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Блок цифровых линий задержек 9 предназначен для задерживания квантованных откорректированных значений заданных элементов опорной кодовой последовательности на время длительности одного элемента принимаемого сигнала. Структурная схема блока цифровых линий задержек 9 идентична структурной схеме, показанной на Фиг. 23 в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Блок управления 10 предназначен для формирования управляющего воздействия на запуск генератора опорного сигнала. Структурная схема блока управления 10 идентична структурной схеме, показанной на Фиг. 24 в описании к патенту RU на изобретение №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Генератор опорных кодовых последовательностей 11 предназначен для формирования опорной кодовой последовательности с использованием аналоговых значений ее элементов. Структурная схема генератора опорных кодовых последовательностей 11 идентична структурной схеме, показанной на Фиг. 28 в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Генератор опорного сигнала 12 предназначен для генерирования псевдослучайной последовательности синхронной с принимаемой. Структурная схема генератора опорного сигнала 12 идентична структурной схеме, показанной на Фиг. 30 в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Цифровой нелинейный узел усложнения 13 предназначен для формирования псевдослучайной последовательности синхронной с принимаемой. Структурная схема цифрового нелинейного узла усложнения 13 идентична структурной схеме, показанной на Фиг. 31 в описании к патенту на изобретение RU №2153230 "Способ и устройство синхронизации М-последовательности с повышенной сложностью".

Второй блок квантователей 14, показанный на Фиг. 11, предназначен для квантования элементов сигнала по уровню 0 и 1 из принятой смеси сигнала и шума. Второй блок квантователей 14 состоит из одного квантователя 14.1 сигнала по уровню 0 или 1 и линии задержки 14.2. Информационный вход второго блока квантователей 14 подключен к входу квантователя 14.1, выход квантователя 14 подключен к первому входу линии задержки 14.2, управляющий вход второго блока квантователей 14 подключен ко второму входу линии задержки 14.2, выход линии задержки 14.2 подключен к информационному выходу второго блока квантователей 14. Информационный вход второго блока квантователей 14 является первым входом блока квантователей 14, управляющий вход второго блока квантователей 14 является входом второго блока квантователей 14, информационный выход второго блока квантователей 14 является выходом второго блока квантователей 14. Кроме того, квантователь 14.1 дополнительно снабжен входом опорного напряжения. По своей физической сути квантователь является компаратором, реагирующим на разность двух сигналов, один из которых опорный. Схемы компараторов, которые могут быть использованы во втором блоке квантователей, известны и показаны, например, в книге: М.У. Банк. "Аналоговые интегральные схемы в радиоаппаратуре". - М.: Радио и связь. 1981, стр. 26, рис. 2.19(a). Цифровая линия задержки 14.2 по своей сути является тактируемым D-триггером, инверсный выход которого в устройстве не используется. Схемы цифровых линий задержек, которые могут быть использованы во втором блоке квантования 14 в качестве цифровых линий задержек 14.2, известны и показаны, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". - М.: Радио и связь. 1986, стр. 26, рис. 13.

Блок поэлементного сравнения 15, показанный на Фиг. 12, предназначен для сравнения поэлементно на продолжительности m-тактов обработки сигнала, поступившего с выхода второго блока квантователей 14 и сигнала поступившего после корректировки из нелинейного узла усложнения 13, а также выдачи с выхода блока поэлементного сравнения 15 управляющего воздействия на пятый вход вычислительного блока 16. Блок поэлементного сравнения 15 состоит из сумматора по модулю два 15.1, последовательного регистра 15.2. и дешифратора 15.3. Первый вход блока поэлементного сравнения 15 является первым входом сумматора по модулю два 15.1. Второй вход блока о поэлементного сравнения 15 является вторым входом сумматора по модулю два 15.1, выход которого является первым входом последовательного регистра 15.2. Третий вход блока поэлементного сравнения 15 является вторым входом последовательного регистра 15.2. Выходы последовательного регистра от первого до m-го соединены с соответствующими входами дешифратора 15.3. Выход дешифратора 15.3 является управляющим выходом блока поэлементного сравнения 15. Сумматор по модулю два, показанный на Фиг. 12, предназначен для сложения по модулю два поэлементно сигнала с выхода второго блока квантователей 14 и сигнала после корректировки из нелинейного узла усложнения 13. Схемы сумматора по модулю два 15.1, которые могут быть использованы в блоке поэлементного сравнения 15, известны и приведены, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". - М.: Радио и связь. 1986, стр. 22, рис. 10. Последовательный регистр 15.2, схема которого представлена на Фиг. 13, состоит из m цифровых линий задержек 15.2. Информационный вход последовательного регистра 15.2 подключен к входу первой цифровой линии задержки 15.2.1, выход которой подключен к входу i-той цифровой линии задержки 15.2i, где i=1…m, и первому выходу последовательного регистра 15.2. Выход m-ой цифровой линии задержки 15.2.m подключен к m выходу последовательного регистра 15.2. Управляющий вход последовательного регистра 15.2 подключен к управляющим входам всех m цифровых линий задержек 15.2. Цифровая линия задержки 15.2.1-15.2.m по своей сути является тактируемым D-триггером, инверсный выход которого в устройстве не используется. Схемы цифровых линий задержек 15.2.1-15.2.m, которые могут быть использованы в последовательном регистре 15.2, известны и приведены, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". -М.: Радио и связь. 1986, стр. 26, рис. 13.

Дешифратор 15.3. Фиг. 14, состоит из m двухвходовых элементов "И" 15.3.1-15.3m. Первый вход дешифратора 15.3 соединен с первым выходом последовательного регистра 15.2 и первым входом элемента "И" 15.3.1, выход которого соединен с первым входом элемента "И" 15.3.2, второй вход дешифратора 15.3 соединен со вторым выходом последовательного регистра 15.2 и входом элемента "И" 15.3.1, третий вход дешифратора 15.3 соединен с третьим выходом последовательного регистра 15.2 и вторым входом элемента "И" 15.3.2 и так далее, m-вход дешифратора соединен с m-входом элемента "И" 15.3.m, выход которого является выходом поэлементного сравнения 15. Схемы элементов "И" 15.3.1-15.3.m, которые могут быть использованы в дешифраторе 15.3 известны и показаны, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". - М.: Радио и связь. 1986, стр. 21, рис. 9а.

Вычислительный блок 16 состоит из выключателя разрешения 16.1 и параллельного регистра 16.2 Фиг. 15. Параллельный регистр 16.2 состоит из 16.2.1-16.2.3 линий задержки Фиг. 15. Первый вход вычислительного блока 16 является первым управляющим входом выключателя разрешения 16.1, выход которого в параллель соединен с первыми входами элементов 16.2.1, 16.2.2, 16.2.3 регистра 16.2. Второй вход вычислительного блока 16 является первым информационным входом регистра 16.2 и вторым входом первого элемента регистра 16.2.1. Третий вход вычислительного блока 16 является вторым информационным входом регистра 16.2 и вторым входом второго элемента регистра 16.2.2. Третий вход вычислительного блока 16 является третьим информационным входом регистра 16.2 и вторым входом третьего элемента регистра 16.2.3, выход которого является выходом параллельного регистра 16.2 и выходом вычислительного блока 16. Пятый вход вычислительного блока 16 является управляющим входом выключателя разрешения 16.1. Выход вычислительного блока является выходом устройства синхронизации нелинейных рекуррентных последовательностей.

Параллельный регистр 16.2, схема которого представлена на Фиг. 15 состоит из цифровых линий задержек 16.2.1, 16.2.2, 16.2.3. Цифровая линия задержки по своей сути является тактируемым D-триггером, инверсный выход которого в устройстве не используется. Схемы цифровых линий задержек 16.2.1, 16.2.2, 16.2.3, которые могут быть использованы в последовательном регистре 9.3, известны и приведены, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". - М.: Радио и связь. 1986, стр. 26, рис. 13. Выключатель разрешения 16.1, показанный на Фиг. 15, по своей физической сущности соответствуют схеме элементарного управляемого переключателя. Схемы управляемых элементарных переключателей известны и приведены, например, в книге В.Л. Шило "Популярные микросхемы КМОП, справочник", - М.: Ягуар. 1993, стр. 22.

Заявленное устройство безопасной обработки служебно-технологических команд работает следующим образом. Смесь сигнала и шума поступает на приемный информационный вход устройства, показанного на Фиг. 10. Сначала сигнал параллельно поступает на приемный информационный вход второго квантователя 14 для обработки в первой ветви, а также на входы дискретизатора 1 и выделителя тактовой частоты 2 для обработки во второй ветви обработки. В выделителе тактовой частоты 2 определяют период следования информационных сигналов и на первом управляющем выходе выделителя тактовой частоты 2 и получают стробирующие импульсы с тактовой частотой информационного сигнала. На втором управляющем выходе выделителя тактовой частоты 2 получают стробирующие импульсы с частотой в k раз превышающей тактовую частоту информационного сигнала. Кроме того, смесь сигнала и шума с входа устройства синхронизации псевдослучайной последовательности поступает в дискретизатор 1. На управляющий вход дискретизатора 1 поступают стробирующие импульсы с частотой в k раз превышающей тактовую частоту информационного сигнала. В дискретизаторе 1 получают дискретизированные отсчеты информационного сигнала, с частотой в k раз выше тактовой частоты информационного сигнала. С выхода дискретизатора 1 дискретизированные отсчеты информационного сигнала поступают на приемный информационный вход корректора 3.

В случае первоначального вхождения в синхронизм в генераторе опорных кодовых последовательностей 11 должны быть записаны произвольные ненулевые аналоговые значения начальных условий в области определения от 0 до 1 или могут находиться значения, оставшиеся с предыдущего сеанса связи.

Под воздействием стробирующего импульса с тактовой частотой поступающего на управляющий вход генератора опорных кодовых последовательностей 11, значения заданных элементов опорной кодовой последовательности считываются и поступают на первый, второй и третий информационные выходы генератора опорных кодовых последовательностей 11. На первый, второй и третий информационные выходы генератора опорных кодовых последовательностей 11 поступают предсказанные значения информационного сигнала. С первого, второго и третьего информационных выходов генератора опорных кодовых последовательностей 11 значения заданных элементов поступают одновременно на первый, второй и третий информационные входы блока формирования уточненного предсказанного значения 4 и на первый, второй и третий информационные входы блока квантователей 8. В блоке квантователей 8 значения заданных элементов опорной кодовой последовательности квантуются и поступают соответственно на первый, второй и третий информационные выходы блока квантователей 8. С первого, второго и третьего информационного выхода блока квантователей 8 квантованные значения заданных элементов опорной кодовой последовательности поступают на первый, второй и третий информационные входы блока цифровых линий задержек 9, где производится задержка сигналов на время длительности одного такта принимаемого сигнала.

Под воздействием стробирующего импульса с тактовой частотой, поступающего на управляющий вход блока цифровых линий задержек 9, квантованные значения считывают и поступают на первый, второй и третий информационные выходы блока цифровых линий задержек 9. С первого, второго и третьего информационных выходов блока цифровых линий задержек 9 квантованные значения поступают соответственно на первый, второй и третий информационные входы блока управления 10.

Под воздействием стробирующего импульса с тактовой частотой поступающего на управляющий вход первого коммутатора 5, уточненные предсказанные значения с первого, второго и третьего информационных выходов блока формирования уточненного предсказанного значения 4 (Фиг. 4) поступают на первый, второй и третий информационные входы первого коммутатора 5 и соответственно на первый, второй и третий информационные выходы первого коммутатора 5, а четвертый, пятый и шестой информационные входы первого коммутатора 5 проключаются соответственно на четвертый, пятый и шестой информационные выходы первого коммутатора 5.

С первого, второго и третьего информационных выходов первого коммутатора 5 уточненные предсказанные значения информационного сигнала поступают соответственно на первый, второй и третий информационные входы корректора 3. В корректоре 3 осуществляется корректировка уточненных предсказанных значений. Откорректированные сигналы поступают на первый, второй и третий информационные выходы корректора 3 и на первый, второй и третий информационные входы блока аналоговых линий задержек 7, где их задерживают на время длительности одного дискретизированного отсчета. Откорректированные сигналы с первого, второго и третьего информационных выходов блока аналоговых линий задержек 7 поступают на четвертый, пятый и шестой информационные входы первого коммутатора 5. При поступлении последующих дискретизированных отсчетов сигнала, начиная со второго и до k-го, стробирующие импульсы с частотой равной тактовой частоте следования информационных сигналов на управляющий вход первого коммутатора 5 не поступают. С четвертого, пятого и шестого информационного входа первого коммутатора 5 откорректированные сигналы поступают соответственно на первый, второй и третий информационные выходы первого коммутатора 5 и затем на первый, второй и третий информационные входы корректора 3, где производится повторная корректировка откорректированных значений с учетом последующего дискретизированного отсчета принимаемого сигнала. Таким образом, осуществляется корректировка предсказанных значений информационного сигнала с учетом дискретизированных отсчетов принимаемого сигнала k раз. Откорректированные сигналы на k-м дискретизированном отсчете принимаемого сигнала поступают на четвертый, пятый и шестой информационные выходы первого коммутатора 5. С четвертого, пятого и шестого информационных выходов первого коммутатора 5 откорректированные сигналы поступают одновременно на четвертый, пятый и шестой информационные входы блока формирования уточненных предсказанных значений 4, где они проключаются на четвертый, пятый и шестой информационные выходы блока формирования уточненных предсказанных значений 4. С четвертого, пятого и шестого информационных выходов блока формирования уточненных предсказанных значений 4 (фиг. 4) откорректированные сигналы в параллель поступают на четвертый, пятый и шестой информационные входы блока квантователей 8 и на первый, второй и третий информационные входы генератора опорных кодовых последовательностей 11. В генераторе опорных кодовых последовательностей 11 из откорректированных сигналов формируется опорная кодовая последовательность, значения заданных элементов которой корректируются на каждом такте обработки. В блоке квантователей 8 откорректированные сигналы квантуются и поступают на четвертый, пятый и шестой информационные выходы блока квантователей 8, откуда поступают одновременно на четвертый, пятый и шестой информационные входы блока управления 10 и на первый, второй и третий информационные входы второго коммутатора 6.

В блоке управления 10 под воздействием стробирующего импульса с тактовой частотой поступающего на управляющий вход блока управления 10, формируется управляющее воздействие на начало генерации псевдослучайной последовательности синхронной с принимаемой при условии совпадения предсказанных значений сигнала, поступающих на первый, второй и третий информационные входы блока управления 10 с откорректированными значениями на длительности 2n-m тактов обработки, поступающими на четвертый, пятый и шестой информационные входы блока управления 10. При отсутствии управляющего сигнала, поступающего на управляющий вход второго коммутатора 6, первый, второй и третий информационные входы второго коммутатора 6 проключаются соответственно на первый, второй и третий информационные выходы. Квантованные откорректированные значения принимаемого сигнала поступают одновременно на первый, второй и третий информационные входы генератора опорного сигнала 12 и на первый, второй и третий входы цифрового нелинейного узла усложнения 13, выход которого является выходом устройства синхронизации. Под воздействием управляющего сигнала, поступающего на управляющий вход второго коммутатора 6, четвертый, пятый и шестой информационные входы второго коммутатора 6 проключаются соответственно на первый, второй и третий информационные выходы второго коммутатора 6. При этом генератор опорного сигнала 12 переходит в автономный режим работы и генерирует ПСП, синхронную с ПСП на передающей стороне, а ПСП с выхода цифрового нелинейного узла усложнения 13, будет синхронна с принимаемой ПСП. А заполнение ячеек регистра генератора опорного сигнала 12 соответствует заполнению ячеек регистра на передающей стороне. Кроме того, получение откорректированных значений сигнала с учетом уточненных предсказанных значений не прекращается и производится непрерывно с целью получения предсказанных значений сигнала для сокращения времени при повторном вхождении в синхронизм. Таким образом, обеспечивается выполнение поставленной цели - сокращение времени вхождения в синхронизм за счет улучшения точности оценки единичного элемента псевдослучайной последовательности.

Квантованные откорректированные значения принимаемого сигнала поступают одновременно на входы цифрового линейного рекуррентного регистра 12 и на входы цифрового НУУ 13. С выхода цифрового НУУ 13 последовательность поступает в блок поэлементного сравнения 15, где сравнивается поразрядно с последовательностью полученной после квантования во втором блоке квантователей 14, при поразрядном совпадении m-количество раз блок поэлементного сравнения 15 выдает управляющее воздействие в вычислительный блок 16 выход которого является выходом устройства. Под воздействием управляющего сигнала от блока поэлементного сравнения 15 в вычислительный блок 16 считываются значения из регистров генератора опорного сигнала 12, которые заполнены к этому моменту в точности, как и формирующие регистры в передающем устройстве. На выходе вычислительного блока 16 в последовательном виде формируется последовательность СТК аналогичная с переданной.

Необходимо отметить, что получение откорректированных значений сигнала с учетом уточненных предсказанных значений не прекращается и производится непрерывно с целью получения предсказанных значений сигнала для сокращения времени при повторном вхождении в связь и приеме служебно-технологических команд. Таким образом, в рассмотренном устройстве реализуются все процедуры способа безопасной обработки служебно-технологических команд, являющиеся его особенностями и одновременно его достоинствами.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2005 |

|

RU2320080C2 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ С ПОВЫШЕННОЙ СЛОЖНОСТЬЮ | 1999 |

|

RU2153230C1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 2002 |

|

RU2244384C2 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1997 |

|

RU2127954C1 |

| ОДНОКАНАЛЬНАЯ МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОПРЕДЕЛЕНИЯ НАПРАВЛЕНИЯ НА ЦЕЛЬ | 1995 |

|

RU2079859C1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| Устройство автоматической коррекции координатных искажений телевизионного изображения | 1981 |

|

SU1012456A1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

Изобретение относится к области передачи служебно-технологических команд, сформированных на основе нелинейных рекуррентных последовательностей. Технический результат заключается в повышении скрытности передачи и приема служебно-технологических команд и уменьшении времени на их обработку. Способ и устройство предусматривают разделение принятой последовательности на две ветви обработки, в первой происходит квантование элементов принятой последовательности, а во второй ветви обработки происходит получение откорректированного значения информационного сигнала путем аналоговой обработки дискретизированных отсчетов информационного сигнала с учетом уточненного предсказанного значения сигнала, полученного на основе рекуррентного преобразования ранее принятых и оцененных информационных сигналов, и осуществляют считывание служебно-технологических команд с выхода устройства безопасной обработки служебно-технологических команд в инфокоммуникационных системах по результатам сравнения. 2 н.п. ф-лы, 15 ил.

1. Способ безопасной обработки служебно-технологических команд в инфокоммуникационных системах, заключающийся в передаче служебно-технологических команд, сформированных на основе нелинейных рекуррентных последовательностей, приеме нелинейной рекуррентной последовательности, отличающаяся тем, что при передаче служебно-технологические команды формируют на основе нелинейных рекуррентных последовательностей и разделяют на две ветви обработки: в первой происходит квантование элементов принятой последовательности, а во второй после дискретизации, задержки, формирования опорной кодовой последовательности в аналоговом виде, считывания аналоговых значений, квантования, задержки, корректировки считанных аналоговых значений, задержки откорректированных аналоговых значений, повторной корректировки аналоговых значений, квантования, запоминания, повторного формирования опорной кодовой последовательности, дополнительно введено формирование управляющего воздействия при сравнении опорной кодовой последовательности с откорректированной на продолжительности 2n-m тактов обработки и генерирование последовательности служебно-технологических команд, аналогичных с принимаемой, поразрядное сравнение значений элементов последовательности, полученной в первой ветви обработки, со значениями элементов последовательности, полученной во второй ветви обработки на продолжительности m-тактов, формирование управляющего воздействия по результатам сравнения на продолжительности m-тактов и разрешении считывания служебно-технологических команд с выхода устройства безопасной обработки служебно-технологических команд в инфокоммуникационных системах.