Предлагаемые технические решения объединены единым изобретательским замыслом и относятся к области радиотехники, а именно к области синхронизации сложных сигналов, в частности M-последовательностей с повышенной сложностью. M-последовательностью с повышенной сложностью принято считать последовательность, сформированную путем усложнения структуры М-последовательности нелинейным узлом усложнения.

Известны способы синхронизации М-последовательности, описанные, например:

- в статье Уорд Р. "Различение псевдошумовых сигналов методом последовательной оценки". - Зарубежная радиоэлектроника, 1966, N 8, с. 20 - 37, как способ RASE (Rapid Acqusition by Sequental Estimation) быстрого распознавания путем последовательной оценки;

- в книге В.И. Журавлев "Поиск и синхронизация в широкополосных системах". - М.: Радио и связь. 1986, с.86-102, как способы последовательной оценки символов псевдослучайной последовательности с одной ступенью проверки с.86, последовательной оценки с двумя ступенями проверки с.92, а также модифицированные способы последовательной оценки, такие как способ последовательной оценки символов и формирование метрик ненадежности с.95, по А.с. 315298 (СССР) (Способ вхождения в синхронизм / Авт. Изобр. В.И. Кириченко, Я.Д. Хацкелевич. - Опубл. В Б.И., 1971, N 28) и способ последовательной мажоритарной оценки символов ПСП с.97.

Каждый из перечисленных способов синхронизации заключается в разделении принятого информационного сигнала на две ветви обработки, временной задержке информационного сигнала в первой ветви, формировании оценочного сигнала и его задерживании во второй ветви, вычислении коэффициента корреляции между задержанной частью информационного сигнала первой ветви и оценочным значением информационного сигнала во второй ветви, формировании управляющего сигнала и генерировании M-последовательности, синхронной с принимаемой последовательностью.

Недостатками перечисленных способов синхронизации являются относительно высокое время синхронизации и низкая помехозащищенность в условиях воздействия преднамеренных помех, что обусловливается:

- предварительным квантованием принимаемого сигнала на два или более уровней и проведением оценки сигнала в дискретном виде, приводящих к потере некоторой части информации;

- необоснованным отказом от учета рекуррентных свойств М-последовательности по предсказанию очередного символа на основе ранее принятых сигналов и использованием задержки сигнала, приводящих к увеличению времени вхождения в синхронизацию;

- детерминированностью структуры используемых M-последовательностей, не обеспечивающей высокой структурной скрытности синхропоследовательностей и помехозащищенности в условиях воздействия преднамеренных помех.

Наиболее близким по своей сущности к заявленному способу синхронизации M-последовательности с повышенной сложностью является "Способ синхронизации систем передачи дискретной информации с широкополосными сигналами" по А.с. SU 1363507 A1 / Авт. Изобр. Ю.В. Арзуманян и А.Х. Райхлин - Опубл. в Бюл. N 48, 30.12.87. Способ-прототип синхронизации М-последовательности заключается в приеме псевдослучайной последовательности (ПСП), запоминании принимаемого сигнала длительностью Tс, многократном считывании его k раз, формировании опорной кодовой последовательности (ОКП) в дискретном виде, многократном перемножении принимаемого сигнала длительностью Tс и ОКП, интегрировании результатов перемножения, определении максимума дискретной взаимокорреляционной функции, сравнении его с порогом, установлении соответствия между принимаемой ПСП и системой отсчета на приемной стороне, формировании управляющего воздействия.

Недостатками способа-прототипа синхронизации являются относительно высокое время синхронизации и низкая помехозащищенность в условиях воздействия преднамеренных помех, что обусловливается:

- предварительным квантованием принимаемого сигнала на два или более уровней и проведением оценки сигнала в дискретном виде, приводящих к потере некоторой части информации;

- необоснованным отказом от учета рекуррентных свойств M-последовательности по предсказанию очередного символа на основе ранее принятых сигналов, использованием задержки сигнала и проведением последующего перерасчета к реальному времени, приводящих к увеличению времени вхождения в синхронизацию;

- детерминированностью структуры используемых M-последовательностей, не обеспечивающей высокой структурной скрытности синхропоследовательностей и помехозащищенности в условиях воздействия преднамеренных помех.

Известны устройства, реализующие указанные выше способы синхронизации M-последовательности, описанные, например:

- в статье Уорд Р. "Различение псевдошумовых сигналов методом последовательной оценки". - Зарубежная радиоэлектроника, 1966, N 8, с. 23, рис.2;

- в книге В.И. Журавлев "Поиск и синхронизация в широкополосных системах". -М. : Радио и связь. 1986, с.86-102, где устройство, реализующее способ последовательной оценки с одной ступенью проверки, изображено на рис.3.1, а устройство, реализующее способ последовательной оценки с двумя ступенями проверки, изображено на с.98;

- по А. с. SU 1626426 A1 / Авт. Изобр. В.П. Ефимов, В.В. Епишев, С.Б. Матлашевский. - Опубл. в Бюл. N 5, 07.02.91, реализующему модификацию способа последовательной мажоритарной оценки символов ПСП как устройство поиска псевдошумового сигнала по задержке.

Каждое из перечисленных устройств включает в себя блок формирования оценочного сигнала, каскадно соединенные по информационным входам линию задержки, коррелятор и устройство управления, выход которого подключен к первому управляющему входу регистра сдвига с обратными связями, выход которого является выходом устройства синхронизации.

Недостатками перечисленных устройств синхронизации являются относительно высокое время синхронизации и низкая помехозащищенность в условиях воздействия преднамеренных помех, что обусловливается:

- предварительным квантованием принимаемого сигнала на два или более уровней и проведением оценки сигнала в дискретном виде, приводящих к потере некоторой части информации;

- необоснованным отказом от учета рекуррентных свойств M-последовательности по предсказанию очередного символа на основе ранее принятых сигналов и использованием задержки сигнала, приводящих к увеличению времени вхождения в синхронизацию;

- детерминированностью структуры используемых M-последовательностей, не обеспечивающей высокой структурной скрытности синхропоследовательностей и помехозащищенности в условиях воздействия преднамеренных помех.

Наиболее близким по своей сущности к заявленному устройству синхронизации M-последовательности является устройство, представленное в описании к авторскому свидетельству "Способа синхронизации систем передачи дискретной информации с широкополосными сигналами" по А.с. SU 1363507 A1 / Авт. Изобр. Ю. В. Арзуманян и А. Х. Райхлин - Опубл. в Бюл. N 48, 30.12.87. Известное устройство-прототип включает коммутатор, каскадно соединенные по информационным входам регистр сдвига, перемножитель, генератор опорных кодовых последовательностей, интегратор, пороговый блок, параллельный регистр, генератор опорного сигнала и блок управления, выход которого подключен к управляющему входу генератора опорного сигнала, выход которого является выходом устройства синхронизации.

Недостатками устройства-прототипа синхронизации являются относительно высокое время синхронизации и низкая помехозащищенность в условиях воздействия преднамеренных помех, что обусловливается:

- предварительным квантованием принимаемого сигнала на два или более уровней и проведением оценки сигнала в дискретном виде, приводящих к потере некоторой части информации;

- необоснованным отказом от учета рекуррентных свойств M-последовательности по предсказанию очередного символа на основе ранее принятых сигналов, использованием задержки сигнала и проведением последующего перерасчета к реальному времени, приводящих к увеличению времени вхождения в синхронизацию;

- детерминированностью структуры используемых M-последовательностей, не обеспечивающей высокой структурной скрытности синхропоследовательностей и помехозащищенности в условиях воздействия преднамеренных помех.

Целью изобретения заявленных технических решений является разработка способа синхронизации M-последовательности с повышенной сложностью и устройства, его реализующего, обеспечивающих уменьшение времени вхождения в синхронизацию при увеличении сложности M-последовательности.

Поставленная цель достигается тем, что в известном способе, заключающемся в приеме псевдослучайной последовательности, формировании опорной кодовой псевдослучайной последовательности, считывании ее значений, формировании управляющего воздействия и генерировании псевдослучайной последовательности, синхронной с принимаемой, принимают псевдослучайную последовательность повышенной сложности (ПСП ПС). ОКП формируют из псевдослучайной последовательности на основе характеристического полинома n-го порядка, где n≥3, путем нелинейного преобразования по заданной дискретной функции. Дискретизируют ее элементы с частотой, в k раз превышающей тактовую частоту принимаемой псевдослучайной последовательности повышенной сложности, где k≥2. При этом опорную кодовую псевдослучайную последовательность формируют в аналоговом виде, а считывают значения только предварительно заданных элементов опорной кодовой псевдослучайной последовательности. После этого их квантуют по уровням 0 и 1 и задерживают на время длительности одного элемента псевдослучайной последовательности повышенной сложности. Затем корректируют считанные значения каждого из заданных элементов опорной кодовой псевдослучайной последовательности с учетом первого дискретизированного отсчета (ДО) принятого элемента псевдослучайной последовательности повышенной сложности. Откорректированные значения заданных элементов опорной кодовой псевдослучайной последовательности задерживают на время длительности одного дискретизированного отсчета принятого элемента псевдослучайной последовательности повышенной сложности, а затем их повторно корректируют с учетом значения последующего дискретизированного отсчета принятого элемента псевдослучайной последовательности повышенной сложности. Причем корректировку и задержку откорректированных значений повторяют k раз. Откорректированные k раз значения квантуют по уровням 0 и 1 и запоминают на n тактов и, кроме того, из них повторно формируют опорную кодовую псевдослучайную последовательность, значения предварительно заданных элементов которой корректируют на следующем такте принимаемой псевдослучайной последовательности повышенной сложности.

Опорную кодовую псевдослучайную последовательность формируют по рекуррентному правилу формирования M-последовательности на основе заданного характеристического полинома n-го порядка, где n≥3, в которой используют ненулевые аналоговые значения ее элементов, а операцию суммирования по модулю 2 двух переменных x и y заменяют на операцию

x+y-2xy.

Для коррекции считанных значений предварительно заданных элементов опорной кодовой псевдослучайной последовательности их считывают за время длительности одного дискретизированного отсчета принятого элемента псевдослучайной последовательности повышенной сложности и нелинейно преобразуют по заданной аналоговой функции. Вычисляют производные заданной функции нелинейного преобразования по значениям предварительно заданных элементов опорной кодовой псевдослучайной последовательности, считанным за время длительности одного дискретизированного отсчета принимаемого элемента псевдослучайной последовательности повышенной сложности. После этого из значения текущего дискретизированного отсчета псевдослучайной последовательности повышенной сложности вычитают значение сформированного дискретизированного отсчета опорной кодовой псевдослучайной последовательности повышенной сложности и умножают на заданный весовой коэффициент. Затем параллельно умножают на значения производных по каждому значению предварительно заданных элементов опорной кодовой псевдослучайной последовательности, полученных ранее, и суммируют с соответствующими значениями предварительно заданных элементов опорной кодовой псевдослучайной последовательности.

Аналоговые значения предварительно заданных элементов опорной кодовой псевдослучайной последовательности и откорректированные значения заданных элементов опорной кодовой псевдослучайной последовательности, полученные на k-м дискретизированном отсчете принятого элемента псевдослучайной последовательности повышенной сложности квантуют по правилу

1, если x>0.5

0, если x≤0.5

Элементы псевдослучайной последовательности повышенной сложности, синхронной с принимаемой, генерируют путем нелинейного преобразования по заданной дискретной функции заданных дискретных значений элементов псевдослучайной последовательности, сформированной на основе характеристического полиномом n-го порядка, где n≥3, из квантованных откорректированных значений заданных элементов опорной кодовой псевдослучайной последовательности.

Управляющее воздействие формируют, если на длительности 2n тактов все квантованные значения заданных элементов опорной кодовой псевдослучайной последовательности равны соответствующим им откорректированным квантованным значениям заданных элементов опорной кодовой псевдослучайной последовательности.

Указанная новая совокупность выполняемых действий заявленного способа синхронизации M-последовательности с повышенной сложностью за счет применения псевдослучайных последовательностей повышенной сложности, корректировки значений предварительно заданных элементов сигнала без предварительного квантования в аналоговом виде, использования рекуррентных свойств M-последовательности по предсказанию очередного элемента сигнала на основе ранее принятых элементов сигнала позволяет сократить время синхронизации, повысить вероятность правильного приема сложных сигналов, а также повышает структурную скрытность синхропоследовательности и помехозащищенность в условиях воздействия преднамеренных помех.

Поставленная цель в заявленном устройстве достигается тем, что в устройство синхронизации, содержащее первый коммутатор, генератор опорных кодовых последовательностей, блок управления, генератор опорного сигнала, дополнительно введены дискретизатор, выделитель тактовой частоты, корректор, блок квантователей, второй коммутатор, блок аналоговых и блок цифровых линий задержек, цифровой нелинейный узел усложнения. Приемный информационный вход дискретизатора соединен со входом выделителя тактовой частоты и является входом устройства. Первый управляющий выход выделителя тактовой частоты соединен с управляющими входами первого коммутатора, блока цифровых линий задержек, блока управления, генератора опорных кодовых последовательностей, генератора опорного сигнала. Второй управляющий выход выделителя тактовой частоты соединен с управляющими входами дискретизатора и блока аналоговых линий задержек. Выход дискретизатора подключен к приемному информационному входу корректора. Первый, второй и третий информационные входы корректора подключены соответственно к первому, второму и третьему информационным выходам первого коммутатора. Первый, второй и третий информационные выходы корректора подключены соответственно к первому, второму и третьему информационным входам блока аналоговых линий задержек, выходы которого соединены соответственно с четвертым, пятым и шестым информационными входами первого коммутатора. Первый, второй и третий выходы генератора опорных кодовых последовательностей подключены соответственно к первому, второму и третьему информационным входам первого коммутатора и к первому, второму и третьему входам блока квантователей. Четвертый, пятый и шестой информационные выходы первого коммутатора подключены соответственно к четвертому, пятому и шестому входам блока квантователей. Первый, второй и третий выходы блока квантователей соединены соответственно с первым, вторым и третьим входами блока цифровых линий задержек, выходы которого подключены соответственно к первому, второму и третьему информационным входам блока управления. Управляющий выход блока управления соединен с управляющим входом второго коммутатора. Четвертый, пятый и шестой выходы блока квантователей соединены соответственно с четвертым, пятым и шестым информационными входами блока управления и соответственно с первым, вторым и третьим входами второго коммутатора. Первый, второй и третий выходы генератора опорного сигнала подключены соответственно к четвертому, пятому и шестому входам второго коммутатора. Первый, второй и третий выходы второго коммутатора соединены соответственно с первым, вторым и третьим информационными входами генератора опорного сигнала и соединены соответственно с первым, вторым и третьим входами цифрового нелинейного узла усложнения, выход которого является выходом устройства.

Корректор состоит из аналогового нелинейного узла усложнения, первого, второго, третьего и четвертого аналоговых сумматоров, умножителя на постоянный множитель, первого, второго и третьего аналоговых перемножителей и первого, второго и третьего блоков вычисления производных. Выход аналогового нелинейного узла усложнения подключен ко второму информационному входу четвертого аналогового сумматора. Выход четвертого аналогового сумматора соединен со входом умножителя на постоянный множитель, выход которого подключен к первым входам соответственно первого, второго и третьего аналоговых перемножителей. Вторые входы первого, второго и третьего аналоговых перемножителей соединены с выходами соответственно первого, второго и третьего блоков вычисления производных. Выходы первого, второго и третьего аналоговых перемножителей соединены соответственно с первыми входами первого, второго и третьего аналоговых сумматоров, выходы которых являются соответственно первым, вторым и третьим информационными выходами корректора. Первый вход аналогового нелинейного узла усложнения, соединенный с первым входом третьего блока вычисления производных, соединенный со вторым входом первого аналогового сумматора, является первым информационным входом корректора. Второй информационный вход аналогового нелинейного узла усложнения, соединенный со вторым входом третьего блока вычисления производных и вторым входом второго аналогового сумматоpa, является вторым информационным входом корректора. Третий вход аналогового нелинейного узла усложнения, соединенный со входом второго блока вычисления производных, соединенный со входом первого блока вычисления производных, соединенный со вторым входом третьего аналогового сумматора, является третьим информационным входом корректора. Причем третий и второй блоки вычисления производных дополнительно снабжены входами опорного напряжения от источника опорного напряжения положительной полярности, структурная схема которого в устройстве не приведена.

Генератор опорных кодовых последовательностей состоит из n аналоговых линий задержек, n+1 умножителей на постоянный множитель и n-1 вычислителей функции обратной связи. Управляющий вход генератора опорных кодовых последовательностей соединен с управляющими входами n аналоговых линий задержек. Выходы всех n аналоговых линий задержек соединены со входами i-тых умножителей на постоянный множитель, где i=2...(n+1), и j-тыми входами аналоговых линий задержек, где j=2...n. Выходы j-тых умножителей на постоянный множитель подключены ко вторым входам соответствующих вычислителей функции обратной связи. Выход (n+1)-го умножителя на постоянный множитель подключен к первому входу (n-1)-го вычислителя функции обратной связи. Выходы, начиная с (n-1)-го вычислителя функции обратной связи и до первого, соединены последовательно с первыми входами соответствующих вычислителей функции обратной связи. Выход первого вычислителя функции обратной связи подключен ко входу первого умножителя на постоянный множитель, выход которого соединен со входом первой аналоговой линии задержки. Причем выходы предварительно заданных аналоговых линий задержек подключены к соответствующим умножителям на постоянный множитель и являются соответственно первым, вторым и третьим информационными выходами генератора опорных кодовых последовательностей. Входы последующих за предварительно заданными аналоговыми линиями задержек являются соответственно первым, вторым и третьим информационными входами генератора опорных кодовых последовательностей.

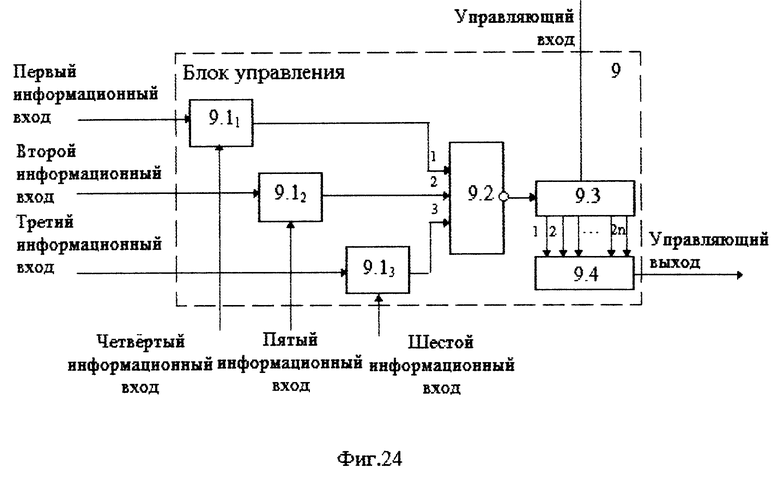

Блок управления состоит из первого, второго и третьего сумматоров по модулю 2, трехвходового элемента ИЛИ-НЕ, последовательного регистра, дешифратора. Выходы первого, второго и третьего сумматоров по модулю 2 соединены соответственно с первым вторым и третьим входами трехвходового элемента ИЛИ-НЕ, выход которого подключен к информационному входу последовательного регистра. Выходы последовательного регистра от первого до 2n-го соединены с соответствующими входами дешифратора. Выход дешифратора является управляющим выходом блока управления. Управляющий вход последовательного регистра является управляющим входом блока управления. Первые входы первого, второго и третьего сумматоров по модулю 2 являются соответственно первым, вторым и третьим информационными входами блока управления. Вторые входы первого, второго и третьего сумматоров по модулю 2 являются соответственно четвертым, пятым и шестым информационными входами блока управления.

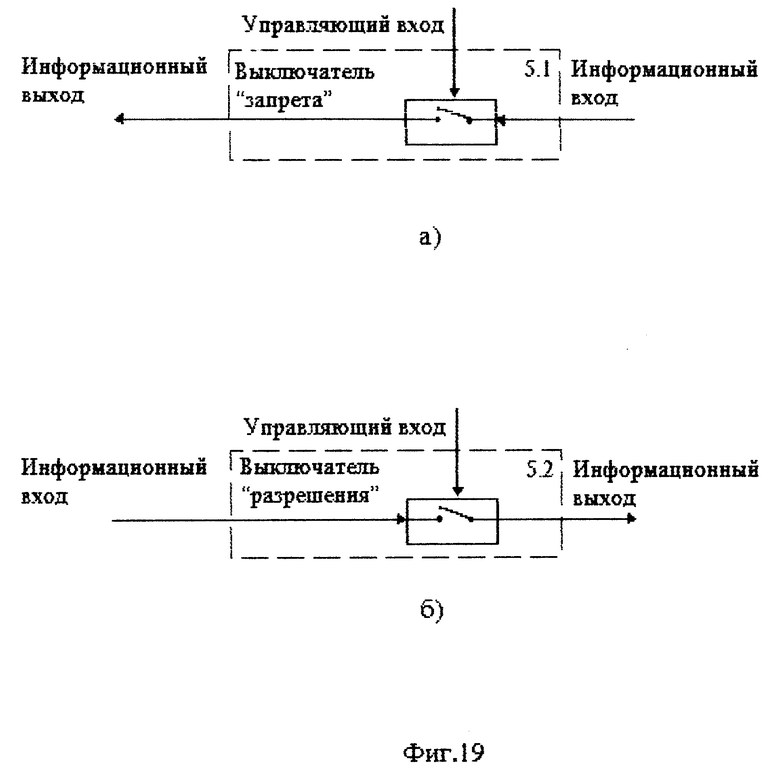

Первый коммутатор состоит из первого, второго и третьего выключателей "запрета" и первого, второго, третьего, четвертого, пятого и шестого выключателей "разрешения". Управляющие входы первого, второго и третьего выключателей "запрета" и первого, второго, третьего, четвертого, пятого и шестого выключателей "разрешения" соединены с управляющим входом первого коммутатора. Первый информационный вход первого коммутатора соединен со входом первого выключателя "разрешения", выход которого соединен с первым информационным выходом первого коммутатора. Второй информационный вход первого коммутатора соединен со входом третьего выключателя "разрешения", выход которого соединен со вторым информационным выходом первого коммутатора. Третий информационный вход первого коммутатора соединен со входом пятого выключателя "разрешения", выход которого соединен с третьим информационным выходом первого коммутатора. Четвертый информационный вход первого коммутатора соединен со входом первого выключателя "запрета", выход которого подключен к первому информационному выходу первого коммутатора и соединен со входом второго выключателя "разрешения", выход которого подключен к четвертому информационному выходу первого коммутатора. Пятый информационный вход первого коммутатора соединен со входом второго выключателя "запрета", выход которого подключен ко второму информационному выходу первого коммутатора и соединен со входом четвертого выключателя "разрешения", выход которого подключен к пятому информационному выходу первого коммутатора. Шестой информационный вход первого коммутатора соединен со входом третьего выключателя "запрета", выход которого подключен к третьему информационному выходу первого коммутатора и соединен со входом шестого выключателя "разрешения", выход которого подключен к шестому информационному выходу первого коммутатора.

Второй коммутатор состоит из первого, второго и третьего выключателей "запрета" и первого, второго и третьего выключателей "разрешения". Управляющие входы первого, второго и третьего выключателей "запрета" и первого, второго и третьего выключателей "разрешения" соединены с управляющим входом второго коммутатора. Первый информационный вход второго коммутатора соединен со входом первого выключателя "запрета", выход которого соединен с первым информационным выходом второго коммутатора. Второй информационный вход второго коммутатора соединен со входом второго выключателя "запрета", выход которого соединен со вторым информационным выходом второго коммутатора. Третий информационный вход второго коммутатора соединен со входом третьего выключателя "запрета", выход которого соединен с третьим информационным выходом второго коммутатора. Четвертый информационный вход второго коммутатора соединен со входом первого выключателя "разрешения", выход которого соединен с первым информационным выходом второго коммутатора. Пятый информационный вход второго коммутатора соединен со входом второго выключателя "разрешения", выход которого соединен со вторым информационным выходом второго коммутатора. Шестой информационный вход второго коммутатора соединен со входом третьего выключателя "разрешения", выход которого соединен с третьим информационным выходом второго коммутатора.

Указанная новая совокупность признаков заявленного устройства синхронизации M-последовательности с повышенной сложностью за счет применения псевдослучайных последовательностей повышенной сложности, корректировки значений предварительно заданных элементов сигнала без предварительного квантования в аналоговом виде, использования рекуррентных свойств М-последовательности по предсказанию очередного элемента сигнала на основе ранее принятых элементов сигнала позволяет уменьшить время синхронизации, повысить вероятность правильного приема сложных сигналов, а также повышает структурную скрытность синхропоследовательности и помехозащищенности в условиях воздействия преднамеренных помех.

Проведенный заявителем анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественными всем признакам заявленных способа и устройства синхронизации, отсутствуют, что указывает на соответствие заявленных изобретений условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипов признаками каждого заявленного изобретения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками каждого из заявленных изобретений на достижение указанного технического результата. Следовательно, каждое из заявленных изобретений соответствует условию патентоспособности "изобретательский уровень".

Заявленные объекты изобретения поясняются чертежами, на которых показаны:

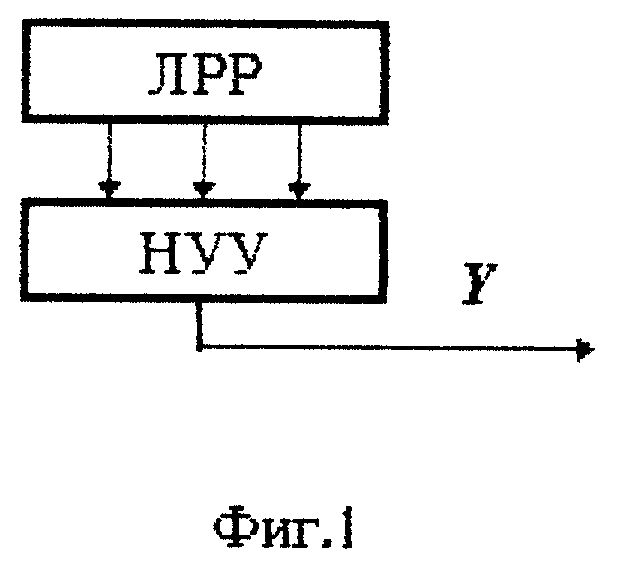

- фиг.1 - структура генератора ПСП ПС;

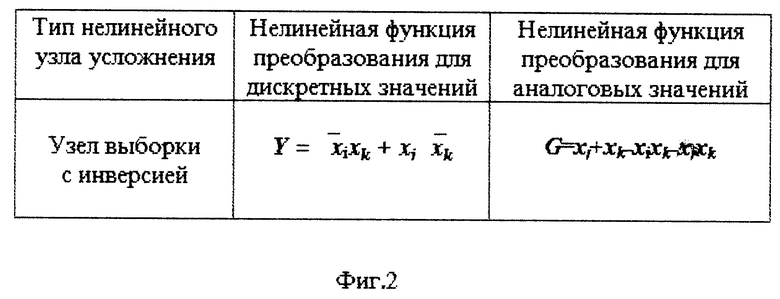

- фиг.2 - нелинейная функция преобразования для дискретных и аналоговых величин;

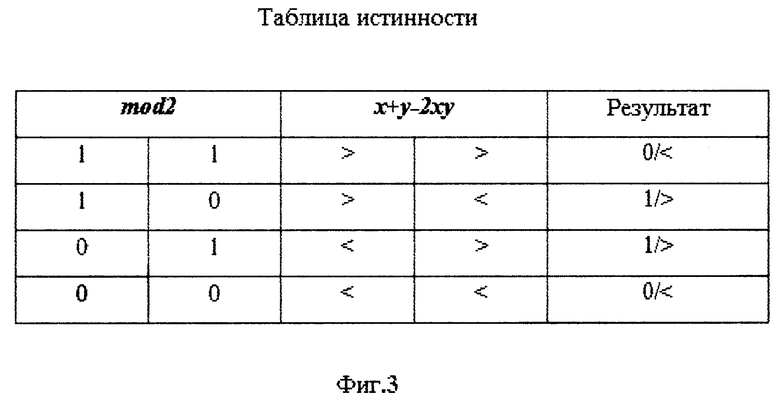

- фиг. 3 - таблицы истинности сумматора по модулю 2 и замещающей аналоговой функции;

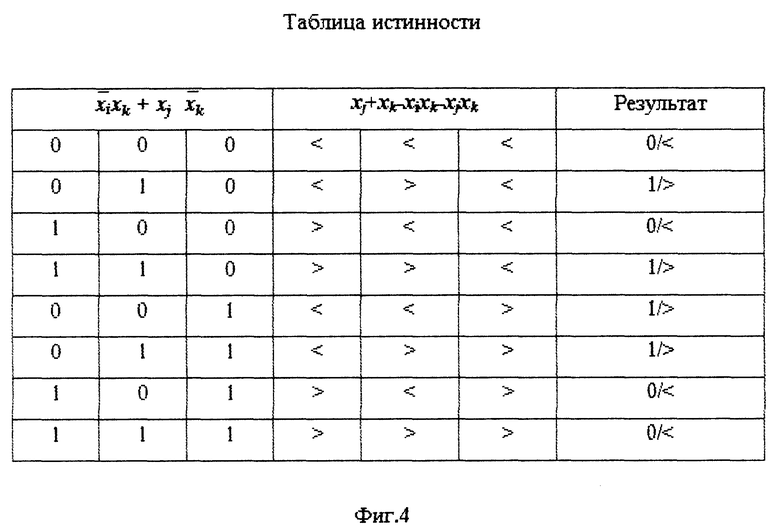

- фиг.4 - таблицы истинности дискретной и аналоговой нелинейных функций;

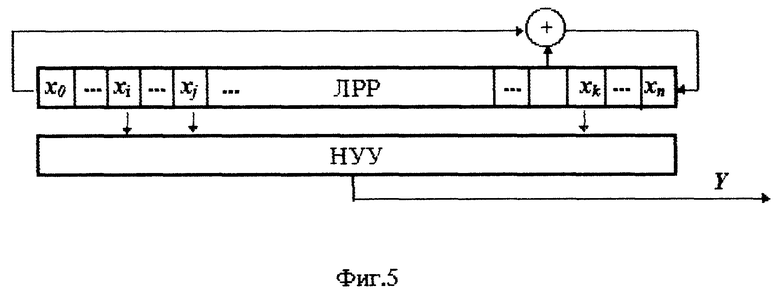

- фиг. 5 - вариант использования заданных значений для формирования ПСП ПС;

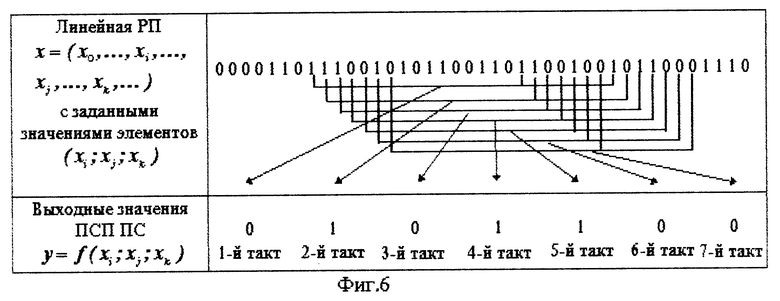

- фиг. 6 - процесс формирования ПСП ПС на передающей стороне;

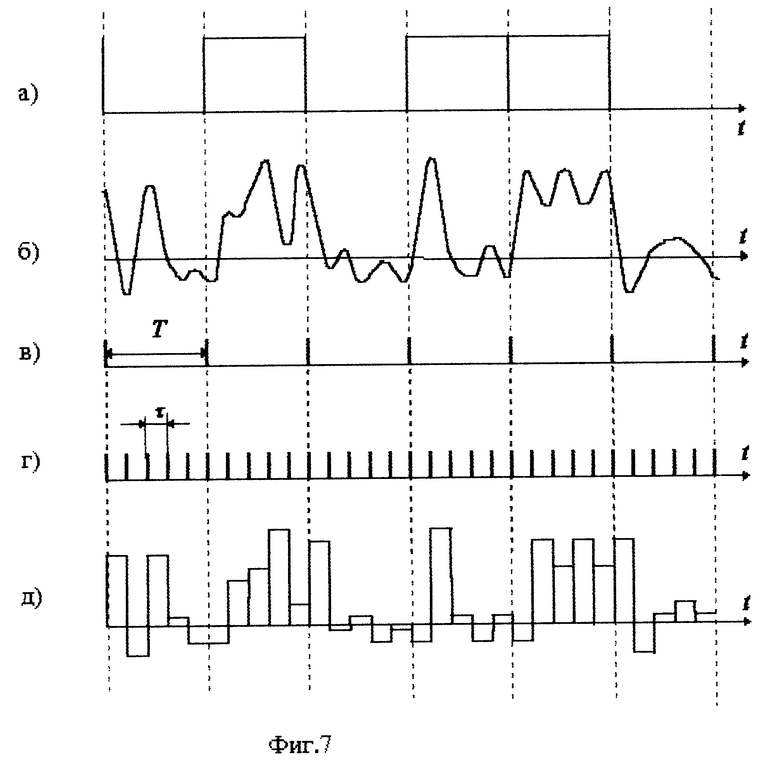

- фиг.7 - осциллограммы, поясняющие суть предлагаемого способа;

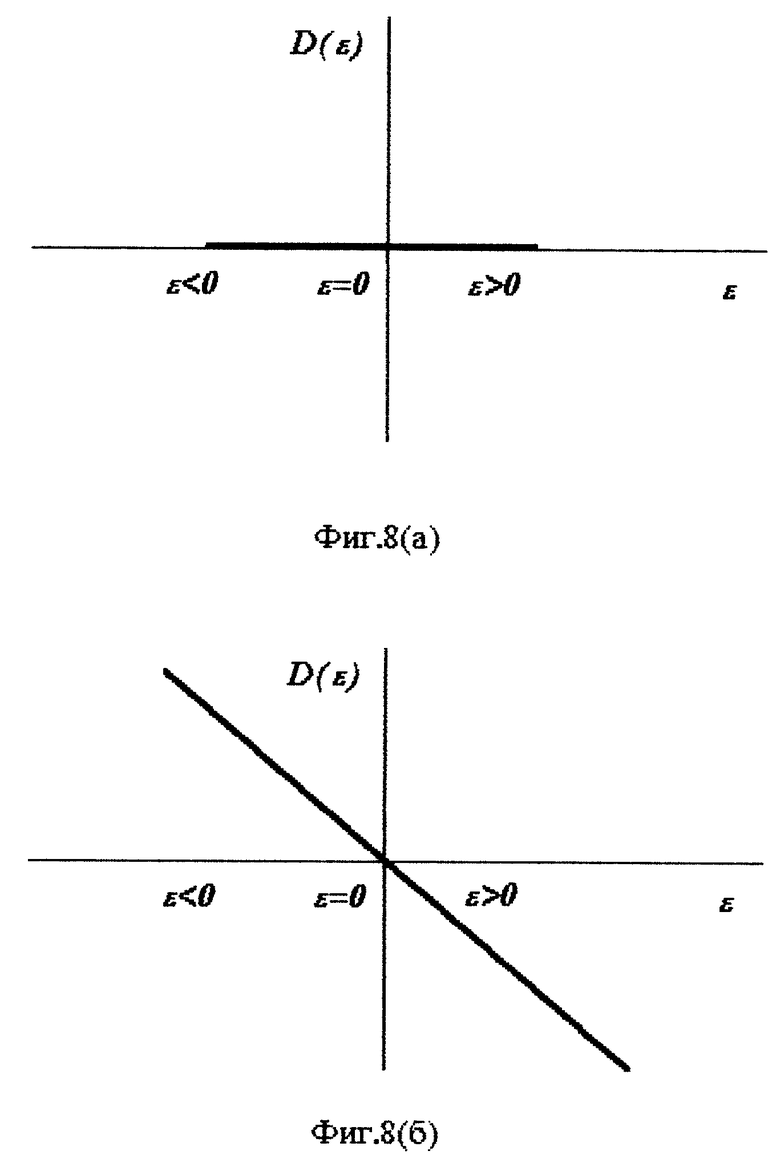

- фиг. 8 - дискриминационные характеристики;

- фиг. 9 - осциллограммы, поясняющие суть предлагаемого способа;

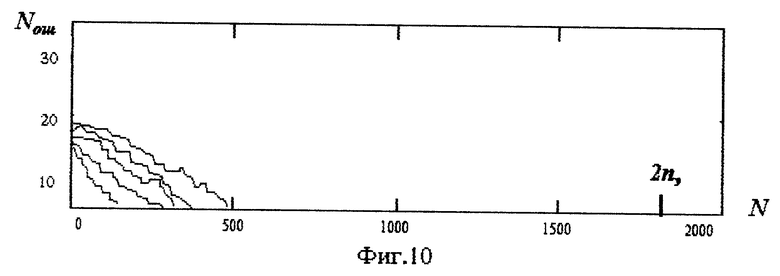

- фиг. 10 - график зависимости количества ошибок при определении значений элементов ПСП от такта обработки;

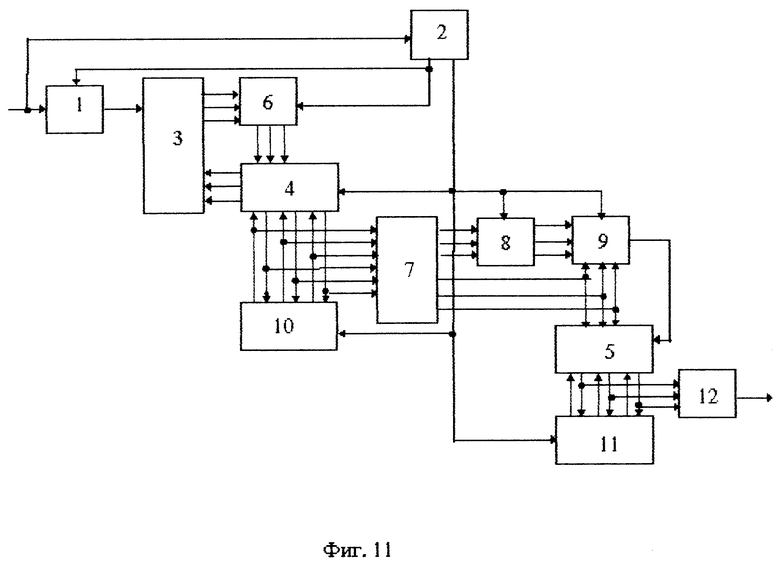

- фиг. 11 - структурная схема устройства синхронизации М-последовательности с повышенной сложностью;

- фиг. 12 - схема выделителя тактовой частоты;

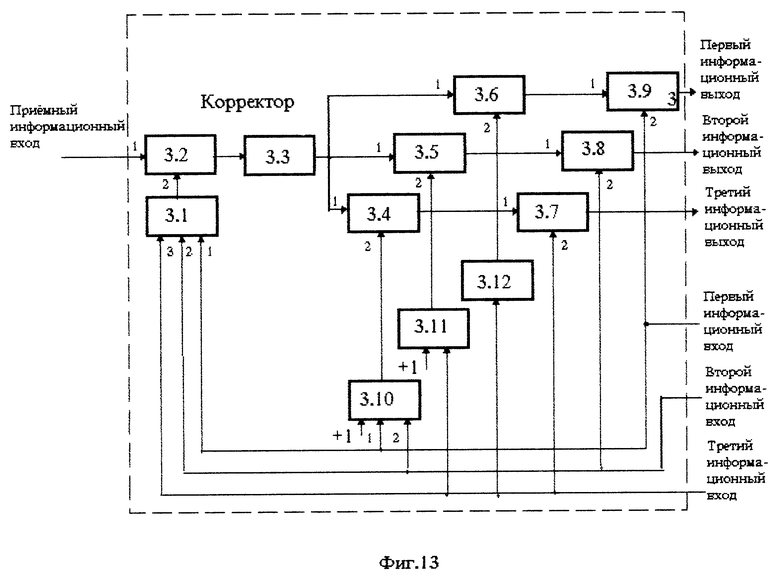

- фиг. 13 - схема корректора;

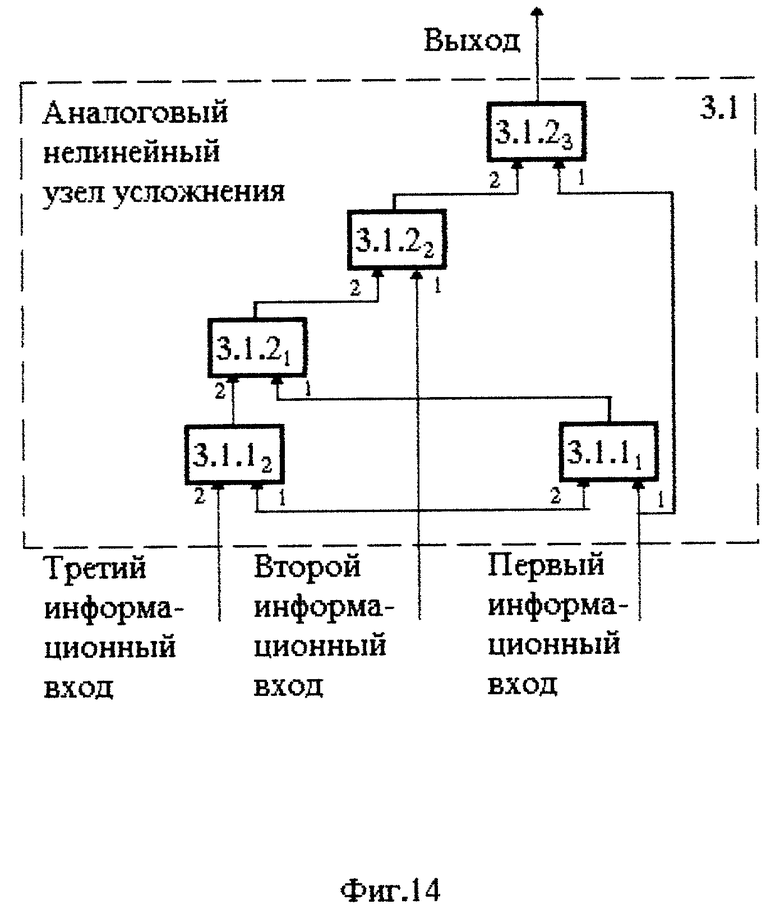

- фиг. 14 - схема аналогового нелинейного узла усложнения;

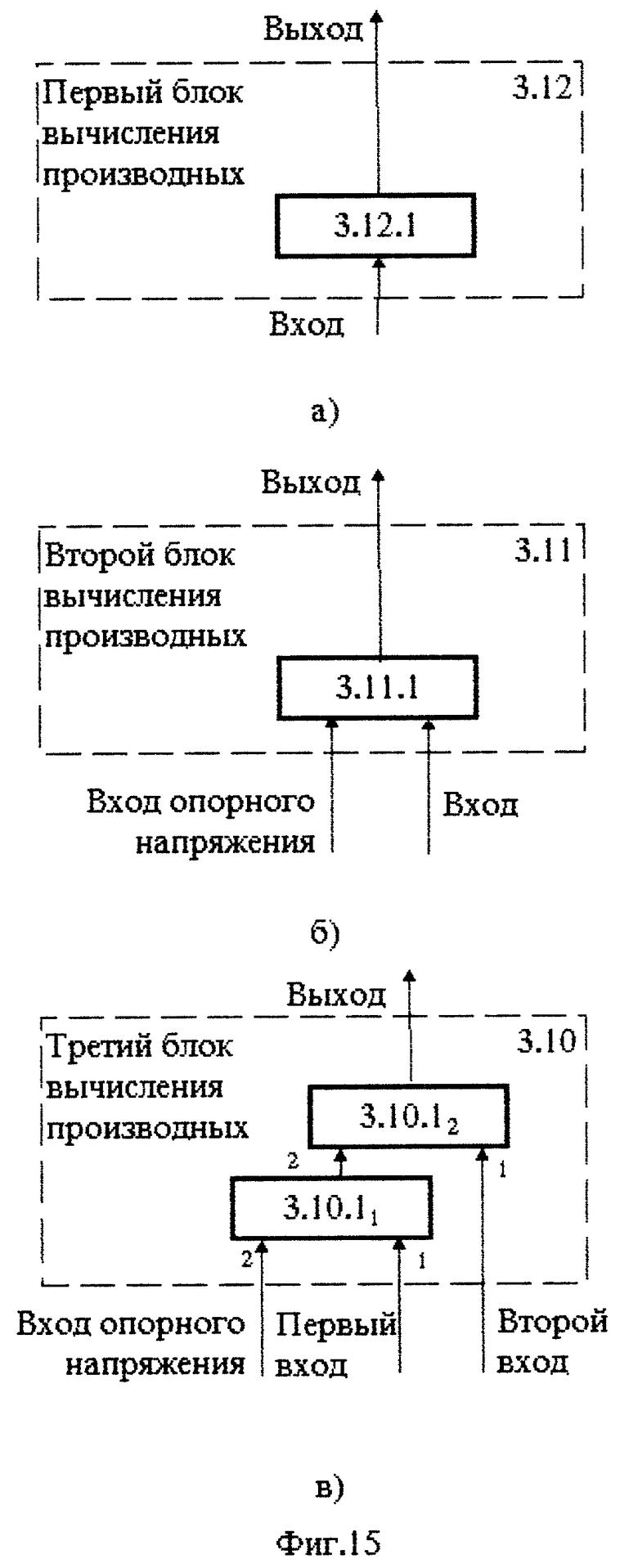

- фиг. 15 - схемы первого, второго и третьего блоков вычисления производных;

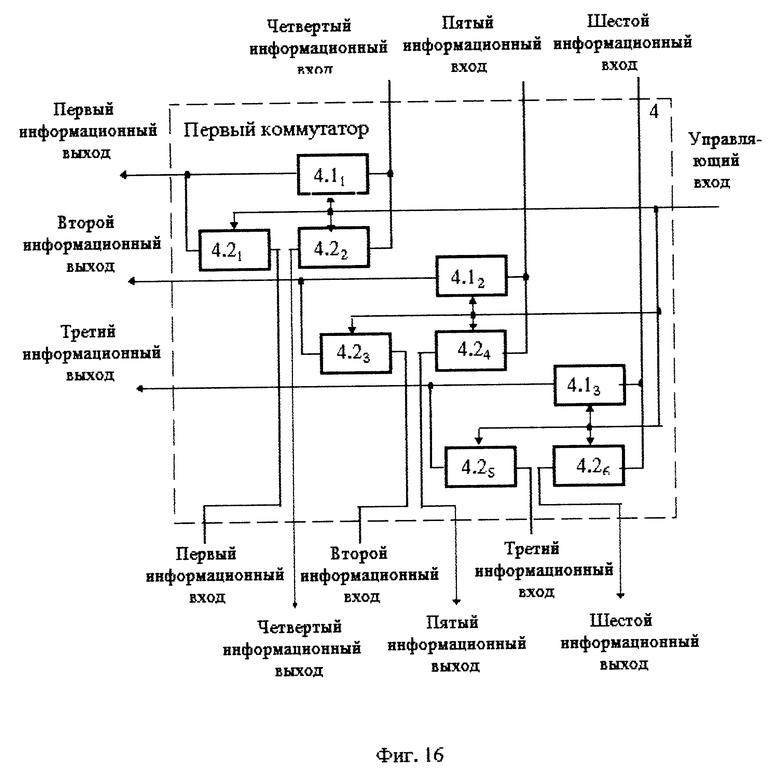

- фиг. 16 - схема первого коммутатора;

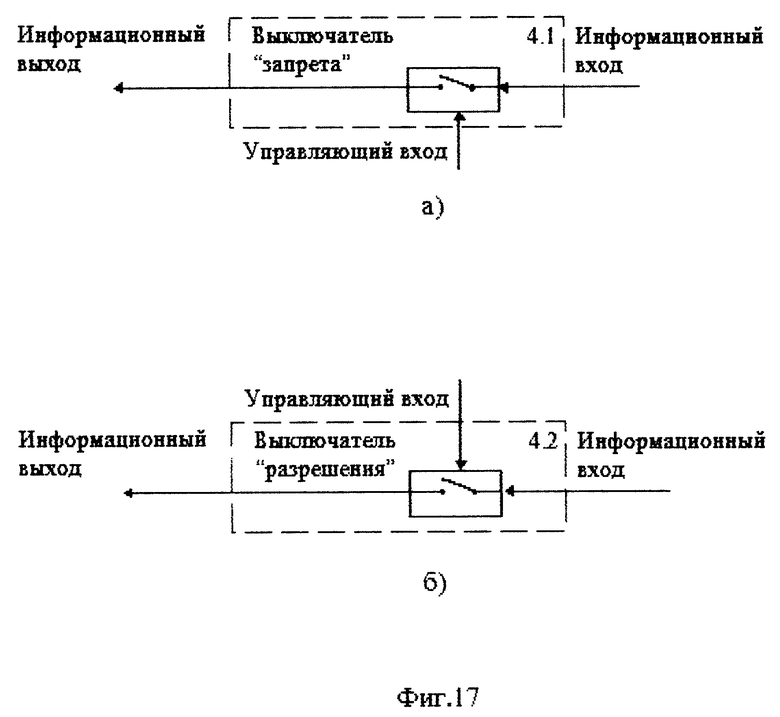

- фиг. 17 - схемы выключателей "запрета" и "разрешения";

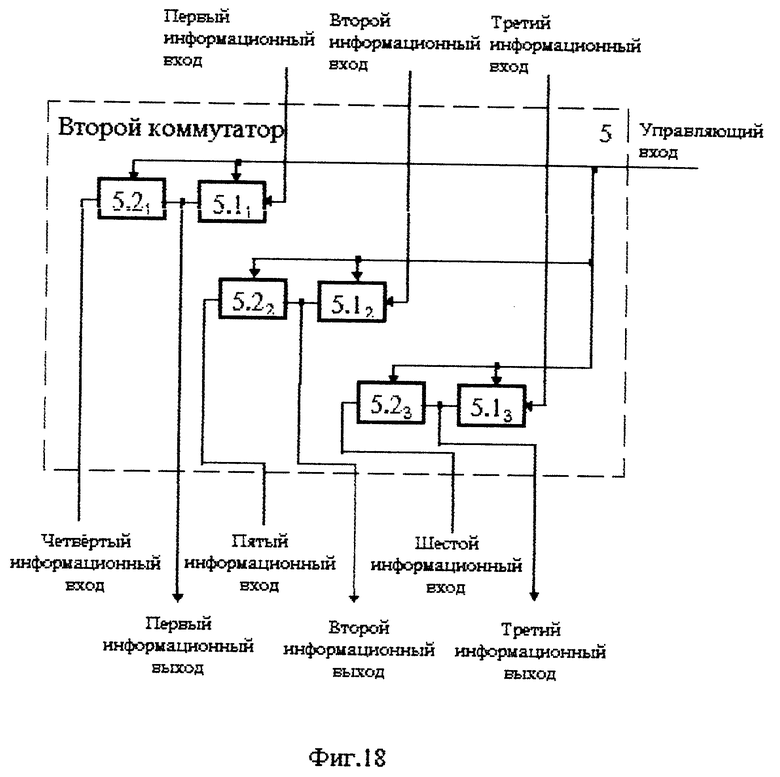

- фиг. 18 - схема второго коммутатора;

- фиг. 19 - схемы выключателей "запрета" и "разрешения";

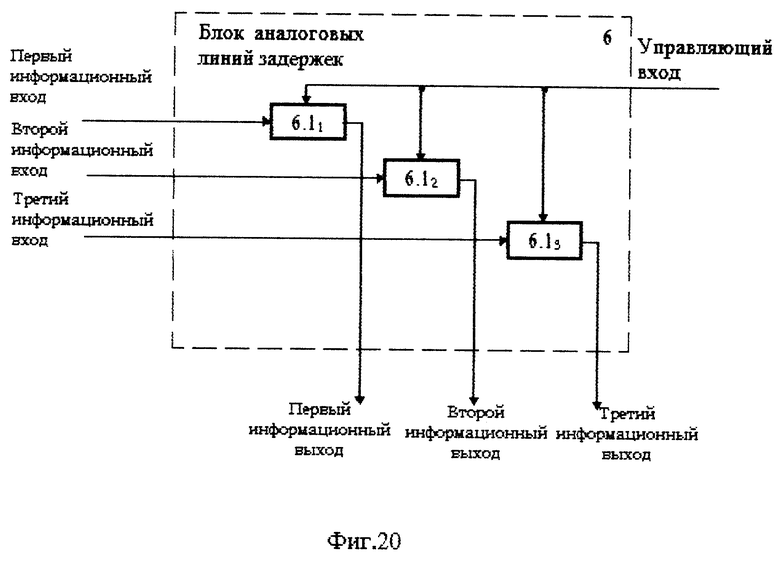

- фиг. 20 - схема блока аналоговых линий задержек;

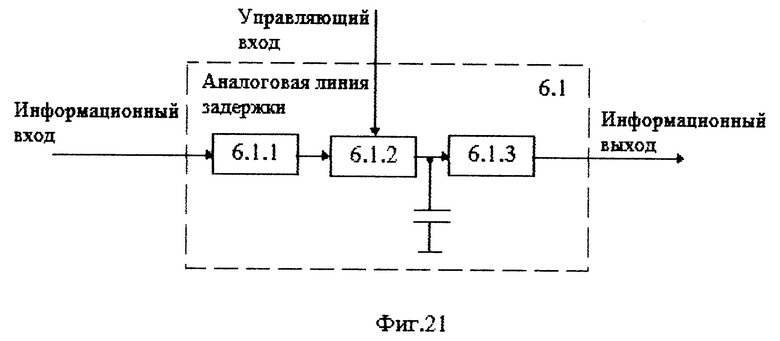

- фиг. 21 - схема аналоговой линии задержки;

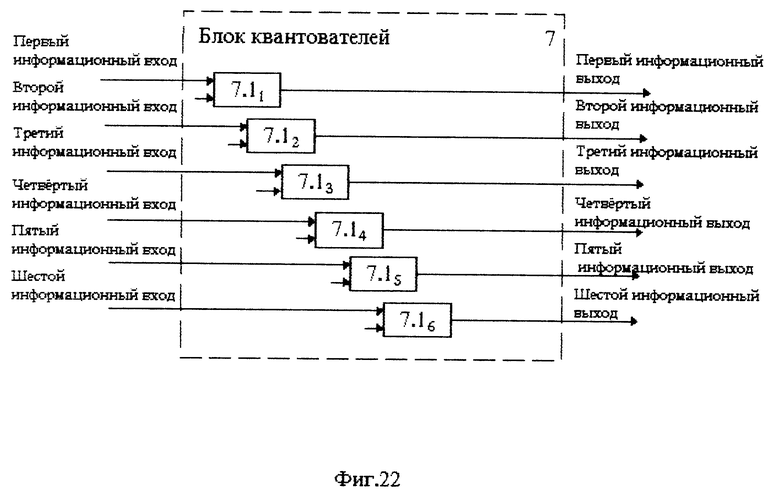

- фиг. 22 - схема блока квантователей;

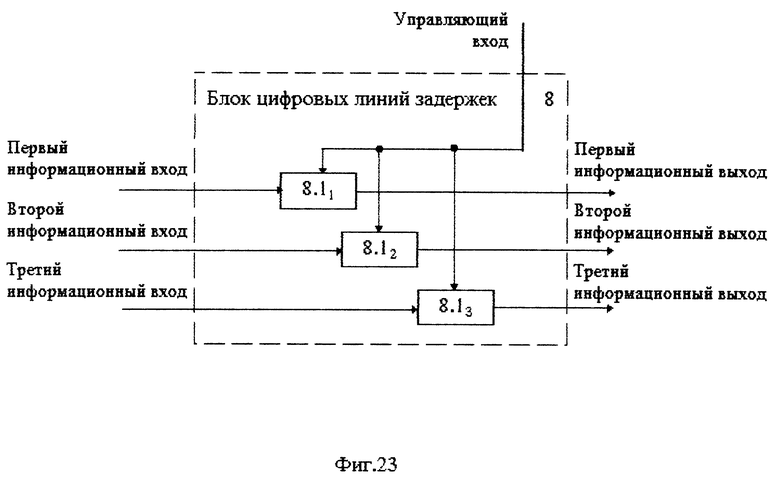

- фиг. 23 - схема блока цифровых линий задержек;

- фиг. 24 - схема блока управления;

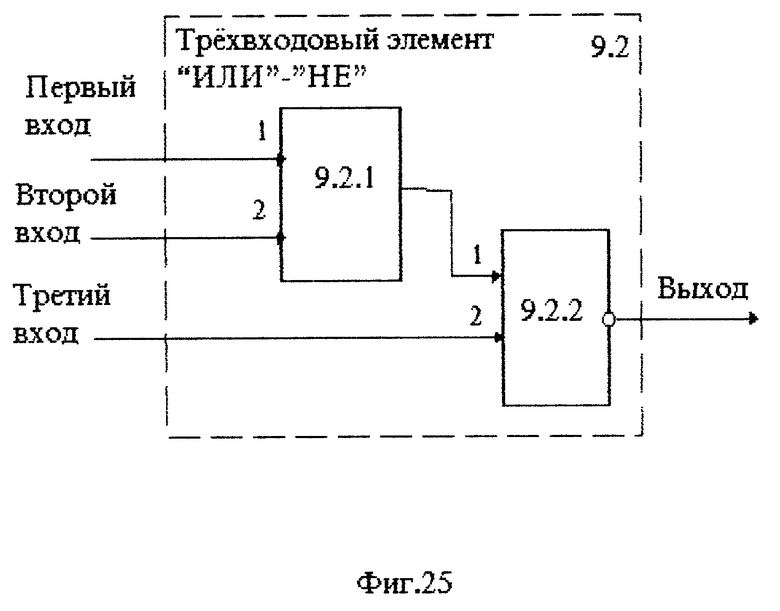

- фиг. 25 - схема трехвходового элемента ИЛИ-НЕ;

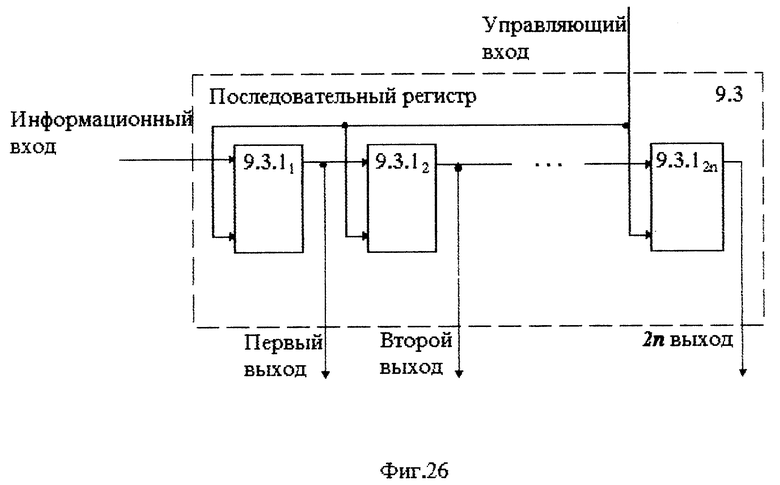

- фиг. 26 - схема последовательного регистра;

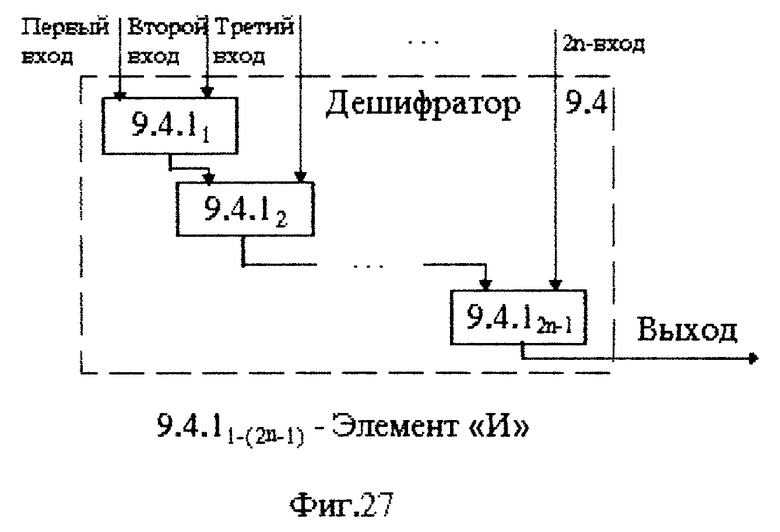

- фиг. 27 - схема дешифратора;

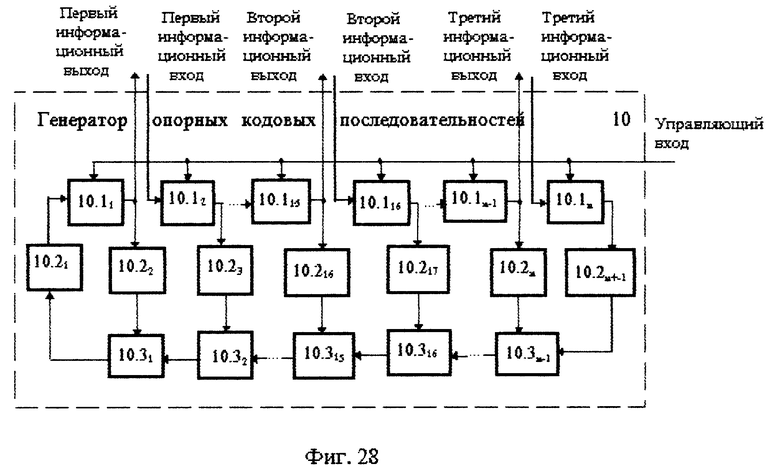

- фиг. 28 - схема генератора опорных кодовых последовательностей;

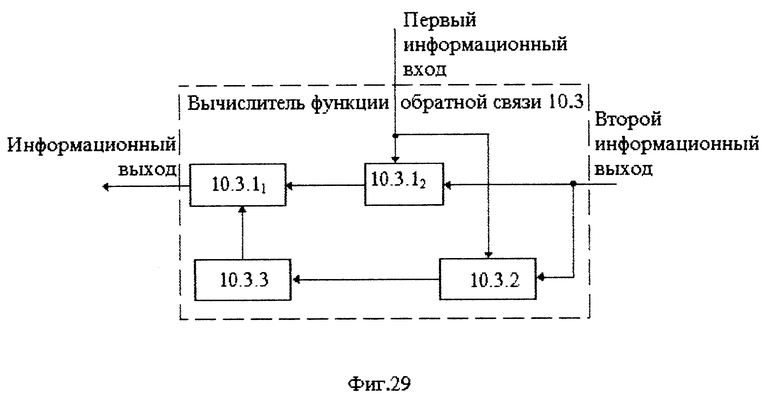

- фиг. 29 - схема вычислителя функции обратной связи;

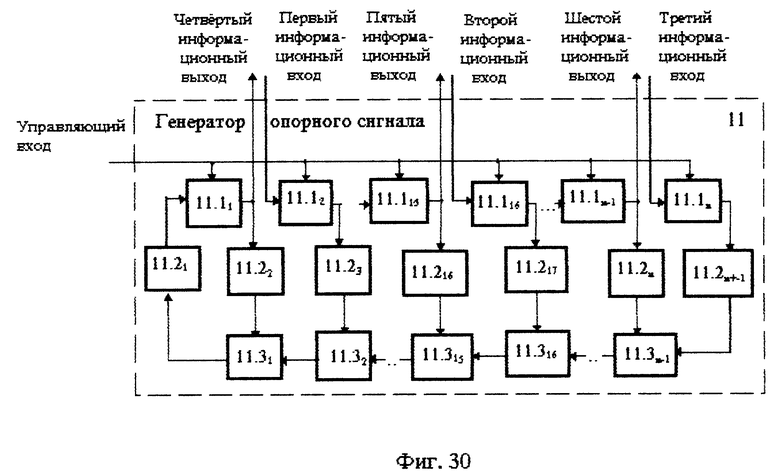

- фиг. 30 - схема генератора опорного сигнала;

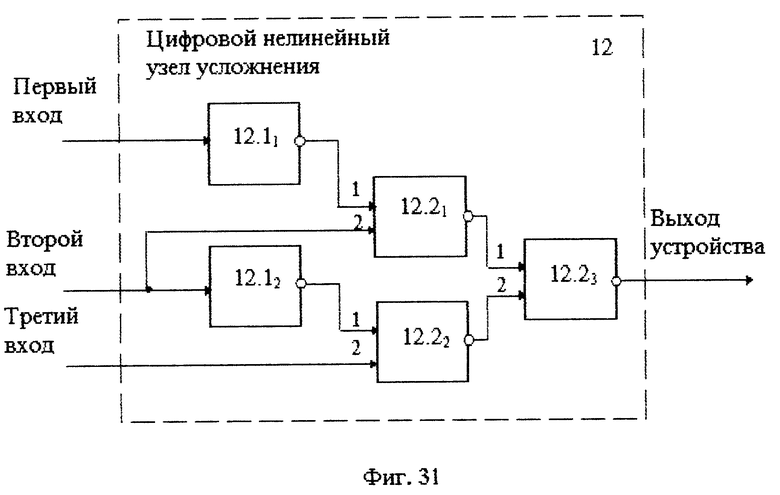

- фиг. 31 - схема цифрового нелинейного узла усложнения.

Реализация заявленного способа синхронизации M-последовательности с повышенной сложностью заключается в следующем. При использовании сложных сигналов большое значение имеет частотно-временное согласование параметров. Процесс синхронизации может занимать достаточно большое время в зависимости от периода используемых ПСП и их корреляционных свойств. Для формирования сложных сигналов широко применяют M-последовательности (последовательности Хаффмана, двоичные линейные рекуррентные последовательности максимальной длины), являющиеся по своей сути псевдослучайными последовательностями. Рекуррентное правило формирования M-последовательности можно представить в виде рекуррентной формулы:

где dj - j-тый элемент М-последовательности, образуемый сложением по модулю 2 некоторого числа предшествующих элементов, хранящихся в регистре, а именно тех из них, коэффициенты (ai) при которых равны 1.

Однако период М-последовательности, равный L=2n-1, где n - порядок порождающего полинома, может оказаться по времени больше, чем время сеанса связи, что значительно осложняет процесс установления синхронизации и соответственно значительно увеличивает время установления синхронизации M-последовательности, кроме того, структуру любой ПСП легко вскрыть по 2n смежным элементам ПСП по алгоритму Берлекэмпа-Месси, описанного в статье: J.L. Massey "Shift register syntheses and BCH decoding. IEEE Trans. Inform. Theory, pp. 122-127, 1969, Vol 15, N1. Следовательно, во избежание вскрытия структуры М-последовательности и постановки оптимизированных помех сигналам синхронизации, необходимо использовать псевдослучайные последовательности повышенной сложности, например, образованные путем нелинейного усложнения структуры M-последовательности нелинейным узлом усложнения (НУУ). Структура генератора ПСП ПС представлена на фиг. 1.

Линейный рекуррентный регистр (ЛРР) представляет собой цифровой регистр сдвига с обратными связями. Подобные регистры оперируют нулями и единицами, а в качестве преобразователя сигнала в регистре сдвига с обратными связями используют сумматоры по модулю 2.

В качестве НУУ целесообразно применять те из них, которые не ухудшают баланс выходной последовательности, например узел выборки с инверсией.

Чтобы избежать дополнительных искажений, ПСП ПС формируют в аналоговом виде, для чего операцию суммирования по модулю 2 двух переменных x и y заменяют выражением x+y-2xy, а дискретную функцию нелинейного преобразования заменяют соответствующей аналоговой функцией нелинейного преобразования, например, как показано на фиг.2, где значения xi, xj и xk считываются с заданных ячеек генератора ПСП. Таблица истинности операции суммирования по модулю 2 и соответствующего аналогового выражения представлена на фиг.3, а таблица истинности дискретного и соответствующего ей аналогового нелинейного преобразования представлена на фиг.4.

Для формирования аналоговой ПСП в качестве ее элементов могут использоваться любые ненулевые значения x и y в пределах от 0 до 1. В этом случае таблицы истинности дискретных и аналоговых значений совпадают.

Схема варианта структуры генератора ПСП ПС, представленная на фиг.1, позволяет достичь высокой структурной и эквивалентной линейной сложности, обеспечивающей непереборность и большую вычислительную сложность определения состояния ЛРР.

В качестве заданных значений используют ненулевые значения, считанные из произвольных, не повторяющихся ячеек ЛРР. Пример использования заданных значений для формирования ПСП ПС показан на фиг.5.

Применение данной схемы позволяет достичь роста эквивалентной линейной сложности согласно формуле n3=n(n-1). Так, например, при n=31 n3=930, а 2n3= 1860.

Процесс формирования ПСП ПС на передающей стороне представлен на фиг.6. Здесь выходная ПСП в виде M-последовательности регистра, построенного на основе примитивного тринома 31-й степени (n=31), усложнена НУУ в виде узла выборки с инверсией. При этом функция нелинейного преобразования для дискретных значений заменяется соответствующей ей аналоговой, как представлено на фиг.2.

Отрезок ПСП ПС на передающей стороне имеет вид, представленный на фиг. 7(а). В процессе передачи сигналы искажаются под воздействием шумов и помех. На приемной стороне искаженный сигнал имеет вид, например, как показано на фиг.7(б).

Из принимаемой смеси сигнала и шума с помощью известных способов выделяют тактовую частоту (Ft). Известные способы выделения тактовой частоты описаны, например, в книге: Е.М. Мартынов "Синхронизация в системах передачи дискретных сообщений". -М.: Связь. 1972, стр. 107. Стробирующие импульсы с тактовой частотой информационных сигналов показаны на фиг.7(в). Период следования импульсов с тактовой частотой равен T=1/Ft.

Используя известные способы деления частоты, получают частоту, в k раз превышающую тактовую fd=kFt, где k - количество дискретизированных отсчетов на длительности одного информационного элемента сигнала. Значение k выбирают в пределах от 2 до 10, так как при k=1 получают вырожденный случай и эффекта улучшения оценивания не наблюдается, при k>10 значительно увеличивается время корректировки сигнала, а точность оценивания практически не увеличивается. Известные способы деления частоты описаны, например, в книге: М.Л.Лейнов, В.С.Качалуба, А.В.Рыжков "Цифровые делители частоты на логических элементах". -М. : Энергия. 1975, стр.93. Стробирующие импульсы с частотой, в k раз превышающей тактовую, показаны на фиг.7(г). Период следования импульсов с частотой, в k раз превышающей тактовую, равен τ = 1/fd.

С целью избежания внесения дополнительных искажений принимаемый сигнал на входе демодулятора не квантуют на два уровня, а дискретизируют с частотой fd. Известные способы дискретизации сигналов описаны, например, в книге: Ж. Маркюс. Дискретизация и квантование". - М.: Энергия. 1969, стр.45. Аналоговые дискретизированные отсчеты принятого сигнала показаны на фиг.7(д). После дискретизации каждый дискретизированный отсчет ПСП ПС поступает на информационный вход корректора, где вырабатываются корректирующие сигналы для каждого значения заданного элемента опорной кодовой последовательности.

О возможности осуществления корректировки значений заданных элементов ОКП, хранящихся в ячейках ЛРР в аналоговом виде, по принимаемому ДО ПСП ПС свидетельствует наличие дискриминационной характеристики, представленной на фиг.8(а) и фиг.8(б), представляющей собой зависимость корректирующего напряжения D(ε) от расстройки (ε) значения заданного элемента ОКП от истинного значения элемента принимаемой ПСП ПС. Если дискриминационная характеристика равна нулю для любых значений расстройки, то осуществить корректировку сигнала невозможно из-за неоднозначности, вводимой нелинейностью. Пример "нулевой" дискриминационной характеристики показан на фиг.8(а). Если дискриминационная характеристика не равна нулю для любых значений расстройки и имеет вид как показано на фиг.8(б), то осуществить корректировку сигнала возможно путем формирования соответствующего корректирующего воздействия.

На фиг. 8(в) представлены дискриминационные характеристики, построенные для значений заданных элементов ОКП, показывающие, каким образом осуществляется подстройка на каждом такте. Если подстройка не осуществляется, то происходит перезапись предыдущих значений заданных элементов ОКП.

Хотя из фигуры 8(в) видно, что количество "нулевых" и "ненулевых" дискриминационных характеристик примерно одинаково, но в среднем произвести корректировку сигнала возможно.

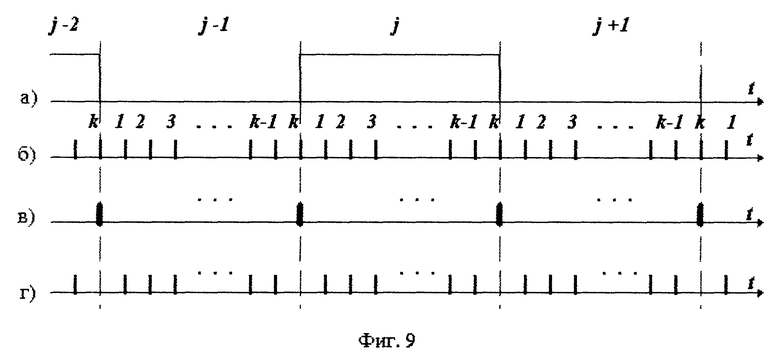

С целью наиболее точной корректировки искаженного информационного сигнала различают обработку при смене тактовых интервалов информационного сигнала и внутри тактовых интервалов информационного сигнала. Последовательность информационных сигналов показана на фиг.9(а). Частота дискретизации в k раз выше тактовой частоты информационных сигналов показана на фиг.9(б).

В моменты смены тактовых интервалов на 1-м до ПСП ПС для значений ОКП формируют откорректированные значения заданных элементов ОКП. Моменты смены тактовых интервалов показаны на фиг.9(в). Для формирования корректирующих сигналов для значений заданных элементов ОКП на 1-м ДО ПСП ПС используют значение функции нелинейного преобразования от значений заданных элементов ОКП и производные функции нелинейного преобразования от значений заданных элементов ОКП, которые являются преобразованными по рекуррентному правилу формирования М-последовательности, откорректированными значениями информационного сигнала, принятого и откорректированного на (n-1) тактов ранее. С этой целью из 1-го ДО принимаемой ПСП ПС вычитают значение функции нелинейного преобразования от значений заданных элементов ОКП и умножают на заданный весовой коэффициент C. По физической сущности умножению сигнала на постоянный множитель соответствует усиление сигнала. Известные способы усиления сигналов описаны, например, в книге: А.А.Сикарев, О.Н.Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М.: Радио и связь. 1983, стр. 184. Эксперименты показали, что коэффициент C целесообразно выбирать в пределах от 0 до 1. При этом в качестве значений заданных элементов ОКП для первоначального установления синхронизации могут быть использованы произвольные ненулевые значения элементов ОКП в пределах от 0 до 1 или значения, оставшиеся от прошлого сеанса связи. После этого осуществляется корректировка значений заданных элементов ОКП. В каждой ветви корректировки сигнал умножают на значения соответствующих производных аналоговой функции нелинейного преобразования от значений заданных элементов ОКП и суммируют с соответствующими значениями заданных элементов ОКП. Известные способы сложения сигналов описаны, например, в книге: А.А.Сикарев, О.Н.Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М. : Радио и связь. 1983, стр. 194. После этого откорректированные значения заданных элементов ОКП, полученные на 1-м ДО ПСП ПС, задерживают на время τ, равное длительности одного ДО. Способы задерживания сигналов известны и описаны, например, в книге: И.А.Цикин "Дискретно-аналоговая обработка сигналов". -М.: Радио и связь. 1982, стр. 19.

В моменты времени внутри тактовых интервалов формируют откорректированные значения заданных элементов ОКП из дискретизированных отсчетов принимаемой ПСП ПС, начиная со второго и до k-го. Моменты времени внутри тактовых интервалов показаны на фиг. 7(г).

Для формирования корректирующих сигналов для значений заданных элементов ОКП на 2-м ДО ПСП ПС и последующих до k-го используют значение аналоговой функции нелинейного преобразования и производные аналоговой функции нелинейного преобразования от откорректированных значений заданных элементов ОКП, полученных из предыдущего ДО принимаемой ПСП ПС. С этой целью, начиная со 2-го и до k-го ДО принимаемой ПСП ПС, вычитают значение аналоговой функции нелинейного преобразования от откорректированных значений заданных элементов ОКП, полученных из предыдущего ДО принимаемой ПСП ПС, и умножают на заданный весовой коэффициент C. По физической сущности умножению сигнала на постоянный множитель соответствует усиление сигнала. Известные способы усиления сигналов описаны, например, в книге: А.А.Сикарев, О.Н.Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М. : Радио и связь. 1983, стр. 184. Эксперименты показали, что коэффициент C целесообразно выбирать в пределах от 0 до 1. После этого осуществляется разделение на три ветви корректировки, где вырабатываются корректирующие сигналы для каждого откорректированного значения заданных элементов ОКП, полученных из предыдущего ДО принимаемой ПСП. В каждой ветви корректировки сигнал умножают на значения соответствующих производных аналоговой функции нелинейного преобразования от откорректированных значений заданных элементов ОКП, полученных из предыдущего ДО принимаемой ПСП ПС, в результате чего на выходе блока корректировки формируются корректирующие сигналы для откорректированных значений заданных элементов ОКП, полученных из предыдущего ДО принимаемой ПСП ПС. В дальнейшем, в каждой ветви корректирующие сигналы суммируются с соответствующими значениями откорректированных значений заданных элементов ОКП, полученных из предыдущего ДО принимаемой ПСП ПС. Известные способы сложения сигналов описаны, например, в книге: А.А.Сикарев, О.Н.Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М. : Радио и связь. 1983, стр. 194. После этого откорректированные значения заданных элементов ОКП, полученные на 2-м и до k-го ДО ПСП ПС, задерживают на время τ, равное длительности одного ДО. Способы задерживания сигналов известны и описаны, например, в книге: И.А.Цикин "Дискретно-аналоговая обработка сигналов". -М.: Радио и связь. 1982, стр. 19. Полученные из k-го ДО ПСП ПС откорректированные значения заданных элементов ОКП считаются откорректированными значениями элемента информационного сигнала в целом. Для оценки следующего элемента информационного сигнала все описанные выше операции повторяются.

Аналогично xi по принимаемым ДО ПСП ПС в соответствующих ветвях производится корректировка и xj, xk.

С целью определения правильности произведенной корректировки квантуют и задерживают на длительность элемента принимаемой ПСП ПС значения заданных элементов ОКП, а также откорректированные значения заданных элементов ОКП на k-м ДО принимаемой ПСП ПС и задержанные на длительность одного ДО принимаемой ПСП ПС. Способы задерживания сигналов известны и описаны, например, в книге: И. А. Цикин "Дискретно-аналоговая обработка сигналов". -М.: Радио и связь. 1982, стр. 19. В каждой ветви корректировки, на каждом такте суммируют по модулю 2 значения заданных элементов ОКП и откорректированные значения заданных элементов ОКП (определяется совпадение). Результаты суммирования по модулю 2 в каждой ветви обработки складываются арифметически, тем самым подсчитывается количество несовпадений начальных условий для корректировки и откорректированных значений. Наличие нуля свидетельствует о совпадении начальных условий для корректировки и откорректированных значений заданных элементов ОКП (xi, xj, xk). Если в результате суммирования на протяжении 2n тактов ПСП ПС начальные условия для корректировки и откорректированные значения заданных элементов ОКП совпадают, то формируется управляющий сигнал на формирование ПСП из откорректированных значений заданных элементов ОКП на k-х ДО принимаемой ПСП ПС и задержанных на длительность одного ДО принимаемой ПСП ПС. Таким образом, сформированная ПСП будет синхронна с принимаемой последовательностью. Для формирования ПСП ПС, синхронной с принимаемой ПСП ПС, используется дискретная функция нелинейного преобразования.

При этом получение откорректированных значений заданных элементов ОКП по принимаемым ДО ПСП ПС, их преобразование по рекуррентному правилу формирования М-последовательности продолжается. Это позволит в дальнейшем получать более точную априорную информацию о значениях ДО принимаемой ПСП ПС для сокращения времени для возможного повторного вхождения в синхронизацию при ее нарушении.

Отличие данного способа от известных заключается в том, что не требуется многократная передача синхросигналов по каналу связи с последующей мажоритарной обработкой на приеме либо безошибочный прием зачетного отрезка рекуррентной последовательности, так как это приводит к увеличению времени вхождения в синхронизацию при отношениях сигнал/шум меньше единицы.

Результаты моделирования заявленного способа синхронизации М-последовательности с повышенной сложностью представлены на фиг. 10 в виде графиков зависимости количества ошибок при определении значений элементов ПСП от такта обработки для различных вариантов формирования ОКП. Исследования подтверждают, что определение значений ПСП происходит за время длительности, значительно меньшее 2n3, то есть обеспечивается уменьшение времени вхождения в синхронизацию при увеличении сложности M-последовательности.

Устройство синхронизации M-последовательности с повышенной сложностью, показанное на фиг. 11, состоит из дискретизатора 1, выделителя тактовой частоты 2, корректора 3, первого коммутатора 4, второго коммутатора 5, блока аналоговых линий задержек 6, блока квантователей 7, блока цифровых линий задержек 8, блока управления 9, генератора опорных кодовых последовательностей 10, генератора опорного сигнала 11, цифрового нелинейного узла усложнения 12. Приемный информационный вход дискретизатора 1 соединен со входом выделителя тактовой частоты 2 и является входом устройства. Первый управляющий выход выделителя тактовой частоты 2 соединен с управляющими входами первого коммутатора 4, блока цифровых линий задержек 8, блока управления 9, генератора опорных кодовых последовательностей 10, генератора опорного сигнала 11. Второй управляющий выход выделителя тактовой частоты 2 соединен с управляющими входами дискретизатора 1 и блока аналоговых линий задержек 6. Выход дискретизатора 1 подключен к приемному информационному входу корректора 3. Первый, второй и третий информационные входы корректора 3 подключены соответственно к первому, второму и третьему информационным выходам первого коммутатора 4. Первый, второй и третий информационные выходы корректора 3 подключены соответственно к первому, второму и третьему информационным входам блока аналоговых линий задержек б, выходы которого соединены соответственно с четвертым, пятым и шестым информационными входами первого коммутатора 4. Первый, второй и третий выходы генератора опорных кодовых последовательностей 10 подключены соответственно к первому, второму и третьему информационным входам первого коммутатора 4 и к первому, второму и третьему входам блока квантователей 7. Четвертый, пятый и шестой информационные выходы первого коммутатора 4 подключены соответственно к четвертому, пятому и шестому входам блока квантователей 7. Первый, второй и третий выходы блока квантователей 7 соединены соответственно с первым, вторым и третьим входами блока цифровых линий задержек 8, выходы которого подключены соответственно к первому, второму и третьему информационным входам блока управления 9. Управляющий выход блока управления 9 соединен с управляющим входом второго коммутатора 5. Четвертый, пятый и шестой выходы блока квантователей 7 соединены соответственно с четвертым, пятым и шестым информационными входами блока управления 9 и соответственно с первым, вторым и третьим входами второго коммутатора 5. Первый, второй и третий выходы генератора опорного сигнала 11 подключены соответственно к четвертому, пятому и шестому входам второго коммутатора 5. Первый, второй и третий выходы второго коммутатора 5 соединены соответственно с первым, вторым и третьим информационными входами генератора опорного сигнала 11 и соединены соответственно с первым, вторым и третьим входами цифрового нелинейного узла усложнения 12, выход которого является выходом устройства.

Дискретизатор 1 предназначен для дискретизации информационного сигнала с частотой, в k раз превышающей тактовую частоту информационных сигналов (fd= k•Ft), где k - количество необходимых дискретизированных отсчетов на длительности одного элемента принимаемой ПСП ПС. По физической сущности дискретизатор 1 является прерывателем. Схемы прерывателей, которые можно использовать в качестве дискретизатора 1, известны и приведены, например, в книге: Ж.Маркюс "Дискретизация и квантование". - М.: Энергия. 1969, стр.52, рис.2.11.

Выделитель тактовой частоты 2 предназначен для выделения тактовой частоты (Ft) и частоты дискретизации (fd) из принимаемой ПСП ПС. По физической сущности схема выделителя тактовой частоты 2 соответствует схеме фазового дискриминатора. Схеме фазового дискриминатора, который может быть использован в устройстве синхронизации М-последовательности, известна и приведена, например, в книге Е.М. Мартынова "Синхронизация в системах передачи дискретных сообщений". - М. : Связь. 1972, стр. 108, рис.6.16. С учетом особенностей заявленного устройства схема выделителя тактовой частоты 2 может быть реализована как показано на фиг. 12. Выделитель тактовой частоты 2 состоит из задающего генератора 2.1, управляющего элемента 2.2, делителя частоты 2.3, усредняющего устройства 2.4 и фазового дискриминатора 2.5. Информационный вход фазового дискриминатора 2.5 является информационным входом выделителя тактовой частоты 2. Первый и второй управляющие выходы фазового дискриминатора 2.5 соединены соответственно с первым и вторым управляющими входами усредняющего устройства 2.4, первый и второй управляющие выходы которого соединены соответственно с первым и вторым управляющими входами управляющего

элемента 2.2. Первый управляющий выход задающего генератора 2.1 соединен с третьим управляющим входом управляющего элемента 2.2, а второй управляющий выход задающего генератора 2.1 в параллель соединен с четвертым управляющим входом управляющего элемента 2.2 и с первым управляющим входом фазового дискриминатора 2.5. Управляющий выход управляющего элемента 2.2 соединен с управляющим входом делителя частоты 2.3 и является первым управляющим выходом выделителя тактовой частоты 2. Управляющий выход делителя частоты соединен со вторым управляющим входом фазового дискриминатора 2,5 и является вторым управляющим выходом выделителя тактовой частоты 2.

Корректор 3 предназначен для поучения откорректированных значений заданных элементов опорной кодовой последовательности, показан на фиг. 13, состоит из аналогового нелинейного узла усложнения 3.1, первого 3.9, второго 3.8, третьего 3.7 и четвертого 3.2 аналоговых сумматоров, умножителя на постоянный множитель 3.3, первого 3.6, второго 3.5 и третьего 3.4 аналоговых перемножителей и первого 3.12, второго 3.11 и третьего 3.10 блоков вычисления производных. Выход аналогового нелинейного узла усложнения 3.1 подключен ко второму информационному входу четвертого аналогового сумматора 3.2. Выход четвертого аналогового сумматора 3.2 соединен со входом умножителя на постоянный множитель 3.3, выход которого подключен к первым входам соответственно первого 3.6, второго 3.5 и третьего 3.4 аналоговых перемножителей. Вторые входы первого 3.6, второго 3.5 и третьего 3.4 аналоговых перемножителей соединены с выходами соответственно первого 3.12, второго 3.11 и третьего 3.10 блоков вычисления производных. Выходы первого 3.6, второго 3.5 и третьего 3.4 аналоговых перемножителей соединены соответственно с первыми входами первого 3.9, второго 3.8 и третьего 3.7 аналоговых сумматоров, выходы которых являются соответственно первым, вторым и третьим информационными выходами корректора 3. Первый вход аналогового нелинейного узла усложнения 3.1, соединенный с первым входом третьего блока вычисления производных 3.10, соединенный со вторым входом первого аналогового сумматора 3.9, является первым информационным входом корректора 3. Второй информационный вход аналогового нелинейного узла усложнения 3.1, соединенный со вторым входом третьего блока вычисления производных 3.10 и вторым входом второго аналогового сумматора 3.8, является вторым информационным входом корректора 3. Третий вход аналогового нелинейного узла усложнения 3.1, соединенный со входом второго блока вычисления производных 3.11, соединенный со входом первого блока вычисления производных 3.12, соединенный со вторым входом третьего аналогового сумматора 3.7, является третьим информационным входом корректора 3. Причем третий 3.10 и второй 3.11 блоки вычисления производных дополнительно снабжены входами опорного напряжения от источника опорного напряжения положительной полярности, структурная схема которого в устройстве не приведена.

Аналоговый нелинейный узел усложнения 3.1, предназначенный для получения значения функции нелинейного преобразования от аналоговых заданных значений элементов опорной кодовой последовательности, показанный на фиг. 14, состоит из аналоговых перемножителей 3.1.11-2 и аналоговых сумматоров 3.1.21-3. Выход аналогового перемножителя 3.1.11 соединен с первым входом аналогового сумматора 3.1.21, а выход аналогового перемножителя 3.1.12 соединен со вторым входом аналогового сумматора 3.1.21, выход которого подключен ко второму входу аналогового сумматора 3.1.22. Выход аналогового сумматора 3.1.22 подключен ко второму входу аналогового сумматора 3.1.23, выход которого является выходом аналогового нелинейного узла усложнения 3.1. Первый вход аналогового сумматора 3.1.23, соединенный с первым входом аналогового перемножителя 3.1.11, является первым информационным входом аналогового нелинейного узла усложнения 3.1. Второй вход аналогового перемножителя 3.1.11, соединенный с первым входом аналогового перемножителя 3.1.12 и первым входом аналогового сумматора 3.1.22, является вторым информационным входом аналогового нелинейного узла усложнения 3.1. Второй вход аналогового перемножителя 3.1.12 является третьим информационным входом аналогового нелинейного узла усложнения 3.1. Схемы аналоговых сумматоров 3.1.21-3, которые могут быть использованы в схеме аналогового нелинейного узла усложнения 3.1, известны и приведены, например, в книге: А.А. Сикарев, О.Н. Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М.: Радио и связь. 1983, стр. 194, рис.7.6. Схемы аналоговых перемножителей 3.1.11-2, которые могут быть использованы в схеме аналогового нелинейного узла усложнения 3.1, известны и приведены, например, в книге: А. А. Сикарев, О.Н. Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М. : Радио и связь. 1983, стр.200, рис.7.11.

Схемы аналоговых сумматоров 3.9, 3.8, 3.7, 3.2, которые могут быть использованы в корректоре 3, известны и приведены, например, в книге: А.А. Сикарев, О. Н. Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М.: Радио и связь. 1983, стр. 194, рис.7.6.

Схема умножителя на постоянный множитель 3.3 по физической сущности является неинвертирующими усилителями. Схемы неинвертирующих усилителей известны и приведены, например, в книге: Ю.А.Мячин "180 аналоговых микросхем (справочник)". -М.: издательство Патриот, МП Символ-Р и редакция журнала Радио, 1993, стр.7.

Схемы аналоговых перемножителей 3.4, 3.5, 3.6, которые могут быть использованы в схеме корректора 3, известны и приведены, например, в книге: А. А. Сикарев, О.Н. Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М.: Радио и связь. 1983, стр. 200, рис. 7.11.

Схемы первого 3.12, второго 3.11 и третьего 3.10 блоков вычисления производных приведены на фиг. 15 (а), (б), (в). Первый блок 3.12 вычисления производных состоит из инвертора 3.12.1, вход которого является входом первого блока вычисления производных 3.12. Выход инвертора 3.12.1 является выходом первого блока вычисления производных 3.12. Схемы инверторов известны и приведены, например, в книге: М.У Банк. "Аналоговые интегральные схемы в радиоаппаратуре". -М.: Радио и связь. 1981, стр. 15, рис.2.1. Второй блок 3.11 вычисления производных состоит из аналогового сумматора 3.11.1, первый вход которого является входом второго блока вычисления производных 3.11. Второй вход аналогового сумматора 3.11.1 является входом опорного напряжения. Выход аналогового сумматора 3.11.1 является выходом второго блока вычисления производных 3.11. Схема аналогового сумматора 3.11.1, которая может быть использована во втором блоке вычисления производных 3.11, известна и приведена, например, в книге: А.А. Сикарев, О.Н. Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М.: Радио и связь. 1983, стр. 194, рис.7.6. Третий блок 3.10 вычисления производных состоит из аналоговых сумматоров 3.10.11-2. Первый вход аналогового сумматора 3.10.11 является первым входом третьего блока вычисления производных 3.10. Второй вход аналогового сумматора 3.10.11 является входом опорного напряжения. Выход аналогового сумматора 3.10.11 является вторым входом аналогового сумматора 3.10.12. Первый вход аналогового сумматора 3.10.12 является вторым входом третьего блока вычисления производных 3.10. Выход аналогового сумматора 3.10.12 является выходом третьего блока вычисления производных 3.10. Схемы аналоговых сумматоров 3.10.11-2, которые могут быть использованы в третьем блоке вычисления производных 3.10, известны и приведены, например, в книге: А. А. Сикарев, О.Н. Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М.: Радио и связь. 1983, стр. 194, рис.7.6.

Первый коммутатор 4 предназначен для переключения режимов работы устройства синхронизации М-последовательности с повышенной сложностью при получении откорректированных значений заданных элементов опорной кодовой последовательности внутри тактовых интервалов и на его границах, показан на фиг. 16, состоит из первого, второго и третьего выключателей "запрета" 4.11-3 и первого, второго, третьего, четвертого, пятого и шестого выключателей "разрешения" 4.21-6. Управляющие входы первого, второго и третьего выключателей "запрета" 4.11-3 и первого, второго, третьего, четвертого, пятого и шестого выключателей "разрешения" 4.21-6 соединены с управляющим входом первого коммутатора 4. Первый информационный вход первого коммутатора 4 соединен со входом первого выключателя "разрешения" 4.21, выход которого соединен с первым информационным выходом первого коммутатора 4. Второй информационный вход первого коммутатора 4 соединен со входом третьего выключателя "разрешения" 4.23, выход которого соединен со вторым информационным выходом первого коммутатора 4. Третий информационный вход первого коммутатора 4 соединен со входом пятого выключателя "разрешения" 4.25, выход которого соединен с третьим информационным выходом первого коммутатора 4. Четвертый информационный вход первого коммутатора 4 соединен со входом первого выключателя "запрета" 4.11, выход которого подключен к первому информационному выходу первого коммутатора 4 и соединен со входом второго выключателя "разрешения" 4.22, выход которого подключен к четвертому информационному выходу первого коммутатора 4. Пятый информационный вход первого коммутатора 4 соединен со входом второго выключателя "запрета" 4.12, выход которого подключен ко второму информационному выходу первого коммутатора 4 и соединен со входом четвертого выключателя "разрешения" 4.24, выход которого подключен к пятому информационному выходу первого коммутатора 4. Шестой информационный вход первого коммутатора 4 соединен со входом третьего выключателя "запрета" 4.13, выход которого подключен к третьему информационному выходу первого коммутатора 4 и соединен со входом шестого выключателя "разрешения" 4.26, выход которого подключен к шестому информационному выходу первого коммутатора 4. Выключатели "запрета" 4.11-3 и "разрешения" 4.21-6, показанные на фиг. 17 (а) и (б) соответственно, по своей физической сущности соответствуют схеме элементарного управляемого переключателя. Схемы управляемых элементарных переключателей известны и приведены, например, в книге В.Л. Шило "Популярные микросхемы КМОП, справочник", -М.: Ягуар. 1993, стр.22.

Второй коммутатор 5 предназначен для переключения режимов работы устройства синхронизации M-последовательности с повышенной сложностью при поиске синхронизации и в режиме генерации, показан на фиг. 18, состоит из первого, второго и третьего выключателей "запрета "5.11-3 и первого, второго и третьего выключателей "разрешения" 5.21-3. Управляющие входы первого, второго и третьего выключателей "запрета"5.11-3 и первого, второго и третьего выключателей "разрешения" 5.21-3 соединены с управляющим входом второго коммутатора 5. Первый информационный вход второго коммутатора 5 соединен со входом первого выключателя "запрета" 5.11, выход которого соединен с первым информационным выходом второго коммутатора 5. Второй информационный вход второго коммутатора 5 соединен со входом второго выключателя "запрета" 5.12, выход которого соединен со вторым информационным выходом второго коммутатора 5. Третий информационный вход второго коммутатора 5 соединен со входом третьего выключателя "запрета" 5.13, выход которого соединен с третьим информационным выходом второго коммутатора 5. Четвертый информационный вход второго коммутатора 5 соединен со входом первого выключателя "разрешения" 5.21, выход которого соединен с первым информационным выходом второго коммутатора 5. Пятый информационный вход второго коммутатора 5 соединен со входом второго выключателя "разрешения" 5.22, выход которого соединен со вторым информационным выходом второго коммутатора 5. Шестой информационный вход второго коммутатора 5 соединен со входом третьего выключателя "разрешения" 5.23, выход которого соединен с третьим информационным выходом второго коммутатора 5. Выключатели "запрета" 5.11-3 и "разрешения" 5.21-3, показанные на фиг. 19(а) и (б) соответственно, по своей физической сущности соответствуют схеме элементарного управляемого переключателя. Схемы управляемых элементарных переключателей известны и приведены, например, в книге В.Л. Шило "Популярные микросхемы КМОП, справочник", - М.: Ягуар, 1993, стр.22.

Блок аналоговых линий задержек б предназначен для задерживания аналоговых откорректрованных значений заданных элементов опорной кодовой последовательности на время длительности одного дискретизированного отсчета принимаемого сигнала, показан на фиг.20, состоит из первой, второй и третьей аналоговых линий задержки 6.11-3. Управляющие входы первой, второй и третей аналоговых линий задержки 6.11-3 подключены к управляющему входу блока аналоговых линий задержек 6. Первый информационный вход блока аналоговых линий задержек 6 подключен ко входу первой аналоговой линии задержки 6.11, выход которой подключен к первому информационному выходу блока аналоговых линий задержек 6. Второй информационный вход блока аналоговых линий задержек 6 подключен к входу второй аналоговой линии задержки 6.12, выход которой подключен к второму информационному выходу блока аналоговых линий задержек 6. Третий информационный вход блока аналоговых линий задержек 6 подключен к входу третьей аналоговой линии задержки 6.13, выход которой подключен к третьему информационному выходу блока аналоговых линий задержек 6. Схемы аналоговых линий задержки, которые могут быть использованы в блоке аналоговых линий задержек 6, известны и показаны, например, в книге: И.А.Цикин "Дискретно-аналоговая обработка сигналов". -М.: Радио и связь. 1982, стр. 19, рис. 2.3. С учетом особенностей заявленного устройства схема аналоговой линии задержки 6.1 может быть реализована как показано на фиг.21. Аналоговая линия задержки содержит усилитель записи (УЗ) 6.1.1, управляемый переключатель (УП) 6.1.2 и усилитель считывания (УС) 6.1.3. Информационный вход усилителя записи 6.1.1 является входом аналоговой линии задержки 6.1, а выход соединен с информационным входом управляемого переключателя УП 6.1.2, управляющий вход которого является управляющим входом аналоговой линии задержки 6.1. Выход управляемого переключателя в параллель соединен с первым контактом конденсатора и со входом усилителя считывания 6.1.3, выход которого является информационным выходом аналоговой линии задержки 6.1. Второй контакт конденсатора соединен с земляной шиной.

Блок квантователей 7 предназначен для квантования аналоговых откорректрованных значений заданных элементов опорной кодовой последовательности по уровню 0 и 1, показан на фиг.22, состоит из первого, второго, третьего, четвертого, пятого и шестого квантователей 7.11-6. Первый информационный вход блока квантователей 7 подключен ко входу первого квантователя 7.11, выход которого подключен к первому информационному выходу блока квантователей 7. Второй информационный вход блока квантователей 7 подключен ко входу второго квантователя 7.12, выход которого подключен ко второму информационному выходу блока квантователей 7. Третий информационный вход блока квантователей 7 подключен ко входу третьего квантователя 7.13, выход которого подключен к третьему информационному выходу блока квантователей 7. Четвертый информационный вход блока квантователей 7 подключен ко входу четвертого квантователя 7.14, выход которого подключен к четвертому информационному выходу блока квантователей 7. Пятый информационный вход блока квантователей 7 подключен к входу пятого квантователя 7.15, выход которого подключен к пятому информационному выходу блока квантователей 7. Шестой информационный вход блока квантователей 7 подключен ко входу шестого квантователя 7.16, выход которого подключен к шестому информационное выходу блока квантователей 7. Кроме того, первый, второй, третий, четвертый, пятый и шестой квантователи 7.11-6 дополнительно снабжены входами опорного напряжения. По своей физической сути первый, второй, третий, четвертый, пятый и шестой квантователи 7.11-6 являются компараторами, реагирующими на разность двух сигналов, один из которых опорный. Схемы компараторов, которые могут быть использованы в блоке квантователей 7, известны и показаны, например, в книге: М.У Банк. "Аналоговые интегральные схемы в радиоаппаратуре". -М.: Радио и связь. 1981, стр.26, рис.2.19(а).

Блок цифровых линий задержек 8 предназначен для задерживания квантованных откорректированных значений заданных элементов опорной кодовой последовательности на время длительности одного элемента принимаемого сигнала, показан на фиг.23, состоит из первой, второй и третьей цифровых линий задержки 8.11-3. Управляющие входы первой, второй и третьей цифровых линий задержки 8.11-3 подключены к управляющему входу блока цифровых линий задержек 8. Первый информационный вход блока цифровых линий задержек 8 подключен к входу первой цифровой линии задержки 8.11, выход которой подключен к первому информационному выходу блока цифровых линий задержек 8. Второй информационный вход блока цифровых линий задержек 8 подключен к входу второй цифровой линии задержки 8.12, выход которой подключен к второму информационному выходу блока цифровых линий задержек 8. Третий информационный вход блока цифровых линий задержек 8 подключен к входу третьей цифровой линии задержки 8.13, выход которой подключен к третьему информационному выходу блока цифровых линий задержек 8. Цифровая линия задержки 8.1 по своей сути является тактируемым D-триггером, инверсный выход которого в устройстве не используется. Схемы цифровых линий задержек 8.1, которые могут быть использованы в блоке цифровых линий задержек 8, известны и показаны, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". -М.: Радио и связь. 1986, стр.26, рис. 13.

Блок управления 9 предназначен для формирования управляющего воздействия на запуск генератора опорного сигнала, показан на фиг.24, состоит из первого, второго и третьего сумматоров по модулю 2 9.11-3, трехвходового элемента ИЛИ-НЕ 9.2, последовательного регистра 9.3, дешифратора 9.4. Выходы первого, второго и третьего сумматоров по модулю 2 9.11-3 соединены соответственно с первым, вторым и третьим входами трехвходового элемента ИЛИ-НЕ 9.2, выход которого подключен к информационному входу последовательного регистра 9.3. Выходы последовательного регистра 9.3 от первого до 2n-го соединены с соответствующими входами дешифратора 9.4. Выход дешифратора 9.4 является управляющим выходом блока управления 9. Управляющий вход последовательного регистра 9.3 является управляющим входом блока управления 9. Первые входы первого, второго и третьего сумматоров по модулю 2 9.11-3 являются соответственно первым, вторым и третьим информационными входами блока управления 9. Вторые входы первого, второго и третьего сумматоров по модулю 2 9.11-3 являются соответственно четвертым, пятым и шестым информационными входами блока управления 9. Схемы сумматоров по модулю 2 9.11-3, которые могут быть использованы в блоке управления 9, известны и показаны, например, в книге: Л. А. Мальцева, Э. М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". -М. : Радио и связь. 1986, стр.22, рис. 10. Схема трехвходового элемента ИЛИ-НЕ 9.2 представлена на фиг.25. Первый вход трехвходового элемента ИЛИ-НЕ 9.2. подключен к первому входу элемента ИЛИ 9.2.1. Второй вход трехвходового элемента ИЛИ-НЕ 9.2 подключен ко второму входу элемента ИЛИ 9.2.1, выход которого подключен к первому входу элемента ИЛИ-НЕ 9.2.2. Третий вход трехвходового элемента ИЛИ-НЕ 9.2 подключен ко второму входу элемента ИЛИ-НЕ 9.2.2, инверсный выход которого является выходом трехвходового элемента ИЛИ-НЕ 9.2. Схема элемента ИЛИ 9.2.1, которая может быть использована в трехвходовом элементе ИЛИ-НЕ 9.2, известна и показана, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C.Ямпольский. "Основы цифровой техники". -М.: Радио и связь. 1986, стр.21, рис.9(б). Схема элемента ИЛИ-НЕ 9.2.2, которая может быть использована в трехвходовом элементе ИЛИ-НЕ 9.2, известна и показана, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". - М.: Радио и связь. 1986, стр.21, рис. 9(е). Последовательный регистр 9.3, схема которого представлена на фиг. 26, состоит из 2n цифровых линий задержек 9.1. Информационный вход последовательного регистра 9.3 подключен ко входу первой цифровой линии задержки 9.11, выход которой подключен ко входу i-той цифровой линии задержки 9.1i, где i= 2...2n, и первому выходу последовательного регистра 9.3. Выход 2n-ой цифровой линии задержки 9.12n подключен к 2n выходу последовательного регистра 9.3. Управляющий вход последовательного регистра 9.3 подключен к управляющим входам всех 2n цифровых линий задержек 9.1. Цифровая линия задержки 9.1 по своей сути является тактируемым D-триггером, инверсный выход которого в устройстве не используется. Схемы цифровых линий задержек 9.1, которые могут быть использованы в последовательном регистре 9.3, известны и показаны, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". -М.: Радио и связь. 1986, стр.26, рис. 13.

Генератор опорных кодовых последовательностей 10 предназначен для формирования опорной кодовой последовательности с использованием аналоговых значений ее элементов, показан на фиг.28, состоит из n аналоговых линий задержек 10.11-n, n+1 умножителей на постоянный множитель 10.21-(n+1) и n-1 вычислителей функции обратной связи 10.31-(n-1). Управляющий вход генератора опорных кодовых последовательностей 10 соединен с управляющими входами n аналоговых линий задержек 10.11-n. Выходы всех n аналоговых линий задержек 10.11-n соединены со входами i-тых умножителей на постоянный множитель 10.2i, где i=2.(n+1), и j-тыми входами аналоговых линий задержек 10.1j, где j= 2. ..n. Выходы j-тых умножителей на постоянный множитель 10.2j подключены ко вторым входам соответствующих вычислителей функции обратной связи 10.3. Выход (n+1)-го умножителя на постоянный множитель 10.2 подключен к первому входу (n-1)-го вычислителя функции обратной связи 10.3. Выходы, начиная с (n-1)-го вычислителя функции обратной связи 10.3 и до первого соединены последовательно с первыми входами соответствующих вычислителей функции обратной связи 10.3. Выход первого вычислителя функции обратной связи 10.3 подключен ко входу первого умножителя на постоянный множитель 10.2, выход которого соединен со входом первой аналоговой линии задержки 10.1. Причем выходы предварительно заданных аналоговых линий задержек 10.1 подключены к соответствующим умножителям на постоянный множитель 10.2 и являются соответственно первым, вторым и третьим информационными выходами генератора опорных кодовых последовательностей 10. Входы последующих за предварительно заданными аналоговыми линиями задержек 10.1 являются соответственно первым, вторым и третьим информационными входами генератора опорных кодовых последовательностей 10. Схемы аналоговых линий задержек 10.1, которые могут быть использованы в генераторе опорных кодовых последовательностей 10, известны и показаны, например, в книге: И. А. Цикин "Дискретно-аналоговая обработка сигналов". -М.: Радио и связь. 1982, стр. 19, рис.2.3. С учетом особенностей заявленного устройства схема аналоговой линии задержки 10.1 может быть реализована как показано на фиг.21. Схемы умножителей на постоянный множитель 10.2 по физической сущности являются неинвертирующими усилителями. Схемы неинвертирующих усилителей известны и приведены, например, в книге: Ю.А.Мячин "180 аналоговых микросхем (справочник)". -М. : издательство Патриот, МП Символ-Р и редакция журнала Радио, 1993, стр.7. Схема вычислителя функции обратной связи 10.3, представленная на фиг.29, состоит из первого и второго аналоговых сумматоров 10.3.11-2, аналогового перемножителя 10.3.2 и умножителя на постоянный множитель 10.3.3.

Схемы аналоговых сумматоров 10.3.11-2, которые могут быть использованы в вычислителе функции обратной связи 10.3, известны и приведены, например, в книге: А.А. Сикарев, О.Н. Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М.: Радио и связь. 1983, стр. 194, рис.7.6.

Схема аналогового перемножителя 10.3.2, которая может быть использована в вычислителе функции обратной связи 10, известна и приведена, например, в книге: А.А. Сикарев, О.Н. Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов". -М.: Радио и связь. 1983, стр.200, рис.7.11.

Схема умножителя на постоянный множитель 10.3.3 по физической сущности является неинвертирующими усилителями. Схемы неинвертирующих усилителей известны и приведены, например, в книге: Ю.А.Мячин "180 аналоговых микросхем (справочник)". -М.: издательство Патриот, МП Символ-Р и редакция журнала Радио, 1993, стр.7.

Генератор опорного сигнала 11 предназначен для генерирования М-последовательности, синхронной с принимаемой, показан на фиг.30, состоит из n цифровых линий задержек 11.11-n, n+1 умножителей на постоянный множитель 10.21-(n+1) и n-1 сумматоров по модулю 2 10.31-(n-1). Управляющий вход генератора опорных кодовых последовательностей 11 соединен с управляющими входами всех n цифровых линий задержек 11.11-n. Выходы всех n цифровых линий задержек 11.11-n соединены со входами i-тых умножителей на постоянный множитель 11.2i, где i=2...(n+1), и j-тыми входами цифровых линий задержек 11.1j, где j=2...n. Выходы j-тых умножителей на постоянный множитель 11.2j подключены ко вторым входам соответствующих сумматоров по модулю 2 11.3. Выход (n+1)-го умножителя на постоянный множитель 11.2 подключен к первому входу (n-1)-го сумматора по модулю 2 11.3. Выходы, начиная с (n-1)-го сумматора по модулю 2 11.3 и до первого соединены последовательно с первыми входами соответствующих сумматоров по модулю 2 11.3. Выход первого сумматора по модулю 2 11.3 подключен ко входу первого умножителя на постоянный множитель 11.2, выход которого соединен со входом первой цифровой линии задержки 11.1. Причем выходы предварительно заданных цифровых линий задержек 11.1 подключены к соответствующим умножителям на постоянный множитель 11.2 и являются соответственно первым, вторым и третьим информационными выходами генератора опорного сигнала 11. Входы последующих за предварительно заданными цифровыми линиями задержек 11.1 являются соответственно первым, вторым и третьим информационными входами генератора опорного сигнала 11. Схемы цифровых линий задержек 11.1 по своей сути являются тактируемыми D-триггерами, инверсные выходы которых в устройстве не используются. Схемы цифровых линий задержек 11.1, которые могут быть использованы в генераторе опорного сигнала 11, известны и показаны, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". -М.: Радио и связь. 1986, стр.26, рис. 13. Схема умножителя на постоянный множитель 11.2 по физической сущности является неинвертирующими усилителями. Схемы неинвертирующих усилителей известны и приведены, например, в книге: Ю.А.Мячин "180 аналоговых микросхем (справочник)". - М. : издательство Патриот, МП Символ-Р и редакция журнала Радио, 1993, стр. 7. Схемы сумматоров по модулю 2 11.3, которые могут быть использованы в генераторе опорного сигнала 11, известны и показаны, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". -М.: Радио и связь. 1986, стр.22, рис. 10.

Цифровой нелинейный узел усложнения 12 предназначен для формирования М-последовательности с повышенной сложностью, синхронной с принимаемой, показан на фиг.31, состоит из первого и второго инверторов 12.11-2 и первого, второго и третьего элементов И-НЕ 12.21-3. Первый вход цифрового нелинейного узла усложнения 12 подключен ко входу первого инвертора 12.11, инверсный выход которого подключен к первому входу первого элемента И-НЕ 12.21. Второй вход цифрового нелинейного узла усложнения 12 подключен ко второму входу первого инвертора 12.11 и ко входу второго инвертора 12,22. Третий вход цифрового нелинейного узла усложнения 12 подключен ко второму входу второго инвертора 12.22, инверсный выход которого подключен ко второму входу третьего элемента И-НЕ 12.23, инверсный выход которого является выходом устройства. Схемы инверторов 12.11-2 которые могут быть использованы в цифровом нелинейном узле усложнения 12, известны и показаны, например, в книге: Л.А. Мальцева, Э. М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". -М.: Радио и связь. 1986, стр.21, рис.9(в). Схемы элементов И-НЕ 12.21-3, которые могут быть использованы в цифровом нелинейном узле усложнения 12, известны и показаны, например, в книге: Л.А. Мальцева, Э.М. Фромберг, B.C. Ямпольский. "Основы цифровой техники". -М.: Радио и связь. 1986, стр.21, рис.9(г).

Заявленное устройство синхронизации М-последовательности с повышенной сложностью работает следующим образом. Смесь сигнала и шума, фиг.7(б), поступает на приемный информационный вход устройства, показанного на фиг. 11. Сначала сигнал параллельно поступает на приемный информационный вход дискретизатора 1 и выделителя тактовой частоты 2. В выделителе тактовой частоты 2, показанном на фиг. 12, с помощью фазового дискриминатора 2.5 определяют период следования информационных сигналов, и на выходе управляющего элемента 2.2 получают стробирующие импульсы с тактовой частотой информационного сигнала, фиг. 7(в). Этот выход является первым управляющим выходом выделителя тактовой частоты 2. А на выходе делителя частоты 2.3 с коэффициентом деления, равным k, получают стробирующие импульсы с частотой, в k раз превышающей тактовую частоту информационного сигнала, фиг.7(г). Этот выход является вторым управляющим выходом выделителя тактовой частоты 2. Кроме того, смесь сигнала и шума со входа устройства синхронизации M-последовательности поступает в дискретизатор 1. На управляющий вход дискретизатора 1 поступают стробирующие импульсы с частотой, в k раз превышающей тактовую частоту информационного сигнала. В дискретизаторе 1 получают дискретизированные отсчеты информационного сигнала с частотой в k раз выше тактовой частоты информационного сигнала, фиг.7(д). С выхода дискретизатора 1 дискретизированные отсчеты информационного сигнала поступают на приемный информационный вход корректора 3, фиг. 13.

В случае первоначального вхождения в синхронизацию в аналоговые линии задержки 10.1 генератора опорных кодовых последовательностей 10, фиг.28, должны быть записаны произвольные ненулевые аналоговые значения начальных условий в области определения от 0 до 1 или могут находиться значения, оставшиеся с предыдущего сеанса связи.