Изобретение относится к устройствам автоматики и может найти применение в устройствах управления ракетно-космической техники (РКТ).

Известен многоканальный командный аппарат с электронной коммутацией, предназначенный для формирования импульсных команд управления исполнительными органами, содержащий соединенные последовательно контроллер интерфейсов, блок дешифраторов, формирователей команд и блок ключей, выходы которых являются выходами устройства, генератор импульсов, а блок формирователей команд выполнен на счетчиках (патент РФ №2340925 кл. G05B 11/00).

Данное устройство не позволяет формировать матричные команды.

Известно устройство формирования матричных команд, содержащее регистры столбцов и строк, первые и вторые дешифраторы столбцов и строк, группы ключей коммутации столбцов и строк, схемы контроля состояния столбцов и строк, схемы обнаружения неисправности в столбцах и строках, регистраторы приема данных столбцов и строк, первая, вторая, третья и четвертая схемы задержки, элемент ИЛИ, первый и второй ключи коммутации матричного питания, матричные шины столбцов и строк, шины питания +Е и -Е (патент РФ №2549123 кл. G05B 11/00).

Недостатком устройства формирования матричных команд является отсутствие информации о факте не формирования команд, например, при возникновении неисправности или сбое в самом устройстве.

Наиболее близким к заявляемому техническому решению по технической сущности и достигаемому техническому результату является устройство формирования матричных команд, содержащее первый регистр (столбцов), второй регистр (строк), первый дешифратор, второй дешифратор, первую группу ключей, вторую группу ключей, вертикальные коммутируемые шины (столбцы) и горизонтальные коммутируемые шины (строки), шины питания +Е и -Е коммутируемых шин, причем шина питания +Е соединена с первой группой ключей, а шина питания -Е соединена со второй группой ключей, информационные входы первого и второго регистра объединены и являются информационными входами устройства, входы «запись» первого и второго регистра объединены и являются входом «запись» устройства, выходы первого регистра соединены с входами первого дешифратора, а выходы первого дешифратора соединены с входами первой группы ключей, выходы которой образуют

вертикальные коммутируемые шины устройства, выходы второго регистра соединены с входами второго дешифратора, а выходы второго дешифратора соединены с входами второй группы ключей, выходы которой образуют горизонтальные коммутируемые шины устройства. Аноды первой группы диодов соединены с соответствующими выходами первой ключевой схемы, а катоды объединены и соединены с положительным входом формирователя наличия матричной команды и фиксатора наличия отказа в строках. Катоды второй группы диодов соединены с соответствующими выходами второй ключевой схемы, а аноды объединены и соединены с отрицательным входом формирователя наличия матричной команды и фиксатора наличия отказа в столбцах. Отрицательный вход фиксатора наличия отказа в столбцах соединен с шиной питания -Е, положительный вход фиксатора наличия отказа в строках соединен с шиной питания +Е, а выходы фиксатора наличия отказа в столбцах, формирователя наличия матричной команды, фиксатора наличия отказа в строках соединены соответственно с первым, вторым, третьим входом анализатор состояния, а вход запись анализатора состояния является входом записи состояния устройства, выход анализатора состояния является выходом устройства (патент РФ №2540780 кл. Н03К 17/04).

Описанное устройство принято за прототип изобретения.

Недостатками указанного устройства является невозможность определения номера отказавшей линии матрицы, знание которой позволило бы продолжить работу устройства с частичным ограничением по числу формируемых команд, а также крутые фронты у матричных команд (отсутствие формирователя фронтов) могут вызвать на соседних линиях матрицы помеху, что, при отсутствии защиты у абонентов, приводит к ложному срабатыванию.

Задачей изобретения является повышение надежности устройства.

Технический результат заключается в повышении надежности устройства путем контроля кода выданной команды и исключение возможности создания помех путем введения формирователя с заданной крутизной фронтов.

Указанный технический результат достигается за счет того, что формирователь матричных команд содержит первый регистр (столбцов), второй регистр (строк), первый и второй дешифратор, первую и вторую группу ключей, вертикальные коммутируемые шины (столбцы) и горизонтальные коммутируемые шины (строки), шины питания +Е и -Е коммутируемых шин; информационные входы первого и второго регистра объединены и являются информационными входами устройства; входы «Запись» первого и второго регистра объединены и являются входом «Запись» устройства; выходы первого регистра соединены с входами первого дешифратора, выходы которого соединены с входами

первой группы ключей, выходы первой группы ключей являются вертикальными коммутируемыми шинами устройства; выходы второго регистра соединены с входами второго дешифратора, выходы которого соединены с входами второй группы ключей, выходы второй группы ключей являются горизонтальными коммутируемыми шинами устройства В устройство введены формирователь длительности фронтов матричной команды, генератор импульсов, первый и второй элемент «И», первый и второй элемент «ИЛИ», первая, вторая, третья и четвертая схемы сравнения, блок гальванической развязки столбцов, блок гальванической развязки строк, первая, вторая, третья схемы задержки, формирователь длительности команды, третий регистр (контроля столбцов), четвертый регистр (контроля строк), блок преобразования и контроля; вторая группа входов первой и второй схем сравнения соединены с информационными входами устройства; выходы первого регистра дополнительно соединены с первой группой входов первой схемы сравнения; выходы второго регистра дополнительно соединены со второй группой входов второй схемы сравнения; вход устройства управления «Запись» дополнительно соединен с входом первой схемы задержки, выход которого соединен со вторым входом первого элемента «И» и входом второй схемы задержки, выход последнего соединен с входом «Запись» третьего и четвертого регистров и входом третьей схемы задержки, выход которого соединен с входом «Запись» блока преобразования и контроля; выходы «равно» первой и второй схем сравнения соединены соответственно с первым и третьим входом первого элемент «И»; выход первого элемента «И» соединен с входом запуска формирователя длительности команды, выход которого соединен с входом разрешения формирователя длительности фронтов матричной команды; выходы «больше» и «меньше» первой и второй схем сравнения через первый элемент «ИЛИ» соединены с входом «Не норма 1» блока преобразования и контроля; выход генератора соединен с тактовыми входами формирователя длительности фронтов и формирователя длительности команды; шина питания +Е через коммутируемый выход формирователя длительности фронтов соединена с первой группой ключей; выходы первой группы ключей дополнительно соединены с входами блока гальванической развязки столбцов, выходы которого соединены с входами третьего регистра, а выходы третьего регистра соединены с первой группой входов блока преобразования и контроля и с первой группой входов третьей схемы сравнения, входы второй группы третьей схемы сравнения соединены с выходами первого дешифратора; выходы второй группы ключей дополнительно соединены с входами блока гальванической развязки строк, выходы которого соединены с входами четвертого регистра, а выходы четвертого регистра соединены со второй группой входов блока преобразования и контроля и со второй

группой входов четвертой схемы сравнения, первая группа входов которой соединена с выходами второго дешифратора; выходы «больше» и «меньше» третьей и четвертой схем сравнения через второй элемент «ИЛИ» соединены с входом «Не норма 2» блока преобразования и контроля; входы второго элемента «И» соединены с выходами «равенства» третьей и четвертой схем сравнения, а выход второго элемента «И» соединен с входом «Норма» блока преобразования и контроля; выходы блока преобразования и контроля являются информационными выходами устройства и объединены с информационными входами устройства, образуя двунаправленную информационную шину устройства; вход «Чтение» блока преобразования и контроля является входом «Чтение» устройства.

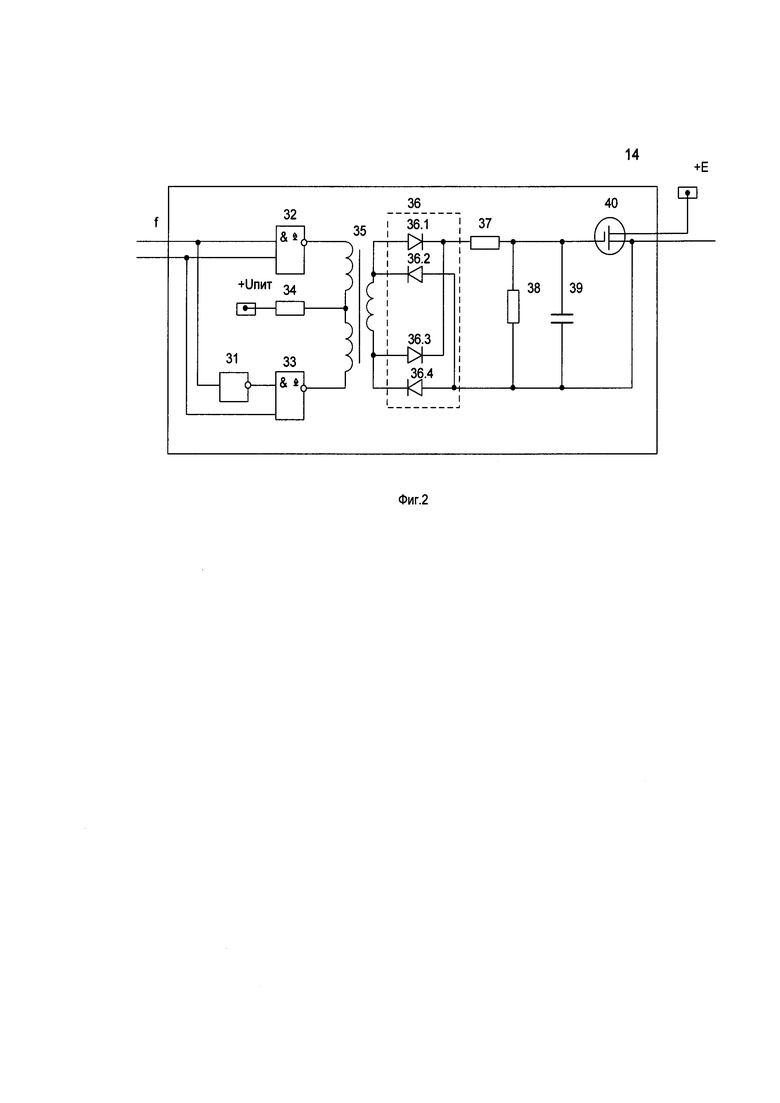

Формирователь длительности фронтов матричной команды состоит из элемента «НЕ», первого и второго элементов «2И-НЕ» с открытым стоковым выходом, первого, второго и третьего резисторов, трансформатора, мостового выпрямителя, конденсатора и транзистора; первый вход формирователя матричной команды соединен с первым входом первого элемента «2И-НЕ» и, через элемент «НЕ», с первым входом второго элемента «2И-НЕ», вторые входы первого и второго элементов «2И-НЕ» объединены и являются вторым входом формирователя; выходы элементов «2И-НЕ» соединены через первичные обмотки трансформатора с первым выводом первого резистора, второй вывод которого соединен с шиной питания логических цепей +Uпит; первый вывод вторичной обмотки трансформатора соединен с первым входом мостового выпрямителя; второй вывод вторичной обмотки трансформатора соединен со вторым входом выпрямителя, положительный выход которого через второй резистор соединен с первыми выводами третьего резистора и конденсатора, а также с затвором транзистора; отрицательный выход выпрямителя соединен со вторыми выводами третьего резистора и конденсатора, с истоком транзистора и является выходом формирователя, сток транзистора соединен с коммутируемой шиной +Е.

Изобретение поясняется схемами:

- на фиг. 1 представлена функциональная схема устройства формирования матричных команд;

- на фиг. 2 изображен формирователь длительности фронтов матричной команды;

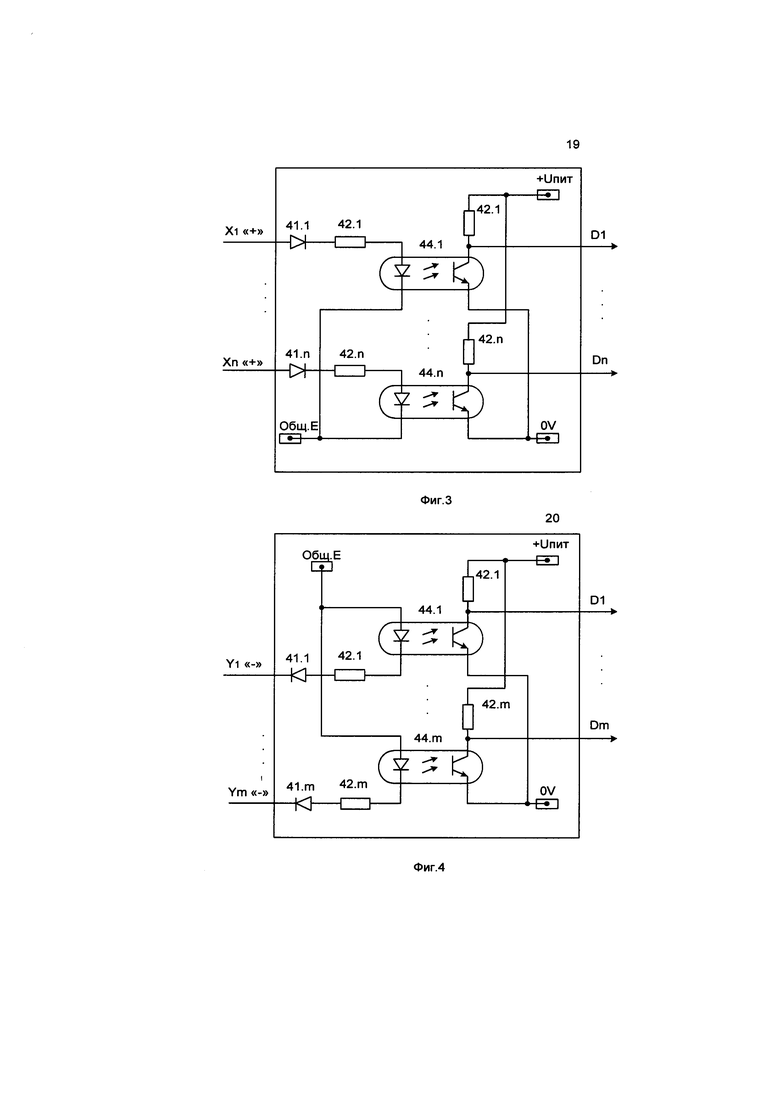

- на фиг. 3 изображен блок гальванической развязки столбцов;

- на фиг. 4 изображен блок гальванической развязки строк.

Устройство формирования матричных команд содержит двунаправленную шину 1 устройства, вход «Запись» кода команды 2 устройства (проходящий через три схемы задержки 5, 17, 23), вход «Чтение» кода выданной команды 3 устройства, первый регистр (столбцов) 4, первую схему задержки 5, второй регистр (строк) 6, первую схему сравнения (столбцов) 7, вторую схему сравнения (строк) 8, первый дешифратор 9 (столбцов), второй дешифратор 10 (строк), генератор 11, первый элемент «И» 12, первый элемент «ИЛИ» 13, формирователь длительности фронтов матричной команды 14, первую группу ключей 15, формирователь длительности команды 16, вторую схему задержки 17, вторую группу ключей 18, блок гальванической развязки столбцов 19, блок гальванической развязки строк 20, третий регистр (контроля столбцов) 21, четвертый регистр (контроля строк) 22, третью схему задержки 23, третью схему сравнения (столбцов) 24, четвертую схему сравнения (строк) 25, второй элемент «ИЛИ» 26, второй элемент «И» 27, блок преобразования и контроля 28, вертикальные коммутируемые шины 29 (Xn), горизонтальные коммутируемые шины 30 (Ym).

Схемы задержки 5, 17, 23 предназначены для исключения влияния переходных процессов переключения в цифровых элементах устройства и ключах.

Формирователь длительности фронтов матричной команды 14 предназначен для коммутации шины +Е для первой группы ключей 15, формирования длительности фронтов выдаваемой матричной команды и развязки шины питания логических цепей управления +Uпит от коммутируемой шины +Е, и состоит из элемента «НЕ» 31, первого 32 и второго 33 элементов «2И-НЕ» с открытым стоковым выходом, первого резистора 34, трансформатора 35, мостового выпрямителя 36, выполненного на диодах, второго 37 и третьего 38 резисторов, конденсатора 39 и выходного транзистора 40.

Блок гальванической развязки столбцов 19 (фиг. 3) предназначен для гальванической развязки и согласования уровней коммутируемых шин Xn с уровнями логических цепей и состоит из n ячеек с входами Xn соответствующими вертикально коммутируемым шинам, в каждую из ячеек входят развязывающий диод 41 (41.1-41.n) первый 42 (42.1-42.n) и второй 43 (43.1-43.n) резисторы и транзисторная оптопара 44 (44.1-44.n). Первый резистор 42 является токозадающим для входной цепи транзисторной оптопары 44, а второй резистор 43 является нагрузкой выходного транзистора оптопары 44.

Блок блок гальванической развязки строк 20 (фиг. 4) предназначен для гальванической развязки и согласования уровней коммутируемых шин Ym с уровнями логических цепей и состоит из m ячеек с входами соответствующими горизонтально коммутируемым шинам, в каждую из ячеек входят развязывающий диод 41 (41.l-41.m), первый 42 (42.l-42.m) и второй 43 (43.l-43.m) резисторы и транзисторная оптопара 44 (44.l-44.m). Первый резистор 42 является токозадающим для входной цепи транзисторной оптопары 44, а второй резистор 43 является нагрузкой выходного транзистора оптопары 44.

Предлагаемое устройство работает следующим образом.

Двоичный код команды, через двунаправленную шину 1 устройства, по сигналу управления «Запись» с входа 2 устройства записывается в первый 4 и второй 6 регистры, код команды дешифрируется первым 9 и вторым 10 дешифратором, на соответствующих выходах которых появляются сигналы, открывающие соответствующие ключи первой 15 и второй 18 группы ключей, при этом на соответствующей горизонтальной коммутируемой линии 30 Ym появляется отрицательный потенциал -Е. Одновременно код команды поступает соответственно на первую 7 и вторую 8 схемы сравнения, где происходит сравнение кода команды установленной на шине 1 и кода записанного в первый 4 и второй 6 регистры; при совпадении кодов на выходах «равно» схем сравнения 7 и 8 появляется уровень логической «1», разрешающий прохождение сигнала управления «Запись» с выхода первой схемы задержки 5 через первый элемент «И» 12 на вход разрешения формирователя длительности команды 16, по которому запускается процесс формирования длительности команды с использованием частоты генератора 11; при этом на выходе формирователя длительности команды 16 устанавливается сигнал равный уровню логической «1» на время длительности команды, который поступает на вход разрешения формирователя длительности фронтов матричной команды 14, где частота с выхода генератора 11 через первый элемент «2И-НЕ» 32 в фазе и через элементы «НЕ» 31, второй элемент «2И-НЕ» 33 в противофазе поступает на трансформатор 35, который обеспечивает гальваническую развязку шин питания +Uпит логических цепей управления и коммутируемой шины +Е. С выхода трансформатора 35 частота поступает на входы выпрямителя 36, на выходах которого появляется потенциал, обеспечивающий открытие транзистора 40, второй 37 и третий 38 резисторы совместно с конденсатором 39 задают длительность переднего и заднего фронта матричной команды соответственно и одновременно определяют порог срабатывания для транзистора 40, который на время длительности команды коммутирует шину +Е, при этом на соответствующей вертикальной коммутируемой линии 29 Xn появляется положительный потенциал +Е (матричная команда выдана).

Одновременно положительный потенциал +Е с соответствующей вертикальной шины 29 Xn поступает на соответствующий вход блока гальванической развязки столбцов 19, а отрицательный потенциал -Е с соответствующей горизонтальной шины 30 Ym поступает на соответствующий вход блока гальванической развязки строк 20; через развязывающие диоды 41, токозадающий резистор 42 и светодиод транзисторной оптопары 44 начинает протекать ток, за счет которого откроются соответствующие транзисторные оптопары, и на соответствующих выходах появятся логические «1», которые по сигналу управления «Запись» с выхода второго формирователя задержки 17 записываются в третий регистр (контроля столбцов) 21 и четвертый регистр (контроля строк) 22 соответственно. Полученный позиционный код столбцов с выхода третьего регистра 21 и позиционный код строк с выхода четвертого регистра 22 поступает на блок преобразования и контроля 28. Параллельно с данным процессом происходит сравнение кодов с выходов дешифратора столбцов 9 и третьего регистра (контроля столбцов) 21 третьей схемой сравнения 24 и сравнение кодов с выходов дешифратора строк 10 и четвертого регистра (контроля строк) 22 четвертой схемой сравнения 25. При совпадении дешифрированных кодов столбцов и считанных с вертикальных коммутируемых шин матрицы 29 на выходе «равно» третьей схемы сравнения 24 появится сигнал логической «1». Аналогично, при совпадении дешифрированных кодов строк и считанных с горизонтальных коммутируемых шин матрицы 30 на выходе «равенства» четвертой схемы сравнения 25 появится сигнал логической «1». Оба сигнала поступают на второй элемент «И» 27, и по сигналу управления «Запись» с выхода третьей схемы задержки 23 в блок преобразования и контроля 28 запишется информационный сигнал исправности «Норма» матрицы вместе с кодом выданной команды. Блок преобразования и контроля 28 преобразует полученные позиционные коды Xn и Ym в двоичный код, формат которой соответствует формату принятой команды по двунаправленной шине 1 устройства и по сигналу «Чтение» передает его на информационный выход в двунаправленную шину 1 устройства для анализа и принятия решения во внешнем устройстве.

При несовпадении кодов на выходах «равно» схем сравнения 7 или 8 устанавливается уровень логического «0», который блокирует прохождение сигнала управления с выхода схемы задержки 5 через первый элемент «И» 12, и формирование матричной команды запрещается; коммутация шины +Е не выполняется; на вертикальных коммутируемых шинах матрицы 29 Xn положительный потенциал +Е отсутствует, матричная команда не выдается. При этом, на выходах «меньше» или «больше» схем сравнения 7 или 8 устанавливается уровень логического «1», который через первый элемент «ИЛИ» 13 поступает на информационный вход «Не норма 1» блока преобразования и контроля 28 и по сигналу управления «Запись» с входа 2 с выхода третьей схемы задержки 23 записывается в блок преобразования и контроля 28. И далее по сигналу «Чтение» передается на информационный выход в двунаправленную шину 1 устройства для анализа и принятия решения во внешнем устройстве.

При несовпадении дешифрированных кодов столбцов и считанных с вертикальных коммутируемых шин матрицы 29 на выходе «больше» или «меньше» третьей схемы сравнения кодов 24 появится сигнал логической «1», или при несовпадении дешифрированных кодов строк и считанных с горизонтальных коммутируемых шин матрицы 30 на выходе «больше» или «меньше» четвертой схемы сравнения 25 появится сигнал логической «1», который через второй элемент «ИЛИ» 26 поступает на информационный вход «Не норма 2» блока преобразования и контроля 28 и по сигналу управления «Запись» с выхода третьей схемы задержки 23 записывается в блок преобразования и контроля 28. По запросу с входа «Чтение» 3, который формируется через время равное не менее времени длительности команды, код выданной команды и информация с блока преобразования и контроля 28 выдаются на информационный выход на двунаправленную шину устройства 1.

При возникновении короткого замыкания одного из ключей первой группы 15, через отказавший ключ и ключ, соответствующий коду команды, в момент выдачи команды, положительные потенциалы +Е поступают на блок гальванической развязки 19, на соответствующих выходах которого появляются уровни логической «1», которые по сигналу управления «Запись» с выхода второй схемы задержки 17 запишутся в третий регистр (контроля столбцов) 21. Далее на выходе «больше» или «меньше» схемы сравнения 24 появляется уровень логической «1», который по сигналу управления с выхода третьей схемы задержки, через второй элемент «И» запишется в блок преобразования и контроля 28, как сигнал «Не норма 2», одновременно в блок преобразования и контроля 28 запишется позиционный код выданной команды. Блок преобразования и контроля 28 преобразует полученные позиционные коды Xn и Ym в двоичный код команды, формат которой соответствует формату принятой команды по двунаправленной шине 1 устройства, при этом дополнительно в блок преобразования и контроля 28 (в регистр состояния) запишется сигнал Х>1. По запросу с входа «Чтение» 3, код выданной команды и информация с блока преобразования и контроля 28 выдаются на информационный выход на двунаправленную шину устройства 1 для анализа и принятия решения во внешнем устройстве.

При возникновении короткого замыкания одного из ключей второй группы 18, через отказавший ключ и ключ соответствующий коду команды, в момент выдачи команды, отрицательные потенциалы -Е поступают на блок гальванической развязки 20 на соответствующих выходах, которого появляются уровни логической «1» и по сигналу «Запись» с выхода второй схемы задержки 17 запишутся в четвертый регистр (контроля строк) 22. Далее на выходе «больше» или «меньше» схемы сравнения 25 появляется уровень логической «1», который по сигналу «Запись» с выхода третьей схемы задержки, через второй элемент «И» запишется в регистр состояния блока преобразования, как сигнал «Не норма 2», одновременно в блок преобразования и контроля 28 запишется позиционный код выданной команды. Блок преобразования и контроля 28 преобразует полученные позиционные коды Xn и Ym в двоичный код команды, при этом дополнительно в блок преобразования и контроля 28 (в регистр состояния) запишется сигнал Y>1. По запросу с входа «Чтение» 3, код выданной команды и информация с блока преобразования и контроля 28 выдаются на информационный выход на двунаправленную шину устройства 1 для анализа и принятия решения во внешнем устройстве.

При возникновении обрыва ключа первой группы 15 через который выдается команда, положительный потенциал +Е не поступает на блок гальванической развязки 19 на соответствующем выходе, которого не появляется уровень логической «1», по сигналу «Запись» с выхода второй схемы задержки 17 в третий регистр 21 запишутся логические «0». Далее на выходе «больше» и «меньше» схемы сравнения 24 появляется уровень логической «1», который по сигналу «Запись» с выхода третьей схемы задержки, через второй элемент «И» запишется в регистр состояния блока преобразования, как сигнал «Не норма 2», одновременно в блок преобразования запишется позиционный код выданной команды. Блок преобразования и контроля 28 преобразует полученные позиционные коды Xn и Ym в двоичный код команды, при этом дополнительно в регистр состояния блока запишется сигнал Х<1. По запросу с входа «Чтение» 3, код выданной команды и информация с блока преобразования и контроля 28 выдаются на информационный выход на двунаправленную шину устройства 1 для анализа и принятия решения во внешнем устройстве.

При возникновении обрыва ключа первой группы 18, через который выдается команда, отрицательный потенциал -Е не поступает на блок гальванической развязки 20, на соответствующем выходе которого не появляется уровень логической «1», по сигналу «Запись» с выхода второй схемы задержки 17 в третий регистр 21 запишется логический «0». Далее на выходе «больше» и «меньше» схемы сравнения 25 появляется уровень логической «1», который по сигналу «Запись» с выхода третьей схемы задержки, через второй элемент «И» запишется в регистр состояния блока преобразования, как сигнал «Не норма 2». Одновременно в блок преобразования запишется позиционный код выданной команды. Блок преобразования и контроля 28 преобразует полученные позиционные коды Xn и Ym в двоичный код команды, при этом дополнительно в регистр состояния блока запишется сигнал Y<1. По запросу с входа «Чтение» 3 код выданной команды и информация с блока преобразования и контроля 28 выдаются на информационный выход на двунаправленную шину устройства 1 для анализа и принятия решения во внешнем устройстве.

Таким образом, реализация указанного схемного решения позволяет контролировать код выданной команды и за счет введенного в схему формирователя с заданной крутизной фронтов исключать возможность создания помех, достигая тем самым выполнения поставленной задачи.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА СИГНАЛОВ КОМАНДНОЙ МАТРИЦЫ | 2011 |

|

RU2487393C1 |

| ФОРМИРОВАТЕЛЬ МАТРИЧНЫХ КОМАНД | 2013 |

|

RU2540780C2 |

| ФОРМИРОВАТЕЛЬ МАТРИЧНЫХ КОМАНД | 2014 |

|

RU2549123C1 |

| Матричное устройство выдачи команд с оптической развязкой | 2016 |

|

RU2628911C1 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ | 1996 |

|

RU2106679C1 |

| Устройство для отображения информации | 1983 |

|

SU1108489A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| Устройство для индикации | 1986 |

|

SU1381586A1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2003 |

|

RU2263345C2 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1982 |

|

SU1042070A1 |

Изобретение относится к устройствам автоматики и может найти применение в устройствах управления ракетно-космической техники. Технический результат заключается в повышении надежности устройства путем контроля кода выданной команды и исключении возможности создания помех путем введения формирователя с заданной крутизной фронтов. Для этого создан формирователь матричных команд, содержащий первый регистр (столбцов), второй регистр (строк), первый дешифратор, второй дешифратор, первую группу ключей, вторую группу ключей, вертикальные коммутируемые шины (столбцы) и горизонтальные коммутируемые шины (строки), шины питания +Е и -Е коммутируемых шин, за счет введения устройств сравнения кодов, блока гальванической развязки контроля строк, блока гальванической развязки контроля столбцов, третьего регистра контроля строк, четвертого регистра контроля столбцов, блока преобразования и контроля, что позволяет в случае сбойной записи кода команды или отказа регистров столбцов или строк блокировать выдачу ложной команды, контролировать код выданной матричной команды, позволяющий определять короткое замыкание или обрыв в ключах матрицы, за счет введения формирователя длительности фронтов матричной команды достигается уменьшение помехи на соседних линиях матрицы, что исключает подработку на нагрузке. 1 з.п. ф-лы, 4 ил.

1. Формирователь матричных команд, содержащий первый регистр (столбцов), второй регистр (строк), первый и второй дешифратор, первую и вторую группу ключей, вертикальные коммутируемые шины (столбцы) и горизонтальные коммутируемые шины (строки), шины питания +Е и -Е коммутируемых шин; информационные входы первого и второго регистра объединены и являются информационными входами устройства; входы «Запись» первого и второго регистра объединены и являются входом «Запись» устройства; выходы первого регистра соединены с входами первого дешифратора, выходы которого соединены с входами первой группы ключей, выходы первой группы ключей являются вертикальными коммутируемыми шинами устройства; выходы второго регистра соединены с входами второго дешифратора, выходы которого соединены с входами второй группы ключей, выходы второй группы ключей являются горизонтальными коммутируемыми шинами устройства, отличающийся тем, что введены формирователь длительности фронтов матричной команды, генератор импульсов, первый и второй элемент «И», первый и второй элемент «ИЛИ», первая, вторая, третья и четвертая схемы сравнения, блок гальванической развязки столбцов, блок гальванической развязки строк, первая, вторая, третья схемы задержки, формирователь длительности команды, третий регистр (контроля столбцов), четвертый регистр (контроля строк), блок преобразования и контроля; вторая группа входов первой и второй схем сравнения соединены с информационными входами устройства; выходы первого регистра дополнительно соединены с первой группой входов первой схемы сравнения; выходы второго регистра дополнительно соединены со второй группой входов второй схемы сравнения; вход устройства управления «Запись» дополнительно соединен с входом первой схемы задержки, выход которого соединен со вторым входом первого элемента «И» и входом второй схемы задержки, выход последнего соединен с входом «Запись» третьего и четвертого регистров и входом третьей схемы задержки, выход которого соединен с входом «Запись» блока преобразования и контроля; выходы «равно» первой и второй схем сравнения соединены соответственно с первым и третьим входом первого элемент «И»; выход первого элемента «И» соединен с входом запуска формирователя длительности команды, выход которого соединен с входом разрешения формирователя длительности фронтов матричной команды; выходы «больше» и «меньше» первой и второй схем сравнения через первый элемент «ИЛИ» соединены с входом «Не норма 1» блока преобразования и контроля; вторая группа входов первой и первая группа входов второй схем сравнения соединены с информационными входами устройства; выходы первого регистра дополнительно соединены с первой группой входов первой схемы сравнения; выходы второго регистра дополнительно соединены со второй группой входов второй схемы сравнения; выход генератора соединен с тактовыми входами формирователя длительности фронтов и формирователя длительности команды; шина питания +Е через коммутируемый выход формирователя длительности фронтов соединена с первой группой ключей; выходы первой группы ключей дополнительно соединены с входами блока гальванической развязки столбцов, выходы которого соединены с входами третьего регистра, а выходы третьего регистра соединены с первой группой входов блока преобразования и контроля и с первой группой входов третьей схемы сравнения, входы второй группы третьей схемы сравнения соединены с выходами первого дешифратора; вывод шины питания -Е соединен со второй группой ключей; выходы второй группы ключей дополнительно соединены с входами блока гальванической развязки строк, выходы которого соединены с входами четвертого регистра, а выходы четвертого регистра соединены со второй группой входов блока преобразования и контроля и со второй группой входов четвертой схемы сравнения, первая группа входов которой соединена с выходами второго дешифратора; выходы «больше» и «меньше» третьей и четвертой схем сравнения через второй элемент «ИЛИ» соединены с входом «Не норма 2» блока преобразования и контроля; входы второго элемента «И» соединены с выходами «равенства» третьей и четвертой схем сравнения, а выход второго элемента «И» соединен с входом «Норма» блока преобразования и контроля; выходы блока преобразования и контроля являются информационными выходами устройства и объединены с информационными входами устройства, образуя двунаправленную информационную шину устройства; вход «Чтение» блока преобразования и контроля является входом «Чтение» устройства.

2. Формирователь матричных команд по п. 1, отличающийся тем, что формирователь длительности фронтов матричной команды состоит из элемента «НЕ», первого и второго элементов «2И-НЕ» с открытым стоковым выходом, первого, второго и третьего резисторов, трансформатора, мостового выпрямителя, конденсатора и транзистора; первый вход формирователя матричной команды соединен с первым входом первого элемента «2И-НЕ» и, через элемент «НЕ», с первым входом второго элемента «2И-НЕ», вторые входы первого и второго элементов «2И-НЕ» объединены и являются вторым входом формирователя; выходы элементов «2И-НЕ» соединены через первичные обмотки трансформатора с первым выводом первого резистора, второй вывод которого соединен с шиной питания логических цепей +Uпит; первый вывод вторичной обмотки трансформатора соединен с первым входом мостового выпрямителя; второй вывод вторичной обмотки трансформатора соединен со вторым входом выпрямителя, положительный выход которого через второй резистор соединен с первыми выводами третьего резистора и конденсатора, а также с затвором транзистора; отрицательный выход выпрямителя соединен со вторыми выводами третьего резистора и конденсатора, с истоком транзистора и является выходом формирователя, сток транзистора соединен с коммутируемой шиной +Е.

| ФОРМИРОВАТЕЛЬ МАТРИЧНЫХ КОМАНД | 2013 |

|

RU2540780C2 |

| ФОРМИРОВАТЕЛЬ МАТРИЧНЫХ КОМАНД | 2014 |

|

RU2549123C1 |

| Устройство формирования двухканального широтно-модулированного сигнала | 2015 |

|

RU2613522C1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

2019-12-02—Публикация

2018-11-29—Подача