Изобретение относится к автоматике и вычислительной технике и может быть использовано в сети отображения информации на матричных индикаторах.

Известные технические решения (Яблонский Ф.М. Троицкий Ю.В. Средства отображения информации. М. Высш. шк. 1985, с.162, рис.5.34), включающие асинхронные последовательные во времени способы записи и отображения информации по восьмиразрядным кодам адреса за счет коммутации адресации с произвольной выборкой и выборкой по линейной адресации, способ динамической индикации информации в поле двухкоординатной матрицы с линейной адресацией по адресным импульсам сканирования строк. Устройство содержит блоки памяти, синхронизации, динамической развертки, коммутатор адреса и матричный индикатор.

Недостатками данных технических решений являются низкая яркость при невысокой частоте сканирования, малая надежность из-за асинхронной коммутации информации и ограниченные функциональные возможности, определяемые жесткой структурой устройства.

Известно также устройство для отображения информации (а. с. СССР N 1571645, кл. G 09 G 3/00, 1990), реализующее способ записи и отображения знакографической информации с совмещением во времени построения нескольких строк в зависимости от конфигурации, а также динамическую индикацию матрицы с выводом информации синхронно адресным импульсам сканирования строк. Устройство содержит регистры адреса и знака, блоки алгоритма и развертки, знакогенератор и матричный индикатор.

К недостаткам этих решений относятся узкая специализация из-за жесткого алгоритма работы, низкая яркость за счет индикации с большой скважностью, относительно низкая надежность, определяемая сложной структурой устройства.

За прототип принято устройство для отображения информации (а.с. СССР N 1566404, кл. G 09 G 3/28, 1990), основанное на способе записи и отображения информации, включающем формирование текущих адресов отображения импульсами тактовой частоты, регистрацию информации в коде по внешнему адресу с произвольной выборкой в поле пространственных координат последовательно во времени с динамической индикацией в каждом цикле по прерыванию, динамическую индикацию с линейной адресацией импульсами, формируемыми из разрядов эталонного адреса посредством умножения тактовой частоты. Способ динамической индикации в поле двухкоординатной матрицы с линейной адресацией состоит в каждом адресном цикле из сканирования столбцов и строк матрицы импульсами, формируемыми из старших и младших разрядов эталонного адреса, пропорционально последним вывода порязрядно информации на время формирования текущего адреса. Устройство для записи и отображения информации содержит блок памяти, выход которого соединен с информационным входом регистра, выходы которого поразрядно объединены с горизонтальной шиной матричного индикатора, вертикальные шины которого поразрядно связаны с выходом блока развертки, информационные входы которого подключены к адресным выходам счетчика столбцов и через коммутатор каналов к одноименным входам старших разрядов блока памяти, младшие разряды адреса блока памяти соединены через коммутатор каналов с адресными выходами счетчика строк, связанного тактовым входом с выходом генератора пачки импульсов, управляемого тактовым генератором блока синхронизации, связанного через коммутатор каналов с адресными входами устройства, управляющие входы последнего через блок синхронизации записи связаны со старшими разрядами блока памяти.

Прототипу присущи следующие недостатки: относительно низкая надежность и яркость, неравномерность отображения информации и узкая специализация. Первая группа недостатков определяется коммутацией во времени различных способов адресации: с последовательной и произвольной выборкой информации, причем запись производится от внешнего устройства, а считывание информации в устройстве отображения. Другие недостатки связаны с наличием двух режимов считывания информации и жесткой централизации структуры устройства от внешней системы. Жесткий алгоритм работы устройства не позволяет режима индивидуального пользования, а наличие двух режимов считывания приводит к мерцанию отображения. В прототипе неэффективно используется для индикации время сканирования столбца, в котором от 20 до 40% занимает выборка информации и на столько же снижается яркость и качество отображения информации.

Целью комплекса предложений является повышение яркости и надежности при записи и отображении, также повышение равномерности отображения в процессе динамической индикации и расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что:

в способе записи и отображения информации, включающем формирование кода адреса отображения с периодом импульсов тактовй частоты, регистрацию информации по коду адреса в поле пространственных координат потенциалом логического уровня и копирование регистрируемой информации в поле двухкоординатной матрицы посредством динамической индикации с линейной адресацией импульсами, формируемыми из разрядов кода эталонного адреса, в отличие от известных решений код адреса отображения организуют из импульсов знаков пар позиций мантиссы числа, осуществляют программное управление кодом адреса отображения по числу возможных сочетаний, задаваемых импульсами знака порядка того же числа, сравнивают коды адреса отображения и эталонного адреса, в момент совпадения которых регистрируют потенциал логического уровня в соответствии с импульсами программы знака порядка числа, причем тактовую частоту вывода регистрируемой информации организуют из импульсов старших разрядов кода эталонного адреса;

в способе динамической индикации информации в поле двухкоординатной матрицы с линейной адресацией, включающем в каждом адресном цикле сканирование столбцов и строк матрицы импульсами, формируемыми соответственно из старших и младших разрядов кода эталонного адреса, по которым выводят поразрядно регистрируемую информацию за время длительности импульсов старшего разряда, в отличие от прототипа формируют по числу строк дополнительные импульсы равной длительности, образующие длительность импульса адресного цикла столбца, из которого выделяют первый дополнительный импульс, длительность которого составляют из последовательности длительностей импульсов сканирования строк матрицы;

в устройство для записи и отображения информации с динамической индикацией, содержащее блок памяти, выход которого соединен с информационным входом регистра, выходы которого поразрядно объединены с горизонтальной шиной матричного индикатора, вертикальные шины которого поразрядно связаны с выходами блока развертки, информационные входы которого подключены к адресным выходам счетчика столбцов и одноименным входам старших разрядов блока памяти, младшие разряды адреса которого соединены с адресными выходами счетчика строк, связанного тактовым входом с первым выходом генератора импульсов, в отличие от прототипа введены микрокалькулятор, блок микропрограммного управления, компаратор и счетчик синхронизации, включенный между счетчиками строк и столбцов, а выходом синхронизации связанный с одноименными входами микрокалькулятора и регистра, тактовый вход которого соединен с первым выходом генератора импульсов, подключенного к шине фаз микрокалькулятора, входы которого являются информационными, диалоговыми и адресными входами устройства, а информационная шина объединена с одноименными шинами компаратора и блока микропрограммного управления, подключенного тактовым входом к выходу синхронизации микрокалькулятора, а управляющими выходами соответственно со входами выбора кристалла компаратора и информации блока памяти, вход записи последнего связан с выходом компаратора, адресные входы которого объединены с одноименными разрядами блока памяти.

При анализе известных технических решений не обнаружены решения, имеющие признаки, сходные с совокупностью отличительных признаков заявляемых решений.

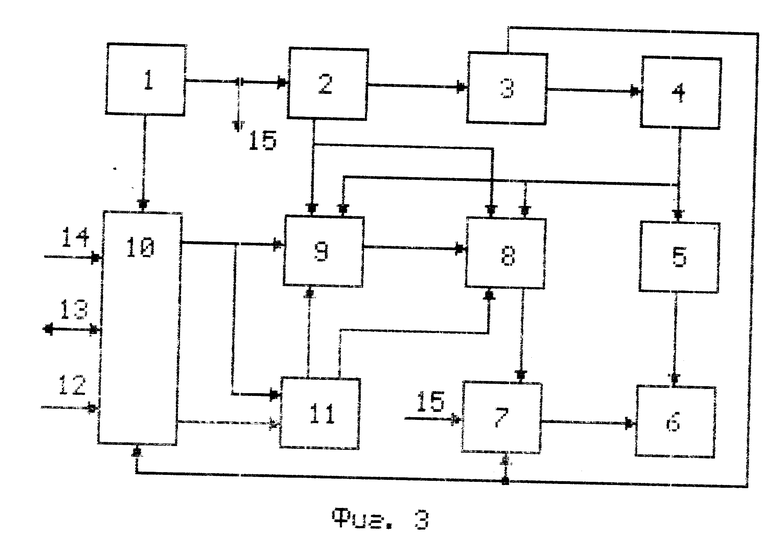

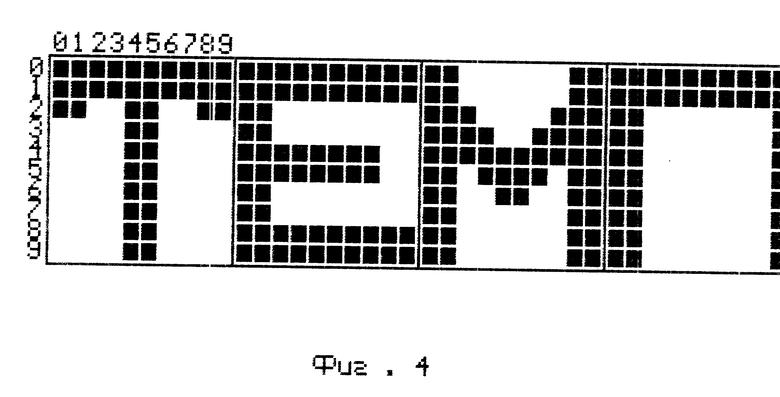

На фиг. 1,2 приведены временные диаграммы, поясняющие сущность способа записи и отображения информации, а также динамическую индикацию; на фиг.3 - структурная схема устройства.

Устройство состоит из последовательного включения генератора импульсов 1, счетчика строк 2, синхронизации 3, столбцов 4, блока развертки 5, матричного индикатора 6, и регистра 7 строк (горизонтальных шин). Кроме них в устройство входят блок 8 памяти, цифровой компаратор 9, микрокалькулятор 10 и блок 11 микропрограммного управления. Блок 11 выполнен на кольцевом включении регистра признаков и постоянного запоминающего устройства, управляемого по младшим адресам счетчиком, который синхронизируется дешифратором нуля. Информационные входы регистра и дешифратора блока 11 объединены с одноименными выходами микрокалькулятора, выход синхронизации которого связан со счетным входом счетчика блока 11. Выходы управления блока 11 являются выходами постоянного запоминающего устройства, в котором "прошиваются" программы кода знака порядкового числа. Число программ определяется числом возможных сочетаний позиций адресов мантиссы числа. Например, программируемый микрокалькулятор "Электроника МК-46" оперирует числом с мантиссой из восьми декад и показателем знака порядка из двух декад. Восьмидекадная мантисса числа делится на четыре пары позиций, составляющих четыре двухдекадных адреса A=Y, X} Включение или выключение адреса задается знаком порядка числа. Знак порядка числа изменяется программно или в диалоговом режиме оператором в диапазоне 00-15, что соответствует числу сочетаний для четырех позиций или четырехвходовой таблице истинности на 16 состояний. Единичный и нулевой термы поставлены в соответствие индикации и гашению адреса указанного знакоместа в мантиссе числа. Для определенности по значению знака порядка00} (код 0000) гасятся все адреса, записанные с 1 по 4 знакоместо;05} (код 1010) включаются первая и третья пары, а вторая и четвертая гасятся;10} (код 0101) - индицируют адреса второй и четвертой пар, а первая и третья выключаются;15} (код 1111) на матричный индикатор выводятся адреса всех четырех знакомест мантиссы числа.

Вводится информация в устройство через микрокалькулятор 10 в автоматическом и диалоговом режимах посредством управления по адресным 12, диалоговым 13 и информационным 14 входам. Информационный вход 14 объединен с информационной магистралью микрокалькулятора 10 через мильтиплексор, коммутируемый по адресным входам 12 с центрального пульта сети. Обмен информацией осуществляется с прямым доступом в кольцо оперативной памяти микрокалькулятора и не превышает для МК-46, например, 0,02 с, что на четыре порядка меньше времени вывода информации из микрокалькулятора. В диалоговом режиме информация в микрокалькуляторе 10 изменяется оператором по шине 13 через контрактуру с контролем по цифровому индикатору. Наличие в устройстве микрокалькулятора 10 позволяет решать самостоятельные задачи посредством модификации адресов по алгоритмическим программам и осуществлять циклические опросы адресного банка без "мелочной опеки" центрального пульта сети.

Информация из микрокалькулятора 10 выводится синхронно импульсом, поступающим с выхода счетчика 3 на соответствующий вход, связанный с интерфейсной схемой К145ИК1801 и появляется на ее выходе в двоично-десятичном коде потетрадно. Для организации двухпозиционного адреса с информационной шины микрокалькулятора 10 в блоки 9 и 11 вводится информация по байтам. Для этого в блоке 11 регистр выполнен двухдекадным, а преобразование на первых входах компаратора осуществляется дополнительным буферным регистром, управляемым по входу предварительной записи импульсами с блока 11. При модификации адресов микрокалькулятором 10 по программе на время вычисления тактовые импульсы со входа синхронизации блокируются, и информация на выход не поступает. Информация из микрокалькулятора 10 выводится циклически за 14 тактов, соответствующих 12 тактов числу и 2 такта служебной информации. Значимым из служебных кодов является код установки порядка (1111), обнуляющий через дешифратор счетчик блока микропрограммного управления 11. Число из микрокалькулятора 10 поступает последовательно во времени, начиная со знака порядка и заканчиваясь младшей позицией мантиссы. Распределением значащей информации занимается по программе блок 11. Текущая программа задается знаком порядка числа, код которого загружается в регистры блока 11 в начале каждого цикла. На адресных входах ПЗУ формируется полный код, состоящий из младших адресов счетчика и старших регистра блока 11. В соответствии с выбранной программой на выходах ПЗУ блока 11 генерируются управляющие импульсы, определяющие алгоритм работы блоков 8 и 9. С выхода микрокалькулятора 10 вслед за знаком порядка поступают адреса, указанные в мантиссе числа.

На фиг. 1а приведен фрагмент записи адресов в блоке 8 памяти на примере мантиссы 99 46 73 28 со знаком порядка 10. Текущий код адреса отображения на фиг. 1а изображен в виде ступенек, так как по оси ординат отложен вес кода, который изменяется на выходе микрокалькулятора 10 каждым тактовым импульсом. На этой же временной диаграмме показано изменение кода эталонного адреса в виде пилы, который воздействует на адресные входы блока 8 памяти, а также вторые входы цифрового компаратора 9. Инициирование компаратора 9 производится импульсами с блока 11 при формировании на его информационных входах байта кода адреса отображения. Компаратор 9 сравнивает текущий код адреса отображения с эталонным кодом адреса, изменяющимся цикличным по линейному закону. При совпадении кодов адресов на выходе компаратора появляется импульс (фиг.1б), воздействующий на вход "запись" блока 8 в памяти. Одновременно на его информационный вход воздействуют потенциалы импульса знака порядка (фиг. 1в), в приведенном примере код (0101). При наличии нулевого потенциала по адресу числа в блоке 8 памяти регистрируется логический нуль, в противном случае логическая единица (фиг.1г). Например, в первом состоянии по адресу 99 фиксируется логический нуль, во втором состоянии по адресу 46 регистрируется логическая единица, в третьем состоянии обнуляется адрес 73, а в четвертом состоянии копируется логическая единица по адресу 28. Преобразование кода адреса отображения производится в фазоимпульсной форме синхронно с выводом информации из микрокалькулятора 10 и копированием информации на матричный индикатор 6. Информация, записанная в блоке 8 памяти, в каждом цикле копируется на индикатор 6, а изменяется при появлении текущего кода адреса отображения на выходах микрокалькулятора 10. Гальваническая развязка между текущим и эталонным кодами адреса повышает надежность копирования и программного совмещения различных способов адресации информации.

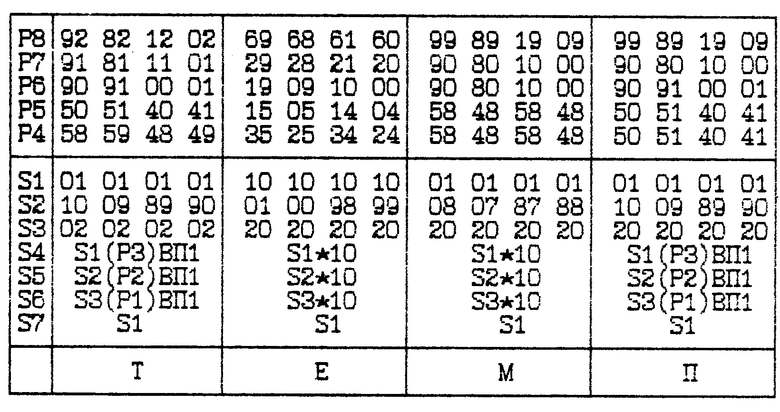

Копирование информации в поле двухкоординатной матрицы 6 осуществляется посредством динамической индикации с линейной адресацией импульсами, формируемыми из кода эталонного адреса на выходах счетчиков строк 2, синхронизации 3 и столбцов 4. Способ динамической индикации включает в каждом адресном цикле T tm2n сканирования столбцов  и строк

и строк  матрицы 6 импульсами, формируемыми из IJ-тых разрядов кода эталонного адреса. Блок 5 развертки инициирует включение J-го столбца (фиг. 2а) матрицы 6 посредством преобразования в позиционный двоично-десятичного кода на выходе счетчика 4. Блок 5 развертки состоит из дешифратора столбцов и токовых ключей. Импульсы сканирования столбцов генерируются из кодов старшего адреса Y, составляющих цикл индикации информации. Адресный цикл столбца составляют импульсы синхронизации (фиг.2б), поступающие на вход счетчика 4 столбцов с выхода счетчика 3. На другом выходе счетчика 3 формируется в каждом J цикле знакоместо первого импульса (фиг. 2в) длительностью T/nm. Эти импульсы используются для синхронизации вывода информации из микрокалькулятора для перезаписи информации из блока 8 памяти в регистр 7 строк. За время воздействия синхронизирующего импульса тактовыми импульсами по входу 15 в регистр 7 загружается регистрируемая информация о выходе блока 8 за счет структурного сдвига. Таким образом, информация на горизонтальных шинах индикатора 6 появляется в знакоместе первого импульса синхронизации адресного цикла столбцов, причем загрузка регистра 7 строк осуществляется синхронно адресным импульсам сканирования строк (фиг. 2г-ж) счетчика 2. Индикация информации на матрице 6 происходит в течение всего адресного цикла столбца за вычетом времени первого знакоместа, это исключает неравномерность отображения информации как при записи, так и при копировании. На индикатор 6 информация выводится по столбцам с разверткой изображения блоком 5.

матрицы 6 импульсами, формируемыми из IJ-тых разрядов кода эталонного адреса. Блок 5 развертки инициирует включение J-го столбца (фиг. 2а) матрицы 6 посредством преобразования в позиционный двоично-десятичного кода на выходе счетчика 4. Блок 5 развертки состоит из дешифратора столбцов и токовых ключей. Импульсы сканирования столбцов генерируются из кодов старшего адреса Y, составляющих цикл индикации информации. Адресный цикл столбца составляют импульсы синхронизации (фиг.2б), поступающие на вход счетчика 4 столбцов с выхода счетчика 3. На другом выходе счетчика 3 формируется в каждом J цикле знакоместо первого импульса (фиг. 2в) длительностью T/nm. Эти импульсы используются для синхронизации вывода информации из микрокалькулятора для перезаписи информации из блока 8 памяти в регистр 7 строк. За время воздействия синхронизирующего импульса тактовыми импульсами по входу 15 в регистр 7 загружается регистрируемая информация о выходе блока 8 за счет структурного сдвига. Таким образом, информация на горизонтальных шинах индикатора 6 появляется в знакоместе первого импульса синхронизации адресного цикла столбцов, причем загрузка регистра 7 строк осуществляется синхронно адресным импульсам сканирования строк (фиг. 2г-ж) счетчика 2. Индикация информации на матрице 6 происходит в течение всего адресного цикла столбца за вычетом времени первого знакоместа, это исключает неравномерность отображения информации как при записи, так и при копировании. На индикатор 6 информация выводится по столбцам с разверткой изображения блоком 5.

Покажем эффективность предлагаемых технических решений по отношению к прототипу.

1. Время индикации столбца в прототипе и в предлагаемых решениях соответственно составляет t1i kT/mn и t2i (i/nm2+(m-1)/nm)T. Учитывая, что время индикации m строк определяется как

Поделив t2 на t1, определим эффективность η по времени индикации и яркости:

h = (m-1/2)/k.

Для прототипа k=6-8 и для m=10 видно, что предлагаемое решение в 1,2-1,6 раза индицирует ярче прототипа.

2. Из-за двух режимов адресации в прототипе "k" принимает значение 8 для линейной адресации и 6 при адресации с произвольной выборкой, при этом яркость от режима к режиму изменяются в 1,3 раза. В предлагаемом решении время индикации t2i лежит в пределах (9,0-9,9)•0,01T, так как  и остается постоянным в каждом цикле на интервале 0,09T, что на практике соответствует равномерной яркости.

и остается постоянным в каждом цикле на интервале 0,09T, что на практике соответствует равномерной яркости.

3. Надежность прототипа ниже надежности предлагаемых решений из-за наличия в прототипе двух режимов адресации: по линейному закону и с произвольной выборкой, которые изменяются посредством коммутатора 9 адреса. С учетом того, что надежность определяется числом позиций адреса (n+m) и числом режимов адресации, находим для предлагаемого решения P1 = P

ηp = P1/P2 = P

Таким образом, надежность прототипа в P

4. Гибкость и автономность предлагаемых решений выше прототипа из-за введения в устройство микрокалькулятора, децентрализующего устройство отображения от центрального пульта сети. Кроме автоматического режима добавляется диалоговый режим, что значительно расширяет функциональные возможности. Программное управление позволяет модифицировать информацию по заданным алгоритмам, а использование в устройстве знакогенератора организует режим бегущей строки. При этом центральный пульт может обслуживать дополнительное число периферийных устройств.

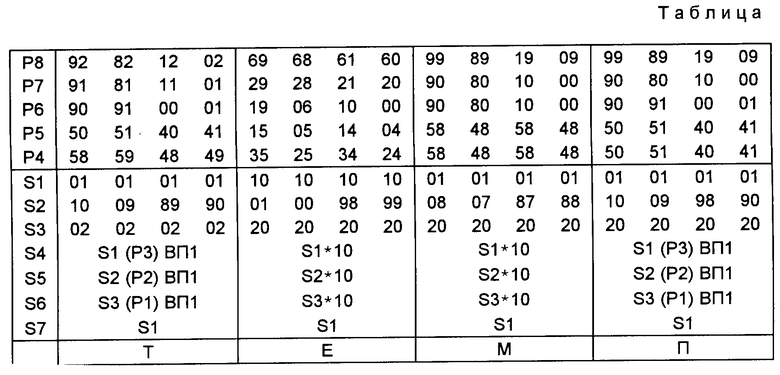

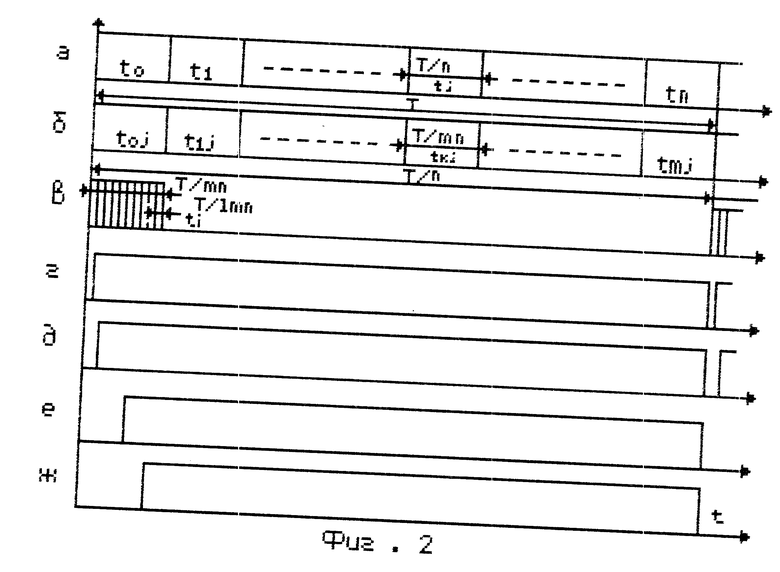

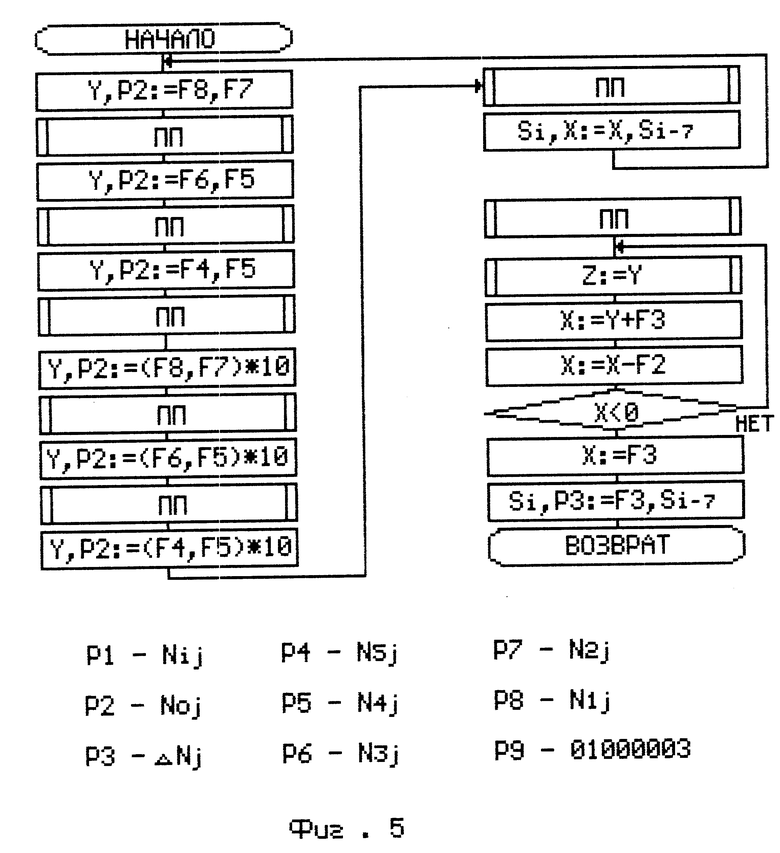

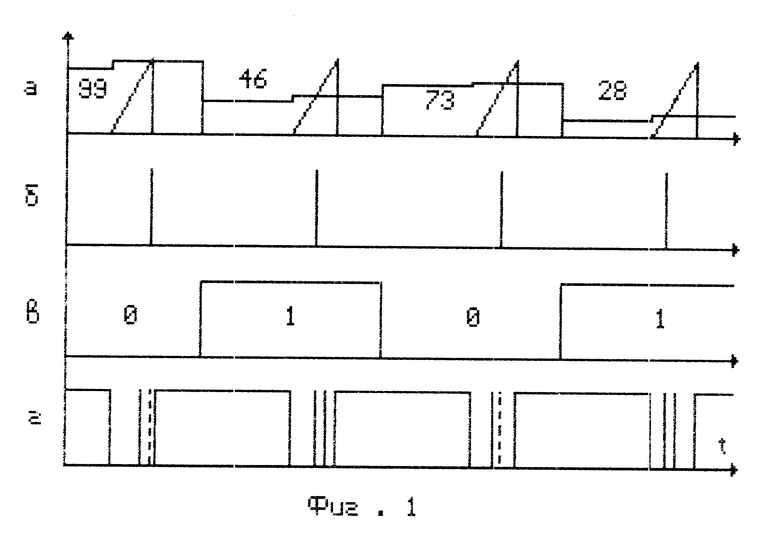

Программное обеспечение устройства рассмотрим на примере алгоритмической знакосинтезирующей программы, мнемосхема ТЕМП приведена на фиг.4, а на фиг.5 показана структурная схема программы. Программа позволяет моделировать буквы русского и латинского алфавита, римские и арабские цифры. Алгоритм программы состоит из шести блоков, первая половина которых осуществляет последовательное во времени включение адресов индикаторов знаков, а вторая половина их включение в той же последовательности. Каждая половина включает три блока, организующие вертикальное, диагональное и горизонтальное управление координатами. Вектор управления задается начальными координатами Nij, приращением ΔNi и конечного адреса N0j. В цикле подпрограммы координаты Nij модифицируются на шаг приращения посредством алгебраического сложения Nij:Nij + ΔNi. Приращение для каждого вида управления хранится в стекловой памяти Si, а опорные координаты вектора загружаются попарно в регистровую память Pi (см. таблицу).

В каждом цикле подпрограммы сравниваются модифицированные Nij и опорный NOi адреса. До тех пор, пока NOi > Nij адреса модифицированных координат выводятся на матричный индикатор, в противном случае заканчивается очередной цикл управления и после загрузки других значений NOj и Nij с Ni продолжается следующий этап. Включение координат осуществляется по коду (1111), что соответствует числу 92 82 12 02 • 1047, при этом знак порядка соответствует 54 степени. Выключение происходит по коду (0000) при модификации степени числа на 10, т.е. знак порядка равен 55 степени. Например, буква Т начинает вводиться с координат 92 82 12 02 с приращением 01 01 01 01 до уровня 91 81 11 01, что соответствует организации торцов верхней перекладины. На втором этапе строится верхняя перекладина буквы от координат 90 91 00 01 до 50 51 40 41 с шагом 10 09 89 90. Третий этап конструирует вертикальную планку буквы от координат 50 51 40 41 до 58 59 48 49 с модификацией каждого адреса на 2 единицы соответственно числу 02 02 02 02. В следующие три этапа вышеописанным способом последовательно во времени выключаются те же координаты и процесс начинается снова. Для четырех устройств, связанных с центральным пультом в сеть на панно последовательно во времени выводится транспарант ТЕМП (фиг.4).

Предлагаемые технические решения реализованы в калькуляторном учебном классе ТЕМП-091. Устройства отображения созданы на базе микрокалькуляторов "Электроника МК-46" с применением интегральных схем серии К564, матричные индикаторы выполнены разрядностью 10•10 на тиратронах МТХ-90 в размер стандартного листа формата А1. Индикаторная панель состоит из четырех матричных индикаторов, ведомых автономными периферийными устройствами, включенными в сеть класса. Индикаторная панель расположена над письменной доской и позволяет наглядно отображать процессы и объекты на мнемосхемах в поле пространственных, временных и функциональных координат.

Калькуляторный класс ТЕМП-091 внедрен в школе N 13 г.Тамбова филиале ТИХМа для изучения основ кибернетики.

Таким образом, программное управление кодом адреса отображения, включающем позиции мантиссы числа, посредством потенциалов импульсов знака порядка, копирование регистрируемой информации в момент первого знакоместа адреса столбца, использование микрокалькулятора, блока микропрограммного управления и компаратора, в отличие от известных решений повышает яркость, надежность и равномерность отображения, расширяет функциональные возможности устройства и автономию периферии за счет разгрузки и децентрализации информационной сети. Это позволяет создавать калькуляторные видеоклассы для коллективного и индивидуального обучения основам гуманитарных, естественных и технических дисциплин.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕНАЖЕР МНЕМОСХЕМ | 1990 |

|

RU2101772C1 |

| ТРЕНАЖЕР МНЕМОСХЕМ | 1994 |

|

RU2116674C1 |

| СПОСОБ КОМПЛЕКСНОГО ОПРЕДЕЛЕНИЯ ТЕПЛОФИЗИЧЕСКИХ ХАРАКТЕРИСТИК МАТЕРИАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2027172C1 |

| ТРЕНАЖЕР ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ МАТРИЦ | 1990 |

|

RU2102792C1 |

| СПОСОБ ОБМЕНА ИНФОРМАЦИИ В МИКРОКАЛЬКУЛЯТОРНОЙ СЕТИ И МИКРОКАЛЬКУЛЯТОРНАЯ СЕТЬ ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2015545C1 |

| Осциллограф с матричным экраном | 1983 |

|

SU1129529A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

| Устройство для отображения информации | 1987 |

|

SU1443024A1 |

| Устройство для отображения информации | 1982 |

|

SU1084868A1 |

| Устройство для проверки электрического монтажа | 1986 |

|

SU1336035A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в сети отображения информации на матричных индикаторах. Изобретение позволяет повысить яркость, надежность и равномерность отображения информации. Устройство содержит генератор 1 импульсов, счетчик 2 строк, счетчик 3 синхронизации, счетчик 4 столбцов, блок 5 развертки, матричный индикатор 6, регистр 7 строк, блок 8 памяти, цифровой компаратор 9, микрокалькулятор 10, блок 11 микропрограммного управления. 1 табл., 5 ил.

Устройство для записи и отображения информации, содержащее блок памяти, выход которого соединен с информационным входом регистра, выходы которого поразрядно объединены с горизонтальной шиной матричного индикатора, вертикальные шины которого поразрядно связаны с выходами блока развертки, информационные входы которого подключены к адресным входам счетчика столбцов и одноименным входам старших разрядов адреса блока памяти, вход младших разрядов адреса которого соединен с адресными выходами счетчика строк, связанного тактовым входом с первым выходом генератора импульсов, отличающееся тем, что в него введены микрокалькулятор, блок микропрограммного управления, компаратор и счетчик синхронизации, счетный вход которого соединен с выходом переноса счетчика строк, адресный выход счетчика синхронизации соединен с адресным входом счетчика столбцов, выход переполнения счетчика синхронизации соединен с входами синхронизации микрокалькулятора и регистра, тактовый вход которого соединен с первым выходом генератора импульсов, второй выход которого соединен с шиной фаз микрокалькулятора, с первого по третий входы которого являются информационными, диалоговыми и адресными входами устройства соответственно, информационная выходная шина микрокалькулятора объединена с одноименными шинами компаратора и блока микропрограммного управления, тактовый вход которого подключен к выходу синхронизации микрокалькулятора, первый и второй выходы блока микропрограммного управления соединены соответственно с входом выбора кристалла компаратора и информационным входом блока памяти, вход записи которого соединен с выходом компаратора, управляющие входы которого объединены с адресными входами блока памяти.

| SU, авторское свидетельство, 1571645, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| SU, авторское свидетельство, 1566404, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1998-01-10—Публикация

1992-05-07—Подача