Данное изобретение относится к вычислительной технике и автоматике, может быть использовано в устройствах ввода в ответственной аппаратуре, например, для космических аппаратов.

Известно устройство приема сигналов командной матрицы и преобразование в позиционный код, содержащее матрицу коммутационных элементов, реле которых включены через развязывающий диод в перекрестие коммутируемых шин матрицы, а контакты этих реле являются информационными выходами устройства. Причем потенциалы строк и столбцов в командной матрице имеют разную полярность (В.Н.Рогинский «Построение релейных схем управления». М.: Энергия, 1964, стр.247, рис.8.8а).

Данное устройство не требует дешифратора, однако имеет большое количество используемых элементов (реле, развязывающие диоды, шунтирующие реле диоды) N=3(n×m), где n - число строк, m - число столбцов в коммутируемых шинах, что делает устройство громоздким.

Известно устройство для ввода информации, содержащее матрицу коммутационных элементов с горизонтальными (строками) и вертикальными (столбцами) шинами, регистр, информационные входы которого через блок согласования подключены к матрице коммутационных элементов, выходы регистра являются информационными выходами устройства, генератор импульсов, а каждый коммутационный элемент матрицы содержит полевой транзистор, канал которого включен в перекрестие шин матрицы коммутационных элементов, а затвор подключен к сенсорной площадке и через ограничительный элемент соединен с первым выходом генератора импульсов, второй выход которого соединен с синхровходом регистра (А.С. №1462284 G06F 3/02, автор О.Н.Мацкевич).

Недостатком данного устройства является большое количество используемых коммутационных элементов (транзисторов и резисторов) N=n×m, где n - число строк, m - число столбцов. Так при n=m=16 число транзисторов и резисторов будет составлять 256 штук каждого. А также устройство нельзя использовать в случае, когда строки и столбцы выдаются напряжением разной полярности.

Наиболее близким к предлагаемому по технической сущности является устройство для ввода информации, содержащее матрицу коммутационных элементов с выходными шинами и с первой и второй группами входных шин, генератор импульсов, выход которого соединен с первым входом элемента И, триггер, выход которого является первым выходом устройства, первый и второй блоки памяти, сдвигающий регистр и элемент ИЛИ, выход которого соединен с вторым входом элемента И и с первыми входами первого и второго блоков памяти, вторые входы которых соединены и являются входом устройства, третий вход первого блока памяти соединен с входами элемента ИЛИ и с выходными шинами матрицы коммутационных элементов, входные шины первой и второй групп которой соединены с третьим и четвертым входами второго блока памяти, выход которого является вторым выходом устройства, выход первого блока памяти является третьим выходом устройства, первый вход сдвигающего регистра соединен с выходом элемента И, выходы сдвигающего регистра соединены с входными шинами первой и второй групп матрицы коммутационных элементов, первая шина первой группы входных шин соединена с первым входом триггера, второй вход которого соединен с первой шиной второй группы входных шин (А.С №964618, G06F 3/02).

Данное устройство взято за прототип.

Недостатком данного устройства является медленный процесс ввода информации за счет последовательного сдвига счетных импульсов в регистре, зависящий от числа вертикальных шин (столбцов) в матрице. Кроме того, это устройство нельзя использовать в случае, когда горизонтальные (строки) и вертикальные (столбцы) шины выдаются напряжением разной полярности.

Целью изобретения является устранение указанных недостатков.

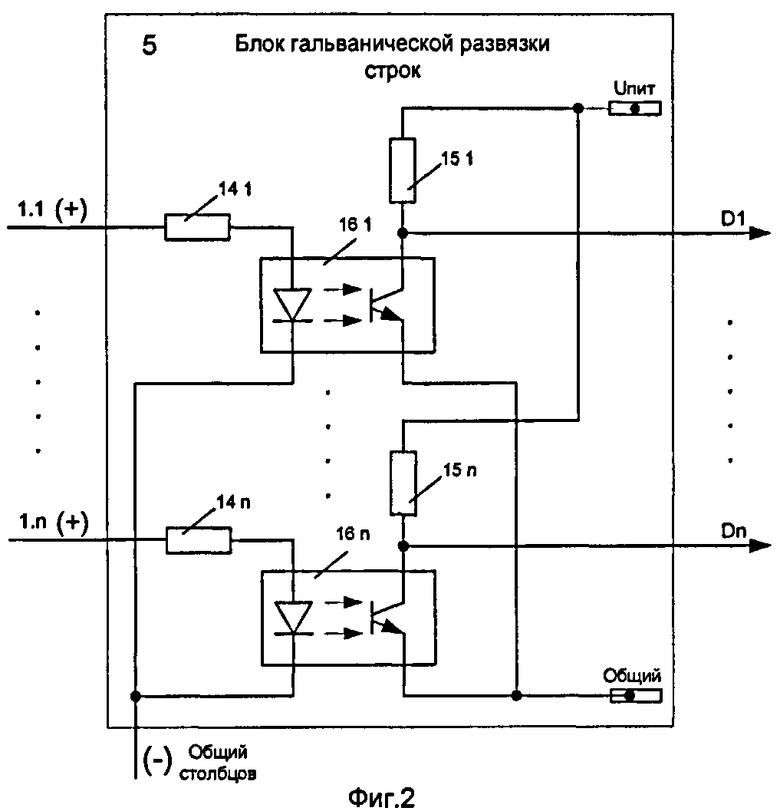

Поставленная цель достигается тем, что в устройство, содержащее первую и вторую группу шин, первый и второй блоки памяти, введены блок гальванической развязки строк, блок гальванической развязки столбцов, первая и вторая группа диодов, формирователь наличия матричной команды, формирователь сигнала «Запись», блок преобразования, горизонтальные коммутируемые шины соединены с соответствующими положительными входами блока гальванической развязки строк и соответствующими анодами диодов первой группы диодов, вертикальные коммутируемые шины соединены с соответствующими отрицательными входами блока гальванической развязки столбцов и соответствующими катодами диодов второй группы диодов, катоды первой группы диодов, объединенные положительные входы блока гальванической развязки столбцов и положительный вход формирователя наличия матричной команды объединены, аноды второй группы диодов, объединенные отрицательные входы блока гальванической развязки строк и отрицательный вход формирователя наличия матричной команды объединены, выходы блока гальванической развязки строк соединены с информационными входами первого блока памяти, выходы блока гальванической развязки столбцов соединены с информационными входами второго блока памяти, информационные выходы первого и второго блока памяти поразрядно объединены и поразрядно соединены с информационными входами блока преобразования, выход формирователя наличия матричной команды соединен с входом формирователя сигнала «Запись», выход которого соединен с входом «Запись» первого и второго блока памяти и с входом «Пуск» блока преобразования, первый выход «Чтение» и второй выход «Чтение» блока преобразования соединены с входом «Чтение» первого и второго блока памяти соответственно, выход «Установка в исходное» блока преобразования соединен с входом «Установка в исходное» первого и второго блока памяти, информационные и сигнальный выходы блока преобразования являются информационными и сигнальным выходами устройства соответственно.

На чертеже (фиг.1) представлена функциональная схема устройства для ввода сигналов командной матрицы.

Устройство для ввода сигналов командной матрицы содержит горизонтальные коммутируемые шины 1 (1.1-1.n), вертикальные коммутируемые шины 2 (2.1-2.m), первую группу диодов 3 (V1-Vn), вторую группу диодов 4 (V1-Vm), блок гальванической развязки строк 5, блок гальванической развязки столбцов 6, формирователь наличия матричной команды 7, формирователь сигнала «Запись» 8, первый блок памяти 9, второй блок памяти 10, блок преобразования 11, информационные выходы 12 устройства, сигнальный выход 13 устройства.

Первый блок памяти и второй блок памяти имеют информационные входы, обозначенные «D», вход «Запись», «Чтение», «Установка в исходное», обозначенные соответственно «WR», «RD», «R».

Блок преобразования имеет информационные и сигнальный выходы, которые являются информационным выходом 12 устройства и сигнальным выходом 13 устройства соответственно. Кроме того, блок преобразования имеет первый выход «Запись», второй выход «Запись», выход «Установка в исходное», обозначенные «RD1», «RD2», «R» соответственно.

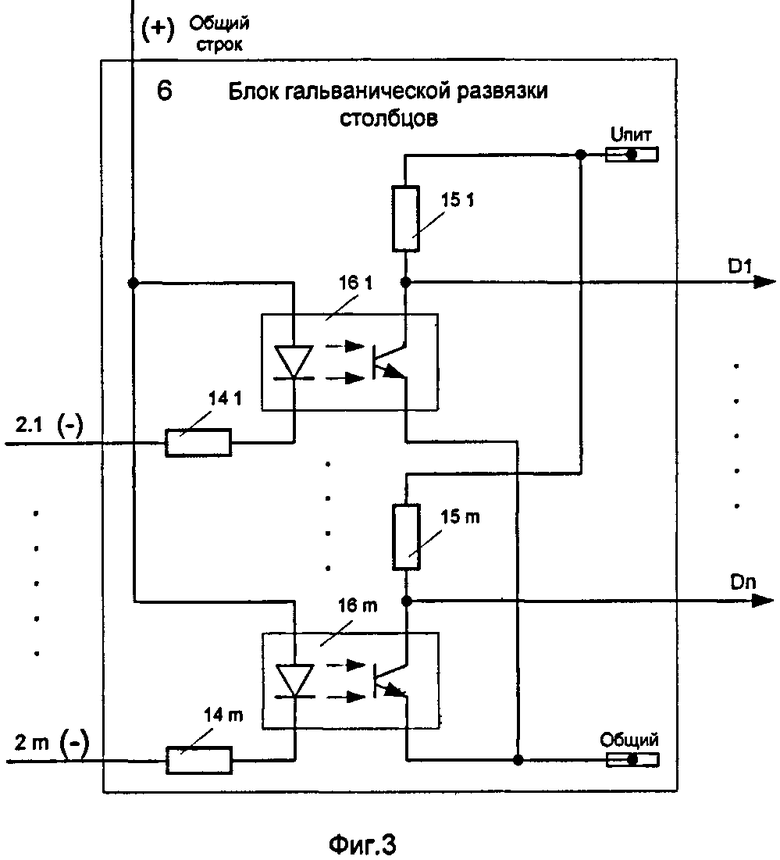

Блок гальванической развязки строк 5 (фиг.2) предназначен для гальванической развязки и согласования уровней коммутируемых шин с уровнями логических цепей и состоит из n ячеек с входами 1.1-1.n, соответствующими горизонтальным коммутируемым шинам, в каждую из ячеек входят соответственно первый 14 и второй 15 резисторы и транзисторная оптопара 16. Первые резисторы 14.1-14.n являются токозадающими для входных цепей оптопар 16.1-16.n, а вторые резисторы 15.1-15.n являются нагрузкой выходных транзисторов оптопар 16.1-16.n соответственно.

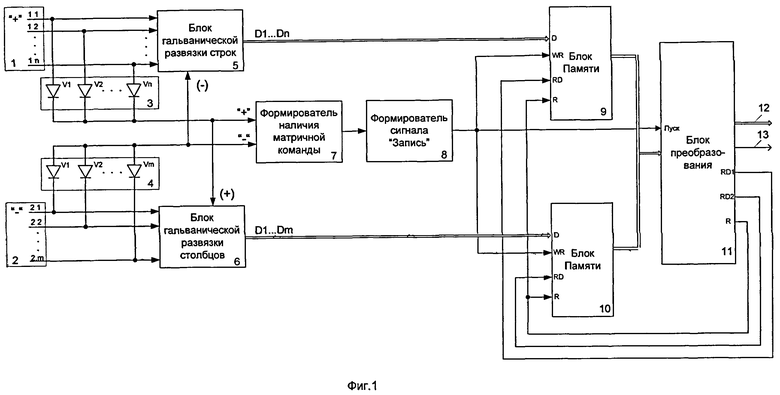

Блок гальванической развязки столбцов 6 (фиг.3) предназначен для гальванической развязки и согласования уровней коммутируемых шин с уровнями логических цепей и состоит из m ячеек с входами 2.1-2.m, соответствующими вертикальным коммутируемым шинам, в каждую из ячеек входят соответственно первый 14 и второй 15 резисторы и транзисторная оптопара 16. Первые резисторы 14.1-14.m являются токозадающими для входных цепей оптопар 16.1-16.m, а вторые резисторы являются нагрузкой выходных транзисторов оптопар 16.1-16.m соответственно.

Устройство работает следующим образом.

Матричная команда на устройство поступает напряжением положительной полярности на одну из горизонтальных (строк) и отрицательной полярности на одну из вертикальных (столбцов) коммутируемых шин, причем очередность поступления не имеет значения. Например, поступила команда К13, тогда положительный потенциал поступает на первую горизонтальную шину 1.1, а отрицательный потенциал поступает на третью вертикальную шину 2.3. Положительный потенциал с горизонтальной шины 1.1 поступает на соответствующий вход блока гальванической развязки строк 5, через диод V1 первой группы диодов 3 поступает на положительный вход формирователя наличия матричной команды 7 и запитывает блок гальванической развязки столбцов 6, а отрицательный потенциал с вертикальной шины 2.3 поступает на соответствующий вход блока гальванической развязки столбцов 6, через диод V3 второй группы диодов 4 поступает на отрицательный вход формирователя наличия матричной команды 7 и запитывает блок гальванической развязки строк 5. Таким образом, через резистор 14.1 и светодиод транзисторной оптопары 16.1 первой ячейки блока гальванической развязки строк 5, а также через резистор 14.3 и светодиод транзисторной оптопары 16.3 блока гальванической развязки столбцов 6 протекает ток, за счет которого откроются соответствующие транзисторные оптопары и соответственно на первом выходе блока гальванической развязки строк 5 и на третьем выходе блока гальванической развязки столбцов 6 появятся логические «1». Наличие отрицательного и положительного потенциала на входах формирователя наличия матричной команды 7 вызовет появление на его выходе логической «1», которая поступает на вход формирователя сигнала «Запись» 8. Формирователь сигнала «Запись» 8 сформирует импульс наличия команды в командной матрице, который запишет логическую «1» в первый разряд первого блока памяти 9 и в третий разряд второго блока памяти 10 и запустит программу съема и обработки информации в блоке преобразования 11, которая последовательно сформирует сигнал на выходе RD1 блока преобразования 11 и считает данные с первого блока памяти 9, затем сформирует сигнал на выходе RD2 блока преобразования 11 и считает данные со второго блока памяти 10 и проведет необходимые преобразования в заданный код, например, в позиционный код, тогда на информационном выходе 12 устройства появится команда K13. После завершения формирования длительности команды с выхода R блока преобразования 11 поступает сигнал на установку в исходное состояние первого 9 и второго 10 блоков памяти.

Блок преобразования 11 выполнен на контроллере, что позволяет осуществлять преобразование матричных команд в необходимый код программно. Кроме того, блок преобразования осуществляет внутренний контроль исправности, так, например, при выдаче любой одиночной матричной команды наличие логической «1» в нескольких разрядах первого блока памяти 9 или второго блока памяти 10 будет признаком неисправности, запрещающим преобразование в блоке преобразования 11 и, который сформирует сигнал на сигнальном выходе 13, сигнализирующий о неисправности. Таким образом, функционально блок преобразования служит для преобразования матричных команд в необходимый код, контроля исправности и управления устройством ввода сигналов командной матрицы.

В упрощенном виде в качестве блока преобразования может быть использована программируемая логическая интегральная схема (ПЛИС) или комбинационная логика на интегральных микросхемах, где, например, для преобразования в позиционный код можно использовать N двухвходовых элементов И, подключенных к выходам первого блока памяти 9 и второго блока памяти 10, при этом N=n×m (n - число строк, m - число столбцов).

Формирователь наличия матричной команды может быть выполнен на транзисторной оптопаре с токозадающим резистором для входной цепи оптопары и резистором нагрузки для выходного транзистора оптопары аналогично ячейке блока гальванической развязки строк (фиг.2).

Формирователь сигнала «Запись» может быть выполнен на двоичном счетчике и осуществляет формирование импульсного сигнала «Запись», а также защиту от коротких помех в горизонтальных (строках) и вертикальных (столбцах) коммутируемых шинах.

Данное устройство предполагается использовать в аппаратуре управления космических аппаратов. Опытный образец выполнен на интегральных микросхемах серии 1554, транзисторных оптопарах 249КП1С и диодных матрицах 2ДС627А. В качестве блока памяти использовались параллельные регистры серии 1554.

Из известных авторам источников информации и патентных материалов не известна совокупность признаков, сходных с совокупностью признаков заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь матричных команд | 2018 |

|

RU2707913C1 |

| ФОРМИРОВАТЕЛЬ МАТРИЧНЫХ КОМАНД | 2013 |

|

RU2540780C2 |

| ФОРМИРОВАТЕЛЬ МАТРИЧНЫХ КОМАНД | 2014 |

|

RU2549123C1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2003 |

|

RU2263345C2 |

| Матричное устройство выдачи команд с оптической развязкой | 2016 |

|

RU2628911C1 |

| ЦЕНТРАЛИЗОВАННАЯ ДИСПЕТЧЕРСКАЯ СИСТЕМА С РАСПРЕДЕЛЕННЫМИ КОНТРОЛИРУЕМЫМИ ПУНКТАМИ | 2003 |

|

RU2240245C1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| Устройство управления процессом сортировки почтовой корреспонденции | 1987 |

|

SU1570801A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ | 1996 |

|

RU2106679C1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

Изобретение относится к вычислительной технике и автоматике. Техническим результатом является возможность преобразования матричных команд в код, когда строки и столбцы выдаются напряжением разной полярности. В устройство, содержащее n горизонтальных и m вертикальных коммутируемых шин, первый и второй блоки памяти, введены блок гальванической развязки строк, блок гальванической развязки столбцов, первая и вторая группа диодов, формирователь наличия матричной команды, формирователь сигнала «Запись», блок преобразования. Преобразование матричных команд в необходимый код осуществляется программно. 3 ил.

Устройство для ввода сигналов командной матрицы, содержащее первую и вторую группу шин, первый и второй блоки памяти, отличающееся тем, что в него введены блок гальванической развязки строк; блок гальванической развязки столбцов; первая и вторая группа диодов, содержащие пит диодов соответственно; формирователь наличия матричной команды; формирователь сигнала «Запись»; блок преобразования; горизонтальные коммутируемые шины соединены с соответствующими положительными входами блока гальванической развязки строк и соответствующими анодами диодов первой группы диодов, вертикальные коммутируемые шины соединены с соответствующими отрицательными входами блока гальванической развязки столбцов и соответствующими катодами диодов второй группы диодов; катоды первой группы диодов, объединенные положительные входы блока гальванической развязки столбцов и положительный вход формирователя наличия матричной команды объединены; аноды второй группы диодов, объединенные отрицательные входы блока гальванической развязки строк и отрицательный вход формирователя наличия матричной команды объединены; выходы блока гальванической развязки строк соединены с информационными входами первого блока памяти; выходы блока гальванической развязки столбцов соединены с информационными входами второго блока памяти; информационные выходы первого и второго блока памяти поразрядно объединены и поразрядно соединены с информационными входами блока преобразования; выход формирователя наличия матричной команды соединен с входом формирователя сигнала «Запись», выход которого соединен с входом «Запись» первого и второго блока памяти и с входом «Пуск» блока преобразования; первый выход «Чтение» и второй выход «Чтение» блока преобразования соединены с входом «Чтение» первого и второго блока памяти соответственно, выход «Установка в исходное состояние» блока преобразования соединен с входом «Установка в исходное состояние» первого и второго блока памяти; информационные и сигнальный выходы блока преобразования являются информационными и сигнальным выходами устройства соответственно.

| КРОСС-КЛАСТЕРНАЯ КОММУТАЦИОННАЯ МАТРИЦА | 2009 |

|

RU2417402C1 |

| УСТРОЙСТВО ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2217791C1 |

| US 6965816 В2, 15.11.2005. | |||

Авторы

Даты

2013-07-10—Публикация

2011-12-22—Подача