Изобретение относится к устройствам автоматики и может найти применение в устройствах управления ракетно-космической техники (РКТ).

Известен многоканальный командный аппарат с электронной коммутацией, предназначенный для формирования импульсных команд управления исполнительными органами, содержащий соединенные последовательно контроллер интерфейсов, блок дешифраторов, формирователей команд и блок ключей, выходы которых являются выходами устройства, генератор импульсов, а блок формирователей команд выполнен на счетчиках (патент РФ №2340925, кл. G05B 11/00).

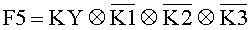

Данное устройство не позволяет формировать матричные команды.

Известно устройство коммутации с адресным управлением, содержащее дешифратор, поляризованные реле с двумя группами переключающих контактов, коммутационную матрицу, состоящую из столбцов и строк, в узлах которых установлены реле с развязывающими диодами. Контакты реле являются выходами матричных команд (а.с. №1274021, кл. Н03К 17/04).

Недостатками указанного устройства являются низкое быстродействие, так как установка требуемого положения коммутатора производится в два этапа, а также отсутствие контроля исправности коммутационной матрицы.

Наиболее близким к заявляемому техническому решению по технической сущности и достигаемому техническому результату является устройство формирования матричных команд, содержащее первый регистр (столбцов), второй регистр (строк), первый дешифратор, второй дешифратор, первую ключевую схему, вторую ключевую схему, матрицу команд с вертикальными (столбцами) и горизонтальными (строками) шинами, причем выходы первого регистра соединены с входами первого дешифратора, а выходы первого дешифратора соединены с входами первой ключевой схемы, выходы которой образуют вертикальные шины матрицы, выходы второго регистра соединены с входами второго дешифратора, а выходы второго дешифратора соединены с входами второй ключевой схемы; выходы которой образуют горизонтальные шины матрицы, в узлах которых установлена нагрузка с развязывающими диодами. Описанное устройство принято за прототип изобретения.

Недостатками указанного устройства является отсутствие контроля исправности состояния формирователя, позволяющее не исполнять команды, если возникли условия их формирования ложно, например за счет отказов в цепи формирования команды или в цепях приема команд у потребителя (в нагрузке). Отказ хотя бы одного развязывающего диода (короткое замыкание) в нагрузке повлечет за собой выдачу дополнительно ложной команды.

Задачей изобретения является создание схемы формирователя матричных команд, позволяющего формировать в любой момент только одну команду и контролировать работоспособность формирователя.

Указанный технический результат достигается за счет того, что в устройство формирования матричных команд, содержащее первый регистр (столбцов), второй регистр (строк), первый дешифратор, второй дешифратор, первую группу ключей, вторую группу ключей, вертикальные коммутируемые шины (столбцы) и горизонтальные коммутируемые шины (строки), шины питания +Е и -Е коммутируемых шин, причем шина питания +Е соединена с первой группой ключей, а шина питания -Е соединена со второй группой ключей, информационные входы первого и второго регистра объединены и являются информационными входами устройства, входы «запись» первого и второго регистра объединены и являются входом «запись» устройства, выходы первого регистра соединены с входами первого дешифратора, а выходы первого дешифратора соединены с входами первой группы ключей, выходы которой образуют вертикальные коммутируемые шины устройства, выходы второго регистра соединены с входами второго дешифратора, а выходы второго дешифратора соединены с входами второй группы ключей, выходы которой образуют горизонтальные коммутируемые шины устройства, введены первая и вторая группа диодов, формирователь наличия матричной команды, фиксатор наличия отказа в строках, фиксатор наличия отказа в столбцах, анализатор состояния, выход которого является информационным выходом устройства; аноды первой группы диодов соединены с соответствующими выходами первой ключевой схемы, а катоды объединены и соединены с положительным входом формирователя наличия матричной команды и фиксатора наличия отказа в столбцах. Катоды второй группы диодов соединены с соответствующими выходами второй ключевой схемы, а аноды объединены и соединены с отрицательным входом формирователя наличия матричной команды и фиксатора наличия отказа в строках. Отрицательный вход фиксатора наличия отказа в столбцах соединен с шиной питания -Е, положительный вход фиксатора наличия отказа в строках соединен с шиной питания +Е, а выходы фиксатора наличия отказа в столбцах, формирователя наличия матричной команды, фиксатора наличия отказа в строках соединены соответственно с первым, вторым, третьим входом анализатор состояния, а вход записи анализатора состояния является входом записи состояния устройства.

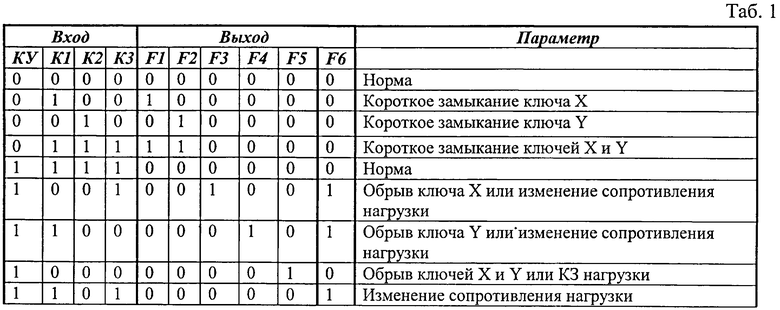

Изобретение поясняется схемами и чертежами:

- на фиг.1 представлена функциональная схема устройства формирования матричных команд;

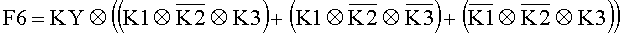

- на фиг.2 изображен фиксатор наличия отказа в строках и столбцах;

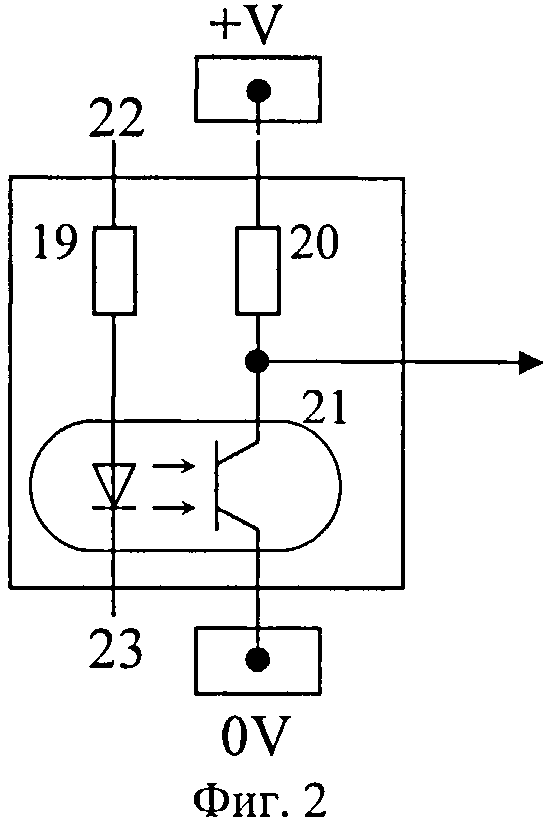

- на фиг.3 изображен формирователь наличия матричной команды.

Устройство формирования матричных команд (фиг.1) содержит входную шину устройства 1, вход записи команды 2 устройства, первый регистр (столбцов) 3, первый дешифратор 4, первую группу ключей 5, первую группу диодов 6 (V1 - Vn), второй регистр (строк) 7, второй дешифратор 8, вторую группу ключей 9, вторую группу диодов 10 (V1 - Vm), формирователь наличия матричной команды 11, фиксатор наличия отказа в столбцах 12, фиксатор наличия отказа в строках 13, вертикальные коммутируемые шины 14 (14.1 - 14.n), анализатор состояния 15, информационные выходы 16 устройства, горизонтальные коммутируемые шины 17 (17.1 - 17.m), вход 18 записи состояния устройства.

Фиксатор наличия отказа в столбцах 12 и фиксатор наличия отказа в строках 13 (Фиг.2) предназначены для гальванической развязки и согласования уровней коммутируемых шин с уровнями логических цепей и состоят из первого 19 и второго 20 резисторов и транзисторной оптопары 21. Первый резистор 19 является токозадающим для входной цепи транзисторной оптопары 21, а второй резистор 20 является нагрузкой выходного транзистора оптопары 21.

Формирователь наличия матричной команды 11 (Фиг.3) выполнен на стабилитроне 27, транзисторной оптопаре 26 с токозадающим резистором 24 для входной цепи оптопары 26 и резистором нагрузки 25 для выходного транзистора оптопары 26 аналогично ячейке блока гальванической развязки строк (фиг.2).

Стабилитрон 27 служит в качестве порогового устройства и обеспечивает срабатывание транзисторной оптопары 26 только при разности потенциалов, превышающей пороговое напряжение, задаваемое стабилитроном, таким образом, при напряжении ниже допустимого значения (напряжения стабилизации) между соответствующими линиями первой и второй группы ключей оптопара 26 не фиксирует выдачу команды.

Предлагаемое устройство работает следующим образом. Код команды через входную шину устройства 1 поступает на первый 3 и второй 7 регистры и по сигналу разрешения формирования команды записывается в регистры, выходной код которых дешифрируется первым 4 и вторым 8 дешифратором, на соответствующих выходах которого появляются сигналы, открывающие соответствующие ключи первой 5 и второй 9 группы ключей, при этом на соответствующей горизонтальной 17 и вертикальной 14 коммутируемой шинах появляется напряжение. Одновременно положительный потенциал +Е через один из диодов V1 - Vn первой группы диодов 6 поступает на положительный вход 22 фиксатора 12 наличия отказа в столбцах и на положительный вход 28 формирователя наличия матричной команды 11, а отрицательный потенциал -Е через один из диодов V1 - Vm второй группы диодов 10 поступает на отрицательный вход 23 фиксатора 13 наличия отказа в строках и на отрицательный вход 29 формирователя наличия матричной команды 11, в результате на выходах формирователя наличия матричной команды 11, фиксатора 12 наличия отказа в столбцах, фиксатора 13 наличия отказа в строках присутствуют логические 1, которые записываются в анализатор состояния 15 по сигналу записи состояния устройства (КУ), подаваемое на вход 18 анализатора состояния.

Формирователь наличия матричной команды 11 состоит из первого 24 и второго 25 резисторов, стабилитрона 27 и транзисторной оптопары 26, причем первый резистор 24 является токозадающим для входной цепи транзисторной оптопары 26, а второй резистор 25 является нагрузкой выходного транзистора оптопары 26.

Анализатор состояния 15 формирует ответное слово и записывает его в выходной регистр.

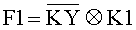

При возникновении короткого замыкания одного из ключей первой группы 5, в момент отсутствия сигнала 18 записи состояния устройства (КУ), через отказавший ключ положительный потенциал +Е поступает на фиксатор 12 наличия отказа в столбцах. Далее фиксатор наличия отказа в столбцах 12 формирует логический сигнал (К1), который поступает в анализатор состояния 15, где по данному событию формируется флаг F1 «Короткое замыкание одного из ключей первой группы» согласно формуле

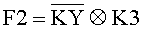

При возникновении короткого замыкания одного из ключей второй группы 9, в момент отсутствия сигнала записи состояния устройства (КУ), через отказавший ключ отрицательный потенциал -Е поступает на фиксатор 13 наличия отказа в строках. Далее фиксатор наличия отказа в строках 13 формирует логический сигнал (К3), который поступает в анализатор состояния 15, где по данному событию формируется флаг F2 «Короткое замыкание одного из ключей второй группы» согласно формуле

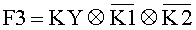

При возникновении обрыва одного из ключей первой группы 5, в момент выдачи сигнала записи состояния устройства (КУ), через отказавший ключ потенциал +Е не поступает на положительный вход фиксатора 12 наличия отказа в столбцах и на положительный вход формирователя наличия матричной команды 11. Таким образом, фиксатор наличия отказа в столбцах 12 не формирует логический сигнал (К1), а формирователь наличия матричной команды 11 не формирует сигнал наличия команды (К2), которые поступают в анализатор состояния 15, где по данному событию формируется флаг F3 «Обрыв одного ключа первой группы» согласно формуле

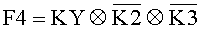

При возникновении обрыва одного из ключей второй группы 9, в момент выдачи сигнала записи состояния устройства (КУ), через отказавший ключ потенциал -Е не поступает на отрицательный вход фиксатора 13 наличия, отказа в строках и на отрицательный вход формирователя наличия матричной команды 11. Таким образом, фиксатор наличия отказа в строках 13 не формирует логический сигнал (К3), а формирователь наличия матричной команды 11 не формирует сигнал наличия команды (К2), которые поступают в анализатор состояния 15, где по данному событию формируется флаг F4 «Обрыв одного ключа второй группы» согласно формуле

При выдаче матричной команды при наличии короткого замыкания в нагрузке разность потенциалов между линиями столбцов и линиями строк будет ниже значения срабатывания оптронов фиксатора наличия отказа в столбцах 12, фиксатора наличия отказа в строках 13 и формирователя наличия матричной команды 11. Таким образом данные устройства не сформируют сигналы К1, К3 и К2 соответственно, в результате чего анализатор состояния 15 сформирует по данному событию флаг F5 «КЗ нагрузки» согласно формуле

При выдаче матричной команды в случае измененного входного сопротивления нагрузки, при котором обеспечивается разность потенциалов между линиями столбцов и линиями строк, достаточная для срабатывания оптронов фиксатора наличия отказа в столбцах 12 и фиксатора наличия отказа в строках 13, но недостаточная для срабатывания оптрона формирователя наличия матричной команды 11, формируются сигналы К1 и К3 и не формируется сигнал К2, в результате чего анализатор состояния 15 по данному событию сформирует флаг F6 «Изменение входного сопротивления нагрузки» согласно формуле

который записывается в выходной регистр анализатора состояния 15.

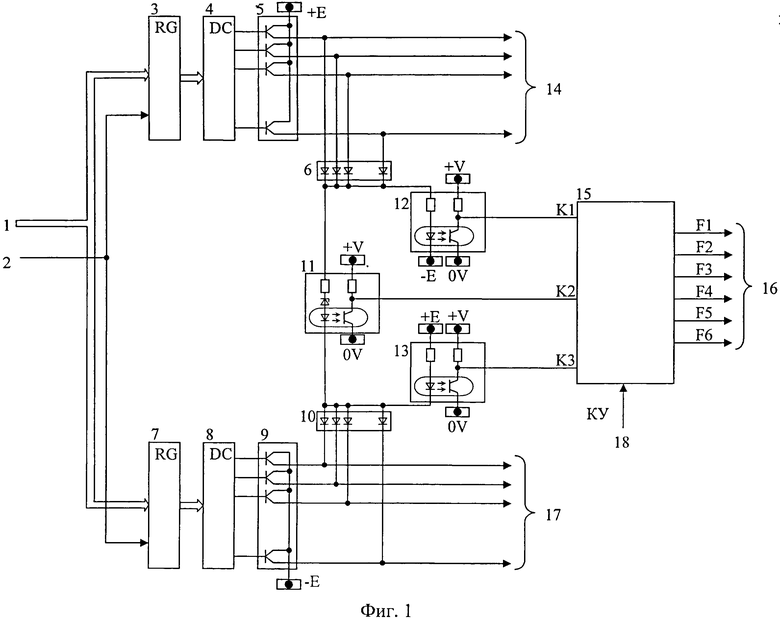

Остальные режимы работы анализатора состояния согласно таблице истинности (табл.1).

Данное устройство предлагается использовать в аппаратуре управления космических аппаратов. Устройство выполнено на интегральных микросхемах серии 1554, транзисторных оптопарах 249КП1С и диодных матрицах 2ДС627А, группа ключей - на микросборках ВК-16. Блок памяти использовались параллельные регистры серии 1554.

Из известных авторам источников информации и патентных материалов не известна совокупность признаков, сходных с совокупностью признаков заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь матричных команд | 2018 |

|

RU2707913C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА СИГНАЛОВ КОМАНДНОЙ МАТРИЦЫ | 2011 |

|

RU2487393C1 |

| ФОРМИРОВАТЕЛЬ МАТРИЧНЫХ КОМАНД | 2014 |

|

RU2549123C1 |

| Устройство для отображения информации | 1983 |

|

SU1108489A1 |

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР | 1991 |

|

RU2026605C1 |

| Матричное коммутационное устройство | 1988 |

|

SU1569965A1 |

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СИСТЕМ УПРАВЛЕНИЯ | 1972 |

|

SU432465A1 |

| Матричное устройство выдачи команд с оптической развязкой | 2016 |

|

RU2628911C1 |

| Устройство для диагностирования троированных дискретных схем автоматики | 1990 |

|

SU1772783A1 |

Изобретение относится к устройствам автоматики и может найти применение в устройствах управления ракетно-космической техники (РКТ). Техническим результатом является обеспечение формирования в любой момент времени только одной команды, контролируя при этом собственную работоспособность формирователя. Формирователь матричных команд, содержащий первый регистр (строк), второй регистр (столбцов), первый дешифратор, второй дешифратор, первую группу ключей, вторую группу ключей, вертикальные коммутируемые шины (столбцы) и горизонтальные коммутируемые шины (строки), шины питания +Е и -Е коммутируемых шин, информационные входы первого и второго регистра объединены и являются информационными входами устройства, входы «запись» первого и второго регистра объединены и являются входом «запись» устройства, также введены первая, вторая группы диодов, формирователь наличия матричной команды, фиксатор наличия отказа в строках, фиксатор наличия отказа в столбцах, анализатор состояния. 1 з.п. ф-лы, 3 ил., 1 табл.

1. Формирователь матричных команд, содержащий первый регистр (столбцов), второй регистр (строк), первый дешифратор, второй дешифратор, первую группу ключей, вторую группу ключей, вертикальные коммутируемые шины (столбцы) и горизонтальные коммутируемые шины (строки), шины питания +Е и -Е коммутируемых шин, причем шина питания +Е соединена с первой группой ключей, а шина питания -Е соединена со второй группой ключей, информационные входы первого и второго регистра объединены и являются информационными входами устройства, входы «запись» первого и второго регистра объединены и являются входом «запись» устройства, выходы первого регистра соединены с входами первого дешифратора, выходы которого соединены с входами первой группы ключей, выходы которой образуют вертикальные коммутируемые шины устройства, выходы второго регистра соединены с входами второго дешифратора, выходы которого соединены с входами второй группы ключей, выходы которой образуют горизонтальные коммутируемые шины устройства, отличающийся тем, что в него введены первая и вторая группа диодов, формирователь наличия матричной команды, фиксатор наличия отказа в строках, фиксатор наличия отказа в столбцах, анализатор состояния, выход которого является информационным выходом устройства; аноды первой группы диодов соединены с соответствующими выходами первой группы ключей, а катоды объединены и соединены с положительным входом формирователя наличия матричной команды и фиксатора наличия отказа в столбцах, катоды второй группы диодов соединены с соответствующими выходами второй группы ключей, а аноды объединены и соединены с отрицательным входом формирователя наличия матричной команды и фиксатора наличия отказа в строках, отрицательный вход фиксатора наличия отказа в столбцах соединен с шиной питания -Е, положительный вход фиксатора наличия отказа в строках соединен с шиной питания +Е, а выходы фиксатора наличия отказа в столбцах, формирователя наличия матричной команды, фиксатора наличия отказа в строках соединены соответственно с первым, вторым, третьим входом анализатора состояния, а вход записи анализатора состояния является входом записи состояния устройства.

2. Устройство по п.1, отличающееся тем, что, формирователь наличия матричной команды состоит из первого и второго резисторов и транзисторной оптопары, стабилитрона, причем первый резистор является токозадающим для входной цепи транзисторной оптопары, а второй резистор является нагрузкой выходного транзистора оптопары.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для ввода информации | 1983 |

|

SU1091147A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

Авторы

Даты

2015-02-10—Публикация

2013-04-29—Подача