ПЕРЕКРЕСТНЫЕ ССЫЛКИ НА РОДСТВЕННЫЕ ЗАЯВКИ

[1] Данная заявка притязает на приоритет заявки на патент Китая № 201520349040.7, зарегистрированной в Китайском государственном ведомстве по интеллектуальной собственности 26 мая 2015 г., которая полностью включена в настоящий документ путем ссылки.

Область техники

[2] Данное изобретение относится к области электроники и, в частности, к матричной подложке и устройству отображения.

Уровень техники

[3] В жидкокристаллическом устройстве отображения молекулы жидких кристаллов регулярно упорядочиваются под действием электрического поля таким образом, что молекулы жидких кристаллов имеют свойства кристаллов и обладают оптической анизотропией. В частности, если все молекулы жидких кристаллов четко упорядочены в одном направлении, световое излучение, испускаемое во всех направлениях сквозь слой жидкого кристалла, различается. Следовательно, макроскопический экран, состоящий из испускаемого светового излучения, также различается при различных углах наблюдения. Свойство сохранения экрана неизменным при изменении углов наблюдения называется характеристикой угла наблюдения жидкокристаллического устройства отображения. У жидкокристаллического устройства отображения с плохой характеристикой угла наблюдения (то есть, с малым углом наблюдения) при наблюдении с большим углом наблюдения могут возникать проблемы уменьшения контраста, обращения черного и белого и хроматическая аберрация.

[4] Однако, наблюдателю часто необходимо наблюдать жидкокристаллическое устройство отображения с большого угла наблюдения, следовательно, необходимо улучшать характеристику угла наблюдения жидкокристаллического устройства отображения.

Сущность изобретения

[5] В соответствии с данным изобретением, предлагаются матричная подложка и устройство отображения, которые позволяют улучшить угол наблюдения жидкокристаллического дисплея и уменьшить сложность структуры тонкопленочного транзистора (TFT) в подложке.

[6] Для достижения вышеуказанной цели в данном изобретении предлагаются следующие технические решения.

[7] В соответствии с данным изобретением, предлагается матричная подложка, которая содержит множество блоков пикселей, разделенных затворными шинами и шинами данных, расположенными перекрестно. Каждый из блоков пикселей содержит первый субпиксельный электрод, второй субпиксельный электрод, первый TFT и второй TFT. Первый субпиксельный электрод соединен со стоком первого TFT, а второй субпиксельный электрод соединен со стоком второго TFT. Сопротивление между истоком первого TFT и шиной данных, соединенной с первым TFT, больше, чем сопротивление между истоком второго TFT и шиной данных, соединенной со вторым TFT; и/или сопротивление между стоком первого TFT и первым субпиксельным электродом больше, чем сопротивление между стоком второго TFT и вторым субпиксельным электродом.

[8] Кроме того, исток первого TFT соединен с шиной данных, соединенной с первым TFT, посредством шины истока в форме ломаной линии, а исток второго TFT соединен с шиной данных, соединенной со вторым TFT, посредством шины истока в форме прямой линии; и/или сток первого TFT соединен с первым субпиксельным электродом посредством шины стока в форме ломаной линии, а сток второго TFT соединен со вторым субпиксельным электродом посредством шины стока в форме прямой линии.

[9] Кроме того, первый резистор делителя напряжения расположен на шине истока, соединенной с истоком первого TFT, и/или второй резистор делителя напряжения расположен на шине стока, соединенной со стоком первого TFT.

[10] Кроме того, когда первый резистор делителя напряжения расположен на шине истока, соединенной с истоком первого TFT, шина истока, соединенная с истоком первого TFT, содержит первые сегменты истока, разнесенные друг от друга, при этом первый резистор делителя напряжения содержит вторые сегменты истока, расположенные в другом слое по отношению к первым сегментам истока. Вторые сегменты истока соединены с разнесенными первыми сегментами истока через сквозные отверстия. Исток второго TFT расположен в том же слое, что и первые сегменты истока или вторые сегменты истока.

[11] Кроме того, вторые сегменты истока расположены в том же слое, что и первый субпиксельный электрод и/или второй субпиксельный электрод.

[12] При необходимости, когда первый резистор делителя напряжения расположен на шине истока, соединенной с истоком первого TFT, шина истока, соединенная с истоком первого TFT, содержит первые сегменты истока и вторые сегменты истока, разнесенные друг от друга, при этом первый резистор делителя напряжения содержит диодную пару. Один конец диодной пары соединен с первым сегментом истока, а другой конец диодной пары соединен со вторым сегментом истока. Диодная пара содержит диод прямой полярности и обращенный диод, соединенные параллельно.

[13] Кроме того, диод прямой полярности и обращенный диод сформированы путем закорачивания тонкопленочного транзистора соответствующим образом. Диод прямой полярности содержит первый закороченный исток, первый закороченный сток и первую область затвора. Первый закороченный исток соединен с первым сегментом истока, первый закороченный сток соединен со вторым сегментом истока, а первая область затвора закорочена на первый закороченный исток через сквозное отверстие. Обращенный диод содержит второй закороченный исток, второй закороченный сток и вторую область затвора. Второй закороченный исток соединен с первым сегментом истока, второй закороченный сток соединен со вторым сегментом истока, а вторая область затвора закорочена на второй закороченный сток через сквозное отверстие.

[14] Кроме того, первая область затвора и вторая область затвора расположены в том же слое, что и затвор первого TFT и затвор второго TFT соответственно.

[15] Кроме того, сквозные отверстия, соответственно, сформированы в первой области затвора и первом закороченном истоке, при этом два сквозных отверстия соединены путем наложения прозрачного проводящего слоя на два сквозных отверстия. Сквозные отверстия, соответственно, сформированы во второй области затвора и втором закороченном стоке, и два сквозных отверстия соединены путем наложения прозрачного проводящего слоя на два сквозных отверстия.

[16] Кроме того, когда второй резистор делителя напряжения расположен на шине стока, соединенной со стоком первого TFT, шина стока, соединенная со стоком первого TFT, содержит первые сегменты стока, разнесенные друг от друга, второй резистор делителя напряжения содержит вторые сегменты стока, расположенные в другом слое по отношению к первым сегментам истока, при этом вторые сегменты стока соединены с разнесенными первыми сегментами стока через сквозные отверстия.

[17] Кроме того, непроникающая канавка расположена на затворной шине, раскрыв канавки обращен к первому субпиксельному электроду или второму субпиксельному электроду, а шина истока первого TFT перекрыта затвором TFT путем прохождения через дно канавки.

[18] Кроме того, канавка проходит в направлении от второго субпиксельного электрода к первому субпиксельному электроду и не проходит через шину затвора.

[19] Кроме того, в одном из блоков пикселей исток первого TFT и исток второго TFT соединены с одной и той же шиной данных, при этом затвор первого TFT и затвор второго TFT соединены с одной и той же затворной шиной.

[20] В соответствии с данным изобретением предлагается также устройство отображения, которое содержит любую из матричных подложек, описанных выше.

[21] В матричной подложке и устройстве отображения, предлагаемых в соответствии с данным изобретением, матричная подложка содержит множество блоков пикселей, разделенных затворными шинами и шинами данных, расположенными перекрестно, при этом каждый из блоков пикселей содержит первый субпиксельный электрод и второй субпиксельный электрод. В частности, первый субпиксельный электрод соединен со стоком первого TFT, а второй субпиксельный электрод соединен со стоком второго TFT. Сопротивление между истоком первого TFT и шиной данных, соединенной с первым TFT, больше, чем сопротивление между истоком второго TFT и шиной данных, соединенной со вторым TFT, и/или сопротивление между стоком первого TFT и первым субпиксельным электродом больше, чем сопротивление между стоком второго TFT и вторым субпиксельным электродом. Видно, что для каждого блока пикселей ввиду того, что резистор соединен последовательно с истоком или стоком первого TFT для деления напряжения, выходное напряжение на стоке первого TFT меньше, чем выходное напряжение на стоке второго TFT, при одном и том же управляющем напряжении. Следовательно, создается разность напряжений между двумя субпиксельными электродами, соответственно, соединенными со стоком первого TFT и стоком второго TFT, при этом углы отклонения молекул жидкого кристалла в пределах соответствующих областей жидкого кристалла изменяются. Таким образом, когда падающее световое излучение передается сквозь область жидкого кристалла, соответствующую одному блоку пикселей, испускаемое световое излучение по существу остается равномерным в различных направлениях, благодаря чему улучшается угол наблюдения жидкокристаллического дисплея и уменьшается сложность структуры матричной подложки без добавления дополнительного TFT.

Краткое описание чертежей

[22] С целью более наглядного объяснения технических решений в вариантах осуществления настоящего изобретения или соответствующей аппаратуре далее вкратце иллюстрируются прилагаемые чертежи вариантов осуществления или предшествующего уровня техники. Очевидно, прилагаемые далее чертежи представляют собой лишь некоторые варианты осуществления настоящего изобретения, и специалисты в данной области техники на основе данных чертежей могут без творческой работы дополнительно получить другие чертежи.

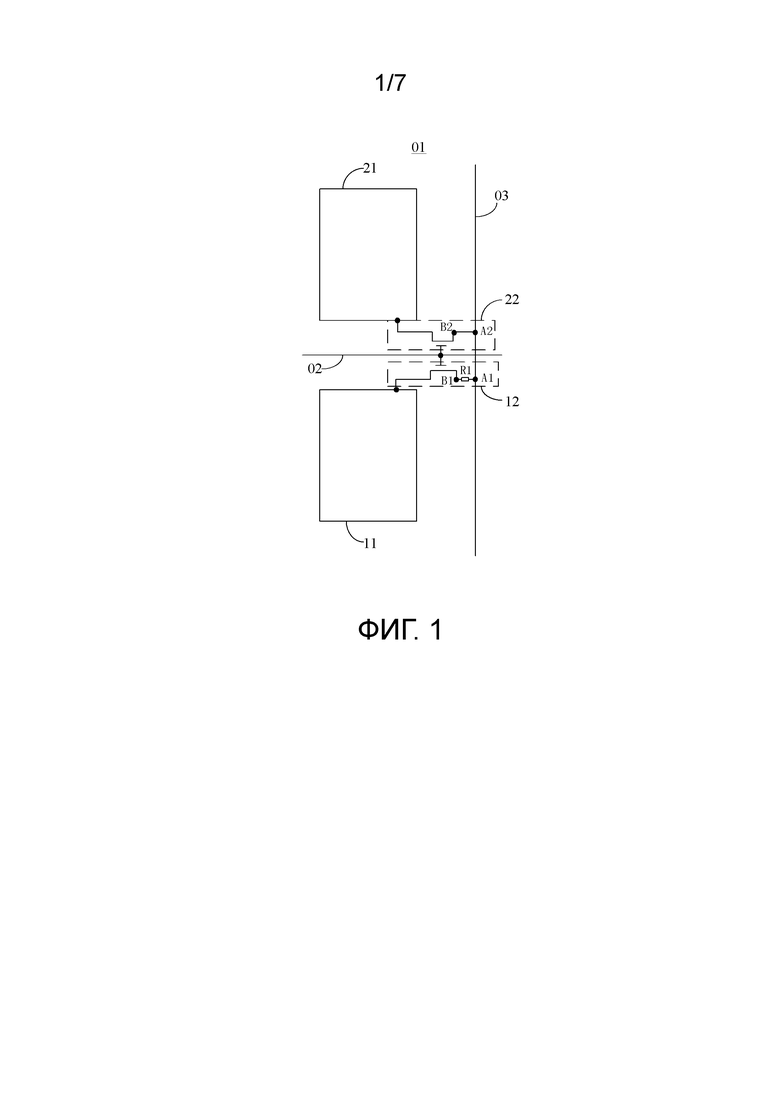

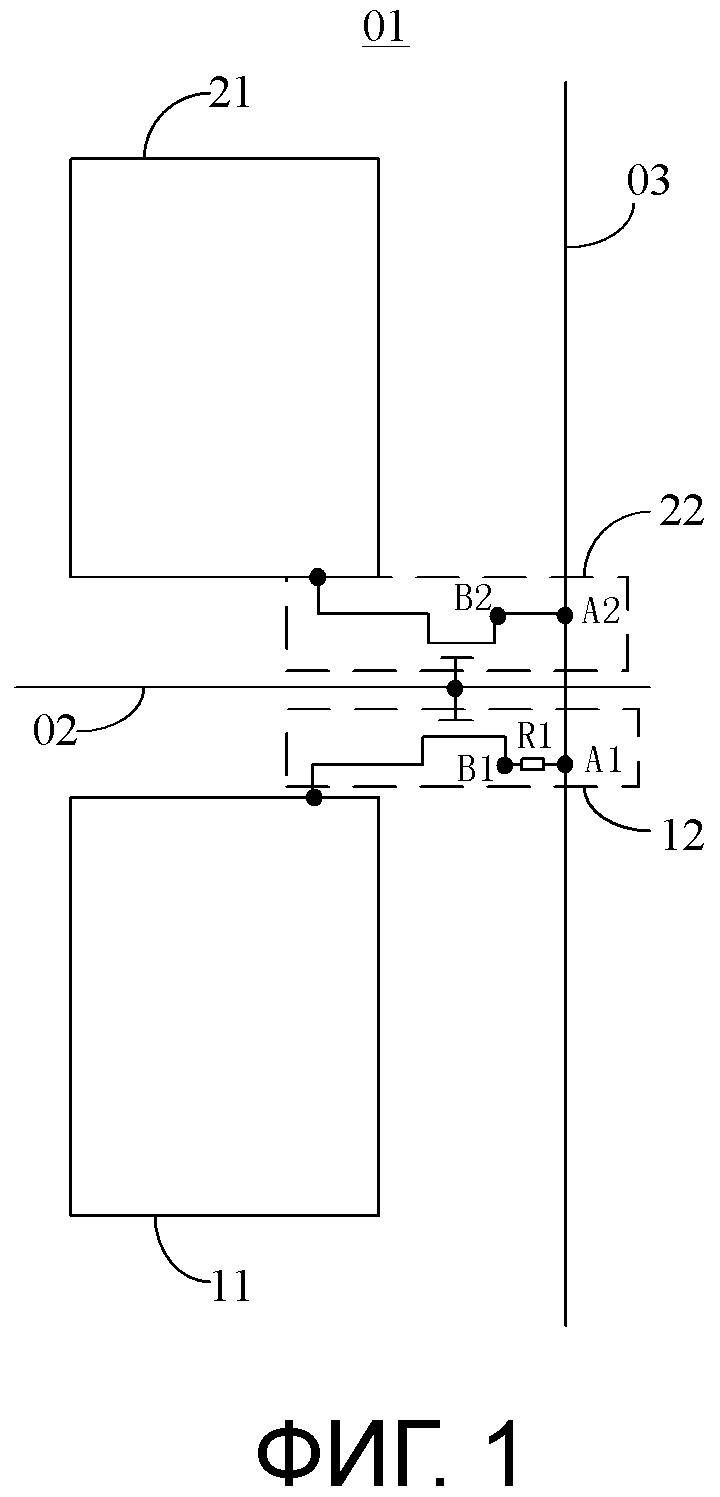

[23] Фиг. 1 представляет собой первый схематический вид в плане структуры блока пикселей на матричной подложке в соответствии с одним вариантом осуществления изобретения;

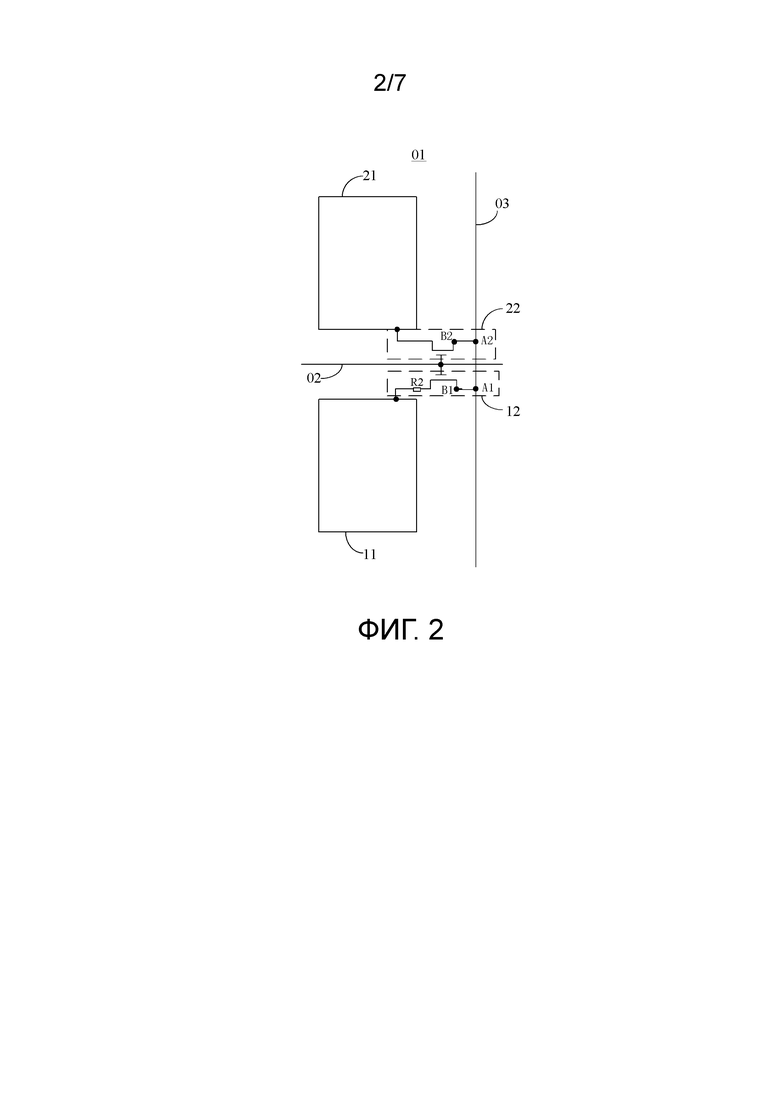

[24] фиг. 2 представляет собой второй схематический вид в плане структуры блока пикселей на матричной подложке в соответствии с одним вариантом осуществления изобретения;

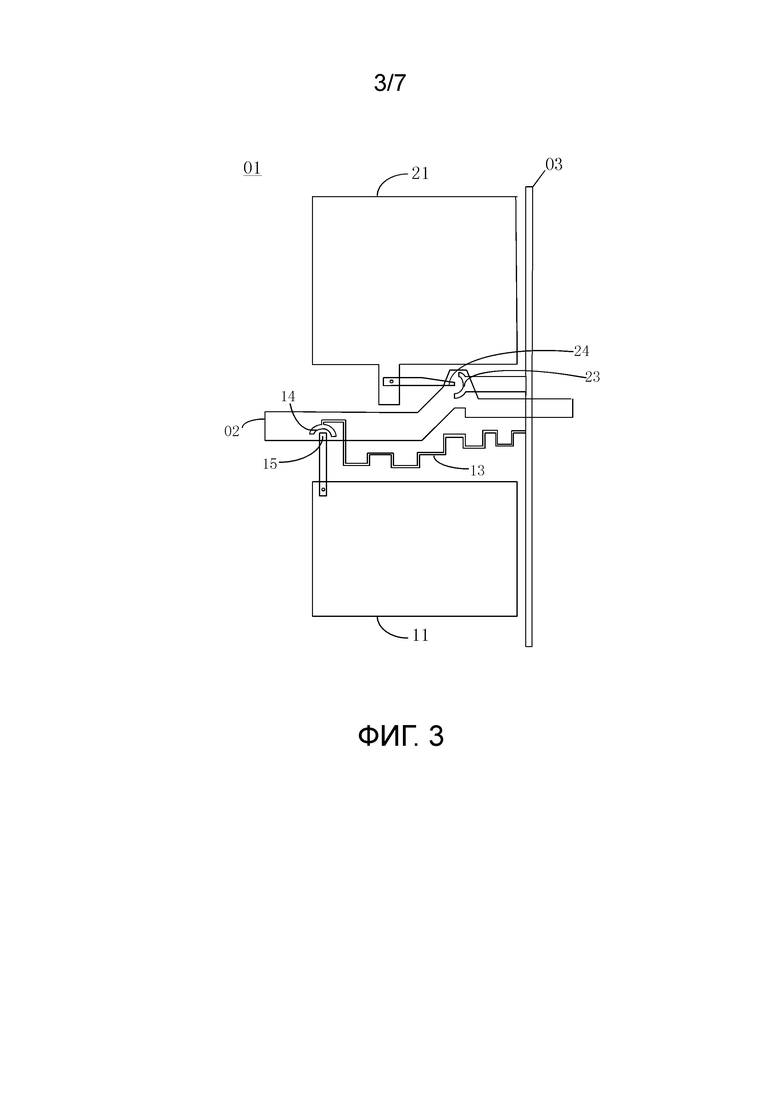

[25] фиг. 3 представляет собой третий схематический вид в плане структуры блока пикселей на матричной подложке в соответствии с одним вариантом осуществления изобретения;

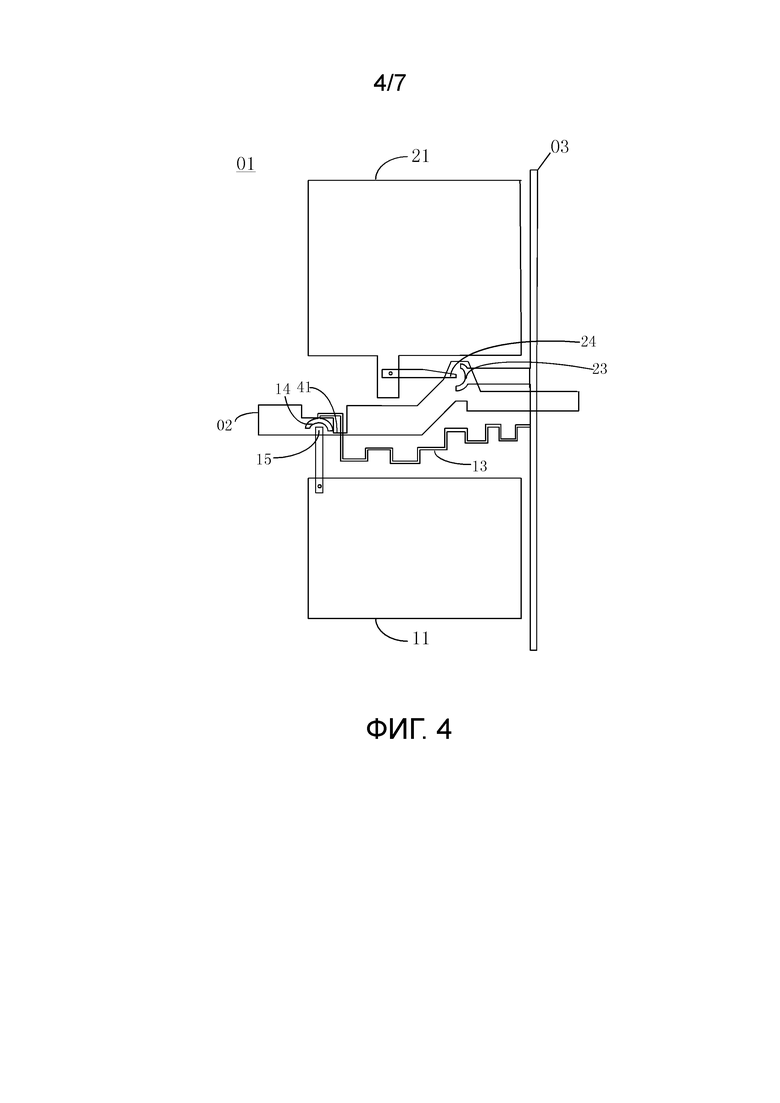

[26] фиг. 4 представляет собой четвертый схематический вид в плане структуры блока пикселей на матричной подложке в соответствии с одним вариантом осуществления изобретения;

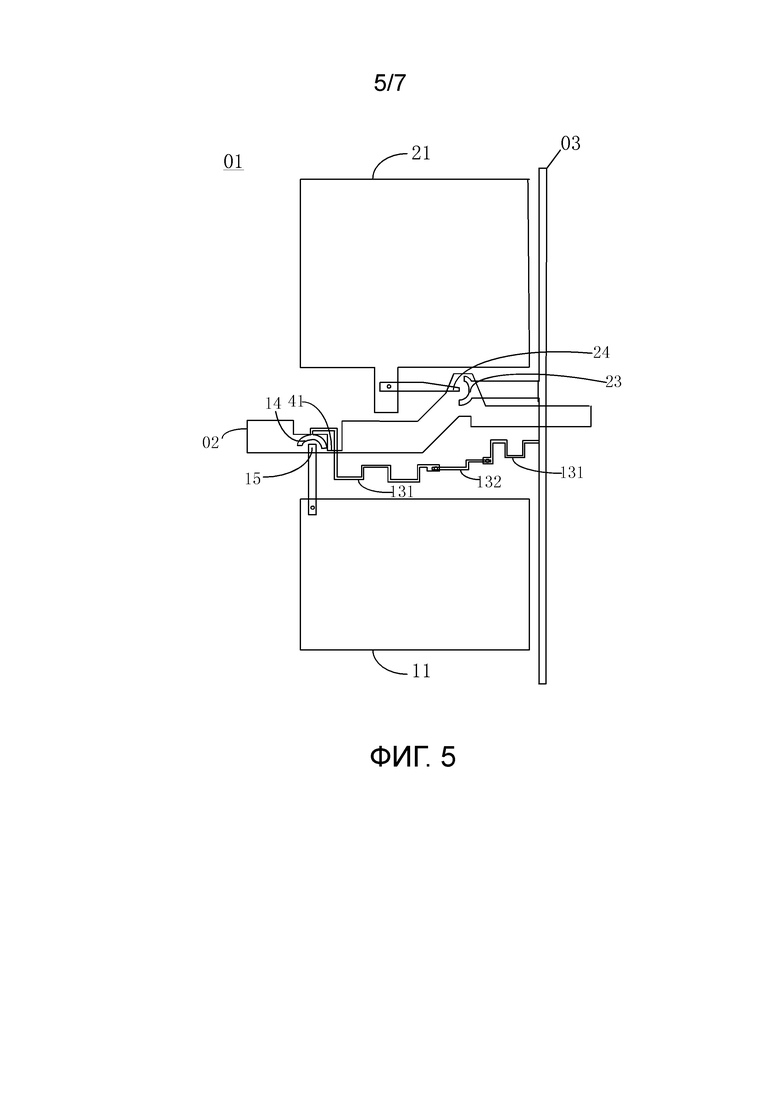

[27] фиг. 5 представляет собой пятый схематический вид в плане структуры блока пикселей на матричной подложке в соответствии с одним вариантом осуществления изобретения;

[28] фиг. 6 представляет собой шестой схематический вид в плане структуры блока пикселей на матричной подложке в соответствии с одним вариантом осуществления изобретения; и

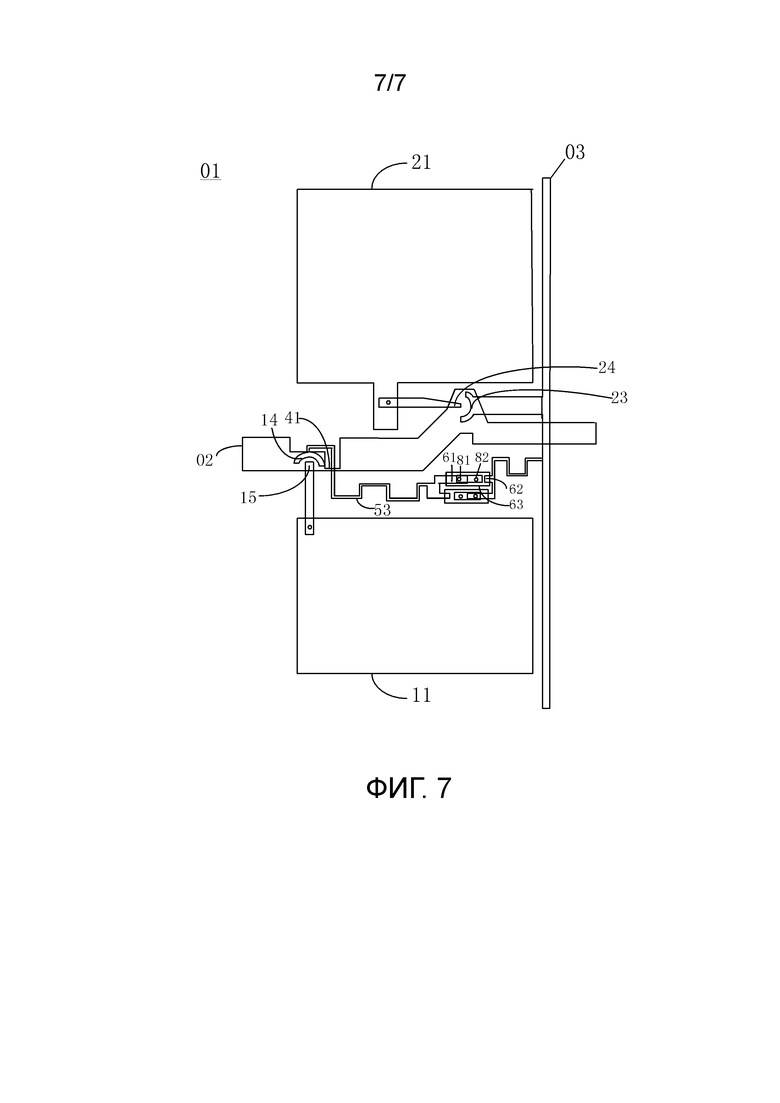

[29] фиг. 7 представляет собой седьмой схематический вид в плане структуры блока пикселей на матричной подложке в соответствии с одним вариантом осуществления изобретения.

Подробное описание

[30] В нижеследующем описании в целях объяснения, а не ограничения излагаются характерные детали, такие как конкретные архитектуры, интерфейсы, методы, чтобы обеспечить полное понимание изобретения. Однако специалистам в данной области техники должно быть ясно, что данное изобретение может быть реализовано в других иллюстративных вариантах осуществления, которые выходят за пределы указанных характерных деталей. В иных случаях подробные описания известных устройств, схем и способов не приводятся, чтобы избежать затруднения понимания изобретения ненужными подробностями.

[31] Кроме того, термин «первый» и «второй» используется лишь для описания и не может рассматриваться как предполагающий относительную важность или указывающий на число технических признаков, задаваемых в инструкциях. Вследствие этого, характеристики, ограниченные «первым», «вторым», могут выражать или предполагать одну или более из характеристик. В описании настоящего изобретения «множество» означает два или более, если не указано иное.

[32] В соответствии с одним вариантом осуществления изобретения, предлагается матричная подложка, которая содержит множество блоков пикселей, разделенных затворными шинами и шинами данных, расположенными перекрестно. В частности, данный вариант осуществления изобретения в качестве примера иллюстрируется одним блоком пикселей.

[33] Как показано на фиг. 1 или фиг. 2, блок 01 пикселей содержит первый субпиксельный электрод 11 и второй субпиксельный электрод 21. Управление первым субпиксельным электродом 11 и вторым субпиксельным электродом 21 осуществляется, соответственно, первым TFT 12 и вторым TFT 22. В частности, первый субпиксельный электрод 11 соединен со стоком первого TFT 12, а второй субпиксельный электрод 21 соединен со стоком второго TFT 22. И затвор первого TFT 12, и затвор второго TFT 22 соединены с одной затворной шиной 02. И исток первого TFT 12, и исток второго TFT 22 соединены с одной шиной 03 данных.

[34] Разумеется, затвор первого TFT 12 и затвор второго TFT 22 могут быть соединены с различными затворными шинами, а исток первого TFT 12 и исток второго TFT 22 могут быть соединены с различными шинами данных, которые в данном изобретении не ограничены.

[35] Сопротивление между истоком первого TFT 12 и шиной 03 данных, соединенной с первым TFT 12, больше, чем сопротивление между истоком второго TFT 22 и шиной 03 данных, соединенной со вторым TFT 22; и/или сопротивление между стоком первого TFT 12 и первым субпиксельным электродом 11 больше, чем сопротивление между стоком второго TFT 22 и вторым субпиксельным электродом 21.

[36] В частности, как показано на фиг. 1, первый резистор R1 делителя напряжения добавлен между истоком первого TFT 12 и шиной 03 данных по отношению к истоку второго TFT 22. Поскольку то же управляющее напряжение прикладывается шиной 03 данных, напряжение в соединительной точке А1 между истоком первого TFT 12 и шиной 03 данных равно напряжению в соединительной точке А2 между истоком второго TFT 22 и шиной 03 данных (то есть, UA1=UA2). Тогда напряжение UB1 в B1 на истоке первого TFT 12 равно UA1 минус IR (I - значение тока, проходящего через первый резистор R1 делителя напряжения) после деления напряжения первым резистором R1 делителя напряжения. Напряжение UB2 в B2 на истоке второго TFT 22 равно UA1. Следовательно, UB2 больше, чем UB1. Кроме того, зарядное напряжение первого субпиксельного электрода 11 после зарядки равно напряжению в В1 или близко к нему, зарядное напряжение второго субпиксельного электрода 21 после зарядки равно напряжению в В2 или близко к нему, а UB2 больше, чем UB1, следовательно, зарядное напряжение первого субпиксельного электрода 11 меньше, чем зарядное напряжение второго субпиксельного электрода 21, напряженности электрического поля в областях жидкого кристалла, соответствующих двум субпиксельным электродам 11 и 21, различны, и, наконец, углы отклонения молекул жидкого кристалла в пределах двух областей различны.

[37] В этом случае, несмотря на то, что молекулы жидкого кристалла все еще обладают оптической анизотропией, направления пропускания светового излучения двух областей различны, при этом испускаемые световые излучения двух областей дополняют друг друга, благодаря чему испускаемое световое излучение становится практически равномерным во всех направлениях. Поскольку экран представлен на макроуровне жидкокристаллическим устройством отображения ввиду интеграла по пространству испускаемого светового излучения от каждого блока пикселей, практически один и тот же экран может наблюдаться с любого из широкого диапазона углов наблюдения в данном варианте осуществления изобретения, то есть, угол наблюдения жидкокристаллического устройства отображения улучшается без добавления дополнительного TFT для управления зарядкой-разрядкой субпиксельных электродов.

[38] При необходимости, как показано на фиг. 2, второй резистор R2 делителя напряжения добавлен между стоком первого TFT 12 и первым субпиксельным электродом 11 по отношению к стоку второго TFT 22. Аналогично приведенному выше описанию, поскольку второй резистор R2 делителя напряжения также выполняет функцию деления напряжения, под действием того же управляющего напряжения зарядное напряжение на стоке первого TFT 12 меньше, чем зарядное напряжение на стоке второго TFT 22, напряженности электрического поля в областях жидкого кристалла, соответствующих двум субпиксельным электродам 11 и 21, различны, и, наконец, углы отклонения молекул жидкого кристалла в пределах двух областей различны.

[39] Необходимо отметить, что подобно принципу деления напряжения, описанному выше, первый резистор R1 делителя напряжения может также быть добавлен между истоком первого TFT 12 и шиной 03 данных, а второй резистор R2 делителя напряжения может быть добавлен между стоком первого TFT 12 и первым субпиксельным электродом 11, следовательно, напряженности электрического поля в областях жидкого кристалла, соответствующих двум субпиксельным электродам 11 и 21, различны, и, наконец, углы отклонения молекул жидкого кристалла в пределах двух областей различны.

[40] Кроме того, исток первого TFT 12 могут быть соединены с шиной 03 данных через шину истока в форме ломаной линии, а исток второго TFT 22 могут быть соединены с шиной 03 данных через шину истока в форме прямой линии, тем самым повышая сопротивление между истоком первого TFT 12 и шиной 03 данных и дополнительно формируя первый резистор R1 делителя напряжения.

[41] Аналогичным образом, сток первого TFT 12 может быть соединен с первым субпиксельным электродом 11 через шину стока в форме ломаной линии, а сток второго TFT 22 соединен со вторым субпиксельным электродом 21 данных через шину стока в форме прямой линии, благодаря чему повышается сопротивление между стоком первого TFT 12 и первым субпиксельным электродом 11 и дополнительно сформирован второй резистор R2 делителя напряжения.

[42] Для иллюстрации, как показано на фиг. 3, исток первого TFT 12 в качестве примера соединен с шиной 03 данных через шину истока в форме ломаной линии. Блок 01 пикселей, в частности, содержит первый субпиксельный электрод 11 и второй субпиксельный электрод 21. Первый субпиксельный электрод 11 и второй субпиксельный электрод 21, соответственно, расположены на обеих сторонах одной затворной шины 02 и на одной и той же стороне шины 03 данных. Затворная шина 02 непосредственно используется в качестве затворов двух TFT. Первый TFT и шина 03 данных соединены через шину 13 истока, которая выполнена в форме ломаной линии, проходящей от шины 03 данных к первому субпиксельному электроду 11 и формирующей первый исток 14 на затворной шине 02. Второй TFT и шина 03 данных соединены через шину истока в форме прямой линии, проходящей от шины 03 данных ко второму субпиксельному электроду 21 и формирующей второй исток 23 на затворной шине 02. Формируются, соответственно, первый сток 15 и второй сток 24, соответствующие первому истоку 14 и второму истоку 23. Первый сток 15 электрически соединен с первым субпиксельным электродом 11 через сквозное отверстие, и второй сток 24 электрически соединен со вторым субпиксельным электродом 21 через сквозное отверстие.

[43] Таким образом, поскольку первый резистор R1 делителя напряжения сформирован из шины 13 истока первого TFT в форме ломаной линии, которая выполняет функцию деления напряжения, под действием одного и того же управляющего напряжения выходное напряжение на первом стоке 15 первого TFT меньше, чем выходное напряжение на втором стоке 24 второго TFT, при этом создается разность напряжений между двумя субпиксельными электродами, соответственно, соединенными со стоком первого TFT и стоком второго TFT.

[44] Разумеется, аналогично блоку 01 пикселей, как показано на фиг. 3, сток первого TFT 12 может также быть соединен с первым субпиксельным электродом 11 через шину стока в форме ломаной линии. В частности, в соответствии с фиг. 3, аналогично шине 13 истока, соединенной с первым TFT 12, шина стока, соединенная с первым стоком 15 первого TFT 12, может быть выполнена в форме ломаной линии, формируя второй резистор R2 делителя напряжения. Таким образом, поскольку второй резистор R2 делителя напряжения также выполняет функцию деления напряжения, может создаваться разность напряжений между двумя субпиксельными электродами, соответственно, соединенными со стоком первого TFT и стоком второго TFT.

[45] Необходимо отметить, что соединение, форма и тип TFT в данном изобретении специально не ограничены. Например, соединение между двумя TFT может быть выполнено в такой форме, что два истока соединены встречно-параллельно, а два соответствующих стока расположены с обеих сторон двух истоков, соединенных встречно-параллельно, либо два истока расположены рядом, а два соответствующих стока расположены на одной и той же стороне двух истоков. TFT может представлять собой TFT типа I, исток которого вытянут, или TFT типа U, исток которого выполнен в форме U. Специалисты в данной области техники могут выбирать наиболее подходящие соединение, форму и тип TFT в зависимости от реальных обстоятельств.

[46] В качестве развития вариантов осуществления, описанных выше, как показано на фиг. 4, на затворной шине 02 может быть расположена непроникающая канавка 41. В одном варианте осуществления канавка 41 проходит в направлении от второго субпиксельного электрода 21 к первому субпиксельному электроду 11 и не проникает в затворную шину 02. Раскрыв канавки 41 обращен к первому субпиксельному электроду 11 или второму субпиксельному электроду 21. Часть шины 13 истока первого TFT, проходящая через нижнюю часть канавки 41, перекрыта затвором первого TFT, а остальные части шины 13 истока первого TFT не перекрыты затвором первого TFT, поэтому зона перекрытия между затворной шиной 02 и шиной 13 истока первого TFT уменьшена. Таким образом, помехи от емкости связи между затворной шиной 02 и шиной 13 истока могут быть уменьшены.

[47] Кроме того, еще в одной реализации в соответствии с одним вариантом осуществления данного изобретения между истоком первого TFT и шиной данных, соединенной с первым TFT, специально введены первые сегменты истока, разнесенные друг от друга, и вторые сегменты истока, расположенные в другом слое по отношению к первым сегментам истока. Вторые сегменты истока соединены с первыми сегментами истока, разнесенными друг от друга, через сквозные отверстия, при этом исток второго TFT расположен в том же слое, что и первые сегменты истока или вторые сегменты истока.

[48] Для иллюстрации, как показано на фиг. 5, один или более разрывов расположены в шине 13 истока первого TFT, исходя из структуры блока пикселей, как показано на фиг. 4. В этом случае между истоком 14 первого TFT и шиной данных 03 специально введены первые сегменты 131 истока, разнесенные друг от друга, и вторые сегменты 132 истока, расположенные в другом слое по отношению к первым сегментам истока. Вторые сегменты 132 истока дополнительно соединены с первыми сегментами 131 истока, разнесенными друг от друга, через сквозные отверстия. В данном варианте осуществления блок 01 пикселей размещен путем использования затворной шины 02 в качестве средней шины, два субпиксельных электрода 11 и 21 примыкают к затворной шине 02 и шине 03 данных, при этом затворная шина 02 непосредственно используется в качестве затворов двух TFT, что может минимизировать соединительные шины (такие как шина между затвором и затворной шиной, шина между шиной данных и истоком и шина между субпиксельным электродом и стоком) и упростить процессы формирования рельефа функциональных слоев.

[49] Второй сегмент 132 истока может, в частности, представлять собой резистор на основе оксида индия и олова (ITO), изготовленный из материала ITO, и, следовательно, второй сегмент 132 истока может быть размещен в том же слое, что и первый субпиксельный электрод 11 и/или второй субпиксельный электрод 21, что не увеличивает числа процессов формирования рельефа, используемых при изготовлении матричной подложки.

[50] Разумеется, второй сегмент 132 истока может также быть изготовлен из других материалов, которые имеют большее сопротивление, при этом второй сегмент 132 истока расположен в другом слое по отношению к первому субпиксельному электроду 11 и/или второму субпиксельному электроду 21. Следовательно, после того, как сформированы истоки и стоки первого TFT и второго TFT, второй сегмент 132 истока дополнительно соединен с первыми сегментами 131 истока, разнесенными путем отдельного однократного использования процессов формирования рельефа.

[51] Необходимо отметить, что аналогично блоку 01 пикселей, как показано на фиг. 4, первые сегменты стока, являющиеся разнесенными, и вторые первые сегменты стока, расположенные в другом слое по отношению к первым сегментам стока, могут размещаться между стоком первого TFT и первым субпиксельным электродом, тем самым формируя второй резистор R2 делителя напряжения. Таким образом, поскольку второй резистор R2 делителя напряжения также выполняет функцию деления напряжения, может создаваться разность напряжений между двумя субпиксельными электродами, соответственно, соединенными со стоком первого TFT и стоком второго TFT.

[52] При необходимости еще в одной реализации в соответствии с одним вариантом осуществления данного изобретения между истоком первого TFT и шиной данных, соединенной с первым TFT, могут быть специально введены диодная пара, первый сегмент истока и второй сегмент истока. Один конец диодной пары соединен с первым сегментом истока, а другой конец диодной пары соединен со вторым сегментом истока. Поскольку диод обладает проводимостью в одном направлении, диодная пара содержит диод прямой полярности и обращенный диод, соединенные параллельно, чтобы обеспечить возможность включения первого TFT при подаче по шине данных высокого напряжения или низкого напряжения.

[53] Кроме того, имеются несколько способов формирования вышеописанной диодной пары, и для иллюстрации в соответствии с данным вариантом осуществления иллюстрируется диодная пара, формируемая закорачиванием двух TFT.

[54] В этом случае, как показано на фиг. 6, диодная пара состоит из диода прямой полярности и обращенного диода, один конец диодной пары соединен с первым сегментом 53 истока, а другой конец диодной пары соединен со вторым сегментом 54 истока. Диод прямой полярности содержит первый закороченный исток 61, первый закороченный сток 62 и первую область 63 затвора (первая область 63 затвора расположена в том же слое, что и затвор первого TFT). Первый закороченный исток 61 соединен с первым сегментом 53 истока. Первый закороченный сток 62 соединен со вторым сегментом 54 истока. Первая область 63 затвора закорочена на первый закороченный исток 61 через сквозное отверстие. Обращенный диод содержит второй закороченный исток 71, второй закороченный сток 72 и вторую область 73 затвора (вторая область 73 затвора расположена в том же слое, что и затвор второго TFT). Второй закороченный исток 71 соединен с первым сегментом 53 истока, второй закороченный сток 72 соединен со вторым сегментом 54 истока, а вторая область 73 затвора закорочена на второй закороченный сток 72 через сквозное отверстие.

[55] В соответствии с фиг. 6, могут существовать несколько способов формирования диода прямой полярности и обращенного диода путем закорачивания TFT, и специалисты в данной области техники могут выбирать наиболее подходящее размещение в зависимости от реальных обстоятельств. Например, как показано на фиг. 7, слой ITO расположен на диоде прямой полярности и обращенном диоде, слой ITO электрически соединен с первым закороченным истоком 61 через сквозное отверстие 81, при этом слой ITO электрически соединен с первой областью 63 затвора через сквозное отверстие 82, чтобы закоротить первую областью 63 затвора и первый закороченный исток 61, тем самым формируя диод прямой полярности. Соответственно, обращенный диод может быть сформирован путем использования вышеописанного способа. Таким образом, первый резистор R1 делителя напряжения может быть сформирован на истоке первого TFT без дополнительного увеличения числа процессов формирования структуры, используемых при изготовлении матричной подложки.

[56] Необходимо отметить, что тот же способ, описанный выше, может использоваться для стока первого TFT, диод прямой полярности и обращенный диод сформированы на стоке 15 первого TFT, тем самым формируя второй резистор R2 делителя напряжения. Таким образом, поскольку второй резистор R2 делителя напряжения также выполняет функцию деления напряжения, генерирование разности напряжений между двумя субпиксельными электродами, соответственно, соединенными со стоком первого TFT и стоком второго TFT, гарантировано.

[57] Кроме того, поскольку TFT может быть эквивалентен резистору в открытом состоянии (когда на затвор подается напряжение, чтобы сделать активный слой проводящим), в этом случае сопротивление TFT определяется отношением ширины к длине TFT. Отношение ширины к длине является внутренне присущим атрибутом и, как правило, записывается в виде W/L, где W и L, соответственно, представляют собой ширину и длину канала. Как видно в формуле (1), отношение W1/L1 ширины к длине TFT связано с сопротивлением TFT, то есть,

1/Ron=∂I/∂V=μnCox(VGS1-Vth1) W1/L1 (1)

[58] где Ron - сопротивление открытого TFT, VGS1 - разность потенциалов между затвором и истоком, а Vth1 - начальное напряжение возбуждения зоны проводимости полупроводникового слоя, создаваемое зарядами, т.е., пороговое напряжение. Cox=ɛ0ɛox/dox, где Cox - удельная емкость на единицу площади изолирующего слоя затвора, ɛ0 - диэлектрическая константа вакуума, ɛox - диэлектрическая константа изолирующего слоя затвора, а dox - толщина изолирующего слоя затвора. μn - подвижность электронов полупроводника. Из формулы видно, что сопротивление открытого TFT обратно пропорционально отношению W1/L1 ширины к длине.

[59] Поскольку диод прямой полярности или обращенный диод, формируемые путем закорачивания TFT, по-прежнему имеют вышеописанную характеристику, сопротивление диода прямой полярности или обращенного диода может регулироваться корректировкой отношения W1/L1 ширины к длине диода прямой полярности или обращенного диода, и, кроме того, регулируется сопротивление резистора делителя. Следовательно, напряженности электрического поля, которым подвергаются области жидкого кристалла, соответствующие двум субпиксельным электродам, различны, и, наконец, углы отклонения молекул жидкого кристалла в пределах двух областей различны, что сохраняет равномерность испускаемого светового излучения во всех направлениях и улучшает характеристику угла наблюдения жидкокристаллического устройства отображения.

[60] Необходимо отметить, что первый резистор делителя напряжения добавлен между шиной данных и истоком первого TFT в отношении истока второго TFT, что иллюстрируется в вышеописанных вариантах осуществления. Следует учесть, что схема построения, в которой второй резистор делителя напряжения добавлен между первым субпиксельным электродом и стоком первого TFT в отношении стока второго TFT, аналогична соответствующей схеме в вышеописанных вариантах осуществления и в настоящем документе не повторяется.

[61] Кроме того, разность между зарядным напряжением первого субпиксельного электрода и зарядным напряжением второго субпиксельного электрода в одном и том же блоке пикселей может выбираться в диапазоне от 0 до 0,5 В, чтобы в максимально возможной степени сохранить равномерность испускаемого светового излучения во всех направлениях. Указанная разность создает оптимизированную разность углов отклонения у соответствующих двух областей жидкого кристалла, что может дополнительно увеличивать равномерность испускаемого светового излучения во всех направлениях. Следовательно, достигается более однородный экран во всех макроскопических направлениях, и улучшается характеристика угла наблюдения жидкокристаллического устройства отображения.

[62] Понятно, что разность зарядных напряжений между двумя субпиксельными электродами в одном и том же блоке пикселей в данном изобретении отдельно не ограничена. Даже если вышеуказанная разность установлена в пределах других диапазонов, они, тем не менее, подпадают под действие правовой охраны данного изобретения при условии, что испускаемое световое излучение может оставаться равномерным во всех направлениях.

[63] Необходимо также отметить, что цель вышеописанных вариантов осуществления состоит в предложении более оптимизированного конструктивного решения для компонентов матричной подложки. Местоположение и тип соединения TFT и субпиксельных электродов в данном изобретении не ограничены, и специалисты в данной области техники могут выбирать наиболее подходящее размещение в зависимости от реальных обстоятельств.

[64] В соответствии с одним вариантом осуществления данного изобретения, предлагается также устройство отображения, которое содержит любую из матричных подложек, описанных выше. Устройство отображения может представлять собой изделие или компонент, который выполняет функцию отображения, например, жидкокристаллическую панель, электронную бумагу, панель на органических светодиодах (OLED), мобильный телефон, планшетный компьютер, телевизор, монитор, ноутбук, цифровую фоторамку и навигатор.

[65] Необходимо отметить, что матричная подложка, входящая в устройство отображения в соответствии с данным изобретением, не ограничена ни одним из вышеописанных вариантов осуществления, и в зависимости от реальных обстоятельств специалистами в данной области техники могут быть выполнены изменения и комбинации вышеописанных вариантов осуществления для изготовления жидкокристаллического устройства отображения, которое имеет приемлемую характеристику угла наблюдения и пригодно для производства и применения.

[66] В соответствии с вариантами осуществления данного изобретения, предлагаются матричная подложка и устройство отображения. Матричная подложка содержит множество блоков пикселей, разделенных затворными шинами и шинами данных, расположенными перекрестно, при этом каждый из блоков пикселей содержит первый субпиксельный электрод и второй субпиксельный электрод, которые, соответственно, управляются первым TFT и вторым TFT. В частности, первый субпиксельный электрод соединен со стоком первого TFT, а второй субпиксельный электрод соединен со стоком второго TFT. Сопротивление между истоком первого TFT и шиной данных, соединенной с первым TFT, больше, чем сопротивление между истоком второго TFT и шиной данных, соединенной со вторым TFT, и/или сопротивление между стоком первого TFT и первым субпиксельным электродом больше, чем сопротивление между стоком второго TFT и вторым субпиксельным электродом. Видно, что для каждого блока пикселей ввиду того, что резистор делителя напряжения расположен на истоке или стоке первого TFT для деления напряжения, выходное напряжение на стоке первого TFT меньше, чем выходное напряжение на стоке второго TFT, при одном и том же управляющем напряжении. Следовательно, создается разность напряжений между двумя субпиксельными электродами, соответственно, соединенными со стоком первого TFT и стоком второго TFT, при этом углы отклонения молекул жидкого кристалла в пределах соответствующих областей жидкого кристалла изменяются. Таким образом, когда падающее световое излучение передается сквозь область жидкого кристалла, соответствующую одному блоку пикселей, испускаемое световое излучение по существу остается равномерным в различных направлениях, тем самым улучшая угол наблюдения жидкокристаллического дисплея и уменьшая сложность структуры матричной подложки без добавления дополнительного TFT.

[67] В описании данного изобретения отдельные признаки, структуры, материалы или характеристики могут соответствующим образом комбинироваться в любом одном или более вариантах осуществления или примерах.

[68] Предшествующее описание всего лишь иллюстрирует конкретные варианты осуществления данного изобретения, но объем данного изобретения не ограничен ими, и любые варианты и изменения, которые, вероятно, могут приходить в голову специалистам в данной области техники в пределах сущности изобретения, находятся в пределах объема изобретения, как определено в прилагаемой формуле изобретения.

В соответствии с вариантами осуществления данного изобретения предлагаются матричная подложка и устройство отображения. Блок пикселей содержит первый субпиксельный электрод и второй субпиксельный электрод, первый субпиксельный электрод соединен со стоком первого TFT, а второй субпиксельный электрод соединен со стоком второго TFT; сопротивление между истоком первого TFT и шиной данных, соединенной с первым TFT, больше, чем сопротивление между истоком второго TFT и шиной данных, соединенной со вторым TFT; и/или сопротивление между стоком первого TFT и первым субпиксельным электродом больше, чем сопротивление между стоком второго TFT и вторым субпиксельным электродом. 2 н. и 11 з.п. ф-лы, 7 ил.

1. Матричная подложка, содержащая: множество блоков пикселей, разделенных затворными шинами и шинами данных, расположенными перекрестно, в которой:

каждый из блоков пикселей содержит первый субпиксельный электрод, второй субпиксельный электрод, первый тонкопленочный транзистор (TFT) и второй TFT; первый субпиксельный электрод соединен со стоком первого TFT, а второй субпиксельный электрод соединен со стоком второго TFT;

сопротивление между истоком первого TFT и шиной данных, соединенной с первым TFT, больше, чем сопротивление между истоком второго TFT и шиной данных, соединенной со вторым TFT; и/или сопротивление между стоком первого TFT и первым субпиксельным электродом больше, чем сопротивление между стоком второго TFT и вторым субпиксельным электродом,

при этом

исток первого TFT соединен с шиной данных, соединенной с первым TFT, посредством шины истока в форме ломаной линии, а исток второго TFT соединен с шиной данных, соединенной со вторым TFT, посредством шины истока в форме прямой линии; и/или

сток первого TFT соединен с первым субпиксельным электродом посредством шины стока в форме ломаной линии, а сток второго TFT соединен со вторым субпиксельным электродом посредством шины стока в форме прямой линии.

2. Матричная подложка по п. 1, дополнительно содержащая:

первый резистор делителя напряжения на шине истока, соединенной с истоком первого TFT, и/или

второй резистор делителя напряжения на шине стока, соединенной со стоком первого TFT.

3. Матричная подложка по п. 2, в которой, когда первый резистор делителя напряжения расположен на шине истока, соединенной с истоком первого TFT, шина истока, соединенная с истоком первого TFT, содержит первые сегменты истока, разнесенные друг от друга, и первый резистор делителя напряжения содержит вторые сегменты истока в другом слое по отношению к первым сегментам истока;

вторые сегменты истока соединены с первыми сегментами истока, разнесенными друг от друга, через сквозные отверстия; а исток второго TFT расположен в том же слое, что и первые сегменты истока или вторые сегменты истока.

4. Матричная подложка по п. 3, в которой вторые сегменты истока расположены в том же слое, что и первый субпиксельный электрод и/или второй субпиксельный электрод.

5. Матричная подложка по п. 2, в которой, когда первый резистор делителя напряжения расположен на шине истока, соединенной с истоком первого TFT, шина истока, соединенная с истоком первого TFT, содержит первый сегмент истока и второй сегмент истока, и первый резистор делителя напряжения содержит диодную пару;

один конец диодной пары соединен с первым сегментом истока, а другой конец диодной пары соединен со вторым сегментом истока; и диодная пара содержит диод прямой полярности и обращенный диод, соединенные параллельно.

6. Матричная подложка по п. 5, в которой диод прямой полярности и обращенный диод сформированы путем закорачивания тонкопленочного транзистора, соответственно;

диод прямой полярности содержит первый закороченный исток, первый закороченный сток и первую область затвора, первый закороченный исток соединен с первым сегментом истока, первый закороченный сток соединен со вторым сегментом истока, а первая область затвора закорочена на первый закороченный исток через сквозное отверстие; и

обращенный диод содержит второй закороченный исток, второй закороченный сток и вторую область затвора, второй закороченный исток соединен с первым сегментом истока, второй закороченный сток соединен со вторым сегментом истока, а вторая область затвора закорочена на второй закороченный сток через сквозное отверстие.

7. Матричная подложка по п. 6, в которой первая область затвора и вторая область затвора расположены в том же слое, что и затвор первого TFT и затвор второго TFT, соответственно.

8. Матричная подложка по п. 6, в которой

сквозные отверстия, соответственно, сформированы в первой области затвора и первом закороченном истоке, и два сквозных отверстия соединены путем наложения прозрачного проводящего слоя на два сквозных отверстия, и

сквозные отверстия, соответственно, сформированы во второй области затвора и втором закороченном стоке, и два сквозных отверстия соединены путем наложения прозрачного проводящего слоя на два сквозных отверстия.

9. Матричная подложка по п. 2, в которой, когда второй резистор делителя напряжения расположен на шине стока, соединенной со стоком первого TFT, шина стока, соединенная со стоком первого TFT, содержит первые сегменты стока, разнесенные друг от друга, второй резистор делителя напряжения содержит вторые сегменты стока, расположенные в другом слое по отношению к первым сегментам истока, и вторые сегменты стока соединены с разнесенными первыми сегментами стока через сквозные отверстия.

10. Матричная подложка по п. 1, в которой непроникающая канавка расположена на затворной шине, раскрыв канавки обращен к первому субпиксельному электроду или второму субпиксельному электроду, а шина истока первого TFT перекрыта затвором упомянутого TFT путем прохождения через дно канавки.

11. Матричная подложка по п. 10, в которой канавка проходит в направлении от второго субпиксельного электрода к первому субпиксельному электроду и не проходит через шину затвора.

12. Матричная подложка по любому из пп. 1-11, в которой в одном из блоков пикселей исток первого TFT и исток второго TFT соединены с одной и той же шиной данных, и затвор первого TFT и затвор второго TFT соединены с одной и той же затворной шиной.

13. Устройство отображения, содержащее: матричную подложку по любому из пп. 1-12.

| CN 101750812 A, 23.06.2010 | |||

| CN 103744244 A, 23.04.2014 | |||

| JP 0572995 A, 26.03.1993 | |||

| US 2009213286 A1, 27.08.2009 | |||

| US 6476787 B1, 05.11.2002 | |||

| ДИСПЛЕЙНАЯ ПАНЕЛЬ СО ВСТРОЕННЫМИ ОПТИЧЕСКИМИ СЕНСОРАМИ | 2009 |

|

RU2469378C1 |

Авторы

Даты

2019-12-26—Публикация

2015-11-02—Подача